Documente Academic

Documente Profesional

Documente Cultură

Lab 6 - 2-Out-Of-5 To BCD Code Converter With Display

Încărcat de

Sanan yaqoobDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lab 6 - 2-Out-Of-5 To BCD Code Converter With Display

Încărcat de

Sanan yaqoobDrepturi de autor:

Formate disponibile

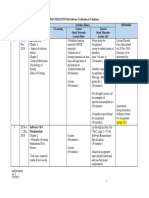

FacultyMember: Engr Arshad Nazir Date: 3rd April, 2018

.

Semester: 2nd Section: BESE-8A

EE221 – Digital Logic Design

Lab7: Part (a): Design of 2-out-of-5 to BCD Code Converter with Display

Part (b): Gate-level Modeling in Verilog

S. No. Student Name Reg. No. Total Marks

S1 Muhammad Shaharyar 211690

S2 Muhammad Usama 212622

S3 Taimoor Khan Mahsud 212573

S4

Method: Viva, Lab report and instructor observation during lab session. Group No. 7

Outcome Assessed:

a. Ability to conduct experiments, as well as to analyze and interpret data (P).

b. Ability to function in a team (A).

c. Ability to use the techniques, skills and modern engineering tools necessary for engineering

practice (P).

Does not meet Marks

Exceeds expectation Meets expectation

Performance expectation

(10--8)/(5--4) (7--5)/(3)

(4--1)/(2--1) S1 S2 S3 S4

Needs guidance to

Selects relevant equipment Incapable ofselecting

select relevant

to the experiment, develops relevant equipment to

1.Realization Of equipment to the

setup diagrams of conduct the experiment,

Experiment [c] experiment and to

equipment connections or equipment connection or

10 develop equipment

wiring. wiring diagrams are

connection or

unrecognizable.

wiringdiagrams.

Actively engages and

Cooperates with other Distracts or discourages

2. Teamwork [b] cooperateswith other group

group members in a other group members from

5 members in an effective

reasonable manner. conducting the experiment.

manner.

Does proper calibration of Calibrates equipment,

Unable to

3.Conducting equipment, carefully examines

calibrateappropriate

Experiment [a] examines equipment and equipmentand wiring

equipmentand wiring, and

5 wiring components, and of components and

equipment operation is

ensures smooth operation operates theequipment

substantially wrong.

and process. with minorerror.

4. Laboratory Respectfully and carefully Observes safety rules

Disregards safety rules and

Safety Rules [a] observes safety rules and and procedures

procedures.

5 procedures. Withminor deviation.

Plans data collection to Plans data collectionto Does not know how to Plan

5. Data achieve experimental achieve experimental data collection toachieve

Collection[a] objectives, and conducts an objectives, and collects experimental goals; data

10 orderlyand a complete data complete data with collected is incomplete and

collection. minor error. contain errors.

EE-221: Digital Logic Design Page 1

Lab7: Part (a): Design of 2-out-of-5 to BCD Code Converter with

Display

This Lab Activity has been designed to familiarize the student with design and working of a 2-out-

of-5 to BCD Code Converter with numeric Display circuit. Psychomotor Level P-4

Objectives:

Simplification of output Boolean functions using Five-Variable map from truth table.

Design of Code Converter block using Two-Level NAND gates.

System integration with BCD-to-Seven-Segment Decoder and Numeric readout for decimal

display.

Understand the difference between common cathode and common anode displays

Lab Instructions

This lab activity comprises three parts, namely Pre-lab, Lab tasks, and Post-Lab Viva

session.

The lab report will be uploaded on LMS three days before scheduled lab date. The

students will get hard copy of lab report, complete the Pre-lab task before coming to

the lab and deposit it with teacher/lab engineer for necessary evaluation.

The students will start lab task and demonstrate design steps separately for step-

wise evaluation (course instructor/lab engineer will sign each step after ascertaining

functional verification)

Remember that a neat logic diagram with pins numbered coupled with nicely

patched circuit will simplify trouble-shooting process.

After the lab, students are expected to unwire the circuit and deposit back

components before leaving.

The Total duration for the lab is 3 hrs. The students are expected to complete

lab within specified time.

A lab with in-complete lab tasks will not be accepted.

The students will complete lab task and submit complete report to Lab Engineer

before leaving lab.

There are related questions at the end of this activity. Give complete answers.

This lab is OBE compliant.

EE-221: Digital Logic Design Page 2

Pre-Lab Tasks:

1. What do you mean by non-weighted codes? Give any two examples. (1 Mark)

Answer:

The codes which have no positional weights are called non-weighted codes. In other

words, the codes which are not given any weights, such as:

Gray code, 2 out of 5 code, XS-3 code etc. In gray code 3 is represented as 0010 then

actually it would have been 0010 it represents 3.

2. What are de-generate forms? List any five. What are the applications of these forms in

digital design? (2 Marks)

Answer:

In a two level circuit those combinations which are reduced to a single operation are

called degenerate forms.

1. AND-AND

2. OR-OR

3. AND-NAND

4. OR-NOR

5. NAND-OR

3. 7-Segment LED Displays are commonly used for displaying decimal Numbers (0 to 9). It

can also be used for displaying alphabets. A 7-Segment LED Displays essentially

consist of 7 LEDs configured as shown below to display numbers. It comes in two

configurations. Common Cathode and Common Anode. Draw the diagram showing

connections to drivers and power source and ground for both configurations and

highlight differences between the two. Also give signal logic level required to light up the

LEDs in the segment in each configuration: (2 Marks)

EE-221: Digital Logic Design Page 3

4. Complete the following table. (3 Marks)

Dec Inputs (2-out-of-5) Output(BCD)

A B C D E W x y z

0 1 1 0 0 0 0 0 0 0

1 0 0 0 1 1 0 0 0 1

2 0 0 1 0 1 0 0 1 0

3 0 0 1 1 0 0 0 1 1

4 0 1 0 0 1 0 1 0 0

5 0 1 0 1 0 0 1 0 1

6 0 1 1 0 0 0 1 1 0

7 1 0 0 0 1 0 1 1 1

8 1 0 0 1 0 1 0 0 0

9 1 0 1 0 0 1 0 0 1

∑d( )

5. Simplify the output functions w, x, y, and z using map method. Try to take maximum

advantage of don’t care conditions. (5 Marks)

W= DE + CE = [(DE)’.(CE)’]’

X= AE + BE + A’DE’ = [(AE)’.(BE)’.(A’DE’)’]’

Y= AB’ + BE = [(AB’)’.(BE)]’

Z= B’D + AB + BE = [(B’D)’.(AB)’.(BE)]’

EE-221: Digital Logic Design Page 4

Lab Tasks:

Lab Task 1

6. Give complete schematics for your design including 2-out-of-5 to BCD Code Converter

block, BCD-to-Seven-Segment driver IC and read out. A Schematic is a logic diagram

with pin numbering and IC Labeling on each gate. (3 Marks)

EE-221: Digital Logic Design Page 5

7. Implement the above circuit in hardware using minimum number of NAND gates at Two-

Level and show the results to Teacher/Lab-Instructor. (10 Marks)

8. Mention which configuration of 7-Segment Display did you use in Lab? If you were to

use the other configuration what change would you need in your circuit? (1 Mark)

Answer:

We used common anode display for the output as the values a, b, c… were

already in complemented form. If we used the common cathode display, it would be

needed to flip the 1’s and 0’s of the BCD to convert the complemented values back to

the original values.

Part (b): Gate-level Modeling in Verilog

Lab Task 2:

EE-221: Digital Logic Design Page 6

9. Design and simulate the gate-level model of the circuit you have patched. Give the code

in the space provided. (8 marks)

Code:

Output:

EE-221: Digital Logic Design Page 7

Observations/Comments:

It took us a lot of time to complete the lab as the decoder IC was faulty and after

long time we came to know that it was not working.

W could also be expressed as ((A’B’E)’). If we used this expression we din’t need

to use C and the circuit could be implemented using four switches only.

EE-221: Digital Logic Design Page 8

S-ar putea să vă placă și

- Lab6a 2-Out-Of-5 To BCD Code Converter and Display CircuitDocument11 paginiLab6a 2-Out-Of-5 To BCD Code Converter and Display CircuitMustafaAsimÎncă nu există evaluări

- Lab Report 10Document5 paginiLab Report 10Samir KhanÎncă nu există evaluări

- Department of Electrical Engineering EE365L: Communication SystemsDocument18 paginiDepartment of Electrical Engineering EE365L: Communication SystemsAbrahan ShahzadÎncă nu există evaluări

- Lab 7Document18 paginiLab 7Dawood MehmoodÎncă nu există evaluări

- Semester: 7th: The Lab and Report SubmittedDocument5 paginiSemester: 7th: The Lab and Report SubmittedSyed Tihaam AhmadÎncă nu există evaluări

- Department of Electrical Engineering EE472: RF & Microwave EngineeringDocument10 paginiDepartment of Electrical Engineering EE472: RF & Microwave EngineeringSaira AzizÎncă nu există evaluări

- Lab 7Document3 paginiLab 7M Shahid HanifÎncă nu există evaluări

- Department of Electrical Engineering EE365L: Communication SystemsDocument13 paginiDepartment of Electrical Engineering EE365L: Communication SystemsAbrahan ShahzadÎncă nu există evaluări

- Electronic Circuits and Analysis-I Lab ECE 217 Credits:2Document49 paginiElectronic Circuits and Analysis-I Lab ECE 217 Credits:2vj86Încă nu există evaluări

- CAD RubricsDocument2 paginiCAD RubricsAbdulManan MemonÎncă nu există evaluări

- Electrical Engineering Department CS243L: Data Structures and AlgorithmsDocument4 paginiElectrical Engineering Department CS243L: Data Structures and AlgorithmsHamza ShahidÎncă nu există evaluări

- Lab 09Document4 paginiLab 09Muhammad Huzaifa AmjadÎncă nu există evaluări

- DCN Manual 12022024 084420pmDocument79 paginiDCN Manual 12022024 084420pmGullalai shahÎncă nu există evaluări

- Particulate Technology Lab: Course code:CHE-324Document20 paginiParticulate Technology Lab: Course code:CHE-324Iqra ShakeelÎncă nu există evaluări

- Electrical Engineering Department CS243L: Data Structures and AlgorithmsDocument6 paginiElectrical Engineering Department CS243L: Data Structures and AlgorithmsHamza ShahidÎncă nu există evaluări

- Electrical Engineering Department CS243L: Data Structures and AlgorithmsDocument5 paginiElectrical Engineering Department CS243L: Data Structures and AlgorithmsHamza ShahidÎncă nu există evaluări

- EE 353 Computer Networks-Fall 2022Document81 paginiEE 353 Computer Networks-Fall 2022Muhammad TalhaÎncă nu există evaluări

- DLP Lab ManualDocument72 paginiDLP Lab ManualPoorna chand Evuru100% (1)

- Ain Shams University Faculty of EngineeringDocument3 paginiAin Shams University Faculty of EngineeringRitaÎncă nu există evaluări

- RubricDocument1 paginăRubricMuhammad Umer ShakirÎncă nu există evaluări

- LR8 Ali Haider 231783 CPDocument17 paginiLR8 Ali Haider 231783 CPKashf ShabbirÎncă nu există evaluări

- WSN Lab Manual PDFDocument109 paginiWSN Lab Manual PDFAnirudh Attanti100% (1)

- Clap Detection With Microcontroller: Cyril Arnould, Nicolas de Palézieux Dit Falconnet, Dennis Meier, Daniel WälchliDocument22 paginiClap Detection With Microcontroller: Cyril Arnould, Nicolas de Palézieux Dit Falconnet, Dennis Meier, Daniel WälchliasldfÎncă nu există evaluări

- DT Key MaretrialDocument12 paginiDT Key MaretrialSudheer RajaÎncă nu există evaluări

- Prepared By: Computer Network Lab ManualDocument47 paginiPrepared By: Computer Network Lab ManualMadihaÎncă nu există evaluări

- Ept Lab 14Document6 paginiEpt Lab 14K162379 Muhammad TalhaÎncă nu există evaluări

- Ept Lab 14Document6 paginiEpt Lab 14K162379 Muhammad TalhaÎncă nu există evaluări

- VerilogDocument55 paginiVerilogGunjan BansalÎncă nu există evaluări

- Electrical Machines-Open Ended LabDocument3 paginiElectrical Machines-Open Ended LabALISHBA AZAMÎncă nu există evaluări

- Control System Lab Manual V 1Document173 paginiControl System Lab Manual V 1Engr. M. Farhan Faculty Member UET Kohat100% (1)

- CNS Post FinalDocument6 paginiCNS Post FinalDev BarotÎncă nu există evaluări

- Lab 3 Introduction To VerilogDocument6 paginiLab 3 Introduction To Verilogpioneer boysÎncă nu există evaluări

- Electrical Engineering Department CS243L: Data Structures and AlgorithmsDocument5 paginiElectrical Engineering Department CS243L: Data Structures and AlgorithmsHamza ShahidÎncă nu există evaluări

- Linear Lab 4Document4 paginiLinear Lab 4Zainab Ali Naveed IrshadÎncă nu există evaluări

- ECE241 Syllabus Fall 2014Document7 paginiECE241 Syllabus Fall 2014Tetteh SamuelÎncă nu există evaluări

- LDCO Lab ManualDocument78 paginiLDCO Lab ManualAshwin singhÎncă nu există evaluări

- EE4455 Embedded Systems - OBTLDocument6 paginiEE4455 Embedded Systems - OBTLAaron Tan100% (1)

- LAb 4Document6 paginiLAb 4Shahzeb KayaniÎncă nu există evaluări

- LICD Lab 2Document5 paginiLICD Lab 2Abdul MohsinÎncă nu există evaluări

- Laboratory Manual: ELE-203 Digital Logic DesignDocument73 paginiLaboratory Manual: ELE-203 Digital Logic DesignMoiz MazharÎncă nu există evaluări

- Institute Vision: To Shape Electronics & Telecommunication Engineers To Be Professionally and Socially CompetentDocument43 paginiInstitute Vision: To Shape Electronics & Telecommunication Engineers To Be Professionally and Socially CompetentFARHAAN. AÎncă nu există evaluări

- COS 0642 Lab Works Jan 2024Document17 paginiCOS 0642 Lab Works Jan 2024zaimdigimaxÎncă nu există evaluări

- Ooj Prac 3 - 30Document5 paginiOoj Prac 3 - 30ABCD EFGÎncă nu există evaluări

- LAb 3BDocument5 paginiLAb 3BShahzeb KayaniÎncă nu există evaluări

- Experiment No 8Document7 paginiExperiment No 85682 AatqaÎncă nu există evaluări

- DJM6113 Lab 1 Introduction of Robot BasisDocument6 paginiDJM6113 Lab 1 Introduction of Robot BasisAmirul Naim50% (2)

- LICD Lab 5Document9 paginiLICD Lab 5Abdul MohsinÎncă nu există evaluări

- CEPEE314 UpdatedDocument4 paginiCEPEE314 UpdatedMuhammad umairÎncă nu există evaluări

- Differential AmplifierDocument5 paginiDifferential AmplifierIsabela SmithÎncă nu există evaluări

- Lab Manual of Computer Networks Lab ETCS 354Document61 paginiLab Manual of Computer Networks Lab ETCS 354vaibhav kashyapÎncă nu există evaluări

- Csc103 PF Lab Manual Sp22 v3.1Document133 paginiCsc103 PF Lab Manual Sp22 v3.1fa22-bse-051Încă nu există evaluări

- Course Code: 4361103: Page 1 of 8Document8 paginiCourse Code: 4361103: Page 1 of 8rashmin tannaÎncă nu există evaluări

- Signals and Systems Lab Manual-2020Document92 paginiSignals and Systems Lab Manual-2020shayan sheikhÎncă nu există evaluări

- Institute VisionDocument38 paginiInstitute VisionSyed Zuhair AbbasÎncă nu există evaluări

- Lab 13Document5 paginiLab 13Fazool FarighÎncă nu există evaluări

- EE445-ABET Form - Course OutlineDocument3 paginiEE445-ABET Form - Course OutlineRaya AwadÎncă nu există evaluări

- Updated MOS 1 (Lab Manual)Document71 paginiUpdated MOS 1 (Lab Manual)Noor Ul Amin AwanÎncă nu există evaluări

- Digital Logic Design Lab: Department of Electrical EngineeringDocument8 paginiDigital Logic Design Lab: Department of Electrical EngineeringHassan Khan100% (1)

- Digital Circuit Testing: A Guide to DFT and Other TechniquesDe la EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesÎncă nu există evaluări

- Spatial ModelerDocument76 paginiSpatial Modelerapi-3788255Încă nu există evaluări

- Functional Dependencies and Normalization For Relational DatabasesDocument77 paginiFunctional Dependencies and Normalization For Relational DatabasesCho ConÎncă nu există evaluări

- Cisco SD WanDocument2 paginiCisco SD WanKurabiye CanavarıÎncă nu există evaluări

- Elmasri 6e Ch04Document45 paginiElmasri 6e Ch04Joona JohnÎncă nu există evaluări

- Oracle Hyperion PlanningDocument3 paginiOracle Hyperion PlanningAmit Sharma0% (1)

- Support File For Actix AnalyzerDocument4 paginiSupport File For Actix Analyzerعلي عباسÎncă nu există evaluări

- ValueCut User Manual EnglishDocument112 paginiValueCut User Manual EnglishJavier Espinoza GamarraÎncă nu există evaluări

- Procedure For Law Enforcement RequestsDocument15 paginiProcedure For Law Enforcement RequestsWallaÎncă nu există evaluări

- Exception HandlingDocument6 paginiException Handlinghonaday945Încă nu există evaluări

- Ahmad Nafir Bin Ahmad Sukeri-2Document4 paginiAhmad Nafir Bin Ahmad Sukeri-2Ahmad NaferÎncă nu există evaluări

- Rhel7 rh124 Course Description PDFDocument3 paginiRhel7 rh124 Course Description PDFJeffÎncă nu există evaluări

- SFP-1GE-FE-E-T: Optics OverviewDocument6 paginiSFP-1GE-FE-E-T: Optics OverviewAlexander Sison Jr.Încă nu există evaluări

- IT462 Internet of ThingsDocument2 paginiIT462 Internet of ThingsHOD CSÎncă nu există evaluări

- Sysmac Studio 3D Simulation Function Operation Manual 202208Document206 paginiSysmac Studio 3D Simulation Function Operation Manual 202208Nurdeny PribadiÎncă nu există evaluări

- ACS800 FirmwareManual 28022007 PDFDocument272 paginiACS800 FirmwareManual 28022007 PDFCarles RochÎncă nu există evaluări

- JavaScript Book Without Projects Code v1Document84 paginiJavaScript Book Without Projects Code v1yeechienÎncă nu există evaluări

- R23AMR ReleaseHighlightsDocument387 paginiR23AMR ReleaseHighlightsgthmraaÎncă nu există evaluări

- CN Chapter1Document22 paginiCN Chapter1nishitha.eeeÎncă nu există evaluări

- Itil v3 A Pocket GuideDocument23 paginiItil v3 A Pocket Guideiraguz1Încă nu există evaluări

- Trainingbook WallixDocument49 paginiTrainingbook WallixRocky4uÎncă nu există evaluări

- (MCQ'S) Production Planning and ControlDocument5 pagini(MCQ'S) Production Planning and ControlHVFTOOLS HVFÎncă nu există evaluări

- PLSQLDocument68 paginiPLSQLSharathRajÎncă nu există evaluări

- Micro Project Proposal: Sharad Institute of Technology, PolytechnicDocument5 paginiMicro Project Proposal: Sharad Institute of Technology, PolytechnicAshish AmbiÎncă nu există evaluări

- OurApp Using NodejsDocument19 paginiOurApp Using NodejsPOLURU SUMANTH NAIDU STUDENT - CSEÎncă nu există evaluări

- 6) Unit II - Multiprocessor SchedulingDocument18 pagini6) Unit II - Multiprocessor SchedulingHehdhdhdjjdÎncă nu există evaluări

- Resumen Capitulo 1 (SOFTWARE REQUIREMENTS 3RD EDITION)Document5 paginiResumen Capitulo 1 (SOFTWARE REQUIREMENTS 3RD EDITION)Isocrates FlyboxÎncă nu există evaluări

- TSV3561 Lesson Plan For StudentDocument9 paginiTSV3561 Lesson Plan For StudentShenWeiÎncă nu există evaluări

- Project Report On Online Sales Order Management SystemDocument77 paginiProject Report On Online Sales Order Management Systemshifara TesfayeÎncă nu există evaluări

- Workstation Heat, Power Usage, and Sound: Lenovo ThinkStation C30 vs. HP Z620 WorkstationDocument14 paginiWorkstation Heat, Power Usage, and Sound: Lenovo ThinkStation C30 vs. HP Z620 WorkstationPrincipled TechnologiesÎncă nu există evaluări

- 19 Concurrency ControlDocument56 pagini19 Concurrency ControlVikram ChandraÎncă nu există evaluări