Documente Academic

Documente Profesional

Documente Cultură

Abstract-The Enhancement of Recycling Folded Cascode (RFC)

Încărcat de

Sougata GhoshTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Abstract-The Enhancement of Recycling Folded Cascode (RFC)

Încărcat de

Sougata GhoshDrepturi de autor:

Formate disponibile

2016 International Conference on Consumer Electronics-Taiwan

The Enhancement of Recycling Folded Cascode Amplifier

Po-Yu Kuo, Gang-Jhih Fan, and Sheng-Da Tsai

Department of Electronic Engineering, National Yunlin University of Science & Technology, Doulou, Taiwan

kuopy@yutech.edu.tw

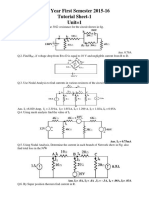

Abstract–The enhancement of recycling folded cascode (RFC) VDD

operational transconductance amplifier (OTA) is described in

this paper. The proposed enhanced recycling folded cascode M15 2Ib/2 Vb1 M0 2Ib 2Ib/2 M16 M17

(ERFC) structure improves dc gain and unity-gain frequency of

RFC amplifier. The ERFC OTA has been implemented using

TSMC 0.18ȝm CMOS process and simulated with a 1.8V power

supply and a 5.6pF capacitor load. Simulation results show that Vb3 M14 VOUT

Vin+ Vin-

the proposed ERFC OTA achieves 27dB increment in dc gain Vb3

(72.2dB versus 45.2dB) and about 11 times better in unity-gain M13 M1 M2 M3 M4 CL

frequency (66.5MHz versus 746MHz) compared with the RFC

OTA. M18

M5 M6 Vb2

Vb2

M11 M12

I. INTRODUCTION Vb2

The operational transconductance amplifier (OTA) is an M7 M8 M9 M10

important building block in most analog circuits [1]–[3]. K Ļġġ1 1 : K

Recently, the folded cascode (FC) amplifier is commonly used GND

in the single-stage or multi-stage amplifiers due to its high Figure 1. Proposed enhanced RFC amplifier.

gain and large signal swing. Therefore, many circuit

topologies has been proposed to improve the traditional FC some topologies have been proposed to improve RFC

amplifier in the past decades [4]-[5]. The recycling folded amplifier, the circuit complexity increases significantly [6]-[7].

cascode (RFC) structure have been proposed to enhance the However, the proposed ERFC amplifier only adds two

performance of traditional FC amplifier for its higher non- transistors M17 and M18 over RFC amplifier as shown in Fig.

dominant poles, slew rate, unity-gain frequency, and dc gain 1. It not only reduces the complexity of the circuits but also

[5]. improves the general performance compared with other

In this paper, an enhanced RFC (ERFC) amplifier is counterparts.

proposed by adding an output-stage to improve the dc gain

and unity-gain frequency. With the extra output-stage, the III. SIMULATION RESULTS

output impedance is increased so that the dc gain is enhanced

[6]. Moreover, the proposed amplifier also improves the unity-

The proposed ERFC amplifier is implemented using TSMC

gain frequency of the RFC amplifier.

0.18ȝm CMOS process and simulated with a 1.8V power

supply and a 5.6pF load. The simulated frequency response of

II. PROPOSED ENHANCED RFC AMPLIFIER

the proposed enhanced RFC amplifier is shown in Fig. 2.

From the simulation results, the dc gain of the FC, RFC and

The proposed enhanced recycling folded cascode (ERFC) ERFC is 34.3dB, 45.2dB and 72.2dB. The phase margin of the

amplifier is shown in Fig.1. The transistor M7, M8, M9, M10 FC, RFC and ERFC is 87.3°, 80° and 105.2°, respectively.

conduct the most currents in amplifier. The transistor M1, M2, The proposed ERFC structure achieves the highest DC gain

M3, M4 limits the currents flowing through whole amplifier and phase margin comparing to the FC and RFC amplifiers.

from power supply VDD. The current flowing through M14 Moreover, the unity-gain frequency of ERFC amplifier

and M15 is identical and equal to Ib/2 [5]. The cross-over achieves 746MHz, which is about 11 times better than that of

connections of current mirrors M7, M8 and M9, M10 ensure RFC amplifier (66.5MHz versus 746MHz). The simulated

the small signal currents injecting into the sources of M11 and transient response of the proposed amplifier is shown in Fig. 3.

M12. Thus, the current can be utilized by devices efficiently From the simulation results, the average slew rate of the

and perform additional task. Moreover, the proposed amplifier proposed amplifier is 4.02 V/ȝs.

modify the RFC amplifier by adding the transistor M17 and Table I shows the performance comparison of the proposed

enhanced recycling folded cascode (ERFC) amplifier against

M18 as enhanced device transistors. Since the dc gain of

previously reported amplifier architectures. From the summary

amplifier is dominated by common source stage, the dc gain

table, the proposed amplifier achieves 27dB enhancement of

can be improved with the enhanced device transistors.

dc gain over the RFC OTA for the same output load. The

In the following of this paper, we will compare the unity-gain frequency of ERFC amplifier also achieves

proposed amplifier with FC and RFC amplifier. Although 746MHz, which is about 11 times better than that of RFC

978-1-5090-2073-7/16/$31.00 ©2016 IEEE

2016 International Conference on Consumer Electronics-Taiwan

TABLE I

PERFORMANCE COMPARISON OF THE PROPOSED AMPLIFIER AND

PREVIOUSLY REPORTED AMPLIFIER ARCHITECTURES

2V- This This This

RFC IRFC

Parameter RFC work work work

[5] [7]

[6] (FC) (RFC) ERFC

0.18 65 0.13 0.18 0.18 0.18

Technology

ȝm nm ȝm ȝm ȝm ȝm

Supply

Voltage 1.8 2 1.2 1.8 1.8 1.8

[V]

CL [pF] 5.6 1 7 5.6 5.6 5.6

DC Gain

53.6 63.4 70.2 34.3 45.2 72.2

[dB]

PM [deg] 70.6 63.6 70 87.3 80 105.2

UGF [MHz] 134.2 236 83 34 66.5 746

SR (Average)

94.1 19 29.8 20.5 41.4 4.02

[V/ȝs]

ACKNOWLEDGMENT

The authors would like to appreciate technical support from

Figure 2. Simulated frequency response of designed amplifiers.

the National Chip Implementation Center (CIC).

REFERENCES

[1] G. Huang, D. Zhou, X. Zeng, and S. Wang, “A practical method

for auto-design and optimization of DC-DC buck converter,” in

Proc. IEEE 10th Int. Conf. on ASIC (ASICON), pp. 1-4, Oct.

2013.

[2] G. Huang and D. Zhou, “Design automation of analog circuit

considering the process variations,” in Proc. IEEE 10th Int. Conf.

on ASIC (ASICON), pp. 1-4, Oct. 2013.

[3] P.-Y. Kuo, S. Saibua, G. Huang and D. Zhou, “An efficient

method for evaluating analog circuit performance bounds under

process variations,” IEEE Tans. Circuits & Systems-II, vol. 59,

no. 6, pp. 351-355, Jun. 2012.

[4] P. Y. Wu, V. S.-L. Cheung, and H. C. Luong, “A 1-V 100-MS/s

8-bit CMOS switched-opamp pipelined ADC using loading-free

architecture,” IEEE J.Solid-Sate Circuit, vol. 42, no. 4, pp. 730-

738, Apr. 2007.

[5] R. S. Assaad and J. Silva-Martinez, “The recycling folded

Figure 3. Simulated transient response of designed amplifiers. cascode: a general enhancement of the folded cascode

amplifier,” IEEE J. Solid-Sate Circuit, vol. 44, no. 9, pp.2535-

2542, Sep. 2009.

amplifier. Hence, the proposed ERFC amplifier obtain highest

[6] M. Liu, P.-I. Mak, Z. Yan, R. P. Martins, and J. R. Carley, “A

performance such as dc gain, phase margin and unity-gain high-voltage-enabled recycling folded cascode OpAmp for

frequency, comparing with the previously reported amplifier nanoscale CMOS technologies,” in Proc. IEEE Int. Symp. on

architectures. Circuits & Systems (ISCAS) , pp. 33-36, May. 2011.

[7] Y. L. Li, K. F. Han, X. Tan, N. Yan, and H. Min,

“Transconductance enhancement method for operational

IV. CONCLUSIONS transconductance amplifiers,” Electronics Letters, pp. 1321-

In this paper, an enhanced RFC amplifier is proposed and 1323, Sep. 2010.

implemented. The proposed amplifier modifies the RFC

amplifier by adding a common source stage. It not only

reduces the complexity of the circuits but also improves the

general performance compared with other counterparts. From

the simulation results, the enhanced RFC amplifier improves

the dc gain by 27dB over the RFC amplifier for the same

power supply. Moreover, it also achieves high unity-gain

frequency and phase margin which is 746MHz and 105°,

respectively.

978-1-5090-2073-7/16/$31.00 ©2016 IEEE

S-ar putea să vă placă și

- The Recycling Folded Cascode A General Enhancement of The Folded Cascode AmplifierDocument8 paginiThe Recycling Folded Cascode A General Enhancement of The Folded Cascode AmplifierAyanabho BanerjeeÎncă nu există evaluări

- A DTMOS-based Power Efficient Recycling Folded Cascode Operational Transconductance AmplifierDocument12 paginiA DTMOS-based Power Efficient Recycling Folded Cascode Operational Transconductance AmplifierBüşra AkyıldızÎncă nu există evaluări

- Paper Publish 1 PDFDocument5 paginiPaper Publish 1 PDFSupriya Tenny SamÎncă nu există evaluări

- High Speed & Low Power Comparator Using Double-Gate MOSFET Scalable To 20nmDocument5 paginiHigh Speed & Low Power Comparator Using Double-Gate MOSFET Scalable To 20nmSupriya Tenny SamÎncă nu există evaluări

- Finfet Based Flash Adc PDFDocument4 paginiFinfet Based Flash Adc PDFJam 234Încă nu există evaluări

- High Performance Folded Cascode OTA Using Positive FeedbackDocument11 paginiHigh Performance Folded Cascode OTA Using Positive Feedbackekta jollyÎncă nu există evaluări

- FinFET Based 3-Bit Flash ADC On 32nm TechnologyDocument6 paginiFinFET Based 3-Bit Flash ADC On 32nm TechnologySupriya Tenny SamÎncă nu există evaluări

- The Recycling Folded CascodeDocument8 paginiThe Recycling Folded CascodeFelipe BertonÎncă nu există evaluări

- Improving Power Efficiency of A Two-Stage Operational AmplifierDocument11 paginiImproving Power Efficiency of A Two-Stage Operational AmplifierHenry HuoÎncă nu există evaluări

- Design and Simulation of 4T-Cascode Amplifier at 45 Nanometer Technology NodeDocument4 paginiDesign and Simulation of 4T-Cascode Amplifier at 45 Nanometer Technology NodeHassan El-kholyÎncă nu există evaluări

- Nested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier With Enhancements of DC Gain, GBW and Slew RateDocument14 paginiNested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier With Enhancements of DC Gain, GBW and Slew Rateian neymarÎncă nu există evaluări

- Optical Amplifiers For Modern NetworksDocument4 paginiOptical Amplifiers For Modern NetworksFilzaÎncă nu există evaluări

- A 3.5 GS/s 5-b Ash ADC in 90 NM CMOS: Proceedings of The Custom Integrated Circuits Conference October 2006Document5 paginiA 3.5 GS/s 5-b Ash ADC in 90 NM CMOS: Proceedings of The Custom Integrated Circuits Conference October 2006Nguyễn Thái NguyênÎncă nu există evaluări

- Design of A 2.4 GHZ High-Performance Up-Conversion Mixer With Current Mirror TopologyDocument6 paginiDesign of A 2.4 GHZ High-Performance Up-Conversion Mixer With Current Mirror TopologyAkhendra KumarÎncă nu există evaluări

- Circuit Applications of Carbon Nanotube FetsDocument4 paginiCircuit Applications of Carbon Nanotube FetsHamad_SpiderÎncă nu există evaluări

- Comparison of BW For RC Coupled Single Stage and Multi Stage AmplifieDocument6 paginiComparison of BW For RC Coupled Single Stage and Multi Stage AmplifieFaras SmansaÎncă nu există evaluări

- A 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyDocument9 paginiA 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyAdam HernandezÎncă nu există evaluări

- High SR 2 Stage Opamp TechPaperDocument3 paginiHigh SR 2 Stage Opamp TechPaperVarad KeniÎncă nu există evaluări

- Conventional and Improved 4-Bit Ripple Carry Adder ComparisonDocument4 paginiConventional and Improved 4-Bit Ripple Carry Adder ComparisonBienvenido LasacaÎncă nu există evaluări

- Continuous-Time Common-Mode Feedback For High-Speed Switched-Capacitor Networks. IEEE Journal of Solid-State Circuits, 40 (8), 1610-1617Document9 paginiContinuous-Time Common-Mode Feedback For High-Speed Switched-Capacitor Networks. IEEE Journal of Solid-State Circuits, 40 (8), 1610-1617LaurMateiÎncă nu există evaluări

- Design of A Wide Band RF Amplifier Using Scattering ParametersDocument4 paginiDesign of A Wide Band RF Amplifier Using Scattering ParametersAnthony HubbardÎncă nu există evaluări

- Wireless Power Transmission Batch7Document7 paginiWireless Power Transmission Batch7St. Anne's CET (EEE Department)Încă nu există evaluări

- Ee410 Final Design ProjectDocument4 paginiEe410 Final Design Projectapi-294954225Încă nu există evaluări

- NE602 App NoteDocument13 paginiNE602 App Noteandrei8411Încă nu există evaluări

- A R Econfigurable L Ow I F - Z Ero I F R Eceiver Architecture F or Multi Standard Wireless Systems Using A Reconfigurable FilterDocument12 paginiA R Econfigurable L Ow I F - Z Ero I F R Eceiver Architecture F or Multi Standard Wireless Systems Using A Reconfigurable Filterjmicrojouranl1Încă nu există evaluări

- Operational Amplifier EX.Document9 paginiOperational Amplifier EX.حسن صادق فرج فليحBÎncă nu există evaluări

- Article ATSIP 1Document4 paginiArticle ATSIP 1amel.neifarÎncă nu există evaluări

- 1 PDFDocument6 pagini1 PDFfadillahÎncă nu există evaluări

- ELEC3240 Laboratories 2011Document18 paginiELEC3240 Laboratories 2011Michael AwaÎncă nu există evaluări

- A 250-Khz 94-Db Double-Sampling A/D Converter With A Modified Noise Transfer FunctionDocument6 paginiA 250-Khz 94-Db Double-Sampling A/D Converter With A Modified Noise Transfer FunctionRamakrishnaVakulabharanamÎncă nu există evaluări

- Synopsis VCO BDCoEDocument9 paginiSynopsis VCO BDCoEraymar2kÎncă nu există evaluări

- 40W No Tune FM Broadcast Power Amplifier DesignDocument15 pagini40W No Tune FM Broadcast Power Amplifier DesignTj Ronz SaguidÎncă nu există evaluări

- A 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)Document4 paginiA 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)dhrubÎncă nu există evaluări

- Current Feedback Vs Voltage Feedback AmplifiersDocument79 paginiCurrent Feedback Vs Voltage Feedback AmplifiersHanieft NdÎncă nu există evaluări

- International Journal of Electronics and Communications (AEÜ)Document10 paginiInternational Journal of Electronics and Communications (AEÜ)Numan KayaÎncă nu există evaluări

- HAMADA - A FULLY INTEGRATED 2x1 DUAL-BAND DIRECT-CONVERSION MOBILE WiMAX TRANSCEIVERDocument11 paginiHAMADA - A FULLY INTEGRATED 2x1 DUAL-BAND DIRECT-CONVERSION MOBILE WiMAX TRANSCEIVERmanasÎncă nu există evaluări

- Valliammai Engineering College: (A Member of SRM Group of Institutions)Document7 paginiValliammai Engineering College: (A Member of SRM Group of Institutions)Jayasuriya PalaniÎncă nu există evaluări

- Free Space Optics ResearchDocument6 paginiFree Space Optics ResearchRF_RAJAÎncă nu există evaluări

- 4GV White PaperDocument13 pagini4GV White Paperrajwarang100% (1)

- Xiaodan Zhou, Langcheng Lei, Chen Su, Ai Guo and Dongmei ZhuDocument6 paginiXiaodan Zhou, Langcheng Lei, Chen Su, Ai Guo and Dongmei ZhuUdai ValluruÎncă nu există evaluări

- A Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterDocument13 paginiA Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterdeviÎncă nu există evaluări

- Design of Double Balanced Gilbert Cell Mixer For WBAN ApplicationsDocument4 paginiDesign of Double Balanced Gilbert Cell Mixer For WBAN ApplicationsAhmed MaGdyÎncă nu există evaluări

- A - Reconfigurable - Rectifier - With - Optimal - Loading - Point - Determination - For - RF - Energy - Harvesting - From - 22 - DBM - To - 2 - DBMDocument5 paginiA - Reconfigurable - Rectifier - With - Optimal - Loading - Point - Determination - For - RF - Energy - Harvesting - From - 22 - DBM - To - 2 - DBMhusam hamidÎncă nu există evaluări

- Homebrew RF Transceiver DesignDocument41 paginiHomebrew RF Transceiver DesignDefaultAnomoly100% (10)

- VCO Design For WLAN 2.4GDocument9 paginiVCO Design For WLAN 2.4GQuang Nguyen-TheÎncă nu există evaluări

- Abstract - : 2.1.pin Configuration and OperationDocument3 paginiAbstract - : 2.1.pin Configuration and OperationPranao NakulÎncă nu există evaluări

- A 2-D Mode-Switching Quad-Core Oscillator Using E-M Mixed-Coupling Resonance BoostingDocument11 paginiA 2-D Mode-Switching Quad-Core Oscillator Using E-M Mixed-Coupling Resonance BoostingQiuFengÎncă nu există evaluări

- Fully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsDocument4 paginiFully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsHam Radio HSMMÎncă nu există evaluări

- LED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForDocument5 paginiLED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForArun KumarÎncă nu există evaluări

- Cmos Two Stage OpamppublishedDocument5 paginiCmos Two Stage Opamppublisheddeepak pandeyÎncă nu există evaluări

- Conducted EMI Issues in A Boost PFC Design: L. Rossetto S. Buso, G.SpiazziDocument8 paginiConducted EMI Issues in A Boost PFC Design: L. Rossetto S. Buso, G.SpiazziVishu JoshiÎncă nu există evaluări

- THE Am TX BEEDocument41 paginiTHE Am TX BEEAntonio SabaÎncă nu există evaluări

- High Speed Analog Design and Application Seminar: From Texas InstrumentsDocument39 paginiHigh Speed Analog Design and Application Seminar: From Texas InstrumentshaoyuqianÎncă nu există evaluări

- 2020.01 A Reconfigurable Rectifier With Optimal Loading Point Determination For RF Energy Harvesting From - 22 DBM To - 2 DBMDocument5 pagini2020.01 A Reconfigurable Rectifier With Optimal Loading Point Determination For RF Energy Harvesting From - 22 DBM To - 2 DBMAzrinYunusÎncă nu există evaluări

- Introduction To RF / Microwave Measurements and ApplicationsDocument5 paginiIntroduction To RF / Microwave Measurements and ApplicationsanetterdosÎncă nu există evaluări

- Complementary Push-Pull AmplifiersDocument12 paginiComplementary Push-Pull AmplifiersmplennaÎncă nu există evaluări

- Eca Lab-Min PDFDocument87 paginiEca Lab-Min PDFAkashita SharmaÎncă nu există evaluări

- Design and Development of Low-Range Frequency ModuDocument7 paginiDesign and Development of Low-Range Frequency ModuMohamed Amine TahiriÎncă nu există evaluări

- HG DS1Document6 paginiHG DS1moonofvuÎncă nu există evaluări

- JFET Characteristics PDFDocument9 paginiJFET Characteristics PDFSougata GhoshÎncă nu există evaluări

- Asynchronous Using D FlipflopDocument3 paginiAsynchronous Using D FlipflopSougata GhoshÎncă nu există evaluări

- Lamda Rules Layout TutorialDocument15 paginiLamda Rules Layout TutorialSougata GhoshÎncă nu există evaluări

- Montecarlo PDFDocument7 paginiMontecarlo PDFSougata GhoshÎncă nu există evaluări

- CCPastStatement03 12 2018 PDFDocument1 paginăCCPastStatement03 12 2018 PDFSougata GhoshÎncă nu există evaluări

- Quick Start PDFDocument1 paginăQuick Start PDFSougata GhoshÎncă nu există evaluări

- Quiz Basic ElectronicsDocument2 paginiQuiz Basic ElectronicsSougata GhoshÎncă nu există evaluări

- 7th LessonDocument54 pagini7th LessonSougata GhoshÎncă nu există evaluări

- IIT Kanpur L20 - Class - AB PDFDocument33 paginiIIT Kanpur L20 - Class - AB PDFSougata GhoshÎncă nu există evaluări

- Comm 03 Amplitude ModulationDocument47 paginiComm 03 Amplitude ModulationHazem Abu RamadanÎncă nu există evaluări

- 03amplitude ModulationDocument50 pagini03amplitude ModulationSougata GhoshÎncă nu există evaluări

- Chapter - 2Document14 paginiChapter - 2Sougata GhoshÎncă nu există evaluări

- SPLNPROC Word 2010-2016 Technical InstructionsDocument9 paginiSPLNPROC Word 2010-2016 Technical InstructionsMartín Montes RiveraÎncă nu există evaluări

- Akhbari Hosiyarpur PaperDocument8 paginiAkhbari Hosiyarpur PaperSougata GhoshÎncă nu există evaluări

- DESIGN of FIR FILTER Low Pass & High Pass FilterDocument4 paginiDESIGN of FIR FILTER Low Pass & High Pass FilterSougata GhoshÎncă nu există evaluări

- Chapter - 10Document20 paginiChapter - 10Sougata GhoshÎncă nu există evaluări

- 1501137243609Document2 pagini1501137243609Sougata Ghosh0% (1)

- Simulation Lab FileDocument42 paginiSimulation Lab FileSougata GhoshÎncă nu există evaluări

- Front PageDocument14 paginiFront PageSougata GhoshÎncă nu există evaluări

- IndexDocument4 paginiIndexSougata GhoshÎncă nu există evaluări

- How To Have A Healthy BabyDocument5 paginiHow To Have A Healthy BabySougata GhoshÎncă nu există evaluări

- Chapter - 3Document40 paginiChapter - 3Sougata Ghosh100% (1)

- New DSP LabDocument31 paginiNew DSP LabSougata GhoshÎncă nu există evaluări

- Chapter - 11Document48 paginiChapter - 11Sougata GhoshÎncă nu există evaluări

- Chapter - 1Document34 paginiChapter - 1Sougata GhoshÎncă nu există evaluări

- Chapter - 4Document58 paginiChapter - 4Sougata GhoshÎncă nu există evaluări

- Phrasal Verbs List PDFDocument20 paginiPhrasal Verbs List PDFNelly Vicky CruzÎncă nu există evaluări

- Question Bank Vlsi Technology Eec-604Document2 paginiQuestion Bank Vlsi Technology Eec-604Sougata Ghosh100% (1)

- Vlsi Technology 10 QuestionsDocument1 paginăVlsi Technology 10 QuestionsSougata GhoshÎncă nu există evaluări

- Vdocuments - MX Fender Performer 650 Guitar AmplifierDocument10 paginiVdocuments - MX Fender Performer 650 Guitar AmplifiermanchuricoÎncă nu există evaluări

- Subject Title: Analog Circuits Course Code: Year and Semester: II & IIDocument8 paginiSubject Title: Analog Circuits Course Code: Year and Semester: II & IIgiribabukandeÎncă nu există evaluări

- First Year First Semester 2015-16 Tutorial Sheet-1 Unit 1: Ans. I 0.75maDocument2 paginiFirst Year First Semester 2015-16 Tutorial Sheet-1 Unit 1: Ans. I 0.75maDr-Amit Kumar SinghÎncă nu există evaluări

- A Fully Differential Phase-Locked Loop With Reduced Loop Bandwidth VariationDocument248 paginiA Fully Differential Phase-Locked Loop With Reduced Loop Bandwidth Variationreshmii_123Încă nu există evaluări

- مكبرات العمليات PDFDocument55 paginiمكبرات العمليات PDFmahmoud DawoodÎncă nu există evaluări

- Design of 12-Bit DAC Using CMOS TechnologyDocument5 paginiDesign of 12-Bit DAC Using CMOS TechnologysanthoshÎncă nu există evaluări

- Servicing Class D Amplifiers: Harman Consumer GroupDocument24 paginiServicing Class D Amplifiers: Harman Consumer GroupSilomo-saka MambaÎncă nu există evaluări

- Ec II Q&A-Assign-6,10 Marks QuestionsDocument32 paginiEc II Q&A-Assign-6,10 Marks QuestionsJoshua Duffy100% (1)

- TDC-GPX An000512 1-00Document9 paginiTDC-GPX An000512 1-00अमरेश झाÎncă nu există evaluări

- Design and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)Document5 paginiDesign and Layout of 1.8V Two Stage CMOS Operational Amplifier (Unbuffered)sudarshan poojaryÎncă nu există evaluări

- Electronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CDocument11 paginiElectronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CSouban JavedÎncă nu există evaluări

- Phys 3102Document23 paginiPhys 3102myo htetÎncă nu există evaluări

- Integrated CircuitDocument160 paginiIntegrated Circuitpcjoshi02Încă nu există evaluări

- AmplifierDocument20 paginiAmplifierHua-Chien ChangÎncă nu există evaluări

- A Wide-Band CMOS LC VCO With Linearized Coarse Tuning CharacteristicsDocument5 paginiA Wide-Band CMOS LC VCO With Linearized Coarse Tuning CharacteristicsBasavaraj S KashappanavarÎncă nu există evaluări

- Ve Feed Back AmplifierDocument4 paginiVe Feed Back AmplifierAnonymous PAdtDAÎncă nu există evaluări

- Phase Locked Loop PLLDocument35 paginiPhase Locked Loop PLLenzuekÎncă nu există evaluări

- BJT SSAC-2spDocument30 paginiBJT SSAC-2spJoannaÎncă nu există evaluări

- Chapter 7 - CMOS AmplifiersDocument40 paginiChapter 7 - CMOS AmplifiersAsyraf NorahairuzanÎncă nu există evaluări

- Modelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Document7 paginiModelling of Operational Amplifier by Using CMOS Technology: VSRD-IJEECE, Vol. 2 (6), 2012, 330-336Akash VermaÎncă nu există evaluări

- Voltage Shunt Feedback AmplifierDocument4 paginiVoltage Shunt Feedback Amplifierersan turkmanÎncă nu există evaluări

- Chapter 3Document25 paginiChapter 3ARif HakimÎncă nu există evaluări

- Eca Ii Lab Manual Final PDFDocument65 paginiEca Ii Lab Manual Final PDFkapil chander100% (1)

- Tonepad - Smallclone PedalDocument2 paginiTonepad - Smallclone PedalArley GomesÎncă nu există evaluări

- 1500 Watt Peak Class AB Audio Power Amplifier For 2-Ohms Loudspeaker (Core) - Ver. Bc-I-1500-Ls2-2013, Rev. 2Document3 pagini1500 Watt Peak Class AB Audio Power Amplifier For 2-Ohms Loudspeaker (Core) - Ver. Bc-I-1500-Ls2-2013, Rev. 2SachinÎncă nu există evaluări

- 2 Inverting and Noninverting AmplifierDocument5 pagini2 Inverting and Noninverting Amplifiersureshy-ee213Încă nu există evaluări

- Chapter 7 UpdatedDocument32 paginiChapter 7 UpdatedWajahat KhanÎncă nu există evaluări

- REC 454 Advanced Electronics LabDocument1 paginăREC 454 Advanced Electronics LabAnonymous eWMnRr70qÎncă nu există evaluări

- Op AmpDocument22 paginiOp AmplolmanÎncă nu există evaluări

- Sallen Key FilterDocument11 paginiSallen Key FilterKenneth Raj KumarÎncă nu există evaluări

- A Pathway to Decarbonise the Shipping Sector by 2050De la EverandA Pathway to Decarbonise the Shipping Sector by 2050Încă nu există evaluări

- Fire on the Horizon: The Untold Story of the Gulf Oil DisasterDe la EverandFire on the Horizon: The Untold Story of the Gulf Oil DisasterÎncă nu există evaluări

- Introduction to Power System ProtectionDe la EverandIntroduction to Power System ProtectionEvaluare: 5 din 5 stele5/5 (1)

- Power of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesDe la EverandPower of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesEvaluare: 4.5 din 5 stele4.5/5 (21)

- RV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!De la EverandRV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!Încă nu există evaluări

- Offshore Wind Energy Generation: Control, Protection, and Integration to Electrical SystemsDe la EverandOffshore Wind Energy Generation: Control, Protection, and Integration to Electrical SystemsÎncă nu există evaluări

- Shorting the Grid: The Hidden Fragility of Our Electric GridDe la EverandShorting the Grid: The Hidden Fragility of Our Electric GridEvaluare: 4.5 din 5 stele4.5/5 (2)

- Nuclear Energy in the 21st Century: World Nuclear University PressDe la EverandNuclear Energy in the 21st Century: World Nuclear University PressEvaluare: 4.5 din 5 stele4.5/5 (3)

- Solar Power Demystified: The Beginners Guide To Solar Power, Energy Independence And Lower BillsDe la EverandSolar Power Demystified: The Beginners Guide To Solar Power, Energy Independence And Lower BillsEvaluare: 4.5 din 5 stele4.5/5 (2)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetDe la EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetEvaluare: 2 din 5 stele2/5 (1)

- Carbon Capture, Utilization, and Storage Game Changers in Asia: 2020 Compendium of Technologies and EnablersDe la EverandCarbon Capture, Utilization, and Storage Game Changers in Asia: 2020 Compendium of Technologies and EnablersEvaluare: 4.5 din 5 stele4.5/5 (2)

- The Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceDe la EverandThe Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceÎncă nu există evaluări

- ISO 50001: A strategic guide to establishing an energy management systemDe la EverandISO 50001: A strategic guide to establishing an energy management systemÎncă nu există evaluări

- Renewable Energy: A Very Short IntroductionDe la EverandRenewable Energy: A Very Short IntroductionEvaluare: 4.5 din 5 stele4.5/5 (12)

- Practical Reservoir Engineering and CharacterizationDe la EverandPractical Reservoir Engineering and CharacterizationEvaluare: 4.5 din 5 stele4.5/5 (3)

- The New 3D Layout for Oil & Gas Offshore Projects: How to ensure successDe la EverandThe New 3D Layout for Oil & Gas Offshore Projects: How to ensure successEvaluare: 4.5 din 5 stele4.5/5 (3)

- Live Off Grid: Escape The City, Learn How To Travel Intelligently Using Solar PowerDe la EverandLive Off Grid: Escape The City, Learn How To Travel Intelligently Using Solar PowerÎncă nu există evaluări

- Formulas and Calculations for Drilling OperationsDe la EverandFormulas and Calculations for Drilling OperationsÎncă nu există evaluări

- The Way Home: Tales from a life without technologyDe la EverandThe Way Home: Tales from a life without technologyEvaluare: 4 din 5 stele4/5 (45)

- Practical Methods for Analysis and Design of HV Installation Grounding SystemsDe la EverandPractical Methods for Analysis and Design of HV Installation Grounding SystemsEvaluare: 4.5 din 5 stele4.5/5 (2)

- Global Landscape of Renewable Energy FinanceDe la EverandGlobal Landscape of Renewable Energy FinanceÎncă nu există evaluări

- Fundamentals of Hydrogen Production and Utilization in Fuel Cell SystemsDe la EverandFundamentals of Hydrogen Production and Utilization in Fuel Cell SystemsÎncă nu există evaluări

- Electrical Load-Curve Coverage: Proceedings of the Symposium on Load-Curve Coverage in Future Electric Power Generating Systems, Organized by the Committee on Electric Power, United Nations Economic Commission for Europe, Rome, Italy, 24 – 28 October 1977De la EverandElectrical Load-Curve Coverage: Proceedings of the Symposium on Load-Curve Coverage in Future Electric Power Generating Systems, Organized by the Committee on Electric Power, United Nations Economic Commission for Europe, Rome, Italy, 24 – 28 October 1977Încă nu există evaluări

- Formulas and Calculations for Drilling, Production, and Workover: All the Formulas You Need to Solve Drilling and Production ProblemsDe la EverandFormulas and Calculations for Drilling, Production, and Workover: All the Formulas You Need to Solve Drilling and Production ProblemsÎncă nu există evaluări

- Recent Advances in Electrical Engineering: Applications OrientedDe la EverandRecent Advances in Electrical Engineering: Applications OrientedÎncă nu există evaluări

- Introduction to Power System ProtectionDe la EverandIntroduction to Power System ProtectionÎncă nu există evaluări

- Industrial Waste Treatment HandbookDe la EverandIndustrial Waste Treatment HandbookEvaluare: 5 din 5 stele5/5 (1)