Documente Academic

Documente Profesional

Documente Cultură

Final 4 DIGITALES

Încărcat de

DanielTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Final 4 DIGITALES

Încărcat de

DanielDrepturi de autor:

Formate disponibile

UNMSM.

Ventura Daniel, Leyva Rojas José, Tomohiko Inafuko

Simplificación de circuitos lógicos

Simplificación de circuitos lógicos

Ventura Vela Daniel, Leyva Rojas José , Tomohiko Inafuko Miyashiro

,dannfher.dl74va56.2@gmail,com,jaleyvarojas@gmail.com,

Facultad de Ingeniería Electrónica y Eléctrica – UNMSM

Resumen— El objetivo principal de la experiencia y el operador complemento o negación. Los

realizada fue estudiar las funciones lógicas del circuito maxtérminos son una expresión dual de los

digital, así mismo extraer de la tabla de verdad la mintérminos. En vez de usar operaciones

función respectiva e implementar la manera estándar AND utilizamos operaciones OR y

en la cual puede ser representado en sus 2 formas procedemos de forma similar.

canónicas: en la suma de productos (Mintérminos) y

producto de sumas (Maxtérminos). Así mismo con la

tabla de datos construir un mapa de Karnaugh para II. MATERIALES Y MÉTODOS

simplificar las ecuaciones.

A. Equipos, materiales y herramientas utilizadas

Una vez que se obtiene la expresión booleana para un

circuito lógico, podemos reducirla a una forma más Multímetro digital DC, Protoboard, MULTISIM,

simple que contenga menos términos, la nueva cocodrilos ,resistencias, jampers, integrados, y

expresión puede utilizarse para implantar un circuito cables de conexión.

que sea equivalente al original pero que contenga

menos compuertas y conexiones. B. Esquemas

Índice de Términos — Mapas de karnaugh,

minterminos, maxterminos,

I. INTRODUCCIÓN

En las funciones lógicas, los Mapas de Karnaugh son

una herramienta muy utilizada para la simplificación

de circuitos lógicos. Cuando se tiene una función

lógica con su tabla de verdad y se desea implementar

esa función de la manera más económica posible se

Fig. 1. Demostración de la tabla de verdad

utiliza este método.

Mintérminos:

Para una función booleana de n variables

x1,...xn, un producto booleano en el que cada

una de las n variables aparece una sola vez

(negada o sin negar). Es decir es una expresión

lógica de n variables consistente únicamente en

el operador con una conjunción lógica (AND) y el

operador complemento o negación (NOT).

El complemento de un mintérmino, es su respectivo

maxtérmino.

Fig. 2. Forma de solución de mapas de karnaugh

Maxtérminos:

Es una expresión lógica de ´n´ variables que

consisten únicamente en la disyunción lógica

UNMSM. Ventura Daniel, Leyva Rojas José, Tomohiko Inafuko

Simplificación de circuitos lógicos

Reduciendo por karnaugh: Hallamos los mintérminos:

Primero ubicamos los correspondientes ∑ 𝒎𝒊𝒏(𝟎, 𝟏, 𝟑, 𝟓, 𝟔, 𝟗, 𝟏𝟏, 𝟏𝟐, 𝟏𝟑, 𝟏𝟓)

mintérminos en el Mapa de Karnaugh. = 𝑨′ 𝑩′ 𝑪′ 𝑫′ + 𝑨′ 𝑩′ 𝑪′ 𝑫

Luego de ello agrupamos en grupos con + 𝑨′ 𝑩′ 𝑪𝑫 + 𝑨′ 𝑩𝑪′ 𝑫

potencia 2n, para lograr reducir la función + 𝑨′ 𝑩𝑪𝑫′ + 𝑨𝑩′ 𝑪′ 𝑫

lógica del circuito. + 𝑨𝑩′ 𝑪𝑫 + 𝑨𝑩𝑪′ 𝑫′

+ 𝑨𝑩𝑪′ 𝑫 + 𝑨𝑩𝑪𝑫

Finalmente usamos la propiedad del producto

de sumas de los mintérminos para llegar a

obtener la función simplificada del mismo. 𝒀 = 𝑨′ 𝑩𝑪𝑫′ + 𝑨′ 𝑩′ 𝑪′ + 𝑨𝑩𝑪′ + 𝑩′ 𝑫 + 𝑪′ 𝑫 + 𝑨𝑫

Fig. 3. Forma de solución de mapas de karnaugh

Fig. 5. Simulación del circuito simplificado

IV. ANÁLISIS DE RESULTADOS

Observamos en las gráficas mostradas

Fig. 4. Ejemplo de circuito simplificado previamente que hemos utilizamos diferentes

métodos para la simplificación de circuitos.

Encontramos una solución simplificada del

III. RESULTADOS circuito, a diferencia de la tabla de verdad,

éstos resultados nos indican que la función

Tabla 1 (Análisis en DC) puede ser simplificada sin necesidad del

álgebra de Boole.

Como podemos observar obtenemos una

salida que ahorra las compuertas que

innecesariamente son usadas en los resultados

de la tabla de verdad.

En el mapa de Karnaugh logramos simplificar

la tabla de verdad, usando los mintérminos en

vez de los maxtérminos, debido a que al

realizar la simplificación por medio de éstos,

nos encontramos con un mayor número de

UNMSM. Ventura Daniel, Leyva Rojas José, Tomohiko Inafuko

Simplificación de circuitos lógicos

ENTRADAS SALIDA

compuertas innecesarias, las cuales nos A B C D Y

dificultan la implementación del circuito TENS TENS TENS TENS TENS LED

GND GND GND GND ON

GND GND GND +5V ON

V. CONCLUSIONES GND GND +5V GND OFF

GND GND +5V +5V ON

GND +5V GND GND OFF

En el mapa de Karnaugh logramos GND +5V GND +5V ON

simplificar la tabla de verdad, usando los GND +5V +5V GND ON

mintérminos en vez de los Maxtérminos, GND +5V +5V +5V OFF

debido a que al realizar la simplificación +5V GND GND GND OFF

por medio de éstos, nos encontramos con +5V GND GND +5V ON

un mayor número de compuertas +5V GND +5V GND OFF

innecesarias, las cuales nos dificultan la +5V GND +5V +5V ON

implementación del circuito, lo cual +5V +5V GND GND ON

también saldría más costoso su +5V +5V GND +5V ON

implementación. +5V +5V +5V GND OFF

Con el mapa de karnaugh podemos +5V +5V +5V +5V ON

minimizar expresiones, las compuertas

lógicas.

Por eso debe considerarse el aprendizaje

de este método como una herramienta

importante en el estudio de informática y

electrónica entre otros.

VI. Bibliografía

[1 J. F. Vergaray, «Blogspot,» Independiente, [En

] línea]. Available:

http://jorgefloresvergaray.blogspot.com/2009/03/

usando-el-dual-opam-747.html. [Último acceso: 01

Junio 2018].

[2 R. Armijo, «Blogspot,» Independiente, 05 Marzo

] 2014. [En línea]. Available: http://rogger-

armijo.blogspot.com/2012/11/opam.html. [Último

acceso: 01 Junio 2018].

[3 StudyLib, «Studylib,» Independiente, [En línea].

] Available:

http://studylib.es/doc/5605589/amplificadores-

diferenciales-y-de-instrumentaci%C3%B3n.

[Último acceso: 01 Junio 2018].

S-ar putea să vă placă și

- Examen Final Comunicaciones MovilesDocument1 paginăExamen Final Comunicaciones MovilesDanielÎncă nu există evaluări

- PC 2Document11 paginiPC 2DanielÎncă nu există evaluări

- Arte Semana 23Document3 paginiArte Semana 23DanielÎncă nu există evaluări

- Matematica Semana 23Document7 paginiMatematica Semana 23DanielÎncă nu există evaluări

- Parte 2-Expo MandujanoDocument20 paginiParte 2-Expo MandujanoDanielÎncă nu există evaluări

- Cartel Sobrel A InclusionDocument1 paginăCartel Sobrel A InclusionDanielÎncă nu există evaluări

- Parcial BiomédicaDocument4 paginiParcial BiomédicaDanielÎncă nu există evaluări

- PC1 BiomédicaDocument4 paginiPC1 BiomédicaDanielÎncă nu există evaluări

- Primer Examen Parcial de Sistemas de Control 2Document5 paginiPrimer Examen Parcial de Sistemas de Control 2DanielÎncă nu există evaluări

- Reporte Parte 1-2Document2 paginiReporte Parte 1-2DanielÎncă nu există evaluări

- CyT Semana 23Document3 paginiCyT Semana 23DanielÎncă nu există evaluări

- CyT Semana 23 1 ParteDocument3 paginiCyT Semana 23 1 ParteDanielÎncă nu există evaluări

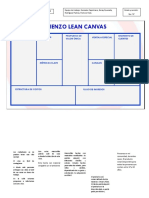

- Lienzo Lean CanvasDocument2 paginiLienzo Lean CanvasDanielÎncă nu există evaluări

- Fisica Semana 15Document6 paginiFisica Semana 15DanielÎncă nu există evaluări

- Arte Semana 20Document4 paginiArte Semana 20DanielÎncă nu există evaluări

- Arte Semana 19Document4 paginiArte Semana 19DanielÎncă nu există evaluări

- DPCC Semana 21Document4 paginiDPCC Semana 21DanielÎncă nu există evaluări

- Arbol GenealogicoDocument1 paginăArbol GenealogicoDanielÎncă nu există evaluări

- Religion Semana 21Document2 paginiReligion Semana 21DanielÎncă nu există evaluări

- Arte Semana 21Document5 paginiArte Semana 21DanielÎncă nu există evaluări

- E.D Fisica Semana 22Document5 paginiE.D Fisica Semana 22DanielÎncă nu există evaluări

- Arte Semana 22Document5 paginiArte Semana 22DanielÎncă nu există evaluări

- DPCC Semana 20Document2 paginiDPCC Semana 20DanielÎncă nu există evaluări

- DPCC Semana 22Document3 paginiDPCC Semana 22DanielÎncă nu există evaluări

- Tutoria Semana 23Document1 paginăTutoria Semana 23DanielÎncă nu există evaluări

- Semana 18 5dDocument4 paginiSemana 18 5dDanielÎncă nu există evaluări

- DPCC Semana 23Document4 paginiDPCC Semana 23DanielÎncă nu există evaluări

- CyT Semana 21Document5 paginiCyT Semana 21DanielÎncă nu există evaluări

- Declaración Jurada BolsistaDocument1 paginăDeclaración Jurada BolsistaDanielÎncă nu există evaluări

- Arte Semana 18Document3 paginiArte Semana 18DanielÎncă nu există evaluări

- Tensiones en Los Acordes y RearmonizacionDocument40 paginiTensiones en Los Acordes y RearmonizacionrafaelÎncă nu există evaluări

- Lab 8 ElectricaDocument8 paginiLab 8 ElectricaEdgardoÎncă nu există evaluări

- Diapo FinalesDocument48 paginiDiapo FinalesJose Gonzales100% (1)

- ALTERNADORDocument79 paginiALTERNADORmichael lobosÎncă nu există evaluări

- Taller Ciencia de Los MaterialesDocument18 paginiTaller Ciencia de Los MaterialesCarlos Mario Perez CastillaÎncă nu există evaluări

- Extracto Especificaciones Pares de Apriete (SSNR3130-15)Document14 paginiExtracto Especificaciones Pares de Apriete (SSNR3130-15)Hugo CiprianiÎncă nu există evaluări

- Guia de Problemas N 5Document5 paginiGuia de Problemas N 5Josue Isac Salomon LandaÎncă nu există evaluări

- Proyecto Formativo CalculoDocument9 paginiProyecto Formativo CalculoDayana Castro MendezÎncă nu există evaluări

- 37 - Tarea - Julio Cesar Palomino - Pensamiento Logico MatematicoDocument8 pagini37 - Tarea - Julio Cesar Palomino - Pensamiento Logico MatematicoJULIO CESAR PALOMINO M.Încă nu există evaluări

- Solución EjerciciosDocument7 paginiSolución EjerciciosDaniela Santander MezaÎncă nu există evaluări

- Marlon Quispe - Practica de SimulacionDocument16 paginiMarlon Quispe - Practica de SimulacionJorge VillanuevaÎncă nu există evaluări

- Silabo - EG118 - QUIMICA GENERALDocument5 paginiSilabo - EG118 - QUIMICA GENERALponc relaÎncă nu există evaluări

- Reseña Histórica Del Dibujo TécnicoDocument3 paginiReseña Histórica Del Dibujo TécnicolopezfeliciaÎncă nu există evaluări

- Planificación Diagnostico-1Document18 paginiPlanificación Diagnostico-1Karolina Tapia scalerandiÎncă nu există evaluări

- Wa0021.Document14 paginiWa0021.Sukigarm MmkÎncă nu există evaluări

- AMD Reporte Visita BoliviaDocument35 paginiAMD Reporte Visita Boliviaandy reyesÎncă nu există evaluări

- Monografia de Tratamientos Termico Del AceroDocument33 paginiMonografia de Tratamientos Termico Del AceroJonatanGalvanRojasÎncă nu există evaluări

- Medidas de Asimetria y CurtosisDocument8 paginiMedidas de Asimetria y CurtosisYojhan AbrilÎncă nu există evaluări

- Excel 302 Plantillas y FormulariosDocument10 paginiExcel 302 Plantillas y FormulariosJose VitorÎncă nu există evaluări

- Introducción A NTFSDocument14 paginiIntroducción A NTFSchubijonesÎncă nu există evaluări

- Practica Vbnet Con AccessDocument3 paginiPractica Vbnet Con AccessfranzepedacÎncă nu există evaluări

- Publicación 2Document1 paginăPublicación 2marlyn cajicaÎncă nu există evaluări

- Realizacion de U Examen Basico en US, Hoja de RutaDocument33 paginiRealizacion de U Examen Basico en US, Hoja de RutaLUZ ANDREA RAMOS RODASÎncă nu există evaluări

- Laboratorio de Actividad EnzimáticaDocument17 paginiLaboratorio de Actividad EnzimáticaMariaHelenaÎncă nu există evaluări

- Cambios físicos del aguaDocument4 paginiCambios físicos del aguaSedevalparaiso LicapeveÎncă nu există evaluări

- Fenoles propiedadesDocument4 paginiFenoles propiedadesOmegaÎncă nu există evaluări

- Teoria Curpuscular 3roDocument1 paginăTeoria Curpuscular 3roPAPELERIA CLIENTESÎncă nu există evaluări

- Unidad 3 Procesos de Cambio de FormaDocument26 paginiUnidad 3 Procesos de Cambio de FormaSamuel Sanchez67% (3)

- Laboratorio - Elaboracion de Pan Tipo FrancesDocument5 paginiLaboratorio - Elaboracion de Pan Tipo FrancesRoberto ArdónÎncă nu există evaluări