Documente Academic

Documente Profesional

Documente Cultură

Digital Circuits and Systems: Spring 2015 Week 9

Încărcat de

Sriram MuruganTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Digital Circuits and Systems: Spring 2015 Week 9

Încărcat de

Sriram MuruganDrepturi de autor:

Formate disponibile

Spring 2015 Week 9 Module 50

Digital Circuits and

Systems

Ripple Carry Adder

Shankar Balachandran*

Associate Professor, CSE Department

Indian Institute of Technology Madras

*Currently a Visiting Professor at IIT Bombay

Adders and Subtracters

The most basic arithmetic operation in a digital computer is

addition.

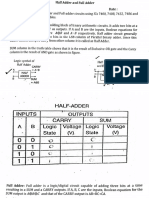

Half Adder is a combination circuit that performs addition of 2

bits.

Inputs Outputs

a b Carry Sum

0 0 0 0

Sum a b a b a b

0 1 0 1

Carry a b

1 0 0 1

1 1 1 0

Ripple Carry Adder 2

Half Adder

Sum a b a b a b

Carry a b

Half adders cannot accept a carry input and hence it is not possible

to cascade them to construct an n-bit binary adder.

Ripple Carry Adder 3

Full Adder

Full Adder is a combinational circuit that forms the arithmetic sum of

three input bits. It is described by the following truth table:

Inputs Outputs

c b a Cout Sum

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

Sum a b c a b c a b c a b c a b c

C out a b a c b c a b c a b

Ripple Carry Adder 4

Full Adder Implementation - 1

Sum a b c a b c a b c a b c a b c

C out a b a c b c a b c a b

ai bi

ai

si bi

Full

Adder

ci+1 ci

(FA)

ci+1

ci

Full Adder at bit i

si

Ripple Carry Adder 5

Full Adder Implementation - 2

A full adder can be implemented using 2 half adders and an OR gate

ai

si bi

ci+1 ci

ai bi

Full

Adder

ci+1 ci

(FA)

si

Ripple Carry Adder 6

Performance of a Full Adder

Use a 2-input NAND gate implementation of a 1-bit full adder.

Ripple Carry Adder 7

Ripple Carry Adder

4-bit Binary Adder: ( Sum = A + B )

A 4-bit binary adder can be implemented by cascading four 1-bit full

adders as follows:

Inputs: A = (a3a2a1a0) Outputs: Sum = (s3s2s1s0)

B = (b3b2b1b0) Cout = c4

Cin = cin = c0

Ripple Carry Adder 8

Performance of an n-bit Ripple Carry

Adder

Carry ripples from input co to output cn

Worst case propagation delay for sum in terms of 2-input NAND gate

delay (1 gd) is given by,

t sum 5 i 1 2 3 5 2n 2 3 2n 4

n 2

Worst case propagation delay for carry output is given by,

t carry delay for cn 1 2 5 ni12 2 2 2n 3

Therefore, propagation delay for an n-bit Ripple Carry Adder is O(n).

Ripple Carry Adder 9

Exercises

Design a signed comparator for comparing two 4-bit 1’s

complement numbers A and B

If A > B, the circuit should produce 1 as output, otherwise 0

Design a signed comparator for comparing two 4-bit 2’s

complement numbers A and B

If A > B, the circuit should produce 1 as output, otherwise 0

Design an n-bit absolute (ABS) value generator for 2’s

complement represented numbers, i.e., for an n-bit input,

X, the output is |X|

Ripple Carry Adder 10

End of Week 9: Module 50

Thank You

Ripple Carry Adder 11

S-ar putea să vă placă și

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDe la EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxEvaluare: 4 din 5 stele4/5 (2)

- L28 - 30 Arithmetic Circuits - AdderDocument69 paginiL28 - 30 Arithmetic Circuits - AdderMuhammad FaizanÎncă nu există evaluări

- Rangkaian AritmatikaDocument26 paginiRangkaian AritmatikaFarhan NurÎncă nu există evaluări

- Lecture 12Document37 paginiLecture 127t854s6wd2Încă nu există evaluări

- VLSI Arithmetic Lect 3Document30 paginiVLSI Arithmetic Lect 3Pratheep KumarÎncă nu există evaluări

- AdderDocument23 paginiAdderUsman ali KhanÎncă nu există evaluări

- Ripple Carry Adder, Full Adder Implementation Using Half AdderDocument22 paginiRipple Carry Adder, Full Adder Implementation Using Half AdderAdolf HitlarÎncă nu există evaluări

- Department of Ece Ec T45 - Digital Circuits Unit - 3Document41 paginiDepartment of Ece Ec T45 - Digital Circuits Unit - 3thiruct77Încă nu există evaluări

- Computer Organization and Architecture Lab DEEPAK KUMARDocument11 paginiComputer Organization and Architecture Lab DEEPAK KUMARAryan VermaÎncă nu există evaluări

- Ripple Carry Adder: Presented By: Aravindreddy M 18951A0582Document11 paginiRipple Carry Adder: Presented By: Aravindreddy M 18951A0582kpriya8687Încă nu există evaluări

- Experiment # 5 To Understand Combinational Circuit and ApplicationsDocument8 paginiExperiment # 5 To Understand Combinational Circuit and Applicationssyed waheedÎncă nu există evaluări

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pagini4 - Bit - Carry - Propagate - Adder PDFSubhajit DasÎncă nu există evaluări

- Adder MeenuDocument52 paginiAdder Meenunaidukoduru2002Încă nu există evaluări

- Chapter - 4part1adder DIGITAL ELECTRONICSDocument28 paginiChapter - 4part1adder DIGITAL ELECTRONICSNUR SYAFIQAH l UTHMÎncă nu există evaluări

- Deld Unit IIDocument87 paginiDeld Unit IIParth KourwarÎncă nu există evaluări

- شابتر4 الاولDocument64 paginiشابتر4 الاولمنار المالكيÎncă nu există evaluări

- Exp-Half and Full AdderDocument4 paginiExp-Half and Full Addergetthat100dkÎncă nu există evaluări

- Complete COA 2nd UnitDocument97 paginiComplete COA 2nd UnitishitaÎncă nu există evaluări

- Lecture 16 DLD 2017Document24 paginiLecture 16 DLD 2017shah hassanÎncă nu există evaluări

- Binary Adder-SubtractorDocument8 paginiBinary Adder-SubtractorNaima Naeem 631-FBAS/BSIT/F21Încă nu există evaluări

- DLLec7a NotesDocument5 paginiDLLec7a NotesChintan MandalÎncă nu există evaluări

- Lab 06Document4 paginiLab 06AafaqIqbalÎncă nu există evaluări

- Analysis and Design of Combinational Logic CirciutsDocument74 paginiAnalysis and Design of Combinational Logic CirciutsMS RahilÎncă nu există evaluări

- Dr. Praveen Kumar: School of Electronics Engineering (SENSE) VIT-AP University E-MailDocument25 paginiDr. Praveen Kumar: School of Electronics Engineering (SENSE) VIT-AP University E-MailrerereÎncă nu există evaluări

- Full Adder: A Full Adder Can Be Made From Two Half Adders (Plus An OR Gate)Document13 paginiFull Adder: A Full Adder Can Be Made From Two Half Adders (Plus An OR Gate)Rachana GadeÎncă nu există evaluări

- Binary Arithmetic and Arithmetic Circuits-2Document22 paginiBinary Arithmetic and Arithmetic Circuits-2Monika SharmaÎncă nu există evaluări

- Unit-3 STLDDocument85 paginiUnit-3 STLDShashank SaiÎncă nu există evaluări

- Arithmetic Circuits: COMP541Document36 paginiArithmetic Circuits: COMP541danya314Încă nu există evaluări

- DLD Exe-3 - Design of Adder CircuitDocument5 paginiDLD Exe-3 - Design of Adder CircuitskrÎncă nu există evaluări

- XOR, XNOR, & Binary Adders: Digital ElectronicsDocument19 paginiXOR, XNOR, & Binary Adders: Digital ElectronicsGeorge HughesÎncă nu există evaluări

- Digital Logic & Processors: Design Concepts of ALU: Arithmetic FunctionsDocument23 paginiDigital Logic & Processors: Design Concepts of ALU: Arithmetic Functionskoppuravuri kusumaÎncă nu există evaluări

- Combinational CircuitsDocument24 paginiCombinational CircuitsRaja VidyaÎncă nu există evaluări

- Chapter 3 OnlyFor Q39 and ProblemNo 9Document32 paginiChapter 3 OnlyFor Q39 and ProblemNo 9fahim faisalÎncă nu există evaluări

- ECEG3101-LC-Lec - 07 - Adders Comparators Decoders Encoders-1Document36 paginiECEG3101-LC-Lec - 07 - Adders Comparators Decoders Encoders-1Tsinat WondimuÎncă nu există evaluări

- Cs3351-Dpco Lab ManualDocument42 paginiCs3351-Dpco Lab Manual19UBCA105 SASIREKA A100% (2)

- DPCO Record - Final - Page NumberDocument53 paginiDPCO Record - Final - Page NumbernietjrajichellamÎncă nu există evaluări

- 08 CA (Constructing+an+ALU)Document17 pagini08 CA (Constructing+an+ALU)Royal StarsÎncă nu există evaluări

- Adder CircuitsDocument26 paginiAdder CircuitsAnkur JhaÎncă nu există evaluări

- Chapter 6 Combinational Logic - Mod-3Document67 paginiChapter 6 Combinational Logic - Mod-3Raghdan TarabayÎncă nu există evaluări

- Adder Subtractor DLDDocument26 paginiAdder Subtractor DLDabcabc999Încă nu există evaluări

- Introduction To VLSI Circuits and SystemsDocument31 paginiIntroduction To VLSI Circuits and SystemsraviÎncă nu există evaluări

- Lecture 5 - Functions of Combinational Logic CircuitDocument71 paginiLecture 5 - Functions of Combinational Logic CircuitDoctor Care100% (1)

- 2EL11-Digital Electronic - Adder and Flip-Flop Circuits: Pusat Pengajian Sains Fizik Universiti Sains MalaysiaDocument8 pagini2EL11-Digital Electronic - Adder and Flip-Flop Circuits: Pusat Pengajian Sains Fizik Universiti Sains MalaysiaCogCoilÎncă nu există evaluări

- Question 6 Assignment-DigitalDocument3 paginiQuestion 6 Assignment-DigitalVictor PrestonÎncă nu există evaluări

- XOR, XNOR, and Binary Adders: © 2014 Project Lead The Way, Inc. Digital ElectronicsDocument19 paginiXOR, XNOR, and Binary Adders: © 2014 Project Lead The Way, Inc. Digital ElectronicsGeorge HughesÎncă nu există evaluări

- Half Adder N Full AdderDocument4 paginiHalf Adder N Full AdderRock MaheshÎncă nu există evaluări

- ch04 Part 2Document17 paginich04 Part 2Zainab KadhemÎncă nu există evaluări

- Functions of Combinational Logic NotesDocument21 paginiFunctions of Combinational Logic NotesAbdullah AftabÎncă nu există evaluări

- Combinational Logic: Md. Nagrul Islam Lecturer Cse, MecDocument47 paginiCombinational Logic: Md. Nagrul Islam Lecturer Cse, MecIzaz Uddin MahmudÎncă nu există evaluări

- DLD Lab Report 4Document6 paginiDLD Lab Report 4Talha TufailÎncă nu există evaluări

- Digital Circuit - 2.1Document4 paginiDigital Circuit - 2.1Utkarsh ShuklaÎncă nu există evaluări

- Digital System Topic 4aDocument37 paginiDigital System Topic 4aAini Hafizah Mohd SaodÎncă nu există evaluări

- Experiment No - Ripple Carry Full AdderDocument3 paginiExperiment No - Ripple Carry Full AdderNikhil PawarÎncă nu există evaluări

- Expt. 03 DLD - UTPALDocument6 paginiExpt. 03 DLD - UTPALLobhas sangaiÎncă nu există evaluări

- De - Unit-4 - Combinational Circuits-1 PDFDocument60 paginiDe - Unit-4 - Combinational Circuits-1 PDFJohn ShahÎncă nu există evaluări

- Digital Electronics Chapter 6Document38 paginiDigital Electronics Chapter 6Pious TraderÎncă nu există evaluări

- 8.1 Adders: Chapter EightDocument24 pagini8.1 Adders: Chapter EightkalaiyarasiÎncă nu există evaluări

- Complete Note Chapter 4Document72 paginiComplete Note Chapter 4ram5nath-3Încă nu există evaluări

- COA Module - 4Document43 paginiCOA Module - 4shashidh1234Încă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- tmp59900 PDFDocument2 paginitmp59900 PDFSriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Writing A Review Paper: Abd Karim Alias@2010Document44 paginiWriting A Review Paper: Abd Karim Alias@2010Sriram MuruganÎncă nu există evaluări

- Format For A Review Paper (Attach To F204)Document1 paginăFormat For A Review Paper (Attach To F204)Ankita BhardwajÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- tmp60624 PDFDocument2 paginitmp60624 PDFSriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- DDDocument2 paginiDDSriram MuruganÎncă nu există evaluări

- CH 02Document46 paginiCH 02Diera Sakura NadiaÎncă nu există evaluări

- Lec10 PDFDocument21 paginiLec10 PDFSriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- A Set 7Document17 paginiA Set 7majid4uonlyÎncă nu există evaluări

- tmp59890 PDFDocument2 paginitmp59890 PDFSriram MuruganÎncă nu există evaluări

- BinomialDocument2 paginiBinomialhmi1748951Încă nu există evaluări

- tmp60027 PDFDocument2 paginitmp60027 PDFSriram MuruganÎncă nu există evaluări

- Fundamentals of Artificial IntelligenceDocument1 paginăFundamentals of Artificial IntelligenceSriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740gova6bargurÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Fundamentals of Artificial IntelligenceDocument1 paginăFundamentals of Artificial IntelligenceSriram MuruganÎncă nu există evaluări

- Daily Eng Ref TablesDocument26 paginiDaily Eng Ref TablesPalaÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Nozzle 1Document3 paginiNozzle 1Sriram MuruganÎncă nu există evaluări

- Phone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Document2 paginiPhone:-Director Office FAX WWW - Kerala.gov - in 0471-2305230 0471-2305193 0471-2301740Sriram MuruganÎncă nu există evaluări

- Profile of The Aerospace Industry in Greater MontrealDocument48 paginiProfile of The Aerospace Industry in Greater Montrealvigneshkumar rajanÎncă nu există evaluări

- ASSA ABLOY - Digital Cam LocksDocument12 paginiASSA ABLOY - Digital Cam LocksSales Project 2 VCPÎncă nu există evaluări

- Sports Collection CatalogueDocument31 paginiSports Collection CataloguesitarazmiÎncă nu există evaluări

- Micronta 12VDC Power Adapter 273-1653A InstructionsDocument2 paginiMicronta 12VDC Power Adapter 273-1653A Instructions240GL guyÎncă nu există evaluări

- Alexandria University Faculty of Engineering: Electromechanical Engineering Sheet 1 (Synchronous Machine)Document5 paginiAlexandria University Faculty of Engineering: Electromechanical Engineering Sheet 1 (Synchronous Machine)Mahmoud EltawabÎncă nu există evaluări

- Server Side - Java - Using Rmi With Apache JservDocument16 paginiServer Side - Java - Using Rmi With Apache JservTotoAlipioÎncă nu există evaluări

- INDUSTRIAL LUBRICANTS-misr Petroleum PDFDocument17 paginiINDUSTRIAL LUBRICANTS-misr Petroleum PDFIslam FawzyÎncă nu există evaluări

- Mouse 200Document2 paginiMouse 200Amjad AliÎncă nu există evaluări

- Acoples Hidraulicos Serie 60 ParkerDocument2 paginiAcoples Hidraulicos Serie 60 ParkerAntonio MoralesÎncă nu există evaluări

- DataDocument4 paginiDataQuế SươngÎncă nu există evaluări

- Quotation For Blue Star Printek From Boway2010 (1) .09.04Document1 paginăQuotation For Blue Star Printek From Boway2010 (1) .09.04Arvin Kumar GargÎncă nu există evaluări

- How To Size Hydropneumatic TankDocument3 paginiHow To Size Hydropneumatic TankfelipeÎncă nu există evaluări

- ICT Css NotesDocument11 paginiICT Css NotesWinnie OoiÎncă nu există evaluări

- Power Network Telecommunication: Powerlink - Technical DataDocument10 paginiPower Network Telecommunication: Powerlink - Technical Datawas00266Încă nu există evaluări

- Online Technical Writing - Progress ReportsDocument9 paginiOnline Technical Writing - Progress ReportstimordiliÎncă nu există evaluări

- Test Procedure and MethodDocument1 paginăTest Procedure and MethodkmiqdÎncă nu există evaluări

- Times of India - Supply Chain Management of Newspapers and MagazinesDocument18 paginiTimes of India - Supply Chain Management of Newspapers and MagazinesPravakar Kumar33% (3)

- 5 CombiflameDocument8 pagini5 CombiflamenitantharaniÎncă nu există evaluări

- LIVING IN THE IT ERA (Introduction)Document9 paginiLIVING IN THE IT ERA (Introduction)johnnyboy.galvanÎncă nu există evaluări

- The Impact of Greed On Academic Medicine and Patient CareDocument5 paginiThe Impact of Greed On Academic Medicine and Patient CareBhawana Prashant AgrawalÎncă nu există evaluări

- K60-HSS Install GuideDocument2 paginiK60-HSS Install GuidedakidofdaboomÎncă nu există evaluări

- The Role of Social Media and Its Implication On Economic Growth On Society in IndiaDocument3 paginiThe Role of Social Media and Its Implication On Economic Growth On Society in IndiaSara EmamiÎncă nu există evaluări

- Long+term+storage+procedure 1151enDocument2 paginiLong+term+storage+procedure 1151enmohamadhakim.19789100% (1)

- Capitulo 9 - Flujo de DatosDocument24 paginiCapitulo 9 - Flujo de DatosOrlando Espinoza ZevallosÎncă nu există evaluări

- Estimation and Costing by M Chakraborty PDFDocument4 paginiEstimation and Costing by M Chakraborty PDFAakash Kamthane0% (3)

- Installation of Water HeatersDocument5 paginiInstallation of Water HeatersLaura KurniawanÎncă nu există evaluări

- Reynolds EqnDocument27 paginiReynolds EqnSuman KhanalÎncă nu există evaluări

- Wind Energy: by Kushagra JainDocument16 paginiWind Energy: by Kushagra JainAkash TalekarÎncă nu există evaluări

- 9500MPR - MEF8 Circuit Emulation ServicesDocument5 pagini9500MPR - MEF8 Circuit Emulation ServicesedderjpÎncă nu există evaluări

- Transition SignalsDocument10 paginiTransition Signalshana nixmaÎncă nu există evaluări