Documente Academic

Documente Profesional

Documente Cultură

AM4825P

Încărcat de

AlejandroVCMXDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

AM4825P

Încărcat de

AlejandroVCMXDrepturi de autor:

Formate disponibile

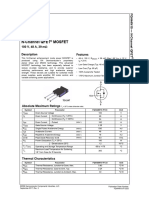

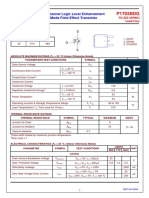

Analog Power AM4825P

P-Channel 30-V (D-S) MOSFET

These miniature surface mount MOSFETs utilize a

PRODUCT SUMMARY

high cell density trench process to provide low

rDS(on) and to ensure minimal power loss and heat VDS (V) rDS(on) m(Ω) ID (A)

dissipation. Typical applications are DC-DC 13 @ VGS = -10V -11.5

converters and power management in portable and -30

battery-powered products such as computers, 19 @ VGS = -4.5V -9.3

printers, PCMCIA cards, cellular and cordless

telephones.

• Low rDS(on) provides higher efficiency and

1 8

extends battery life

2 7

• Low thermal impedance copper leadframe

SOIC-8 saves board space 3 6

• Fast switching speed 4 5

• High performance trench technology

o

ABSOLUTE MAXIMUM RATINGS (TA = 25 C UNLESS OTHERWISE NOTED)

Parameter Symbol Maximum Units

Drain-Source Voltage VDS -30

V

Gate-Source Voltage VGS ±25

o

a TA=25 C -11.5

Continuous Drain Current o

ID

TA=70 C -9.3 A

b

Pulsed Drain Current IDM ±50

a

Continuous Source Current (Diode Conduction) IS -2.1 A

o

a TA=25 C 3.1

Power Dissipation o

PD W

TA=70 C 2.3

o

Operating Junction and Storage Temperature Range TJ, Tstg -55 to 150 C

THERMAL RESISTANCE RATINGS

Parameter Symbol Maximum Units

a o

Maximum Junction-to-Case t <= 5 sec RθJC 25 C/W

a o

Maximum Junction-to-Ambient t <= 5 sec RθJA 50 C/W

Notes

a. Surface Mounted on 1” x 1” FR4 Board.

b. Pulse width limited by maximum junction temperature

1 Publication Order Number:

PRELIMINARY DS-AM4825_F

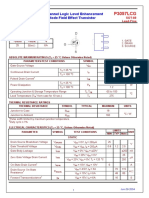

Analog Power AM4825P

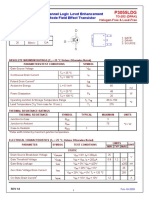

SPECIFICATIONS (T A = 25oC UNLESS OTHERWISE NOTED)

Limits

Parameter Symbol Test Conditions Unit

Min Typ Max

Static

Drain-Source Breakdown Voltage V(BR)DSS VGS = 0 V, ID = -250 uA -30

V

Gate-Threshold Voltage VGS(th) VDS = VGS, ID = -250 uA -1

Gate-Body Leakage IGSS VDS = 0 V, VGS = ±25 V ±100 nA

VDS = -24 V, VGS = 0 V -1

Zero Gate Voltage Drain Current IDSS o

uA

VDS = -24 V, VGS = 0 V, TJ = 55 C -5

A

On-State Drain Current ID(on) VDS = -5 V, VGS = -10 V -50 A

A VGS = -10 V, ID = -11.5 A 13

Drain-Source On-Resistance rDS(on) mΩ

VGS = -4.5 V, ID = -9.3 A 19.0

A

Forward Tranconductance gfs VDS = -15 V, ID = -11.5 A 29 S

Diode Forward Voltage VSD IS = 2.5 A, VGS = 0 V -0.8 V

b

Dynamic

Total Gate Charge Qg 64

VDS = -15 V, VGS = -10 V,

Gate-Source Charge Qgs 11 nC

ID = -11.5 A

Gate-Drain Charge Qgd 17

Input Capacitance Ciss 2300

Output Capacitance Coss VDS=-15V, VGS=0V, f=1MHz 600 pF

Reverse Transfer Capacitance Crss 300

Turn-On Delay Time td(on) 15

Rise Time tr VDD = -15 V, RL = 6 Ω , ID 13

nS

Turn-Off Delay Time td(off) = -1 A, VGEN = -10 V 100

Fall-Time tf 54

Notes

a. Pulse test: PW <= 300us duty cycle <= 2%.

b. Guaranteed by design, not subject to production testing.

Analog Power (APL) reserves the right to make changes without further notice to any products herein. APL makes no warranty, representation

or guarantee regarding the suitability of its products for any particular purpose, nor does APL assume any liability arising out of the application or

use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental

damages. “Typical” parameters which may be provided in APL data sheets and/or specifications can and do vary in different applications and

actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by

customer’s technical experts. APL does not convey any license under its patent rights nor the rights of others. APL products are not designed,

intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or

sustain life, or for any other application in which the failure of the APL product could create a situation where personal injury or death may occur.

Should Buyer purchase or use APL products for any such unintended or unauthorized application, Buyer shall indemnify and hold APL and its

officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney

fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such

claim alleges that APL was negligent regarding the design or manufacture of the part. APL is an Equal Opportunity/Affirmative Action Employer.

2 Publication Order Number:

PRELIMINARY DS-AM4825_F

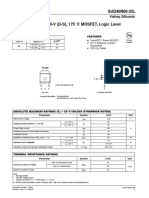

Analog Power AM4825P

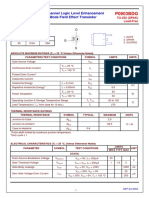

Typical Electrical Characteristics (P-Channel)

-5 0 0.03

4 V thru 1 0 v

-4 0 0.026

3 .5 V

(Ω)

-3 0 0.022

Vgs = 4.5V

-2 0 0.018

3V

Vgs = 10V

R

0.014

-1 0 2 .5 V

0 0.01

0 -1 -2 -3 0 -4 -8 -12 -16 -20

ID - Drain Current (A)

VDS - Dra in to S o urc e Vo lta ge (V)

Figure 2. On-Resistance Variation with

Figure 1. On-Region Characteristics Drain Current and Gate Voltage

1.6

0 .0 5

1.5 VGS =10V

Normalized RDS (on)

1.4 ID =11.5A 0 .0 4

1.3

(Ω)

1.2 0 .0 3

1.1

1.0

ID = 1 1 .5 a

0 .0 2

0.9

R

0.8 0 .0 1

0.7

0.6 0

-50 -25 0 25 50 75 100 125 150 0

Figure 6. Body 2 Forward

Diode 4 6

Voltage 8 10

Variation

T J - Juncation T emperature (ºC) with SourceVGS - Gate

Current and to Source Voltage

Temperature (V)

Figure 3. On-Resistance Variation with Temperature Figure 4. On-Resistance with Gate to Source Voltage

100 -50

25C

-40

I - Drain Current (A)

125C

IS - Source Current (A)

-55C

10

TJ = 150°C -30

-20

TJ = 25°C

1

-10

0

0.1 0 -1 -2 -3 -4 -5

0 0.2 0.4 0.6 0.8 1 1.2 VGS - Gate to Source Voltage (V)

VSD - Source to Drain Current (V)

Figure 5. Transfer Characteristics Figure 6. Body Diode Forward Voltage Variation

with Source Current and Temperature

3 Publication Order Number:

PRELIMINARY DS-AM4825_F

Analog Power AM4825P

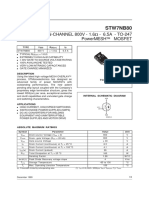

Typical Electrical Characteristics (P-Channel)

4000

10

VDS = 10V

VGS Gate to Source Voltage (V)

8

CISS

Capacit ance (pF)

3000

6

2000

4

CRSS COSS

2 1000

0

0

0 10 20 30 40 50 0 -5 -1 0 -1 5 -2 0

QGS, T otal Gate Charge (nC) VDS (V)

Figure 7. Gate Charge Characteristics Figure 8. Capacitance Characteristics

0.8

50

45

0.6

Variance (V)

40

0.4 35

30

Power (W)

0.2

25

0 20

15

-0.2

V

10

-0.4 5

-50 -25 0 25 50 75 100 125 150 0

T J - Juncation T emperature (ºC) 0.01 0.1 1 10 100 1000

Pulse T ime (S)

Figure 9. Maximum Safe Operating Area

Figure 10. Single Pulse Maximum Power Dissipation

Normalized Thermal Transient Junction to Ambient

1

0.5

0.2

P DM

0.1

0.1 t1

0.05

t2

0.02 1. Duty Cycal D = t1/t2

2. Per Unit Base RθJ A =70C/W

3. TJ M - TA = PDM Zθjc

Single Pulse

4. Sureface Mounted

0.01

0.0001 0.001 0.01 0.1 1 10 100 1000

Square Wave Pulse Duration (S)

Figure 11. Transient Thermal Response Curve

4 Publication Order Number:

PRELIMINARY DS-AM4825_F

Analog Power AM4825P

Package Information

SO-8: 8LEAD

H x 45°

5 Publication Order Number:

PRELIMINARY DS-AM4825_F

S-ar putea să vă placă și

- AM4407PE Analog Power P-Channel 30-V (D-S) MOSFET: 9 at V - 10V - 15 13 at V - 4.5V - 11 - 30Document3 paginiAM4407PE Analog Power P-Channel 30-V (D-S) MOSFET: 9 at V - 10V - 15 13 at V - 4.5V - 11 - 30jose4445Încă nu există evaluări

- AM4835P Analog Power P-Channel 30-V (D-S) MOSFET: 19 at V - 10V - 9.5 30 at V - 4.5V - 7.5 - 30Document6 paginiAM4835P Analog Power P-Channel 30-V (D-S) MOSFET: 19 at V - 10V - 9.5 30 at V - 4.5V - 7.5 - 30kevin XmxÎncă nu există evaluări

- DS Am4410n F1 PDFDocument5 paginiDS Am4410n F1 PDFmad saniÎncă nu există evaluări

- Am 4825 PeDocument3 paginiAm 4825 PeMafia BetawiÎncă nu există evaluări

- AM4512C Analog Power P & N-Channel 30-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryDocument8 paginiAM4512C Analog Power P & N-Channel 30-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryAtlantis GuadalupeÎncă nu există evaluări

- AM4910N Analog Power Dual N-Channel 30-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryDocument6 paginiAM4910N Analog Power Dual N-Channel 30-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryRanfis Rojas BorgesÎncă nu există evaluări

- AM7331P Analog Power P-Channel 30-V (D-S) MOSFET: 13 at V - 10V - 13.4 19 at V - 4.5V - 11.1 - 30Document5 paginiAM7331P Analog Power P-Channel 30-V (D-S) MOSFET: 13 at V - 10V - 13.4 19 at V - 4.5V - 11.1 - 30Rafael FernándezÎncă nu există evaluări

- AM7202N Analog Power N-Channel 200-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryDocument3 paginiAM7202N Analog Power N-Channel 200-V (D-S) MOSFET: V (V) R M ( ) I (A) Product SummaryVikinguddin AhmedÎncă nu există evaluări

- Datasheet - HK mc4422 6457294Document5 paginiDatasheet - HK mc4422 6457294Mario Rosas VargasÎncă nu există evaluări

- AMD540CE Analog Power P & N-Channel 40-V (D-S) MOSFETDocument7 paginiAMD540CE Analog Power P & N-Channel 40-V (D-S) MOSFETbünyamin altunÎncă nu există evaluări

- P - Channel Power MOSFE: SI2305DSDocument6 paginiP - Channel Power MOSFE: SI2305DSRomer NORIEGAÎncă nu există evaluări

- WPM 2341Document9 paginiWPM 2341veronicaÎncă nu există evaluări

- VBsemi-Elec-FR120N C879050Document7 paginiVBsemi-Elec-FR120N C879050Truong Dang VinhÎncă nu există evaluări

- Data SheetDocument8 paginiData SheetSuyash SuyashÎncă nu există evaluări

- AOD4 04 / MCD4 04 Freescale: V (V) R M ( ) I (A) Product SummaryDocument3 paginiAOD4 04 / MCD4 04 Freescale: V (V) R M ( ) I (A) Product SummaryLudmila MilaÎncă nu există evaluări

- MDF9N50F MagnaChipDocument6 paginiMDF9N50F MagnaChipchokÎncă nu există evaluări

- P YYBAGGlzi CAGQg IABd EWcg 9 MW I206Document7 paginiP YYBAGGlzi CAGQg IABd EWcg 9 MW I206intemenmenÎncă nu există evaluări

- Buz71A: N - Channel 50V - 0.1 - 13A To-220 Stripfet Power MosfetDocument8 paginiBuz71A: N - Channel 50V - 0.1 - 13A To-220 Stripfet Power Mosfetbugy costyÎncă nu există evaluări

- MDD7N25Document6 paginiMDD7N25José Manuel Izea NavarroÎncă nu există evaluări

- p3055ldg NikoDocument4 paginip3055ldg NikoАлексей ГомоновÎncă nu există evaluări

- Mosfet Original P75N02LDGDocument3 paginiMosfet Original P75N02LDGRisoSilvaÎncă nu există evaluări

- P2610ADG Niko-Sem: N-Channel Enhancement Mode Field Effect TransistorDocument6 paginiP2610ADG Niko-Sem: N-Channel Enhancement Mode Field Effect Transistormhmd193Încă nu există evaluări

- P0903BSG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 paginiP0903BSG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorAndika WicaksanaÎncă nu există evaluări

- Pa102fdg Mos PDocument5 paginiPa102fdg Mos PValentinÎncă nu există evaluări

- p0903bdg Mosfet PC PDFDocument5 paginip0903bdg Mosfet PC PDFvictor muñozÎncă nu există evaluări

- VBsemi-Elec-D10PF06 C879157Document8 paginiVBsemi-Elec-D10PF06 C879157dedy supriÎncă nu există evaluări

- SSH9N80ADocument7 paginiSSH9N80AJose CastellanosÎncă nu există evaluări

- N - Channel 500V - 2.5 - 2.5 A - To-220 Powermesh Mosfet: DescriptionDocument8 paginiN - Channel 500V - 2.5 - 2.5 A - To-220 Powermesh Mosfet: Description田忠勇Încă nu există evaluări

- Stp40Nf03L: N - Channel 30V - 0.020 - 40A To-220 Stripfet Power MosfetDocument8 paginiStp40Nf03L: N - Channel 30V - 0.020 - 40A To-220 Stripfet Power MosfetsuppoÎncă nu există evaluări

- AONR21357 ReemplazoDocument6 paginiAONR21357 ReemplazoDavid Enrique Rivero CahuichÎncă nu există evaluări

- WSNC 90 ZDocument8 paginiWSNC 90 ZCarlos Ben AdonayÎncă nu există evaluări

- SUM110N03-03P N-Channel 30-V (D-S) 175 - C MOSFET: Vishay SiliconixDocument6 paginiSUM110N03-03P N-Channel 30-V (D-S) 175 - C MOSFET: Vishay SiliconixJarekÎncă nu există evaluări

- Datasheet STP3NB100 Mosfet N IndigoDocument6 paginiDatasheet STP3NB100 Mosfet N Indigopepemex3Încă nu există evaluări

- P1703BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 paginiP1703BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistorserrano.flia.coÎncă nu există evaluări

- tsm4425 A09Document6 paginitsm4425 A09خليل الحريريÎncă nu există evaluări

- General Description Product Summary: 30V P-Channel MOSFETDocument5 paginiGeneral Description Product Summary: 30V P-Channel MOSFETteranet tbtÎncă nu există evaluări

- P2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 paginiP2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistorserrano.flia.coÎncă nu există evaluări

- Data SheetDocument4 paginiData SheetVibhor KumarÎncă nu există evaluări

- Huf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetDocument7 paginiHuf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetJose cuelloÎncă nu există evaluări

- MDD1752Document7 paginiMDD1752Homer Sadych Henao MarinÎncă nu există evaluări

- TSM060NB06CZ: Taiwan SemiconductorDocument6 paginiTSM060NB06CZ: Taiwan Semiconductorn tanevarÎncă nu există evaluări

- General Description Product Summary: 30V P-Channel MOSFETDocument6 paginiGeneral Description Product Summary: 30V P-Channel MOSFETmagentaÎncă nu există evaluări

- SFR/U2955: Advanced Power MOSFETDocument7 paginiSFR/U2955: Advanced Power MOSFETStuxnetÎncă nu există evaluări

- SQ2362ES: Vishay SiliconixDocument11 paginiSQ2362ES: Vishay SiliconixMantasPuskoriusÎncă nu există evaluări

- MDP18N50: N-Channel MOSFET 500V, 18.0 A, 0.27Document6 paginiMDP18N50: N-Channel MOSFET 500V, 18.0 A, 0.27gabriel SantosÎncă nu există evaluări

- General Description Product Summary: 30V P-Channel MOSFETDocument6 paginiGeneral Description Product Summary: 30V P-Channel MOSFETluis alberto perez monteroÎncă nu există evaluări

- P3057LCG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument4 paginiP3057LCG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistorlepicane7Încă nu există evaluări

- Data Sheet: N-Channel Enhancement Mode MOS TransistorDocument8 paginiData Sheet: N-Channel Enhancement Mode MOS TransistorArgenis VeraÎncă nu există evaluări

- Datasheet 7Document7 paginiDatasheet 7luis figuerasÎncă nu există evaluări

- N - Channel 50V - 0.03 - 30A - To-220 Stripfet Power MosfetDocument6 paginiN - Channel 50V - 0.03 - 30A - To-220 Stripfet Power MosfetSergio MartínezÎncă nu există evaluări

- P1203BV Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 paginiP1203BV Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorMalith UdayangaÎncă nu există evaluări

- SUD50N10-18P: Vishay SiliconixDocument10 paginiSUD50N10-18P: Vishay SiliconixWalter CzyzyniewskiÎncă nu există evaluări

- Stb19Nb20: N - Channel Enhancement Mode Powermesh MosfetDocument8 paginiStb19Nb20: N - Channel Enhancement Mode Powermesh Mosfetadfa9Încă nu există evaluări

- SUD50N024-09P: Vishay SiliconixDocument5 paginiSUD50N024-09P: Vishay SiliconixOirã Vinícius Moreira de OliveiraÎncă nu există evaluări

- AP0503GMT-HF DatasheetDocument4 paginiAP0503GMT-HF DatasheetAisya NurcahyaÎncă nu există evaluări

- SUD40N06-25L: Vishay SiliconixDocument6 paginiSUD40N06-25L: Vishay SiliconixFahd AfifiÎncă nu există evaluări

- TSM900N06: 60V N-Channel Power MOSFETDocument8 paginiTSM900N06: 60V N-Channel Power MOSFETshounakroyÎncă nu există evaluări

- IRFS630A - N CH, Power MOSFET 200V, 6.5A 25ºC, 4.1A 100ºC, 4v Vgs (TH)Document8 paginiIRFS630A - N CH, Power MOSFET 200V, 6.5A 25ºC, 4.1A 100ºC, 4v Vgs (TH)LangllyÎncă nu există evaluări

- N - Channel 50V - 0.085 - 17A To-220 Stripfet Power MosfetDocument9 paginiN - Channel 50V - 0.085 - 17A To-220 Stripfet Power MosfetFarid BakaÎncă nu există evaluări

- 1458888260Document19 pagini1458888260cristiÎncă nu există evaluări

- SPD39T 39B6X Service Manual-01-0226 PDFDocument63 paginiSPD39T 39B6X Service Manual-01-0226 PDFAlejandroVCMXÎncă nu există evaluări

- SurgiStat II - Service ManualDocument98 paginiSurgiStat II - Service ManualAlejandroVCMX100% (2)

- AN3339 Application Note: 185 W Power Supply With PFC and Standby Supply For LED TV Using The L6564, L6599A, and VIPER27LNDocument44 paginiAN3339 Application Note: 185 W Power Supply With PFC and Standby Supply For LED TV Using The L6564, L6599A, and VIPER27LNrokis dwikyÎncă nu există evaluări

- kb9012qf PDFDocument257 paginikb9012qf PDFDaniel CrespoÎncă nu există evaluări

- Atlas LCR45: Preliminary Product DataDocument2 paginiAtlas LCR45: Preliminary Product DataAlejandroVCMXÎncă nu există evaluări

- Stmicro LCD Backlight ADocument24 paginiStmicro LCD Backlight AAndres Alegria100% (2)

- Valleylab Force FX-8c Electrosurgical Generator - Service Manual PDFDocument218 paginiValleylab Force FX-8c Electrosurgical Generator - Service Manual PDFElias AuccapiñaÎncă nu există evaluări

- Ge Adaptive DefrostDocument17 paginiGe Adaptive Defrostihsanerden100% (1)

- AET 9 RectifiersDocument63 paginiAET 9 RectifiersNeha GuptaÎncă nu există evaluări

- Valleylab Force EZ 8C高频电刀维修手册 (英文)Document208 paginiValleylab Force EZ 8C高频电刀维修手册 (英文)AlejandroVCMXÎncă nu există evaluări

- ELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsDocument80 paginiELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsAlejandroVCMXÎncă nu există evaluări

- ELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsDocument80 paginiELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsAlejandroVCMXÎncă nu există evaluări

- WTMC WTXD BOSCH Siemens Gas and Electric DryerDocument76 paginiWTMC WTXD BOSCH Siemens Gas and Electric DryerAlejandroVCMX100% (1)

- Reliance Literature - RRTB001109Document44 paginiReliance Literature - RRTB001109AlejandroVCMXÎncă nu există evaluări

- 31 9090 SXS Variable Speed CompDocument45 pagini31 9090 SXS Variable Speed CompAlejandroVCMXÎncă nu există evaluări

- Galvanized Pump Tank - 184980-001Document12 paginiGalvanized Pump Tank - 184980-001AlejandroVCMXÎncă nu există evaluări

- Reliance Expansion & Pump Tank Brochure - 210568-RPMCP00211Document2 paginiReliance Expansion & Pump Tank Brochure - 210568-RPMCP00211AlejandroVCMXÎncă nu există evaluări

- Galvanized Pump Tank - 184980-001Document12 paginiGalvanized Pump Tank - 184980-001AlejandroVCMXÎncă nu există evaluări

- Galvanized Pump Tank - 184980-001Document12 paginiGalvanized Pump Tank - 184980-001AlejandroVCMXÎncă nu există evaluări

- 2006 Service HandbookDocument75 pagini2006 Service HandbookspartacusrocksÎncă nu există evaluări

- Reliance Selection Guide - RSGBR00413Document2 paginiReliance Selection Guide - RSGBR00413AlejandroVCMXÎncă nu există evaluări

- Reliance Expansion & Pump Tank Brochure - 210568-RPMCP00211Document2 paginiReliance Expansion & Pump Tank Brochure - 210568-RPMCP00211AlejandroVCMXÎncă nu există evaluări

- Reliance Product Catalog 2012Document13 paginiReliance Product Catalog 2012AlejandroVCMXÎncă nu există evaluări

- Ge Adaptive DefrostDocument17 paginiGe Adaptive Defrostihsanerden100% (1)

- 111687-SpringSummer 2Document96 pagini111687-SpringSummer 2AlejandroVCMXÎncă nu există evaluări

- ELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsDocument80 paginiELECTROLUX - 361 - TumbleActionWasherswithElectronicControlsAlejandroVCMXÎncă nu există evaluări

- Sistema Electrico VWDocument40 paginiSistema Electrico VWsvismaelÎncă nu există evaluări

- CD Mechanism Type CDM53F-K2BD38Document5 paginiCD Mechanism Type CDM53F-K2BD38AlejandroVCMXÎncă nu există evaluări

- Flashback RAC Database To Guarantee Restore PointDocument2 paginiFlashback RAC Database To Guarantee Restore PointNguyen Khanh Hoa (TGV)Încă nu există evaluări

- Os Lab Manual AlgorithmDocument12 paginiOs Lab Manual Algorithmemail2vadivel100% (1)

- Srs of Insta 1 PDFDocument13 paginiSrs of Insta 1 PDFRohit KumarÎncă nu există evaluări

- Vaidehi - Patil Computer BDocument1 paginăVaidehi - Patil Computer BSamiksha ChavanÎncă nu există evaluări

- Genius Publications ListDocument5 paginiGenius Publications ListArun Trichal25% (4)

- Syllabus of DataStage CourseDocument8 paginiSyllabus of DataStage CourseDinesh SanodiyaÎncă nu există evaluări

- Mid Sem ExamDocument2 paginiMid Sem ExamPiyush MaheshwariÎncă nu există evaluări

- SACOD1Document6 paginiSACOD1PepeVichecheÎncă nu există evaluări

- OWASP LA The Last XSS Defense Talk Jim Manico 2018 08Document75 paginiOWASP LA The Last XSS Defense Talk Jim Manico 2018 08Ismael OliveiraÎncă nu există evaluări

- Gujarat Technological UniversityDocument2 paginiGujarat Technological UniversityMihir RanaÎncă nu există evaluări

- Console Output CLI ConsoleDocument9 paginiConsole Output CLI ConsoleJuan Carlos YepezÎncă nu există evaluări

- SQL em InglesDocument87 paginiSQL em InglesRafael PonceÎncă nu există evaluări

- Differences Between Andriod and IphoneDocument13 paginiDifferences Between Andriod and IphoneAndrew HunterÎncă nu există evaluări

- Online Condominium House Management System: Chapter One 1Document11 paginiOnline Condominium House Management System: Chapter One 1girmas100% (1)

- Ieee802 Hetnet TutorialDocument75 paginiIeee802 Hetnet TutorialPayal PriyaÎncă nu există evaluări

- Close: Lascon Storage BackupsDocument4 paginiClose: Lascon Storage BackupsAtthulaiÎncă nu există evaluări

- SE-HD55 (sm-AD9803049C2)Document29 paginiSE-HD55 (sm-AD9803049C2)Jory2005Încă nu există evaluări

- Lg-Pdp-Training Plasma TV AlapokDocument67 paginiLg-Pdp-Training Plasma TV AlapokHamedKoneÎncă nu există evaluări

- Effective Cmake Daniel Pfeifer Cppnow 05-19-2017Document106 paginiEffective Cmake Daniel Pfeifer Cppnow 05-19-2017masterhacksÎncă nu există evaluări

- ATU-100 Mini User Manual EngDocument12 paginiATU-100 Mini User Manual EngFlorin Nicola100% (1)

- Fast BeamDocument2 paginiFast BeamSimila Razzak RahmanÎncă nu există evaluări

- T5010 ManualDocument1.156 paginiT5010 Manual123chessÎncă nu există evaluări

- Service Manual SS700Document72 paginiService Manual SS700David Kasamba100% (1)

- Automatic Stabilization of Zigbee Network: Guanghui Pan Jia HeDocument4 paginiAutomatic Stabilization of Zigbee Network: Guanghui Pan Jia HeEdgar A.BÎncă nu există evaluări

- InteliCompact NT 1.4r3 ManualDocument273 paginiInteliCompact NT 1.4r3 ManualYuri Da Gama Santos100% (4)

- NA80 MB0 Manual PR - 0260Document62 paginiNA80 MB0 Manual PR - 0260roberto pirmatiÎncă nu există evaluări

- La-5322p Nswaa NtwaaDocument58 paginiLa-5322p Nswaa NtwaaVadim Shapovalov100% (1)

- Byte Con Fiden Tial Don Otc Opy: Model Name: Ga-H81M-HDocument29 paginiByte Con Fiden Tial Don Otc Opy: Model Name: Ga-H81M-Hjose GonzalesÎncă nu există evaluări

- Brosur Ofs 95eaDocument3 paginiBrosur Ofs 95eaJanuar JonathanÎncă nu există evaluări