Documente Academic

Documente Profesional

Documente Cultură

FDD5N50

Încărcat de

primero marnezDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

FDD5N50

Încărcat de

primero marnezDrepturi de autor:

Formate disponibile

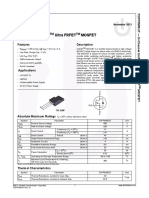

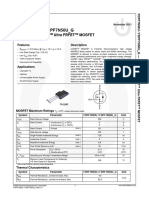

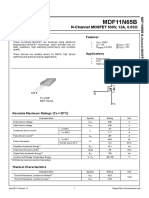

FDD5N50 N-Channel MOSFET

December 2007

UniFETTM

FDD5N50

tm

N-Channel MOSFET

500V, 4A, 1.4Ω

Features Description

• RDS(on) = 1.15Ω ( Typ.)@ VGS = 10V, ID = 2A These N-Channel enhancement mode power field effect

transistors are produced using Fairchild’s proprietary, planar

• Low gate charge ( Typ. 11nC) stripe, DMOS technology.

• Low Crss ( Typ. 5pF) This advanced technology has been especially tailored to

• Fast switching minimize on-state resistance, provide superior switching

performance, and withstand high energy pluse in the avalanche

• 100% avalanche tested and commutation mode. These devices are well suited for high

efficient switched mode power suppliesand active power

• Improved dv/dt capability

factor correction.

• RoHS compliant

D

G

G

S

D-PAK

S

MOSFET Maximum Ratings TC = 25oC unless otherwise noted*

Symbol Parameter Ratings Units

VDSS Drain to Source Voltage 500 V

VGSS Gate to Source Voltage ±30 V

-Continuous (TC = 25oC) 4

ID Drain Current A

-Continuous (TC = 100oC) 2.4

IDM Drain Current - Pulsed (Note 1) 16 A

EAS Single Pulsed Avalanche Energy (Note 2) 256 mJ

IAR Avalanche Current (Note 1) 4 A

EAR Repetitive Avalanche Energy (Note 1) 4 mJ

dv/dt Peak Diode Recovery dv/dt (Note 3) 4.5 V/ns

(TC = 25oC) 40 W

PD Power Dissipation

- Derate above 25oC 0.3 W/oC

o

TJ, TSTG Operating and Storage Temperature Range -55 to +150 C

Maximum Lead Temperature for Soldering Purpose, o

TL 300 C

1/8” from Case for 5 Seconds

Thermal Characteristics

Symbol Parameter Ratings Units

RθJC Thermal Resistance, Junction to Case 1.4 o

C/W

RθJA Thermal Resistance, Junction to Ambient 110

©2007 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDD5N50 Rev. A

FDD5N50 N-Channel MOSFET

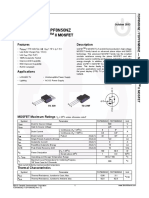

Package Marking and Ordering Information TC = 25oC unless otherwise noted

Device Marking Device Package Reel Size Tape Width Quantity

FDD5N50 FDD5N50TM D-PAK 380mm 16mm 2500

FDD5N50 FDD5N50TF D-PAK 380mm 16mm 2000

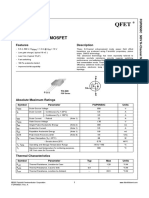

Electrical Characteristics

Symbol Parameter Test Conditions Min. Typ. Max. Units

Off Characteristics

BVDSS Drain to Source Breakdown Voltage ID = 250µA, VGS = 0V, TJ = 25oC 500 - - V

∆BVDSS Breakdown Voltage Temperature

ID = 250µA, Referenced to 25oC - 0.6 - V/oC

∆TJ Coefficient

VDS = 500V, VGS = 0V - - 1

IDSS Zero Gate Voltage Drain Current µA

VDS = 400V, TC = 125oC - - 10

IGSS Gate to Body Leakage Current VGS = ±30V, VDS = 0V - - ±100 nA

On Characteristics

VGS(th) Gate Threshold Voltage VGS = VDS, ID = 250µA 3.0 - 5.0 V

RDS(on) Static Drain to Source On Resistance VGS = 10V, ID = 2A - 1.15 1.4 Ω

gFS Forward Transconductance VDS = 20V, ID = 2A (Note 4) - 4.3 - S

Dynamic Characteristics

Ciss Input Capacitance - 480 640 pF

VDS = 25V, VGS = 0V

Coss Output Capacitance - 66 88 pF

f = 1MHz

Crss Reverse Transfer Capacitance - 5 8 pF

Qg(tot) Total Gate Charge at 10V - 11 15 nC

Qgs Gate to Source Gate Charge VDS = 400V, ID = 5A - 3 - nC

VGS = 10V

Qgd Gate to Drain “Miller” Charge (Note 4, 5) - 5 - nC

Switching Characteristics

td(on) Turn-On Delay Time - 13 36 ns

tr Turn-On Rise Time VDD = 250V, ID = 5A - 22 54 ns

td(off) Turn-Off Delay Time RG = 25Ω - 28 66 ns

tf Turn-Off Fall Time (Note 4, 5) - 20 50 ns

Drain-Source Diode Characteristics

IS Maximum Continuous Drain to Source Diode Forward Current - - 4 A

ISM Maximum Pulsed Drain to Source Diode Forward Current - - 16 A

VSD Drain to Source Diode Forward Voltage VGS = 0V, ISD = 4A - - 1.4 V

trr Reverse Recovery Time VGS = 0V, ISD = 5A - 300 - ns

Qrr Reverse Recovery Charge dIF/dt = 100A/µs (Note 4) - 1.8 - µC

Notes:

1: Repetitive Rating: Pulse width limited by maximum junction temperature

2: L = 32mH, IAS = 4A, VDD = 50V, RG = 25Ω, Starting TJ = 25°C

3: ISD ≤ 4A, di/dt ≤ 200A/µs, VDD ≤ BVDSS, Starting TJ = 25°C

4: Pulse Test: Pulse width ≤ 300µs, Duty Cycle ≤ 2%

5: Essentially Independent of Operating Temperature Typical Characteristics

FDD5N50 Rev. A 2 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

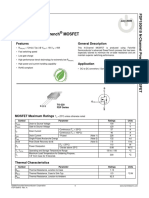

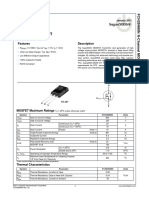

Typical Performance Characteristics

Figure 1. On-Region Characteristics Figure 2. Transfer Characteristics

20 20

VGS = 15.0V

10 10.0V

8.0 V

10

7.0 V

6.5 V

ID,Drain Current[A]

ID,Drain Current[A]

6.0 V

o

5.5 V 150 C

1 o

25 C

1

o

-55 C

*Notes: *Notes:

0.1 1. 250µs Pulse Test 1. VDS = 20V

o

2. TC = 25 C 2. 250µs Pulse Test

0.04 0.1

0.1 1 10 30 4 5 6 7 8

VDS,Drain-Source Voltage[V] VGS,Gate-Source Voltage[V]

Figure 3. On-Resistance Variation vs. Figure 4. Body Diode Forward Voltage

Drain Current and Gate Voltage Variation vs. Source Current

and Temperature

3.0 70

Drain-Source On-Resistance

IS, Reverse Drain Current [A]

2.5

o

150 C

RDS(ON) [Ω],

10

2.0 VGS = 10V

o

25 C

1.5 VGS = 20V

*Notes:

1. VGS = 0V

o

*Note: TJ = 25 C 2. 250µs Pulse Test

1.0 1

0 3 6 9 12 0.4 0.8 1.2 1.6

ID, Drain Current [A] VSD, Body Diode Forward Voltage [V]

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Characteristics

1000 10

Ciss = Cgs + Cgd (Cds = shorted)

VDS = 100V

Coss = Cds + Cgd

VDS = 250V

VGS, Gate-Source Voltage [V]

Crss = Cgd

8 VDS = 400V

750 *Note:

1. VGS = 0V

Capacitances [pF]

2. f = 1MHz 6

Ciss

500

Coss 4

250

2

Crss

*Note: ID = 5A

0 0

0.1 1 10 30 0 4 8 12

VDS, Drain-Source Voltage [V] Qg, Total Gate Charge [nC]

FDD5N50 Rev. A 3 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

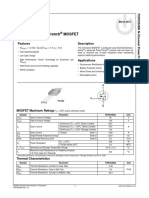

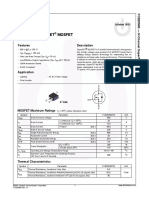

Typical Performance Characteristics (Continued)

Figure 7. Breakdown Voltage Variation Figure 8. On-Resistance Variation

vs. Temperature vs. Temperature

1.2 3.0

Drain-Source Breakdown Voltage

2.5

Drain-Source On-Resistance

1.1

BVDSS, [Normalized]

RDS(on), [Normalized]

2.0

1.0 1.5

1.0

0.9

*Notes: 0.5 *Notes:

1. VGS = 0V 1. VGS = 10V

2. ID = 250µA 2. ID = 2A

0.8 0.0

-75 -25 25 75 125 175 -75 -25 25 75 125 175

o o

TJ, Junction Temperature [ C] TJ, Junction Temperature [ C]

Figure 9. Maximum Safe Operating Area Figure 10. Maximum Drain Current

vs. Case Temperature

30 4.5

30µs

4

10 100µs

ID, Drain Current [A]

ID, Drain Current [A]

1ms

3

1 10ms

DC 2

Operation in This Area

is Limited by R DS(on)

0.1 *Notes:

o

1

1. TC = 25 C

o

2. TJ = 150 C

3. Single Pulse

0.01 0

1 10 100 800 25 50 75 100 125 150

o

VDS, Drain-Source Voltage [V] TC, Case Temperature [ C]

Figure 11. Transient Thermal Response Curve

3

Thermal Response [ZθJC]

1

0.5

0.2

PDM

0.1

t1

0.1 0.05 t2

*Notes:

0.02 o

0.01

1. ZθJC(t) = 1.4 C/W Max.

2. Duty Factor, D= t1/t2

Single pulse 3. TJM - TC = PDM * ZθJC(t)

0.01

-5 -4 -3 -2 -1 0 1

10 10 10 10 10 10 10

Rectangular Pulse Duration [sec]

FDD5N50 Rev. A 4 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

Gate Charge Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms

FDD5N50 Rev. A 5 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

Peak Diode Recovery dv/dt Test Circuit & Waveforms

DUT +

V DS

I SD

L

D r iv e r

R G

S am e T ype

as DUT V DD

V G S • d v / d t c o n t r o lle d b y R G

• I S D c o n t r o lle d b y p u ls e p e r io d

G a t e P u ls e W id th

V GS D = --------------------------

G a te P u ls e P e r io d 10V

( D r iv e r )

I F M , B o d y D io d e F o r w a r d C u r r e n t

I SD

( DUT ) d i/ d t

IR M

B o d y D io d e R e v e r s e C u r r e n t

V DS

( DUT ) B o d y D io d e R e c o v e r y d v / d t

V SD

V DD

B o d y D io d e

F o r w a r d V o lt a g e D r o p

FDD5N50 Rev. A 6 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

Mechanical Dimensions

D-PAK

Dimensions in Millimeters

FDD5N50 Rev. A 7 www.fairchildsemi.com

FDD5N50 N-Channel MOSFET

TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and

is not intended to be an exhaustive list of all such trademarks.

ACEx® FPS™ PDP-SPM™ SyncFET™

Build it Now™ FRFET® Power220® ®

CorePLUS™ Global Power ResourceSM Power247®

The Power Franchise®

CROSSVOLT™ Green FPS™ POWEREDGE®

CTL™ Green FPS™ e-Series™ Power-SPM™ tm

Current Transfer Logic™ GTO™ PowerTrench®

TinyBoost™

EcoSPARK® i-Lo™ Programmable Active Droop™ TinyBuck™

EZSWITCH™ * IntelliMAX™ QFET®

™ TinyLogic®

ISOPLANAR™ QS™

TINYOPTO™

MegaBuck™ QT Optoelectronics™ TinyPower™

®

MICROCOUPLER™ Quiet Series™

tm

TinyPWM™

Fairchild® MicroFET™ RapidConfigure™

TinyWire™

Fairchild Semiconductor® MicroPak™ SMART START™ µSerDes™

FACT Quiet Series™ MillerDrive™ SPM®

UHC®

FACT® Motion-SPM™ STEALTH™

Ultra FRFET™

FAST® OPTOLOGIC® SuperFET™ UniFET™

FastvCore™ OPTOPLANAR® SuperSOT™-3

VCX™

FlashWriter® * ® SuperSOT™-6

tm

SuperSOT™-8

* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT NOTICE TO ANY PRODUCTS HEREIN TO

IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER

ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems 2. A critical component is any component of a life support

which, (a) are intended for surgical implant into the body, or device or system whose failure to perform can be reasonably

(b) support or sustain life, and (c) whose failure to perform expected to cause the failure of the life support device or

when properly used in accordance with instructions for use system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to result

in significant injury to the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

This datasheet contains the design specifications for product development.

Advance Information Formative or In Design

Specifications may change in any manner without notice.

This datasheet contains preliminary data; supplementary data will be pub-

Preliminary First Production lished at a later date. Fairchild Semiconductor reserves the right to make

changes at any time without notice to improve design.

This datasheet contains final specifications. Fairchild Semiconductor reserves

No Identification Needed Full Production

the right to make changes at any time without notice to improve design.

This datasheet contains specifications on a product that has been discontin-

Obsolete Not In Production ued by Fairchild semiconductor. The datasheet is printed for reference infor-

mation only.

Rev. I32

FDD5N50 Rev. A 8 www.fairchildsemi.com

S-ar putea să vă placă și

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDe la EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsÎncă nu există evaluări

- Ch.4 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument79 paginiCh.4 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Fdpf5N50Ut: N-Channel Unifet Ultra Frfet MosfetDocument8 paginiFdpf5N50Ut: N-Channel Unifet Ultra Frfet MosfetJOHN BRICCO A. MATACSILÎncă nu există evaluări

- Fdp12N50 / Fdpf12N50T: N-Channel Unifet MosfetDocument11 paginiFdp12N50 / Fdpf12N50T: N-Channel Unifet MosfetJuan CarlosÎncă nu există evaluări

- FDPF10N50FTDocument9 paginiFDPF10N50FTAbigail HoobsÎncă nu există evaluări

- DatasheetDocument8 paginiDatasheetRegisk8 OliveiraÎncă nu există evaluări

- 28N50F FairchildSemiconductorDocument8 pagini28N50F FairchildSemiconductorgabosakrÎncă nu există evaluări

- Fdd390N15Alz: N-Channel Powertrench MosfetDocument9 paginiFdd390N15Alz: N-Channel Powertrench Mosfetserrano.flia.coÎncă nu există evaluări

- Fdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetDocument10 paginiFdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetsrasicÎncă nu există evaluări

- Fdp52N20 / Fdpf52N20T: UnifetDocument10 paginiFdp52N20 / Fdpf52N20T: UnifetJoão de barroÎncă nu există evaluări

- 100N50F FDL Mosfet N PDFDocument8 pagini100N50F FDL Mosfet N PDFHưng HQÎncă nu există evaluări

- Fqa9n90c F109-96052 PDFDocument9 paginiFqa9n90c F109-96052 PDFKhoa DangÎncă nu există evaluări

- FDP 150 N 10Document8 paginiFDP 150 N 10Luka BaracÎncă nu există evaluări

- FDP025N06Document9 paginiFDP025N06bravo.bravoÎncă nu există evaluări

- Fdpf7n50u Fdpf7n50u GDocument8 paginiFdpf7n50u Fdpf7n50u Gdhunter ZenfoneÎncă nu există evaluări

- Datasheet FDP7N50Document10 paginiDatasheet FDP7N50Anonymous fAL3CNtUiÎncă nu există evaluări

- fdp054n10 PDFDocument8 paginifdp054n10 PDFAldi DwprstwnÎncă nu există evaluări

- FQP6N50C: 500V N-Channel MOSFETDocument8 paginiFQP6N50C: 500V N-Channel MOSFETHenry ToroÎncă nu există evaluări

- FQD4P40 D 1809499Document9 paginiFQD4P40 D 1809499SaanounÎncă nu există evaluări

- MDF7N60BDocument8 paginiMDF7N60BFreddyÎncă nu există evaluări

- FDP20N50 184794Document11 paginiFDP20N50 184794Paulo NogueiraÎncă nu există evaluări

- FQPF12N60C FairchildSemiconductorDocument9 paginiFQPF12N60C FairchildSemiconductorAkhmad Isnaeni RamdaniÎncă nu există evaluări

- FQD7P06: P-Channel QFET MosfetDocument9 paginiFQD7P06: P-Channel QFET MosfetIsela LopezÎncă nu există evaluări

- FCH25N60NDocument8 paginiFCH25N60Ngustavo gonzalezÎncă nu există evaluări

- FQP10N20C / FQPF10N20C: N-Channel QFET MosfetDocument10 paginiFQP10N20C / FQPF10N20C: N-Channel QFET MosfethenriquegonferÎncă nu există evaluări

- FQPF 8 N 60 CFDocument8 paginiFQPF 8 N 60 CFBhadreshkumar SharmaÎncă nu există evaluări

- MDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Document8 paginiMDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Erroz RosadiÎncă nu există evaluări

- Fcb20N60: N-Channel Superfet MosfetDocument9 paginiFcb20N60: N-Channel Superfet MosfetEo GpÎncă nu există evaluări

- FQPF13N50CFDocument8 paginiFQPF13N50CFPiotr vvÎncă nu există evaluări

- fdp33n25 fdpf33n25tDocument10 paginifdp33n25 fdpf33n25tNovri AndiÎncă nu există evaluări

- MDF10N60G 1Document6 paginiMDF10N60G 1samvick103Încă nu există evaluări

- Fch25N60N: N-Channel Supremos MosfetDocument8 paginiFch25N60N: N-Channel Supremos MosfetKUMAR ABHINAVÎncă nu există evaluări

- FQP12N60C FairchildSemiconductorDocument9 paginiFQP12N60C FairchildSemiconductoroskr.bstÎncă nu există evaluări

- FQP10N60C DatasheetzDocument10 paginiFQP10N60C DatasheetzagesoporteÎncă nu există evaluări

- MDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Document6 paginiMDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Moroșan CristiÎncă nu există evaluări

- FQP12P10: P-Channel QFET MosfetDocument8 paginiFQP12P10: P-Channel QFET MosfetCrdz LouisÎncă nu există evaluări

- 18N80T DatasheetDocument10 pagini18N80T DatasheetVịnh DemoÎncă nu există evaluări

- FCH067N65S3 FairchildSemiconductorDocument9 paginiFCH067N65S3 FairchildSemiconductorJoaquim FernandesÎncă nu există evaluări

- MDF12N50Document8 paginiMDF12N50Djalma MoreiraÎncă nu există evaluări

- MDF10N65B: N-Channel MOSFET 650V, 10.0A, 1.0Document6 paginiMDF10N65B: N-Channel MOSFET 650V, 10.0A, 1.0Pablo AllosiaÎncă nu există evaluări

- Fqa 24 N 50Document8 paginiFqa 24 N 50CristhianÎncă nu există evaluări

- MDF11N65BDocument6 paginiMDF11N65BElec FoÎncă nu există evaluări

- Fqa38n30 310169Document9 paginiFqa38n30 310169Владимир ВайнерÎncă nu există evaluări

- FQP8N60C: N-Channel QFET MosfetDocument8 paginiFQP8N60C: N-Channel QFET MosfetVuksanov ZarkoÎncă nu există evaluări

- fqpf5n50cf Fqpf5n50cftu PDFDocument8 paginifqpf5n50cf Fqpf5n50cftu PDFALFREDO BARREZUETAÎncă nu există evaluări

- STF 13 NM 60 NDDocument12 paginiSTF 13 NM 60 NDlejojoel321Încă nu există evaluări

- FQPF7N80C FQPF7N80CDocument12 paginiFQPF7N80C FQPF7N80Cmadeline cruzata downerÎncă nu există evaluări

- N-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesDocument6 paginiN-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesjokophpÎncă nu există evaluări

- MDP13N50B / MDF13N50B: N-Channel MOSFET 500V, 13.0 A, 0.5Document8 paginiMDP13N50B / MDF13N50B: N-Channel MOSFET 500V, 13.0 A, 0.5nassimÎncă nu există evaluări

- FQA28N15: 150V N-Channel MOSFETDocument8 paginiFQA28N15: 150V N-Channel MOSFETRoberto BlazquezÎncă nu există evaluări

- 20 N 60Document10 pagini20 N 60Asep AcengÎncă nu există evaluări

- 16N60 Fairchild SemiconductorDocument10 pagini16N60 Fairchild SemiconductorPop-Coman SimionÎncă nu există evaluări

- Fca47n60 FetDocument10 paginiFca47n60 FetRuslanÎncă nu există evaluări

- 6N90C Mosfet N PDFDocument10 pagini6N90C Mosfet N PDFHưng HQÎncă nu există evaluări

- Irf 634 BDocument8 paginiIrf 634 BAhmed ShagidullinÎncă nu există evaluări

- Superfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetDocument10 paginiSuperfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetAlexandros BobÎncă nu există evaluări

- FDD8447LDocument6 paginiFDD8447Lsorsa1Încă nu există evaluări

- MDF9N50F MagnaChipDocument6 paginiMDF9N50F MagnaChipchokÎncă nu există evaluări

- Lect 20 19EEE111 Thyristors - SCRDocument36 paginiLect 20 19EEE111 Thyristors - SCRDenifer DeepÎncă nu există evaluări

- Longi LR5-72 HPH 550M G2 30mm Frame - PANDocument1 paginăLongi LR5-72 HPH 550M G2 30mm Frame - PANChristopher BalbuenaÎncă nu există evaluări

- Diode AnimationDocument87 paginiDiode AnimationRamadhurai100% (2)

- Micromanufacturing: Bulk Micromanufacturing Surface Micromachining The LIGA ProcessDocument25 paginiMicromanufacturing: Bulk Micromanufacturing Surface Micromachining The LIGA Processvivek ghatbandheÎncă nu există evaluări

- AEC Module1 Clipping and ClampingDocument43 paginiAEC Module1 Clipping and ClampingVinay kumar havinalÎncă nu există evaluări

- History of Semiconducting Systems: Kesavarao A/L Anantharavoo (16Dem14F1013) Dem 2ADocument10 paginiHistory of Semiconducting Systems: Kesavarao A/L Anantharavoo (16Dem14F1013) Dem 2AKehisorKumarÎncă nu există evaluări

- Different Types of Transistors and Their WorkingDocument22 paginiDifferent Types of Transistors and Their WorkingVenki EdeÎncă nu există evaluări

- Bd64538efv-E2Document1 paginăBd64538efv-E2AndiÎncă nu există evaluări

- II PU Physics Passing Package 21-22Document19 paginiII PU Physics Passing Package 21-22Kalyan ReddyÎncă nu există evaluări

- Green14 Snaith PerovskiteSolarCells ReviewDocument9 paginiGreen14 Snaith PerovskiteSolarCells ReviewjonbilbaoÎncă nu există evaluări

- SP07 L13Document17 paginiSP07 L13NITIN NAYANÎncă nu există evaluări

- BSIM 4.7 ManualDocument184 paginiBSIM 4.7 ManualtbsuirÎncă nu există evaluări

- Ensc 851 PDFDocument13 paginiEnsc 851 PDFMubina SarwarÎncă nu există evaluări

- Indiabix 1ST HalfDocument45 paginiIndiabix 1ST HalfCaryl Kim DelacruzÎncă nu există evaluări

- Candidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksDocument3 paginiCandidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksAdhikari SushilÎncă nu există evaluări

- 4435SCDocument8 pagini4435SCRonald NascimentoÎncă nu există evaluări

- 3428825Document23 pagini3428825Ghubaida HassaniÎncă nu există evaluări

- Solid State Microwave Devices - Unit IIIDocument65 paginiSolid State Microwave Devices - Unit IIIsaim khanÎncă nu există evaluări

- ThyristorDocument22 paginiThyristorBharat100% (1)

- Tranzitor J3YDocument2 paginiTranzitor J3YLu HoaÎncă nu există evaluări

- MOSFETs For Switching AC - AVR FreaksDocument11 paginiMOSFETs For Switching AC - AVR FreaksBill WhiteÎncă nu există evaluări

- Physics ProjectDocument11 paginiPhysics ProjectYouTubeFleX OPÎncă nu există evaluări

- E3-282 MidSemPaper Aug2021Document3 paginiE3-282 MidSemPaper Aug2021Wiluam Rutherford BondÎncă nu există evaluări

- Basic Electrical Properties of MosDocument10 paginiBasic Electrical Properties of Mosmayamohan725Încă nu există evaluări

- Ada302734, Tree HDBKDocument507 paginiAda302734, Tree HDBKRGK77Încă nu există evaluări

- 2SK2759Document2 pagini2SK2759hectorsevillaÎncă nu există evaluări

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 paginiAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941Încă nu există evaluări

- Sample Problems and Solution - 2Document6 paginiSample Problems and Solution - 2김동욱Încă nu există evaluări

- Lectures On Diodes 3Document14 paginiLectures On Diodes 3Tt RrtÎncă nu există evaluări