Documente Academic

Documente Profesional

Documente Cultură

I2C Tutorial: News Reviews Guides & Tutorials Embedded Previews & Unboxing More

Încărcat de

Ganesh WattamwarTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

I2C Tutorial: News Reviews Guides & Tutorials Embedded Previews & Unboxing More

Încărcat de

Ganesh WattamwarDrepturi de autor:

Formate disponibile

22.11.

2017 I2C Tutor al

About Us Contact Us

News Reviews Guides & Tutorials Embedded Previews & Unboxing More

HOME EMBEDDED I2C TUTORIAL

FOLLOW US FACEBOOK

Search ...

I2C Tutorial We

SUBSCRIBE VIA EMAIL Posted By Umang Gajera Posted date: April 05, 2017 in: Embedded No Comments

Bu w

Email Address Erişi

Subscribe In this tutorial we will go through I2C Bus & Protocol. I2C was originally invented by Philips(now NXP) in

1982 as bi-directional bus to communicate with multiple devices using just 2 wires/lines. I2C stands for GOOGLE+

Inter-Integrated Circuit. I2C is sometimes also referred as TWI, which is short for Two Wire Interface, since

it uses only 2 wires for data transmission and synchronization. I2C is pronounced and referred to as “I-

Squared-C” [I2C] , “I-Two-C” [I2C] and “I-I-C” [IIC]. The two wires of I2C Bus consists of:

1. Data Line called SDA which is short for Serial Data

2. Clock Line called SCL which is short for Serial Clock

SDA is the wire on which the actual data transfer happens, which is bi-directional, between different

masters and slaves. SCL is the wire on which the Master device generates a clock for slave device(s).

I2C supports 7 bit and 10 bit addresses for each device connected to the bus. 10 bit addressing was

introduced later. With 7 bit address its possible to connect up to 128 I2C devices to the same bus, however,

some addresses are reserved so practically only 112 devices can be connected at the same time. With 10

bit address a maximum of 1024 devices can be connected. To keep things simple we will be going through

goo

7 bit addressing in this tutorial. For 10 bit addressing you can look up the official I2C specification by NXP, a

Refuge

link to which is given at the bottom of this tutorial. Once you get familiar with the I2C protocol, 10 bit

addressing will be a piece of cake.

As per the original specification of I2C/TWI, it supports a maximum frequency of 100Khz. But along the

years the specifications was updated many times and now we have a bunch of different speed modes. The

latest mode added was Ultra-Fast Mode which allows I2C bus transfer speeds of up to 5Mhz.

I2C Speed Mode I2C Speed Communication

Standard Mode (Sm) 100 Kbit/s [Khz] Bidirectional

Fast Mode (Fm) 400 Kbit/s [Khz] Bidirectional

Fast Mode Plus (Fm+) 1 MBits/s [Mhz] Bidirectional

High-speed mode (Hs-mode) 3.4 MBits/s [Mhz] Bidirectional

Ultra Fast-mode (UFm) 5 MBits/s [Mhz] Unidirectional

I2C has 4 operating modes:

1. Master Transmitter mode : Master Writes Data to Slave

2. Master Receiver mode : Master Reads Data from Slave

3. Slave Transmitter mode : Slave Write Data to Master

4. Slave Receiver mode : Slave Reads Data from Master

To achieve high transfer speeds Ultra-Fast Mode uses push-pull drivers instead of open-drain

which eliminates the use of pull-up resistors. Ultra-Fast Mode is unidirectional only and uses same

bus protocol but is not compatible with bi-directional I2C devices.

Even though multiple masters may be present on the I2C bus the arbitration is handled in such a way that

there is no corruption of data on bus in case when more than 2 masters try to transmit data at the same

time. Since the transmission, synchronization and arbitration is done using only 2 wires on the bus, the

communication protocol might be a bit uneasy to understand for beginners .. but its actually easy to

understand – just stick with me 🙂

http://www.ocfreaks.com/ 2c-tutor al/ 1/7

22.11.2017 I2C Tutor al

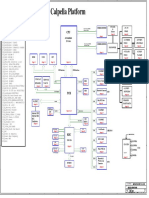

A general I2C/TWI bus topology with multiple masters and multiple slaves connected to the bus at the

same time is shown below:

Let us go through I2C protocol basics first. I2C bus is a Byte Oriented bus. Only a Byte can be transferred

at a time. Communication(Write to & Read from) is always initiated by a Master. The Master first sends a

START condition and then writes the Slave Address (SLA) and the Direction bit(Read=1/Write=0) on bus

and the corresponding Slave responds accordingly.

Format for I2C communication protocol

Depending on the Direction bit, 2 types of transfers are possible on the I2C bus:

Case 1 – Data transfer from “Master transmitter” to “Slave receiver”

1. In this case, after sending the START condition, the Master sends the First Byte which contains

the Slave address + Write bit.

2. The corresponding slave acknowledges it by sending back an Acknowledge (ACK) bit to the

Master.

3. Next, the Master sends 1 or more bytes to slave. After each byte received the Slave sends back

an Acknowledge bit (ACK).

4. When Master wants to stop writing it then sends a STOP condition.

Case 2 – Data transfer from “Slave transmitter” to “Master receiver”

1. Here the Master sends the First Byte which contains the Slave address + Read bit

2. The corresponding Slave acknowledges it by sending back an Acknowledge (ACK) bit to the

Master.

3. Next, the Slave sends 1 or more bytes and the Master acknowledges it everytime by sending an

Acknowledge bit (ACK).

4. When the Master wants to stop reading it sends a Not Acknowledge bit (NACK) followed by a

STOP condition.

Format for rst byte after START

As soon as the START condition is transmitted on the bus, the first byte (or the control byte) is transmitted.

Bits 7 to 1 contain the Slave address and Bit 0 is direction(Read/Write) bit.

http://www.ocfreaks.com/ 2c-tutor al/ 2/7

22.11.2017 I2C Tutor al

An example of timing diagram for complete data transfer

Given below, is a timing diagram for complete transfer of 3 Bytes including the first byte:

Image Source: I2C Specification

Start & Stop Conditions

All I2C transactions begin with a START (S) and are terminated by a STOP (P).

START condition : When a HIGH to LOW transition occurs on the SDA line while SCL is HIGH.

STOP condition : When a LOW to HIGH transition occurs on the SDA line while SCL is HIGH.

Repeated Start

A Repeat Start condition is similar to a Start condition, except it is sent in place of Stop when the master

does not want to loose the control over the bus and wants to complete its transfers in atomic manner

when multiple masters are present. When a master wants to switch to Master Receiver Mode from Master

Transmitter mode or vice-versa it sends a Repeated start at the end of the current transfer so it remains

master when next transfer starts.

Generating the Clock pulses, STOP and START is the responsibility of the Master. When the

Master wants to change the transfer mode(i.e Read/Write) it sends a Repeated START condition

instead of a STOP condition. A transfer typically ends with a STOP or Repeated START condition.

SDA & SCL Voltage levels for di erent Voltage devices on same

bus

In many cases(but not all!), I2C supports devices having different signal voltage levels to be connected to

the same bus. Like for example interfacing 5V I2C Slave device with a 3.3V microcontroller like lpc1768,

lpc2148 or interfacing 3.3V I2C Slave device with 5V microcontroller like Arduino. In such cases we connect

the Pull-up resistors to the lower of the Vcc/Vdd. In the mentioned examples it would be 3.3V in both cases

since its the lower one. As per the I2C specification Input reference levels are set as 30 % and 70 % of Vcc.

Hence, VIL(LOW-level input voltage) is 0.3Vcc and VIH(HIGH-level input voltage) is 0.7Vcc . If these

thresholds for Input Reference Levels are met when using two or more device with different voltages you

are good to go by connecting pull ups to lowest Vcc else you will need a line buffer/driver which provides

level-shifting, between the different voltage level devices based on CMOS, NMOS, TTL, etc.

http://www.ocfreaks.com/ 2c-tutor al/ 3/7

22.11.2017 I2C Tutor al

Opendrain SDA and SCL lines

I2C uses Open-drain / Open-Collector drivers for both SDA and SCL. Consider the following image showing

basic open-drain driver for I2C:

Here the buffer is used to Receive(input) data and Mosfet is used to Transmit(output) data. Drivers for both

SDA and SCL are similar. When the Mosfet is activated it will sink the current from pull-ups resistors which

forces the pin to a Logic Low. Note that it cannot drive the line to HIGH by itself which is obvious. To

provide a logic High state when the output driver is not trying to pull the line LOW we use Pull-Up resistors.

Using pull-ups the logic state of SDA and SCL signals on the I2C bus is always defined and never

floating(digitally). Hence, when no transfers are occurring and the bus is idle, SDA and SCL are continuously

pulled to logic high.

I2C Pull-Up Resistor Values

We will go into intricacies of Pull up resistor Value selection for a particular mode in another post since its a

function of bus capacitance and Vcc/Vdd along with sinking current. For beginners it better to following the

rule of thumb: You need lower resistor values as the speed increases and Vice-versa. For simple general

purpose projects/application you can use a pull-up resistor value between 1kΩ to 10kΩ. For example when

interfacing I2C devices at 100Khz I use 10kΩ pull ups.

Typical Range for Pull up Resistor value in Standard mode (Sm) i.e. 100Khz is between 5kΩ to

10kΩ, while that in Fast Mode (Fm) i.e. 400Khz is between 2kΩ to 5kΩ. For High Speed mode (Hs-

mode) i.e. 3.4Mhz, its around 1kΩ. Be sure to check your part manufacturer’s datasheet for more.

Clock Stretching

Clock Stretching is a mechanism for slave devices to make the master wait until data is ready or slave

device has to finish some internal operations (like: ADC conversion, Initial internal Write cycle, etc..) before

proceeding further. In Clock Stretching the SCL line is held low by the slave which pauses the current

transfer.

Acknowledge Polling

In practice, many Slave devices do not support clock stretching. Consider 24c16, at24c32, 24lc256, etc.

series of EEPROMs. These devices do not support clock stretching even though they have to perform

internal byte write or page write operation when the master does a write operation. In this case the master

has to initiate an Acknowledge Polling (for EEPROMs its also called Write Polling ) which checks if the

http://www.ocfreaks.com/ 2c-tutor al/ 4/7

22.11.2017 I2C Tutor al

EEPROM has finished internal operation or not. When the EEPROM starts internal write cycle it won’t

respond to its address but when it completes, it responds with an ACK to the master. So, in Acknowledge

Polling we keep on sending the slave address with write bit and wait for any ACK from the Slave which

indicates Slave is ready for next operation.

Condition for Valid Data (Data Validity)

For any data bit to be Valid, the SDA line must be stable when the period of clock is HIGH. The change in

state of the SDA line(From HIGH to LOW or Vice-versa) can only happen when the SCL line is LOW. A valid

data bit is transferred for each corresponding clock pulse. This is illustrated in the timing diagram shows

below:

I2C Master Modes when using Microcontrollers / Arduino

When interfacing Microcontrollers, like LPC2148, LPC1768, LPC1114, Atmega8/16, PICs or MCU Boards like

Arduino Uno (Atmega 168/368) or Raspberry Pi, generally we use Master Transmitter & Master Receiver

mode since we interface such MCUs with Slave-Only I2C devices like EEPROMs, LCD panels, RTCs, Sensors

like digital Gyroscopes, 3 axis accelerometer, temperature sensors, etc. Such devices generally use 7 bit

addresses and commonly support Standard & Fast Speed mode i.e. they operate at frequencies from

100Khz to 400Khz.

Master Transmitter mode is summarized in the following diagram:

and Master Receiver Mode is summarized as follows:

Reference(s):

I2C Official Specification by NXP

Share this:

Share

Tags: electronics I2C tutorial

Like Tweet Share Share Share

Previous Next

Create Keil uVision5 Project for LPC2148 ARM7 LPC2148 I2C Programming Tutorial

MCU

http://www.ocfreaks.com/ 2c-tutor al/ 5/7

22.11.2017 I2C Tutor al

LPC2148 I2C Basic UART Tutorial LPC2148 GPIO

Programming Tutorial Programming Tutorial

Tutorial on Using LPC2148 ADC Interfacing 16X2 LCD

MCUXpresso to create Programming Tutorial with LPC2148 tutorial

Cortex-M projects with...

ABOUT THE AUTHOR

Umang Gajera

3 Comments OCFreaks!

1 Login

Sort by Newest

Recommend 2 ⤤ Share

Join the discussion…

LOG IN WITH

OR SIGN UP WITH DISQUS ?

Name

Roshan Mani • 7 months ago

Hats off, great explanation. Please update an tutorial on SPI also.

△ ▽ • Reply • Share ›

Shaheem ahamed • 7 months ago

Really good work Umang sir,

Looking forward to your i2c tutorial with ARM.

△ ▽ • Reply • Share ›

Power_user_EX Mod > Shaheem ahamed • 7 months ago

Thanks Shaheem. Its already posted, check it under Embedded category from main menu.

△ ▽ • Reply • Share ›

ALSO ON OCFREAKS!

LPC2148 I2C Programming Tutorial LPC1768 UART Programming Tutorial

7 comments • 7 months ago 1 comment • 2 months ago

Sunil — so there is error handling mechanism in Venkat — Nice tutorial Umang.Do you have an

I2C right? in CAN protocol we error handling example on RS485 for LPC1768?

mechanism (CRC error)

How to Retarget/Redirect printf & scanf to LPC2148 DAC Programming Tutorial

UART in KEIL 2 comments • a month ago

2 comments • a month ago Power_user_EX — Hi Ritu, how much difference

Power_user_EX — Hi Lewi. Even I had the same are you getting at the output? Check the reference

question when I was researching on this. The best voltage at VREF pin - it must be 3.3v exactly or …

explanation I could get was from ARM C and …

✉ Subscribe d Add Disqus to your siteAdd DisqusAdd 🔒 Privacy

http://www.ocfreaks.com/ 2c-tutor al/ 6/7

22.11.2017 I2C Tutor al

(C) OCFreaks! 2011-17. About Us Contact Us

http://www.ocfreaks.com/ 2c-tutor al/ 7/7

S-ar putea să vă placă și

- What Is I2C?: To Know The I2C in Detail See This ArticleDocument6 paginiWhat Is I2C?: To Know The I2C in Detail See This ArticleRauf LalaÎncă nu există evaluări

- Aardvark v5.11Document69 paginiAardvark v5.11Yogesh KumarÎncă nu există evaluări

- SPI and I2CDocument3 paginiSPI and I2CVinod KumarÎncă nu există evaluări

- I2C SPI: The Important Difference Between I2C and SPI (I2C Vs SPI) Communication ProtocolDocument3 paginiI2C SPI: The Important Difference Between I2C and SPI (I2C Vs SPI) Communication ProtocolBenjamin HouseÎncă nu există evaluări

- Aardvark v3.30Document62 paginiAardvark v3.30Agustín RamírezÎncă nu există evaluări

- Explain The Physical Layer of The I2C ProtocolDocument7 paginiExplain The Physical Layer of The I2C ProtocolNEETHU PRAKASH100% (1)

- ESP32 I2C TutorialDocument16 paginiESP32 I2C TutorialpanikmanÎncă nu există evaluări

- IJERA WWW Ijera ComDocument9 paginiIJERA WWW Ijera ComAman Ullah AmanÎncă nu există evaluări

- Implementation of Inter-Integrated Circuit (I2C) Multiple Bus ControllerDocument5 paginiImplementation of Inter-Integrated Circuit (I2C) Multiple Bus ControllerKumars tiwariÎncă nu există evaluări

- I2c ThesisDocument7 paginiI2c Thesisannmontgomeryjackson100% (1)

- I2C Protocol Implementation: Guided By: MR .Y.V. Joshi Mr. Vaibbhav TaraateDocument52 paginiI2C Protocol Implementation: Guided By: MR .Y.V. Joshi Mr. Vaibbhav TaraateOmprasad RathodÎncă nu există evaluări

- Serial CommunicationDocument3 paginiSerial CommunicationMathematics TutorÎncă nu există evaluări

- Implementation of I2C-DMA & SPI-DMA Interface: A Comparative StudyDocument6 paginiImplementation of I2C-DMA & SPI-DMA Interface: A Comparative StudySantiagoCorazaoPeraltaÎncă nu există evaluări

- Basics of The I2C Communication ProtocolDocument26 paginiBasics of The I2C Communication ProtocolBeatriz PedroÎncă nu există evaluări

- I2C - Learn - SparkfunDocument6 paginiI2C - Learn - SparkfunyuvarajnarayanasamyÎncă nu există evaluări

- How To Network Five Arduinos (Or More) Using I2C - TechBitarDocument6 paginiHow To Network Five Arduinos (Or More) Using I2C - TechBitarSigid AriewibowoÎncă nu există evaluări

- I C-Bus Specification and User ManualDocument50 paginiI C-Bus Specification and User ManualDong NguyenÎncă nu există evaluări

- Ceresoli Basics of I2c On LinuxDocument47 paginiCeresoli Basics of I2c On LinuxcodesnishÎncă nu există evaluări

- I2C Info - I2C Bus, Interface and ProtocolDocument2 paginiI2C Info - I2C Bus, Interface and ProtocolChakkaravarthiErÎncă nu există evaluări

- I2C Use On The STM32F103R Medium Density Devices - Micromouse Online PDFDocument12 paginiI2C Use On The STM32F103R Medium Density Devices - Micromouse Online PDFNguyễn Văn ThắngÎncă nu există evaluări

- Audit Access Expires Jun 28, 2019: Introducing I CDocument5 paginiAudit Access Expires Jun 28, 2019: Introducing I Czaheeruddin_mohdÎncă nu există evaluări

- Apb I2c InterfaceDocument3 paginiApb I2c InterfaceAyushÎncă nu există evaluări

- Snake Robot ReportDocument30 paginiSnake Robot ReportAditya Vidolkar100% (1)

- Serial Interfaces I2C, Spi, I2SDocument37 paginiSerial Interfaces I2C, Spi, I2Seugen lupu100% (2)

- Philips I2c HandbookDocument16 paginiPhilips I2c HandbookEmílio Ferro100% (3)

- I C Eeproms:: General Information? Beyond The Data Sheet? Hardware Recommendations? More Throughput? Battery Life?Document17 paginiI C Eeproms:: General Information? Beyond The Data Sheet? Hardware Recommendations? More Throughput? Battery Life?Luckyman ChiwezaÎncă nu există evaluări

- Design of I2C Protocol: March 2019Document5 paginiDesign of I2C Protocol: March 201921CS185 VISHAL.MÎncă nu există evaluări

- Lab 8 - I2CDocument7 paginiLab 8 - I2CNhi MẫnÎncă nu există evaluări

- I2C/SPI Host Adapter.Document63 paginiI2C/SPI Host Adapter.sruiz7100% (2)

- NodeMCU Based RelayDocument33 paginiNodeMCU Based Relayumer farooq tariqÎncă nu există evaluări

- An Implementation of I2C Slave Interface Using Verilog HDLDocument6 paginiAn Implementation of I2C Slave Interface Using Verilog HDLIJMERÎncă nu există evaluări

- PLC and Arduino Interaction Based On Modbus ProtocolDocument9 paginiPLC and Arduino Interaction Based On Modbus Protocoltoptop chanelÎncă nu există evaluări

- What Is Modbus?: Global Controls ServicesDocument18 paginiWhat Is Modbus?: Global Controls ServicesShahruh RejepbayevÎncă nu există evaluări

- Review: International Journal of Research in Advent TechnologyDocument6 paginiReview: International Journal of Research in Advent TechnologyAman Ullah AmanÎncă nu există evaluări

- FSM Implementation of I2C Protocol and Its Verification Using VerilogDocument3 paginiFSM Implementation of I2C Protocol and Its Verification Using Verilogyogiyogi7474Încă nu există evaluări

- I2C Communication ProtocolDocument34 paginiI2C Communication Protocolyuosef hababaÎncă nu există evaluări

- Inter Integrated Circuit TrainingDocument26 paginiInter Integrated Circuit Trainingsai saiÎncă nu există evaluări

- Internet Connections: Big B or Little B?Document11 paginiInternet Connections: Big B or Little B?ajaycasperÎncă nu există evaluări

- Today: Wired Embedded Networks: Characteristics and Requirements Some Embedded LansDocument25 paginiToday: Wired Embedded Networks: Characteristics and Requirements Some Embedded LansKani MozhiÎncă nu există evaluări

- An Implementation of I2C Slave Interface Using Verilog HDL: JournalDocument6 paginiAn Implementation of I2C Slave Interface Using Verilog HDL: Journalvisu100% (1)

- Designing SPI To I2C Protocol Converter Base On ASIC Technology and Implementing On The FPGA PlatformDocument8 paginiDesigning SPI To I2C Protocol Converter Base On ASIC Technology and Implementing On The FPGA Platformyogiyogi7474Încă nu există evaluări

- Datasheet Interface I C PhilipsDocument101 paginiDatasheet Interface I C PhilipsClovis Rodrigues100% (1)

- Lecture 13Document40 paginiLecture 13Pratik SolankiÎncă nu există evaluări

- COMP600 Spring Lab#1Document3 paginiCOMP600 Spring Lab#1jassica sahiÎncă nu există evaluări

- Serial Interfaces PDFDocument55 paginiSerial Interfaces PDFGaurav GrimReaper Roy100% (1)

- I2c-Apb BridgeDocument6 paginiI2c-Apb BridgeVarun PÎncă nu există evaluări

- I2CDocument6 paginiI2CGovinda RaoÎncă nu există evaluări

- Martinj NCP3101 A9Document3 paginiMartinj NCP3101 A9Jeriel Miguel MartinÎncă nu există evaluări

- Satellite Television Set On Your Computer System, No Decoder, No Membership.20140211.013418Document2 paginiSatellite Television Set On Your Computer System, No Decoder, No Membership.20140211.013418clavevalley9Încă nu există evaluări

- Serial Communication Protocols Part 2: Nasif MDocument26 paginiSerial Communication Protocols Part 2: Nasif MnobodyÎncă nu există evaluări

- Ccna Notes-1 PDFDocument151 paginiCcna Notes-1 PDFDayaÎncă nu există evaluări

- Network Design 2 (IP Connectivity & Routing Protocol)Document74 paginiNetwork Design 2 (IP Connectivity & Routing Protocol)Altayeb AbdulhameedÎncă nu există evaluări

- BCSE2052 - Lab Manual - StudentVerDocument63 paginiBCSE2052 - Lab Manual - StudentVerAniket SharmaÎncă nu există evaluări

- How To Subnet A NetworkDocument8 paginiHow To Subnet A Networkloganathan234Încă nu există evaluări

- Ccna PDFDocument20 paginiCcna PDFhimanshu kumarÎncă nu există evaluări

- STP PDFDocument60 paginiSTP PDFMartyn OlaÎncă nu există evaluări

- CCNA Routing and Switching: © 2008 Cisco Systems, Inc. All Rights Reserved. Cisco Confidential Presentation - IDDocument60 paginiCCNA Routing and Switching: © 2008 Cisco Systems, Inc. All Rights Reserved. Cisco Confidential Presentation - IDMartyn OlaÎncă nu există evaluări

- IPv6 Fundamentals: Learn the Basics of How IPv6 Works, IPv6 Addresses and IPv6 Subnetting: Computer Networking, #2De la EverandIPv6 Fundamentals: Learn the Basics of How IPv6 Works, IPv6 Addresses and IPv6 Subnetting: Computer Networking, #2Evaluare: 4.5 din 5 stele4.5/5 (2)

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionDe la EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionEvaluare: 5 din 5 stele5/5 (4)

- SPANNING TREE PROTOCOL: Most important topic in switchingDe la EverandSPANNING TREE PROTOCOL: Most important topic in switchingÎncă nu există evaluări

- Memory Devices: Address Connections Data Connections Selection Connections Control ConnectionsDocument14 paginiMemory Devices: Address Connections Data Connections Selection Connections Control ConnectionsviruÎncă nu există evaluări

- L L N '/R: 3. Setting and Adjustment of Velocity Control Unit 3.1 Setting and Adjustment of Velocity Control Unit PCBDocument8 paginiL L N '/R: 3. Setting and Adjustment of Velocity Control Unit 3.1 Setting and Adjustment of Velocity Control Unit PCBMohamed Sayed Abdel-khalekÎncă nu există evaluări

- Sony Ta-Fe610r PDFDocument20 paginiSony Ta-Fe610r PDFms4forumÎncă nu există evaluări

- Eg8010 SPWM v2.2 enDocument13 paginiEg8010 SPWM v2.2 enSandeep S50% (2)

- Power Topologies Quick Reference Guide: 5 DpnqpxfsupqpmphjftDocument7 paginiPower Topologies Quick Reference Guide: 5 Dpnqpxfsupqpmphjftdcastrelos2000Încă nu există evaluări

- Mitsubishi F700 VFD Manual-Applied-Japanese DomesticDocument303 paginiMitsubishi F700 VFD Manual-Applied-Japanese DomesticMROstop.comÎncă nu există evaluări

- Battery ChargerDocument43 paginiBattery ChargerAhmed SheirÎncă nu există evaluări

- Isa Cba 1000 ManualDocument29 paginiIsa Cba 1000 ManualYugie OktavianaÎncă nu există evaluări

- DevlistDocument9 paginiDevlistHouman JafarniaÎncă nu există evaluări

- Sencore Tech Tip #129 Learning To Test CRTs With The CR70s Universal AdapterDocument3 paginiSencore Tech Tip #129 Learning To Test CRTs With The CR70s Universal AdaptertwolluverÎncă nu există evaluări

- Instruction CodesDocument35 paginiInstruction Codesanilk_patiÎncă nu există evaluări

- HTFS 200 800P SP2Document0 paginiHTFS 200 800P SP2lxz5101Încă nu există evaluări

- Pages From Cdfi Phase Final Report-3 2Document9 paginiPages From Cdfi Phase Final Report-3 2api-261836656Încă nu există evaluări

- Schematic Diagram - 1 (Main 1 / 2: Amp)Document7 paginiSchematic Diagram - 1 (Main 1 / 2: Amp)api-3703813Încă nu există evaluări

- Bidirectional 12kV To 1.2kV DC-DC Converter For Renewable Energy ApplicationsDocument8 paginiBidirectional 12kV To 1.2kV DC-DC Converter For Renewable Energy ApplicationsJyothiPunemÎncă nu există evaluări

- LCD TV Repair Guide Handbook - 140211 - v1Document45 paginiLCD TV Repair Guide Handbook - 140211 - v1henry200892% (78)

- Experiment No.03: Implementation of Dipole Antenna Using CST Microwave Studio. Objectives: Equipment RequiredDocument9 paginiExperiment No.03: Implementation of Dipole Antenna Using CST Microwave Studio. Objectives: Equipment RequiredM. Ahmad RazaÎncă nu există evaluări

- Panasonic CT 20R6E PDFDocument30 paginiPanasonic CT 20R6E PDFnapoleon_velasc3617Încă nu există evaluări

- TPEL Xiang A High-Efficiency High-Power-Density On-Board Low-Voltage DCDC Converter For EV PDFDocument14 paginiTPEL Xiang A High-Efficiency High-Power-Density On-Board Low-Voltage DCDC Converter For EV PDF21F018 - HARIPRASAD MÎncă nu există evaluări

- Mux & Demux - 19.9Document31 paginiMux & Demux - 19.9j vanishreeÎncă nu există evaluări

- BTT6200 1EJA Data Sheet 10 Infineon 748987 PDFDocument49 paginiBTT6200 1EJA Data Sheet 10 Infineon 748987 PDFGeovanny SanJuanÎncă nu există evaluări

- Users Guide - 4 - 1Document126 paginiUsers Guide - 4 - 1punwireÎncă nu există evaluări

- CH 2: Basic MOS Device PhysicsDocument20 paginiCH 2: Basic MOS Device PhysicsMuhammad FaizanÎncă nu există evaluări

- M O D E L 1 2 0 7 B: Microprocessor Motor Speed ControllersDocument2 paginiM O D E L 1 2 0 7 B: Microprocessor Motor Speed ControllersCristian TeodorescuÎncă nu există evaluări

- Ei Model Test Question BankDocument7 paginiEi Model Test Question BankbcemailidÎncă nu există evaluări

- 1n4148 Foaie CatalogDocument2 pagini1n4148 Foaie CatalogLebar de casaÎncă nu există evaluări

- 1.adc DacDocument35 pagini1.adc DacGopinathan MÎncă nu există evaluări

- Chenming Hu Ch1 SlidesDocument34 paginiChenming Hu Ch1 Slides詹浩正Încă nu există evaluări

- Tutorial 5Document2 paginiTutorial 5xfgdgfÎncă nu există evaluări

- Msi ms-1681 cr620 SCH PDFDocument45 paginiMsi ms-1681 cr620 SCH PDFkamil_yilmaz_6Încă nu există evaluări