Documente Academic

Documente Profesional

Documente Cultură

Emt

Încărcat de

Raj SharmaDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Emt

Încărcat de

Raj SharmaDrepturi de autor:

Formate disponibile

ELECTRONICS & COMMUNICATION ENGINEERING

1. COMMON EMITTER AMPLIFIER

Aim

1. Design a COMMON - EMITTER amplifier for given specifications.

2. Simulate the designed amplifier.

3. Develop the hard ware for designed amplifier.

4. Compare simulated results with practical results.

Apparatus

S.No Name of The Component/ Specifications Qty

Equipment

Icmax=100mA

1 Transistor (BC-107) PD=300mw 1

Vceo=45V

Vbeo=50V

2 Capacitors(designed values) Electrolytic type, 3

Voltage rating=

1.6v

3 Resistors (designed values) Power rating=0.5w 4

Carbon type

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

Theory: Common Emitter amplifier has the emitter terminal as the common

terminal between input and output terminals. The emitter base junction is forward

biased and collector base junction is reverse biased, so that transistor remains in

active region throughout the operation. When a sinusoidal AC signal is applied at

input terminals of circuit during positive half cycle the forward bias of base emitter

junction VBE is increased resulting in an increase in IB ,The collector current Ic is

increased by β times the increase in IB, VCE is correspondingly decreased. i.e output

voltage gets decreased. Thus in a CE amplifier a positive going signal is converted

into a negative going output signal i.e..180o phase shift is introduced between output

and input signal and it is an amplified version of input signal.

Characteristics of CE amplifier

1. Large current gain (AI )

2. Large voltage gain (AV)

3. Large power gain(AP=AI .AV)

4. Phase shift of 180o

5. Moderate input & output impedances.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 1

ELECTRONICS & COMMUNICATION ENGINEERING

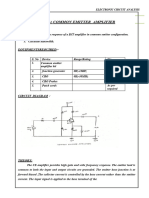

Circuit Diagram

Fig. 1 Common Emitter Amplifier circuit diagram

Design Equations

Given Data

VCC =12V, VCE = 6V, IE =2mA, β=500, S ≤ 5.

1) For fixing the optimum operating point Q, mark the middle of the d.c load line

and the corresponding VCE (Q) and ICQ values are determined.

VCE (Q) = VCC/2

2) Applying Kirchoff’s voltage law to the collector circuit in the diagram

VCC ≥ ICQ(RC+RE) +VCE(Q)

3) By choosing drop across RE as 0.1 VCC

VE = VCC/10

4) In transistor since base current is very small, so IE is approximately equal to

IC ( IE = IC) , IERE

5) RC

6) The voltage across R2 is

VR2 = VBE+IERE

VCC. R2/(R1+R2)

R1/(R1+R2)= ----------------------------- (a)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 2

ELECTRONICS & COMMUNICATION ENGINEERING

7) S = (1+ β) / (1+ βRE/(RE+RB))

5= 101/ (1+(100 X 600/(600+RB)))

RB=

R1R2 / (R1+R2) = ------------------- (b)

From (a) & (b)

R1 = _______ R2 = ________

Capacitor Calculations

To provide low reactances almost short circuit at the operating frequency

f=1KHZ.

XCi = 0.1RB , Xco =0.1 RC, XcE =0.1 RE

Standard values of Resistors and capacitors R1_____, R2=____ RC=_____, RE=____,

Ci = Co = _______, CE=______

Procedure

1. Connect the circuit as per the circuit diagram Fig. 1.

2. Apply the supply voltage , VCC=12V

3. Make sure that the transistor is operating point in active region by keeping

VCE half of VCC.

4. Now feed an ac signal of 20mV at the input of the amplifier with different

frequencies ranging from 100HZ to 300 MHZ and measure the amplifier

output voltage.

5. Now calculate the gain in decibels at various input signal frequencies.

6. Draw a graph with frequencies on X-axis and gain in dbs on Y-axis. From

the graph calculate Bandwidth.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 3

ELECTRONICS & COMMUNICATION ENGINEERING

Tabular form

Simulation

Input AC voltage, ______ mV (peak-peak)

Frequency Output Voltage(Vo) Gain in decibels

S.No

(HZ) (Volts-p-p) AV=20 log (Vo / Vi)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Practical

Input AC voltage, VI= _____ mV (peak-peak)

Output Voltage (Vo) Gain in decibels

S.No Frequency (HZ)

(Volts-p-p) AV=20 log (Vo/ VI)

1

2

3

4

5

6

7

8

9

10

11

12

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 4

ELECTRONICS & COMMUNICATION ENGINEERING

Model graph

Observations

Simulated Practical

Maximum gain (Av) =

Lower cutoff frequency (FL) =

Upper cutoff frequency (FH) =

Band width (B.W) = (FH – FL) =

Gain bandwidth product = Av (B.W) =

Precautions

1. Connections must be given very carefully.

2. Readings should be noted without any parallax error.

3. The applied voltage, current should not exceed the maximum rating of the

given transistor.

Inferences

Result

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 5

ELECTRONICS & COMMUNICATION ENGINEERING

Questions

1. What are the characteristics of C.E amplifier?

2. What is the main application of CE amplifier?

3. What is meant by Bandwidth of an amplifier?

4. Find the phase relation b/w input and output?

5. Measure Ri, RO and Ai of a circuit?

6. Define operating point?

7. Proof for the circuit/BJT is in active region operation?

8. Which component in the circuit effects the gain and bandwidth of an amplifer?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 6

ELECTRONICS & COMMUNICATION ENGINEERING

2. COMMON COLLECTOR AMPLIFIER

Aim

1. To design a COMMON – COLLECTOR amplifier for given specifications.

2. Simulate the designed amplifier.

3. Develop the hard ware for designed amplifier.

4. Compare simulated results with practical results.

Apparatus

S.No Name of The Component/ Specifications Qty

Equipment

Icmax=100mA

1 Transistor (BC-107) PD=300mw 1

Vceo=45V

Vbeo=50V

2 Capacitors(designed values) Electrolytic type, 3

Voltage rating=

1.6v

3 Resistors (designed values) Power rating=0.5w 4

Carbon type

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

Theory

Common Collector amplifier has the collector terminal as the common terminal

between input and output terminals. The emitter base junction is forward biased and

collector base junction is reverse biased, so that transistor remains in active region

throughout the operation. The collector base junction acts as input and emitter base

junction acts as output. Thus the output taken across the emitter, it exactly follows

the input voltage variation. Hence it is named as emitter follower. An external load

resistor RL is capacitor coupled to the emitter terminal of the transistor. Bias voltage

VB is derived from Vcc by means of potential divider R 1 and R 2 .So circuit employs

emitter current bias. No resistor is connected in series with the transistor collector

terminal, and no emitter bypass capacitor is employed. The capacitors C 1 and C 2

acts as input and output coupling capacitors.CC-amplifier circuit provides current

gain and power gain but no voltage gain. It has high input impedance and very low

output impedance. The voltage gain of emitter follower is unity, thus it is used as

buffer amplifier. It is also used as impedance matching network.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 7

ELECTRONICS & COMMUNICATION ENGINEERING

Characteristics of CC amplifier

1. High input impedance

2. Low output impedance

3. High current gain(Ai)

4. Large power gain(AP=AI .AV)

5. Voltage gain is unity.

Circuit Diagram

Fig. 1 Common Collector Amplifier Circuit Diagram

Design Equations

Given Data:

VCC =12V, IE =2mA, β=500, S ≤ 5,f=1KHZ

1. For fixing the optimum operating point Q, mark the middle of the d.c load

line and the corresponding VCE (Q) and ICQ values are determined.

VCE (Q) = VCC/2 =

2. Applying Kirchoff’s voltage law to the collector circuit in the diagram

VCC ≥ IERE +VCE(Q)

RE=

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 8

ELECTRONICS & COMMUNICATION ENGINEERING

3. S = (1+ β) / (1+ βRE/(RE+RB))

RB=

RB = R1R2 / (R1+R2) =

4. VR2 =VBE+VE =0.7+IERE

VR2=

5. VR2= Vcc (R2)/(R1+R2)

R2/(R1+R2)=

R1=

R2=

Capacitor Calculations

To provide low reactances almost short circuit at the operating frequency

f=1KHZ.

XCi = 0.1RB

6. XCi =

Ci =

7. Xco = RE/10

Co =1/ (2πfXco)=

Procedure

1. Connect the circuit as per the circuit diagram Fig. 1.

2. Apply the supply voltage , VCC=12V

3. Make sure that the transistor is operating point in active region by keeping

VCE half of VCC.

4. Now feed an ac signal of 1V at the input of the amplifier with different

frequencies ranging from 100HZ to 300 MHZ and measure the amplifier

output voltage.

5. Now calculate the gain in decibels at various input signal frequencies.

6. Draw a graph with frequencies on X-axis and gain in dbs on Y-axis. From

the graph calculate Bandwidth.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 9

ELECTRONICS & COMMUNICATION ENGINEERING

Tabular form

Simulation

Input AC voltage, VI= ______ V (peak-peak)

Frequency Output Voltage(Vo) Gain in decibels

S.No

(HZ) (Volts-p-p) AV=20 log (Vo / Vi)

Practical

Input AC voltage, VI= ______ V (peak-peak)

Output Voltage (Vo) Gain in decibels

S.No Frequency (HZ)

(Volts-p-p) AV=20 log (Vo/ VI)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 10

ELECTRONICS & COMMUNICATION ENGINEERING

Model graph

Observations

Simulated Practical

Maximum gain (Av)

Lower cutoff frequency (FL)

Upper cutoff frequency (FH)

Band width (B.W) = (FH – FL)

Gain bandwidth product = Av (B.W)

Precautions

1. Connections must be given very carefully.

2. Readings should be noted without any parallax error.

3. The applied voltage, current should not exceed the maximum rating of

the given transistor.

Inferences:

Result .

Questions

1. What are the characteristics of CC amplifier?

2. What is the main application of CC amplifier?

3. What is meant by Bandwidth of an amplifier?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 11

ELECTRONICS & COMMUNICATION ENGINEERING

3. TWO STAGE RC COUPLED AMPLIFIER

Aim:

1. Design two stage RC coupled amplifier for given specifications.

2. Simulate the designed amplifier.

3. Develop the hard ware for designed amplifier.

4. Compare practical results with theoretical results.

Apparatus

S.No Name of The Specifications Qty

Component/equipment

1 Transistor (BC-107) Icmax=100mA

PD=300mw 02

Vceo=45V

Vbeo=50V

2 Capacitors(designed values) Electrolytic type 05

Voltage rating= 1.6v

3 Resistors (designed values) Power rating=0.5w 09

Carbon type

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

Theory

When two amplifiers are connected, in such a way that the output signal of

first serves as the input signal of second, the amplifiers are said to be connected in

cascade. Cascading is done to increase the gain of the amplifier.

Each stage of the cascade amplifier should be biased at its designed

level. It is possible to design a Multistage cascade in which each stage is separately

biased and coupled to the adjacent stage using blocking or coupling capacitors. In

this circuit each of the two capacitors c1 & c2 isolate the separate bias network by

acting as open circuits to dc and allow only signals of sufficient high frequency to

pass through cascade.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 12

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig. 1 Two Stage Common Emitter Amplifier Circuit Diagram.

Design equations

Given Data:

hfe1 = hfe2= 200, RL =10Ω,IE1 = IE2 =1mA, s1 = s2 =8, f=100HZ, VCC=12v

1) For fixing the optimum operating point Q, mark the middle of the d.c load line

and the corresponding VCE (Q) and ICQ values are determined.

VCE (Q) = VCC/2

2) By choosing drop across RE as 0.1 VCC

VE = VCC/10

3) In transistor since base current is very small, so IE is approximately equal to

IC ( IE = IC) , IERE = ; ICRE =

RE = VE / IE =

4) Applying Kirchoff’s voltage law to the collector circuit in the diagram

RC = (VCC – VCE – VE) / IC = (

5) The voltage across R2 is

VBB = VCC * R2 / (R1 + R2) --------------- (1)

VBB = VBE + IERE -------------------- (2)

Substitute (2) in (1)

1.8 = 12 R2 / (R1+R2)

R2 = 0.1761 R1 ------------------ (a)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 13

ELECTRONICS & COMMUNICATION ENGINEERING

6) S=1+ R1R2/ (R1+R2) RE -----------------(b)

By solving (a) and (b) we get

R1 = _________ R2 = ________

Capacitor calculations:

To provide low reactances almost short circuit at the operating frequency

f=100HZ.

X cE = 0.1RE , Xci =0.1 Zi, Xco =0.001 Z0

7) X cE << RE,

X cE =RE/10

=> CE=

8) XCi=Zi/10 Where Zi=hie//RE =

=> Ci =

9) XCo= ZO/1000

ZO=RL//RC =

=> CO =

Standard values

R11= R12= R1=______, R21 = R22 =R2 = _______, RE1 =RE2 =RE =_______

RC1 =RC2 =RC=_______, RL=______,Ci=_____,CC= _____,CE = _____ C0= _______

Procedure

1. Connect the circuit as per the circuit diagram Fig. 1.

2. Apply supply voltage, Vcc= 12V.

3. Make sure that the transistor is operating in active region by keeping Vce half

of Vcc.

4. Now feed an ac signal of 20mV at the input of the amplifier with different

frequencies ranging from 100Hz to 1MHz and measure the amplifier output

voltage, Vo.

5. Now calculate the gain in db at various input signal frequencies.

6. Draw a graph with frequencies on X- axis and gain in db on Y- axis. From

graph calculate bandwidth.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 14

ELECTRONICS & COMMUNICATION ENGINEERING

Tabular Form

Simulation

Input AC voltage, Vi = ______mV (peak-peak)

Output voltage Vo Gain in decibels

S.No Frequency (Hz)

(mv) (peak-peak) AV=20 log (Vo / Vi)

Practical

Input AC voltage, Vi = _______mV (peak-peak)

Output voltage Vo Gain in decibels

S.No Frequency (Hz)

(mv) (peak-peak) AV=20 log (Vo / Vi)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 15

ELECTRONICS & COMMUNICATION ENGINEERING

Observations

Simulation Practical

Maximum gain (Av)

Lower cutoff frequency (fL)

Upper cutoff frequency (FH)

Band width (B.W) = (FH – FL)

Gain bandwidth product = Av (B.W)

Model graph

Precautions

1. Connections must be done very carefully.

2. Readings should be noted without any parallax error.

3. The applied voltage and current should not exceed the maximum

ratings of the given transistor.

Inferences

Result

Questions

1. Why RC coupled amplifiers widely used as voltage amplifiers?

2. Why the voltage gain of RC coupled amplifier falls in low frequency range?

3. Why the voltage gain of RC coupled amplifier falls at high frequency range?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 16

ELECTRONICS & COMMUNICATION ENGINEERING

4. WIENBRIDGE OSCILLATOR

Aim

1. Design a WIEN BRIDGE OSCILLATOR for given specifications.

2. Simulate the designed oscillator.

3. Develop the hard ware for designed oscillator.

4. Compare practical results with theoretical results.

Apparatus

S.No Name of The Component/Equipment Specifications Qty

1 Transistor (BC-107) ICMAX=100mA

PD=300mw 2

VCEO=45V

VBEO=50V

2 Capacitors(designed values) Voltage rating= 5

1.6v Electrolytic

type

3 Resistors (designed values) Power 10

rating=0.5w

Carbon type

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

Theory

The circuit diagram of Wien bridge oscillator is given in figure .The circuit

consists of a two stage RC coupled amplifier which provides a phase shift of 360 or

0. A balanced bridged is used as the feedback network which has no need to provide

any additional phase shift. The feedback network consists of lead-lag network(R 1 -C 1

and R 2 -C 2 ) and a voltage divider (R 3 -R 4 ). The lead–lag network provides positive

feedback to the input of first stage and the voltage divider provides a negative

feedback to the emitter of Q 1 .If the bridge is balanced,

R3/R4=(R1-jXc1)/(R2)(-jX2)/(R2-jXc2)).

Where Xc1 and Xc2 are the reactances of the capacitors.

By simplifying and equating the real and imaginary parts on both sides,we get the

frequency of oscillation as,

fo= 1/ ( 2π√R1R2C1C2)

=1/(2πRC), if R1=R2=R3 and C1=C2=C.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 17

ELECTRONICS & COMMUNICATION ENGINEERING

The ratio of R3 to R4 being greater than 2 will provide a sufficient gain for the circuit

to oscillate at the desired frequency. This oscillator is used in commercial audio

signal generator.

Circuit Diagram

Fig. 1 Wienbridge Oscillator Circuit Diagram

Design Equations

Given data:

VCC =15v, VCE =8v, IC=2mA, β=100, VBE =0.6v,

1) Applying Kirchoff’s voltage law to the collector circuit in the diagram

VCC = VCE+ ICRC

Rc = (Vcc -Vce)/Ic

IB= IC/β =

2) Applying Kirchoff’s voltage law to the base circuit in the diagram

Vcc = IBRB+ VBE => Rb =

Current through R5,R6

I1 = 10IB

But I1= Vcc/(R5+ R6)

R5 + R6 =

But V6 = VBE + VE

VE =

V6 =

I1 (R6 )=

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 18

ELECTRONICS & COMMUNICATION ENGINEERING

R6 =

R5 + R6 =

R5=

Ve = IERE=> RE=

XCO=RC/10=(3.5k)/10

f=1KHZ

CO=1/(2πfRC/10)=

CF=

Practical Values

Time period=

%error = (|Theoritical-Practical|/ Theoritical) x100

Procedure

1. Connections are made as per the circuit diagram.

2. Switch on power supply.

3. Connect the CRO at output of the circuit.

4. Adjust potentiometer for distortion free wave form.

5. Measure the output frequency and amplitude on CRO and compare the

theoretical and practical frequencies.

6. Repeat the procedure for different values of capacitor.

Tabular form

Simulation

S.No Amplitude(V) (Peak-Peak) Frequency(KHZ) % Error

Practical

S.No Amplitude(V) Peak- Frequency(KHZ) % Error

peak

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 19

ELECTRONICS & COMMUNICATION ENGINEERING

Model Graph

Inferences

Result .

Questions

1. What is oscillator?

2. What are BHARKHAUSEN conditions of oscillators?

3. Which type of feedback is used in wein bridge oscillator?

4. What is the application of wein bridge oscillator?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 20

ELECTRONICS & COMMUNICATION ENGINEERING

5. RC PHASE SHIFT OSCILLATOR

Aim

1. To design RC phase shift oscillator for given specifications.

2. Simulate the designed circuit.

3. Compare the theoretical and practical values.

Apparatus

S.No Name of The Specifications Qty

Component/equipment

1 Transistor (BC -107) Icmax=100mA

PD=300mw 1

Vceo=45V

Vbeo=50V

2 Capacitors(designed values) Electrolytic type 3

Voltage rating= 1.6v

3 Resistors (designed values) Power rating=0.5w 4

Carbon type

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

Theory

RC phase shift oscillators are more suitable oscillators as they occupy less

space. RC phase shift oscillator can be achieved by two means,

1. RC phase shift oscillator using cascade of high pass filters.

2. RC phase shift oscillator using cascade of low pass filters.

If values of R and C are chosen that every RC section provides a phase shift of 60o.

thus theoretically RC ladder network produces a total phase shift of 1800 between

input and output voltages for the given frequency. Therefore at a specified frequency

fr the total phase shift from base of transistor around and back to the base will be

3600 or 00, there by Barkausen condition of oscillation, the frequency of oscillations is

given by

f=1/2πRC (6+4K)1/2 Where C1=C2=C3=C,

K=RC/R,

R1=R2=R3=R

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 21

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig.1 RC Phase Shift Oscillator Circuit Diagram

Design Equations

Given data: VCC =12v, IC =1mA, β = 100, VBE =0.3v, VCE =8v,f = 1KHZ

1) The d.c current gain is defined as the ratio of collector current (IC) to the base

current (IB) βdc = IC/ IB

IB = IC /β =

2) The voltage across the base resistor is

VCC = VB + VBE = IB RB + VBE

RB =

3) By choosing drop across RE as 0.1 VCC

VRE = VCC / 10 = ICRE

RE =

4) Applying Kirchoff’s voltage law to the collector circuit in the diagram

VCC ≥ ICQ(RC+RE) +VCE(Q)

RC+RE =

RC =

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 22

ELECTRONICS & COMMUNICATION ENGINEERING

Capacitor calculations

To provide low reactances almost short circuit at the operating frequency

f=1KHZ.

XCE = 0.1RE , XcO =0.1 RO

5) XCO= RO/10 , CO=1/(2πf RO) =

6) XcE = RE / 10 ,CE =1/(2πf RE) =

Theoretical Values

Assume f=1k HZ, C=0.01µ F

f=1/(2πRC)((6+4k))1/2 where k=RC/R, R=

Procedure

1. Connections are made as per circuit diagram Fig. 1.

2. Switch on the power supply.

3. Connect the CRO at the output of the circuit and apply supply voltage of

VCC =12v.

4. Compare the simulation frequency and practical frequency values.

5. Plot the graph for amplitude versus frequency.

Observations

Time period, T of the AC signal available at the output =

The frequency of Oscillations, f = 1 / T =

Tabular Form

Simulation

S.NO Amplitude(v) p-p Frequency (KHZ) % Error

Practical

S.NO Amplitude(v) p-p Frequency (KHZ) % Error

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 23

ELECTRONICS & COMMUNICATION ENGINEERING

Model Graph

Precautions

1. Connections must be done very carefully.

2. Readings should be noted without any parallax error.

3. The applied Voltage and current should not exceed the maximum ratings of the

given transistor.

Inferences

Result:

Questions

1. Which type of feedback is used in RC phase shift oscillator?

2. How many RC networks are used in RC phase shift oscillator?

3. What must be the gain of the internal amplifier in the general RC phase shift

oscillator?

4. What is the effect of VCC, R & C values on output?

5. How to vary the frequency in worse and fine ways?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 24

ELECTRONICS & COMMUNICATION ENGINEERING

6. CLASS-A POWER AMPLIFIER

Aim

1. Design a class-A inductor coupled power amplifier to deliver 4W power to 10

Ohms load resistor.

2. Simulate the designed amplifier.

3. Develop the hard ware for designed amplifier.

4 Compare practical results with theoretical results.

Apparatus

S.No Name of the Component Specifications Qty

/equipment

1 Power transistor (BD139) VCE =60V, VBE = 100V 1

IC = 100mA hfe = 40 to160

2 Resistor (designed values) Power rating=0.5w 4

Carbon type

3 Capacitors(designed values) Electrolytic type Voltage 3

rating= 1.6v

4 Function Generator 0 -1MHZ 1

5 Cathode Ray Oscilloscope 20MHZ 1

6 Regulated Power Supply 0-30V,1Amp 1

7 Inductor(designed values) Operating 1

temperature=ambient

Theory

The power amplifier is said to be class A amplifier if the Q point is selected in

such a way that output signal is obtained for a full input cycle. For class A power

amplifier position of Q point is at the centre of mid point of load line. For all values of

input signals the transistor remains in the active region and never enters into the cut

off or saturation region. When an ac signal is applied, the collector current flows for

3600 of the input cycle. In other words, the angle of collector current flow is 3600 i.e...

One full cycle. Here signal is faithfully reproduced at the output without any distortion.

This is an important feature of class A operation. The efficiency of class A operation

is very low with resistive load and is 25%. This can be increased to 50% by using

inductive load. In the present experiment inductive load is used.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 25

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig. 1 Class-A Power Amplifier Circuit Diagram

Design Equations

Given data: RL= 10Ω, PL max= 4W, f=1KHZ

1) Selection of L:

ωL>>RL

L>>RL/2πfL =

2) Selection of VCC:

The maximum power which can be delivered is obtained for Vm = VCC

(if vmin=0)

PL max ≤ VCC ² /2RL

VCC ² ≥PLmax X 2RL, VCC =

3) Selection of RE:

ICQ = (PC max /RL)1/2 =

ICQ=VCC/(Rac+Rdc) where Rac= RL, Rdc= RE

ICQ=VCC/(RL+RE) , RE = (VCC /ICQ) - RL , RE =

4) Selection of biasing resisters R1 & R2:

VBB= VBE+VE

VE = ICQ*RE =

VBB=

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 26

ELECTRONICS & COMMUNICATION ENGINEERING

The voltage across R2 is

VBB=VCCR2/(R1+R2)

RB= R1R2/(R1+R2)

R1 =______ , R2 , = _________

Capacitor calculations

To provide low reactances almost short circuit at the operating frequency

f=1KHZ. XCE = 0.01RE , Xci =0.1 RB ,Xc0 =0.1 RL

5) Selection of CE:

XcE= RE/100 CE = _______

6) Selection of Ci& C0:

Xci≈RB/10=

Ci = _______

7) Xc0≈RL/10 =____, C0 = _______

Procedure

1. Connect the circuit as shown Fig. 1 and supply the required DC voltage 2.

Feed an AC signal at the input and keep the frequency at1 KHZ and

amplitude 5V.Connect a power o/p meter at the o/p.

2. Change the o/p impedance in steps for each value of impedance and note

down the o/p power.

3. Plot a graph between o/p power and load impedance. From this graph find

the impedance for which the o/p power is maximum. This is the value of

optimum load.

4. Select load impedance which is equal to 0V or near about the optimum load.

See the wave form of the o/p of the C.R.O.

5. Calculate the power sensitivity at a maximum power o/p using the relation.

Power sensitivity = output power / (rms value of the signal)2

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 27

ELECTRONICS & COMMUNICATION ENGINEERING

Tabular Form

Simulation

Input Power=VCC x ICQ=_______

S.No RL(Ohm) D.C.Input Output Power Efficiency =

Power Pin (W) Pout (W)

pout/pin*100(%)

Practical

S.No RL(Ohm) D.C Input A.C output η=(Pac)/(Pdc)*100

Power Pin (W) Power Pout (W)

Model Graph

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 28

ELECTRONICS & COMMUNICATION ENGINEERING

Precautions

1. Connections should be done care fully.

2. Take the readings with out any parallax error.

Inferences

Result

Questions

1. What is power amplifier?

2. Why power amplifiers are called as large signal amplifiers?

3. What is the maximum collector efficiency of transformer load class A

power amplifier?

4. What is the maximum collector efficiency of resistive load class A

power amplifier?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 29

ELECTRONICS & COMMUNICATION ENGINEERING

7. CLASS-B POWER AMPLIFIER

Aim

1. Design a class B push pull amplifier to deliver 5W to 10 Ohm load resistor

2. Simulate the designed regulator.

3. Develop the hardware for designed Regulator.

4. Compare the practical values with theoretical values.

Apparatus

S.No Name of the component Specifications Qty

/Equipment

1 Power transistors Pcmax =12.5W 2

BD 138, BD139 Icmax=1.5A

Vcemax=80V,hfe=100

2 I/P Transformer Turns Ratio 1:1 1

3 O/P Transformer Turns Ratio 4:1 1

4 Resistor (designed values) Power rating=0.5w 4

Carbon type

5 Function Generator 0 -1MHZ 1

6 Cathode Ray Oscilloscope 20MHZ 1

7 Regulated Power Supply 0-30V,1Amp 1

Theory

The two transistors are biased to work in class-B operation. This increases

the power efficiency of the circuit. When the signal is applied, the transformer Q1

works as a phase splitter. It produces two signals (for the two transistors) which are

equal in magnitude but opposite in phase. During positive half-cycle of the input

signal, the base of the transistor Q1 is driven positive. So, it will be in the conducting

state. The base of the transistor Q 2 is driven negative. It remains cut-off. Current ic1

flows, but ic2 is zero. During the negative half cycle of the input signal, the opposite

happens. Q 2 conducts, but Q 1 does not.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 30

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit diagram

Fig.1 Class-B Power Amplifier Circuit Diagram

Design Equations

Given data: PL (max) = 5W, PC (max) = 12.5 W, IC (max) = 1.5A, V CC (max) = 80V,

S=8

1. Selection of Vcc:

PL (max) =VCC X IC (MAX) / 2

Vcc=

2. Selection of RL

IC (max) =VCC / N ² X RL

RL =______

3. Selection of RE :

RE << RL

RE=RL/10

4. Selection of R1 & R2:

VE= ICQ X RE

ICQ=PC (max) / VCE

S=RB // RE=R1 // R2 // RE

R2 =

VE = Vcc X R1 / (R1+R2)

R1 = ______ R2= _______

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 31

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the circuit as per the circuit diagram shown in Fig. 1

2. Connect the required supply from the regulated R.P.S

3. Feed the AC signal at the I/p and keep the frequency at 1 KHz . connect the

power o/p meter at the o/p. Change the o/p impedance in steps for each

value of impedance and note down the o/p power.

4. Plot a graph between o/p power and load impedance. From this graph find

the impedance for which the output power is maximum. This is the value of

optimum load.

5. Select load impedance which is equal to optimum load. See the wave form of

the output on C.R.O.

6. Calculate the conversion efficiency..

Tabular form

Simulation

S.NO Load resistance Pac (W) Pdc (W) % η = ((Pac)

RL (Ohms) / (Pdc))*100

Practical

S.NO Load resistance Pac (W) Pdc (W) % η = ((Pac)

RL (Ohms) / (Pdc))*100

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 32

ELECTRONICS & COMMUNICATION ENGINEERING

Model Graph

Precautions

1. Connections should be made carefully.

2. Take the readings without parallax error.

Inferences

Result

Questions

1. What are the advantages of class B power amplifier?

2. What is the period of conduction in class B power amplifier?

3. How is the cross over distortion eliminated?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 33

ELECTRONICS & COMMUNICATION ENGINEERING

8. CLASS B COMPLEMENTARY SYMMETRY

POWER AMPLIFIER

Aim

1. Design a complementary symmetry power amplifier to deliver maximum

power to 10 Ohm load resistor.

2. Simulate the design circuit.

3. Develop the hard ware for design circuit.

4. Compare the practical results with theoretical values.

Apparatus

Sl.No Name of the Component Specifications Qty

/equipment

1 Power transistor (BD139) VCE =60V VBE = 100V 1

IC = 100mA hfe = 40 -160

2 Resistor (designed values) Power rating=0.5w 4

Carbon type

3 Capacitors(designed values) Electrolytic type Voltage 3

rating= 1.6v

4 Inductor(designed values) Operating temp =ambient 1

5 Function Generator 0 -1MHZ 1

6 Cathode Ray Oscilloscope 20MHZ 1

7 Regulated Power Supply 0-30V,1Amp 1

Theory

In complementary symmetry class B power amplifier one is p-n-p and other

transistor is n-p-n. In the positive half cycle of input signal the transistor Q1 gets

driven into active region and starts conducting. The same signal gets applied to the

base of the Q2. it ,remains in off condition, during the positive half cycle. During the

negative half cycle of the signal the transistor Q2 p-n-p gets biased into conduction.

While Q1 gets driven into cut off region. Hence only Q2 conducts during negative half

cycle of the input, producing negative half cycle across the load.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 34

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig. 1 Class-B Complementary Symmetry Power Amplifier Circuit Diagram

Design Equations:

Given data: PL (MAX) =5 W, RL= 10Ω, f = 1KHZ

1. Selection of VCC:-

PL (MAX) = VCC ² / 2RL

VCC ² = PL (MAX) 2RL

VCC =

2. Selection R and RB:-

VBB = VBE = 0.6V , assume R = 150Ω

VBB=VCC.R / (R+RB)

RB =

Capacitor calculations

To provide low reactances almost short circuit at the operating frequency

f=1KHZ.

XCC1 = XCC2 = (R \\ RB) / 10

CC1 = CC2 = 1/ 2 π f XCC1 =

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 35

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the circuit diagram as shown in Fig. 1 and supply the required

DC supply.

2. Apply the AC signal at the input and keep the frequency at 1 KHz and

connect the power o/p meter at the output. Change the Load resistance in

steps for each value of impedance and note down the output power.

3. Plot the graph between o/p power and load impedance. From this graph

find the impedance for which the output power is maximum. This is the

value of optimum load.

4. Select load impedance which is equal to 0V or near about the optimum

load. See the wave form of the o/p of the C.R.O.

5. Calculate the power sensitivity at a maximum power o/p using the relation.

Tabular Form

Simulation

Input power = 2 VCC2 / (πRL) =

S.No O/P Impedance (Ω) I/P Power O/P N=(Po)/( Pi)*100

(pi) (W) Power(po)

(W)

Practical

Input power = _____mW

S.NO O/P Impedance I/P Power(pi ) O/P Power(po) η=(Pac)/(Pdc)*100

(Ω) (mW) (mW)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 36

ELECTRONICS & COMMUNICATION ENGINEERING

Model Graph

Precautions

1. Connections should be made care fully.

2. Take the readings with out parallax error.

3. Avoid loose connections.

4. Simulation switch must be off while changing the values.

Inferences

Result

.

Questions

1. What is the use of Heat sinks in power amplifiers?

2. What is cross over distortion?

3. What is the maximum efficiency of Class B complementary symmetry

Power amplifier?

4. What are the advantages of Class B complementary symmetry amplifier?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 37

ELECTRONICS & COMMUNICATION ENGINEERING

9. SINGLE TUNED VOLTAGE AMPLIFIER

Aim

To design a class c tuned voltage amplifier for the input signal frequency of

5 kHz

Apparatus

Sl.No Name of the Specifications Qty

Component / equipment

1 Power transistor Icmax=100mA

pDmax=300mw

Vceo(max)=45v 1

Vcbo(max)=50v

2 capacitor(designed values) Max temp : 65c

Electrolytic type 3

capacitor

3 Resistors(designed values) Power rating=0.5w

Carbon type 2

4 Inductors(designed values) Internal resistance=∞ 1

Operating point :

Ambient

5 Function Generator 0 -1MHZ 1

6 Cathode Ray Oscilloscope 20MHZ 1

7 Regulated Power Supply 0-30V,1Amp 1

Theory

In class C amplifier, the Q point and input signal are selected such that the

output signal is obtained for less than a half cycle, for a full wave input. Due to such a

selection of Q point, transistor remains active , for less than a half cycle, For

remaining cycle of input cycle, the transistor remains cut off and no signal is

produced at the output. When a class C amplifier is connected to a parallel tuned

circuit, there fore the output voltage is maximum at the resonant frequency. The

resonant frequency for parallel tuned circuit is given by fr = 1/2 Π LC .

Tuned Amplifiers are used at radio frequencies. The amplifier consists of LC

Circuit for tuning certain frequency. The resonant frequency of lc circuit is equal to

input frequency.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 38

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit diagram

Fig. 1 Single Tuned Voltage Amplifier Circuit Diagram

Design equations

Given data:

fr=5KHz , C=0.01µF,RB=1KHz,RL=1MΩ

1. selection of L:

fr = 1/2 Π LC

L=

Capacitor calculations

To provide low reactances almost short circuit at the operating frequency

f=5KHZ.

XC1 = 0.1RB , XC2 =0.1 RL,

2. selection of capacitor c 1 :

XC1=RB / 10

C1=

selection of capacitor c 2 :

Xc2 = RL/10

C2=

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 39

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the circuit as per the circuit diagram shown in Fig. 1.

2. Apply input signal of some fixed amplitude.

3. Set input signal frequency at some frequency (say 100 KHz).

4. Increase the frequency in steps of KHz and observe the output.

5. Measure the output voltage for each value of input frequency.

6. Find the frequency at which maximum output is obtained.

7. Tabulate the readings and find voltage gain.

8. Draw the graph between frequencies vs. gain.

9. Locate two points on either side of the amplitude peak value on the graph at

which the gain is 70.7% of maximum gain.

Tabular Form

Simulation

Input voltage = _____V (peak-peak)

S.No Frequency Output Voltage (Vo) Gain in dB AV=20

(KHZ) (peak-peak) volts log (Vo / Vi)

Practical

Input voltage = _____V (peak-peak)

S. No Frequency Output Voltage (Vo) Gain in dB =

(KHZ) (volts p-p) 20log (Vo/Vi)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 40

ELECTRONICS & COMMUNICATION ENGINEERING

Model graph

Precautions

1. Connections should be made care fully.

2. Take the readings with out parallax error

Inferences

Result

Questions

1. What are the applications of Tuned amplifiers?

2. What are the requirements of tuned amplifiers?

3. What is Q-factor?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 41

ELECTRONICS & COMMUNICATION ENGINEERING

10. SERIES VOLTAGE REGULATOR

Aim

1. Design series voltage regulator to operate on supply of 15v.

2. Simulate the design of regulator.

3. Develop the hardware for design of voltage regulator.

4. Compare the practical results with theoretical results.

Apparatu:

S.No Name of the Specifications Qty

component/equipment

1 Zener diode (Bz6.5) Vz=6.5v 1

2 Transistors (BC 107) I c max =100ma, 1

VCEO =45v,

Pd(min) =300mw

3 Resistors(designed values) Power dissipation=0.5w 1

Carbon type Tolerance ±5%

4 Regulated power supply 0-30 V,1Amp 1

Theory

A regulator is an electronic circuit which maintains a constant output irrespective

of change in input voltage, load resistance and change in temperature. Series

voltage regulator is one type of regulator. If in a voltage regulator circuit , the control

element is connected in series with the load ,then the circuit is called series voltage

regulator circuit. The unregulated d.c voltage is the input to the circuit. The control

element controls the input voltage, that gets to the output. The sampling circuit

provides the necessary feed back signal. The comparator circuit compares the feed

back with the reference voltage to generate appropriate control signal. In a

transistorized series feedback type regulator the output voltage is given by

Vo = (1+R1/R2) (VBE2+Vz)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 42

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig. 1 Series Voltage Regulator Circuit Diagram

Design Equations

Given data

VL= 9V, IL = 40mA, IZ = 1mA, VZ = 6.5V Vi =15V, IB =1mA, hfe=100

1. Assume the current flowing through the resistor R1 & R3 is 1/10 of the IL

I1=I3=IL/10 =40mA / 10 =

2. IE1=I1+I3+IL =

3. RL=VL/IL = 9/(40 X 10-3) =

4. VO=VL=R3I3+VZ

R3=VL-VZ/I3 =

5. R1I1+VBE2+VZ=VO

R1=VO-(VBE2+VZ)/I1 =

4 R2I2 = VBE2 + VZ

hfe = 100, IC2 =

5 I2 = I1-IB2 ( Since hfe = IC2/IB2 )

I2=

6 I4= IB1 + IC2

IB1 = IC1 / hfe1 (IC1 = IE1)

I4 = 3

7 Vi = I4R4 + VBE1 + VO

R4 =

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 43

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the Circuit diagram as shown in the Fig. 1.

2. Apply the input voltage of 15V

3. Keep the input Voltage constant. Vary the load resistance and measure the

output Voltage and output current

4. Tabulate the readings

5. Plot the graph between Load current versus Load Resistance and Output

Voltage versus Load resistance.

Tabular forms

Simulation

S.No Load resistance Output Voltage (v) Output Current

RL (Ohms) IL (mA)

Practical

S.No Load resistance Output Voltage (v) Output Current

RL (Ohms) IL (mA)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 44

ELECTRONICS & COMMUNICATION ENGINEERING

Model graph

Precautions

1. Connections should me made care fully.

2. Take the readings with out parallax error.

Inferences

Result

Questions

1. What is voltage regulator?

2. Why series regulators are called as linear voltage regulators.

3. What are the applications of series voltage regulator?

4. What are the characteristics of series voltage regulator?

5. How the regulation is obtained in series regulator.

6.What is the effect of output short on circuit operation?

7.What is the range of input voltage for which output is constant?

8. Define line and load regulations?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 45

ELECTRONICS & COMMUNICATION ENGINEERING

11. SHUNT VOLTAGE REGULATOR

Aim

1. Design a Voltage Shunt regulator for a supply of 15V to provide an o/p of 7V with

load current 40 mA.

2. Simulate the designed regulator.

3. Develop the hardware for designed Regulator.

4. Compare the practical values with theoretical values.

Apparatus

S.No Name of the component Specifications Qty

/Equipment

1 Resistors ( designed values) 0.5w , Tolerance ±5% 1

2 Transistor (BC107) ICmax=100mA, Vce = 5V 1

Vceo=45v,Pd(min)=300mw,

hfe=100

3 Zener diode(BZ6.5) 6.5V 1

4 Regulated Power Supply 0-30V,1Amp 1

Theory

The heart of any regulator circuit is a control element. If such a control

element is connected in shunt with the load, the regulator is called shunt voltage

regulator. The unregulated input voltage Vm tries to provide the load current but path

of current is taken by the control element to maintain the constant voltage across the

load. The control element remains constant voltage by shunting the current. Hence

regulated power supply is called voltage shunt regulated circuit. The output voltage

and output current of emitter follower series regulator is

VL = Vz + VBE ------1

IL = VL/RL ------ 2.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 46

ELECTRONICS & COMMUNICATION ENGINEERING

Circuit Diagram

Fig. 1 Shunt Voltage Regulator Circuit Diagram.

Design Equations

Given data : VL= 7V, IL = 40mA, IZ = 1mA, VZ = 6.5V Vi =15V, IB =1mA, hfe=100

1) RL = VL / IL=

2) By applying kirchoff’s current law

IS = IZ+IC+IL ; where IC = hfe IB =100*1mA=100mA

3) Choose the zener breakdown voltage as less (0.5v-1v) than the

required output voltage.

VL= VZ+VBE

VZ = VL- VBE

4) RS = (Vi – VL) / IS =

Procedure

1) Connect the circuit as per the circuit diagram shown in Fig. 1.

2) Keep the input voltage constant vary the load resistance Rl and

measure the o/p voltage and o/p current.

3) Plot the graph between VO and IL.

4) Plot the graph between IL and RL.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 47

ELECTRONICS & COMMUNICATION ENGINEERING

Tabular forms

Simulation

S.No Load resistance RL O/P Voltage Vo Load Current IL

(ohms) (volts) (mA)

Practical

S.No Load resistance RL O/P Voltage Vo Load Current IL

(ohms) (volts) (mA)

Model Graph

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 48

ELECTRONICS & COMMUNICATION ENGINEERING

Precautions

1. Connections should me made care fully.

2. Take the readings with out parallax error.

3. Avoid loose connections

Inferences

Result

Questions

1. What are the applications of shunt voltage regulator?

2. What are the characteristics of shunt voltage regulator?

3. How is the regulation obtained in shunt regulator?

4. What is the effect of output short on circuit operation?

5.What is the range of input voltage for which output is constant?

6.Define line and load regulations?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 49

ELECTRONICS & COMMUNICATION ENGINEERING

PULSE AND DIGITAL CIRCUIT

EXPERIMENTS

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 50

ELECTRONICS & COMMUNICATION ENGINEERING

1. LINEAR WAVE SHAPING

Aim

i) To design a low pass RC circuit for the given cutoff frequency and obtain its

frequency response.

ii) To observe the response of the designed low pass RC circuit for the given

square waveform for T<<RC,T=RC and T>>RC.

iii) To design a high pass RC circuit for the given cutoff frequency and obtain

its frequency response.

iv) To observe the response of the designed high pass RC circuit for the given

square waveform for T<<RC,T=RC and T>>RC.

Apparatus Required

Name of the

Specifications Quantity

Component/Equipment

1KΩ 1

Resistors

2.2KΩ,16 KΩ 1

Capacitors 0.01µF 1

CRO 20MHz 1

Function generator 1MHz 1

Theory

A linear network is a network made up of linear elements only. When we transmit

a sinusoidal signal through the linear network it preserves its shape .No other period

signal like square, pulse, ramp and exponential signal preserve its shape when

transmitted through a linear network.

The process whereby the form of a non sinusoidal signal is altered by

transmission through a linear network is called “linear wave shaping”

Low Pass RC Circuit

An ideal low pass circuit is one that allows all the input frequencies below a

frequency called cutoff frequency f c and attenuates all those above this frequency.

A practical low pass circuit as shown in (Fig.1)

At zero frequency the reactance of the capacitor is infinity(because the capacitor

acts as an open circuit) so the entire input is appear at the output ,

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 51

ELECTRONICS & COMMUNICATION ENGINEERING

i.e .the input is transmitted to output with zero attenuation. So the output is same as

input. So the gain is unity.

As the frequency increase the capacitor reactance (Xc=1/2πfC) decrease and so

the output decreases. At very high frequencies the capacitor virtually acts as a short

–circuit and the out becomes zero. So the circuit is called “Low pass filter”.

High Pass RC Circuit

An ideal high pass circuit is one that allows all the input frequencies above a

frequency called cutoff frequency f c and attenuates all those below the cutoff

frequency. A practical high pass circuit as shown in (Fig.2)

At zero frequency the reactance of the capacitor is infinity (because the capacitor

acts as an open circuit) and so it blocks the entire input and hence the output is zero.

As the frequency increase the capacitor reactance (Xc=1/2πfC) decrease and

hence the output and gain increases. At very high frequencies the capacitor

reactance is very small so the output is equal to input and the gain is equal to 1. So

the circuit is called “High pass filter”.

Circuit Diagram

Fig. 1 Low Pass RC Circuit

Fig. 2 High Pass RC Circuit

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 52

ELECTRONICS & COMMUNICATION ENGINEERING

Design equations

f=1/2πRC

for the given cutoff frequency choose R value and calculate C

Procedure

A) Frequency response characteristics

1 .Connect the circuit as shown in Fig.1 and apply a sinusoidal signal of

amplitude of 2V p-p as input.

2. Vary the frequency of input signal in suitable steps of 100 Hz to 1 MHz and

measure the peak to peak amplitude of output signal.

3. Obtain frequency response characteristics of the circuit by calculating the gain

at each frequency and plotting gain in dB vs frequency in hertzs.

4. Find the cut off frequency fc by noting the value of f at 3 dB down from the

maximum gain

B) Output response

If the time constant of the circuit RC= 0.0198 ms

1. Apply a square wave of 2v p-p amplitude as input.

2. Adjust the time period of the waveform so that T>>RC, T=RC, T<<RC and observe

the output in each case.

3. Draw the input and output wave forms for different cases.

Readings

Table 1 Low Pass RC Circuit

Input Voltage, Vi=_____ V(p-p)

Frequency O/P Voltage, Vo Gain = 20log(Vo/Vi)

S.No

(Hz) (V) (dB)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 53

ELECTRONICS & COMMUNICATION ENGINEERING

Table 2 High Pass RC Circuit

Input Voltage, Vi=______ V(p-p)

Frequency O/P Voltage, Vo Gain = 20log(Vo/Vi)

S.No

(Hz) (V) (dB)

Model Graphs and Wave forms

Fig. 5 Output response of Low Pass RC circuit for different time constants

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 54

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 6 Output response of high Pass RC circuit for different time constants

Precautions

1. Connections should be made carefully.

2. Verify the circuit connections before giving supply.

3. Take readings without any parallax error.

Result:

Inference

Questions

1. Define linear wave shaping?

2. When does the low pass circuit act as integrator?

3. When does the high pass circuit acts as a differentiator?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 55

ELECTRONICS & COMMUNICATION ENGINEERING

2. NON LINEAR WAVE SHAPPING-CLIPPERS&

CLAMPERS

Aim

i) To obtain the output and transfer characteristics of various diode clipper

circuits.

ii) To verify the output response of different diode clamping circuits

Apparatus required

Name of the

Component/Equipme Specifications Quantity

nt

Resistors 1KΩ 1

Diode 1N4007 1

CRO 20MHz 1

Function generator 1MHz 1

DC Regulated power 1

0-30V,1A

supply

Theory

The circuits for which the outputs are non-sinusoidal for sinusoidal inputs are called

“Nonlinear wave shaping circuits”. Examples for nonlinear wave shaping circuits are

clipper and clamping circuits.

Clippers

Clipping means cutting or removing a part. The basic action of a clipper circuit is

to remove certain portions of the waveform, above or below certain levels as per the

requirements. Thus the circuits which are used to clip off unwanted portion of the

waveform, without distorting the remaining part of the waveform are called “Clipper

circuits or Clippers”.

The half wave rectifier is the best and simplest type of clipper circuit which clips

off the positive/negative portion of the input signal. The clipper circuits are also called

voltage or current limiters, amplitude sectors or slicers.

The clippers are mainly classified into two types based on level of clipping.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 56

ELECTRONICS & COMMUNICATION ENGINEERING

1) Single level clippers: In this a single diode is used to perform single-ended

limiting at one independent level.

2) Two level clippers: In this a pair of diodes is used to perform double-ended

limiting at two independent levels. A parallel, a series, or a series-parallel

arrangement may be used.

Single level clippers may be

a) series diode clippers with or without reference

b) shunt diode clippers with or without reference

Applications of clippers includes

i) Sine to square wave converters

ii) Voltage comparators

iii) Noise eliminating circuits

Circuit diagrams

Fig. 1 Positive peak clipper with reference voltage, V=2V

Fig. 2 Positive Base Clipper with Reference Voltage, V=2V

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 57

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 3 Negative Base Clipper with Reference Voltage, V=-2V

Fig. 4 Negative peak clipper with reference voltage, V=-2v

Fig. 5 Slicer Circuit

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 58

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the circuit as per circuit diagram shown in fig.1. Obtain a sine wave of

constant amplitude 8Vp-p from function generator and apply as input to the circuit.

2. Observe the output waveform and note down the amplitude at which clipping

occurs.

3. Draw the observed output waveforms.

4. To obtain the transfer characteristics apply dc voltage at input terminals and vary

the voltage insteps of 1V up to the voltage level more than the reference voltage

and note down the corresponding voltages at the output.

5. Plot the transfer characteristics between output and input voltages.

6. Repeat the steps 1 to 5 for all other circuits.

Readings

Table 1 Positive peak clipper: Reference voltage, V=___v

I/p voltage O/p voltage

(v) (v)

Table 2 Positive base clipper: Reference voltage V= ____v

I/p voltage(v) O/p voltage(v)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 59

ELECTRONICS & COMMUNICATION ENGINEERING

Table 3 Negative base clipper: Reference voltage V=___v

I/P voltage(v) O/Pvoltage(v)

Table 4 Negative peak clipper: Reference voltage V= _____v

I/P voltage(v) O/P voltage(v)

Table 5 Slicer Circuit

I/p voltage(v) O/p voltage(v)

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 60

ELECTRONICS & COMMUNICATION ENGINEERING

Theoretical calculations

Positive peak clipper

Vr=2V, Vγ=0.6V

When the diode is forward biased Vo =Vr+ Vγ = 2.6v

When the diode is reverse biased the Vo=Vi

Positive base clipper

Vr=2V, Vγ=0.6V

When the diode is forward biased Vo=Vr –Vγ = 1.4v

When the diode is reverse biased Vo=Vi .

Negative base clipper

Vr=2V, Vγ=0.6V

When the diode is forward biased Vo = -Vr+ Vγ = -1.4v

When the diode is reverse biased Vo=Vi .

Negative peak clipper

Vr=2V, Vγ=0.6V

When the diode is forward biased Vo= -(Vr+ Vγ) =-2.6v

When the diode is reverse biased Vo=Vi .

Slicer

When the diode D1 is forward biased and D2 is reverse biased Vo= Vr+ Vγ

=2.6V

When the diode D2 is forward biased and D2 is reverse biased Vo=-(Vr+ Vγ)

=-2.6V

When the diodes D1 &D2 are reverse biased Vo=Vi .

Model Graphs

Output response Transfer Characteristics

Fig. 6 Positive peak clipper: Reference voltage V=----V

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 61

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 7 Positive base clipper: Reference voltage V=-----V

Fig. 8 Negative base clipper: Reference voltage V=----V

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 62

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 9 Negative peak clipper: Reference voltage V=----V

Fig. 10: Slicer Circuit

Precautions

1. Connections should be made carefully.

2. Verify the circuit before giving supply.

3. Take readings without any parallax error.

Result

Inference

Questions

1. In the fig.1 if reference voltage is 0v then what will be the output?

2. What are the other names for the clippers?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 63

ELECTRONICS & COMMUNICATION ENGINEERING

CLAMPERS

Apparatus Required

Name of the Specifications Quantity

Component/Equipment

Resistors 10KΩ 1

Capacitor 100uF, 100pF 1

Diode 1N4007 1

CRO 20MHz 1

Function generator 1MHz 1

Theory

Clampers

Clamping circuits are the circuits, which are used to clamp or fix the extremity of

a period wave form to some constant reference level Vr .These are also use.d to add a

d.c level as per the requirement to the a.c signals. Capacitor, diode, resistor are the

three basic elements of a clamper circuit.

The Clamping Circuit Theorem

When a signal is transmitted through a capacitive coupling network (RC high –

pass circuit), it looses its dc component, and a clamping circuit may be used to introduce

a dc component by fixing the positive or negative extremity of that waveform to some

reference level. For this reason, the clamping circuit is often referred to as dc restorer

or dc reinserter.

Classification: Basically clampers are classified in to

1. Negative clampers: In negative clamping, the positive extremity of the

waveform is fixed at the reference level and the entire waveform appears below the

reference level, i.e. the output waveform is negatively clamped with reference to the

reference level.

2. Positive clampers: In positive clamping, the negative extremity of the

waveform is fixed at the reference level and the entire waveform appears above the

reference level, i.e. the output waveform is positively clamped with reference to the

reference level.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 64

ELECTRONICS & COMMUNICATION ENGINEERING

The capacitor is essential in clamping circuits. The difference between the

clipping and clamping circuits is that while the clipper clips off an unwanted portion of the

input waveform, the clamper simply clamps the maximum positive or negative peak of

the waveform to a desire level. There will be no distortion of waveform.

Circuit Diagrams

Fig. 11 Positive peak clamping to 0V

Fig. 12 Positive peak clamping to Vr=----

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 65

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 13 Negative peak clamping to Vr=0v

Fig. 14 Negative peak clamping to Vr= -2v

Procedure

1. Connect the circuit as per circuit diagram Fig. 11

2. Obtain a constant amplitude sine wave from function generator of 6 Vp-p, frequency

of 1 KHz and give the signal as input to the circuit.

3. Observe and draw the output waveform and note down the amplitude at which

clamping occurs.

4. Repeat the steps 1 to 3 for all circuits.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 66

ELECTRONICS & COMMUNICATION ENGINEERING

Model waveforms

Fig. 15 Positive peak clamping to 0V:

Fig. 16 Positive peak clamping to Vr=2V

Fig. 17 Negative peak clamping to 0V

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 67

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 18 Negative peak clamping to Vr= -2V

Precautions

1. Connections should be made carefully.

2. Verify the circuit before giving supply.

3. Take readings without any parallax error.

Result

Inference

Questions

1. What is a clamper?

2. Give some practical applications of clamper.

3. What is the purpose of shunt resistance in clamper?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 68

ELECTRONICS & COMMUNICATION ENGINEERING

3. LOGIC GATES WITH DISCRETE COMPONENTS

Aim

To construct the basic and universal gates using discrete components and Verify their

truth tables

Apparatus required

Name of the

Specifications Quantity

Component/Equipment

Transistor BC 107 1

Diode IN4007 1

4.7KΩ 2

Resistors

100KΩ 1

LED - 1

Bread Board - 1

Regulated Power Supply 0-30V, 1A 1

Theory

1. OR-GATE

OR gate has two or more inputs and a single output and it operates in

accordance with the following definitions.

• The output of an OR gate is high if one or more inputs are high. When all the

inputs are low then the output is low.

• If two or more inputs are in high state then the diodes connected to these inputs

conduct and all other diodes remain reverse biased so the output will be high and

OR function is satisfied.

2. AND-GATE

AND gate has two or more inputs and a single output and it operates in

accordance with the following definitions.

• The output of an AND gate is high if all inputs are high.

• If Vin is chosen i.e. more positive than Vcc then all diodes will be conducting upon

a coincidence and the output will be clamped to ‘1’.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 69

ELECTRONICS & COMMUNICATION ENGINEERING

• If Vr is equal to Vcc then all diodes are cut-off and output will raise to the voltage

Vr if not all inputs have same high value then the output of AND gate is equal to

Vi (min0).

3. NOT-GATE

The NOT gate circuit has a single input input and a single input and perform the

operation of negation in accordance with definition, the output of a NOT gate is high if

the input is low and the output is low or zero if the input is high or 1.

4. NOR-GATE

A negation following on OR is called as NOT-OR gate or NOR gate. As shown in

figure if Vo is applied as input signal to the diodes then both diodes are forward biased.

Hence no voltage is applied to emitter base junction and total current is passed through

the LED and it glows which indicate high or one state.

5. NAND-GATE

The NAND gate can be implemented by placing a transistor NOT gate after the

AND gate circuit with diodes. These gates are called diode-transistor logic gates.

If Vo is applied to input of the diode then the diode D1 and D2 will be forward biased.

Hence no voltage applied across base-emitter junction and this junction goes into cut-off

region. Hence total current from source Vce will flow through LED and it flows which

indicate the one state or high state.

Circuit diagrams

Fig. 1 OR GATE

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 70

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 2 AND GATE

Fig. 3 NOT GATE

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 71

ELECTRONICS & COMMUNICATION ENGINEERING

Fig. 4 NOR GATE

Fig. 5 NAND GATE

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 72

ELECTRONICS & COMMUNICATION ENGINEERING

Truth tables

Table 1 AND GATE Table 2 OR GATE

Inputs Output Inputs Output

A B Y=AB A B Y=A+B

0 0 0 0 0 0

1 0 0 1 0 1

0 1 0 0 1 1

1 1 1 1 1 1

Table 3 NOT GATE Table 4 NAND GATE

Input Output Inputs Output

A Y= A B Y=

0 0 1

0 1

1 0 1

1 0 0 1 1

1 1 0

Table 5 NOR GATE

Inputs Output

A B Y=

0 0 1

1 0 0

0 1 0

1 1 0

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 73

ELECTRONICS & COMMUNICATION ENGINEERING

Procedure

1. Connect the circuit as per the circuit diagram Fig.1

2. Apply 5V from RPS for logic 1and 0V for logic 0.

3. Measure the output voltage using digital multimeter and verify the truth table.

4. Repeat the same for all circuits.

Result

Inference

Questions

1. What are the universal gates? Why they are called universal gates?

2. What is the other name of the EX-NOR gate?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 74

ELECTRONICS & COMMUNICATION ENGINEERING

4. BISTABLE MULTIVIBRATOR

Aim

To observe the stable state voltages of Bistable Multivibrator.

Apparatus required

Name of the

Specifications Quantity

Component/Equipment

Transistor BC 107 2

2.2KΩ 2

Resistors

12KΩ 2

Regulated Power Supply 0-30V, 1A 1

Digital multi meter 3 ½ digit display 1

Theory

Multivibrator

Multi means many ; vibrator means oscillator. A circuit which can oscillate at a

number of frequencies is called a Multivibrator. Each multivibrator has two states.

Bistable Multivibrator

A bistable multivibrator has two stable states. Each multivibrator is having

two coupling elements. In bistable multivibrator circuit both the coupling elements are

resistors (i.e. dc couplings). It requires a triggering signal to change from one stable state

to another, and another triggering signal for the reverse transition.

A bistable multivibrator is also called as a multi, Eccles-Jordan circuit, trigger

circuit, scale –of-two toggle circuit, flip-flop, and binary.

Circuit Operation

The circuit diagram of a fixed bias bistable multivibrator using transistors is as

shown in fig. 1. The output of each amplifier is direct coupled to the input of the other

amplifier. In one of the stable states transistor Q1 and Q2 is off and in the other stable

state. Q1 is off and Q2 is on even though the circuit is symmetrical; it is not possible for

the circuit to remain in a stable state with both the transistors conducting simultaneously

and caring equal currents. The reason is that if we assume that both the transistors are

biased equally and are carrying equal currents i1 and i2 suppose there is a minute

fluctuation in the current i1-let us say it increases by a small amount .Then the voltage at

the collector of Q1 decreases. This will result in a decrease in voltage at the base of Q2.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 75

ELECTRONICS & COMMUNICATION ENGINEERING

So Q2 conducts less and i 2 decreases and hence the potential at the collector of q2

increases. This results in an increase in the base potential of Q1. So Q1 conducts still

more and i1 is further increased and the potential at the collector of Q1 is further

decreased, and so on. So the current i1 keeps on increasing and the current i 2 keeps on

decreasing till Q1 goes in to saturation and Q2 goes in to cut-off. This action takes place

because of the regenerative feed –back incorporated into the circuit and will occur only if

the loop gain is greater than one.

Applications of Bistable Multivibrator

1) It is used as a basic memory element

2) It is used to perform many digital operations such as counting, storing of binary

data.

3) It is also used in the generation & processing of pulse type waveform.

.

Circuit Diagram

Fig.1 Bistable Multivibrator

Procedure

1. Connect the circuit as shown in Fig.1

2. Verify the stable state by measuring the voltages at two collectors by using

multimeter.

3. Note down the corresponding base voltages of the same state (say state-1).

4. To change the state, apply negative voltage (say-2v) to the base of on

transistor or positive voltage to the base of transistor (through proper

current limiting resistance).

5. Verify the state by measuring voltages at collector and also note down

voltages at each base.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 76

ELECTRONICS & COMMUNICATION ENGINEERING

Observations

Before Triggering

Q1 Q2

VBE1= VBE2=

VCE1= VCE2=

After Triggering

Q1 Q2

VBE1= VBE2=

VCE1= VCE2=

Precautions

1. Connections should be made carefully.

2. Note down the parameters carefully.

3. The supply voltage levels should not exceed the maximum rating of the transistor.

Inference

Result

Questions

1. What do you mean by a bistable circuit?

2. What are the other names of a bistable multivibrator?

3. What do you mean by triggering signal?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 77

ELECTRONICS & COMMUNICATION ENGINEERING

5. ASTABLE MULTIVIBRATOR

Aim

To observe the ON & OFF states an Astable Multivibrator.

Apparatus required

Name of the

Specifications Quantity

Component/Equipment

Transistor BC 107 2

3.9KΩ 2

Resistors

100KΩ 2

Capacitor 0.01µF 2

Regulated Power Supply 0-30V, 1A 1

Theory

Multivibrator

Multi means many ; vibrator means oscillator. A circuit which can oscillate at a

number of frequencies is called a Multivibrator. Each multivibrator has two states.

Astable Multivibrator

An astable multivibrator has no stable state. And it is having two quasi stable

states. In astable multivibrator circuit both the coupling elements are capacitors (i.e. ac

couplings). And it keeps on switching between these two states by itself. No external

triggering signal is needed. The astable multivibrator cannot remain indefinitely in any

one of the two states .The two amplifier stages of an astable multivibrator are

regenerative across coupled by capacitors. The astable multivibrator may be to

generate a square wave of period,1.38RC. The astable multivibrator circuit is used as a

master oscillator to generate square waves. It is often a basic source of fast waveforms.

It is a free running oscillator. It is called a “Square wave generator”. It is also termed a

“Relaxation oscillator”.

Circuit Operation

The circuit diagram of the collector – coupled astable multivibrator using

transistors as shown in fig.1. The collectors of both the transistors Q1 & Q2 are connected

to the bases of the other transistors through the coupling capacitors C1 & C2. Since both

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 78

ELECTRONICS & COMMUNICATION ENGINEERING

are ac couplings, neither transistor can remain permanently at cut-off. Instead, the circuit

has two quasi-stable states, and it makes periodic transistors between these states.

Hence it is used as a master oscillator. No triggering signal is required for this

multivibrator. The component values are selected such that, the moment it is connected

to the supply, due to supply transients one transistor will go into saturation and the other

into cut-off, and also due to capacitive coupling it keeps on oscillating between its two

quasi stable states.

Applications of Astable Multivibrator

1) It is used in Square wave generators

2) It is also used in voltage to frequency converters.

Circuit Diagram

Fig.1 Astable Multivibrator

Procedure

1. Calculate the theoretical frequency of oscillations of the circuit.

2. Connect the circuit as per the circuit diagram.

3. Observe the voltage wave forms at both collectors of two transistors

simultaneously.

4. Observe the voltage wave forms at each base simultaneously with

corresponding collector voltage.

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 79

ELECTRONICS & COMMUNICATION ENGINEERING

5. Note down the values of wave forms carefully.

6. Compare the theoretical and practical values.

Calculations

Theoretical Values

RC= R1C1+ R2C2

Time Period, T = 1.368RC

= 1.368x100x103x0.01x10-6

= 93 µ sec

Frequency, f = 1/T = 10.75kHz

Model waveforms

Fig. 2 Output response of Astable Multivibrator

Precautions

1. Connections should be made carefully.

2. Readings should be noted without parallax error.

Result

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 80

ELECTRONICS & COMMUNICATION ENGINEERING

Inference

Questions

1.Define stable state ?

2.Define quasi stable state ?

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 81

ELECTRONICS & COMMUNICATION ENGINEERING

6.MONOSTABLE MULTIVIBRATOR

Aim

To observe the stable state and quasi stable state voltages of monostable multivibrator.

Apparatus Required

Name of the

Specifications Quantity

Component/Equipment

BC 107 2

Transistor

1.5KΩ 1

2.2KΩ 2

Resistors

68KΩ 1

1KΩ 1

Capacitor 1µF 2

Diode 0A79 1

CRO 20MHz 1

Function generator 1MHz 1

Regulated Power Supply 0-30V, 1A 1

Theory

Multi means many ; vibrator means oscillator. A circuit which can oscillate at a number of

frequencies is called a Multivibrator. Each multivibrator has two states.

Monostable Multivibrator

A monostable multivibrator on the other hand compared to astable, bistable has

only one stable state, the other state being quasi stable state. Normally the monostable

multivibrator is in stable state and when an externally triggering pulse is applied, it

switches from the stable to the quasi stable state. It remains in the quasi stable state for

a short duration, but automatically reverse switches back to its original stable state

without any triggering pulse.

The monostable multivibrator is also called as ‘one shot’ or ‘uni vibrator’ since

only one triggering signal is required to reverse the original stable state. The duration of

quasi stable state is termed as delay time (or) pulse width (or) gate time. It is denoted

as ‘t’

Circuit Operation

Under quiescent conditions, the monostable multivibrator will be in its stable

state only. A triggering signal is required to induce a transition from the stable state to

ELECTRONIC CIRCUITS AND PULSE AND DIGITAL CIRCUITS 82

ELECTRONICS & COMMUNICATION ENGINEERING

the quasi stable state. Once triggered properly the circuit may remain in its quasi stable

state for a time which is very long compared with the time of transition between the

states, and after that it will return to its original state. No external triggering signal is

required to induce this reverse operation. In monostable multivibrator one coupling

element is a resistor & another coupling element is capacitor.

When triggered, since the circuit returns to its original state by itself after a time T,

it is known as a one shot, single-step, or a univibrator. Since it generates a rectangular

waveform which can be used to gate other circuits, it is also called a gating circuit.

The circuit diagram for monostable multivibrator is as shown in fig 1. The R1C1

combination is differentiating circuit. Let the pulse width of the triggering signal be tp =1

µs.

Circuit diagram