Documente Academic

Documente Profesional

Documente Cultură

PV Inverter

Încărcat de

knighthood4allTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

PV Inverter

Încărcat de

knighthood4allDrepturi de autor:

Formate disponibile

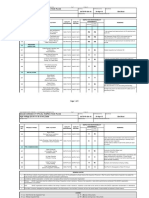

2014 IEEE 3rd Global Conference on Consumer Electronics (GCCE)

Photovoltaic Inverter Employing Auxiliary Circuit to

Synthesize Multilevel Output Voltage

Jin-soo Park Feel-soon Kang, Member, IEEE

Dept. of Control and Instrumentation Eng. Dept. of Electronics and Control Eng.

Hanbat National Univ. Hanbat National Univ.

Daejeon, Korea Daejeon, Korea

lovely2556@naver.com feelsoon@ieee.org

Abstract—It presents a circuit configuration, which can

synthesize a multilevel output voltage for the use of stand-alone II. PROPOSED PV INVERTER EMPLOYING AUXILIARY CIRCUIT

photovoltaic inverter. The proposed system consists of a buck- Fig. 1 shows a circuit diagram for the proposed stand-

boost converter, an auxiliary circuit, and an H-bridge inverter. alone photovoltaic power generating system. It consists of a

The simple auxiliary circuit, which generates a multilevel output buck-boost converter, an auxiliary circuit, an H-bridge inverter,

voltage, configures a switch, three diodes, and two batteries.

and an output filter. The buck-boost converter steps up a low

Thanks to the multilevel output voltage, it can reduce dv/dt stress,

dc solar voltage to a high dc-link voltage with MPPT. An

switching loss, and output filter size. After theoretical analysis,

computer-aided simulation and experimental results carries out auxiliary circuit to synthesize a multilevel consists of a switch,

to verify the validity of the proposed approach. two batteries, and three diodes. When QF turns on, Vdc

connects to a back-end H-bridge inverter. When QF turns off,

Keywords—maximum power point tracking control (MPPT), Vdc1 and Vdc2 in parallel connect to the H-bridge inverter. In

multilevel (ML) inverter, photovoltaic inverter (PV) general PV inverter, a battery pack locates at the dc-link stage

or at the solar cell in parallel. In this viewpoint, the proposed

I. INTRODUCTION auxiliary circuit can reduce voltage stress on a battery,

moreover, it increases the power capacity due to the parallel

Stand-alone photovoltaic power generating system usually supplying when it produces Vdc/2 level. The front-end buck-

employs a dc-link capacitor between a front-end dc-to-dc boost converter works to convert a low dc solar voltage to a

converter and a back-end dc-to-ac inverter. The dc-link high dc-link voltage. So it can use a conventional boost or

capacitor maintains a high dc voltage to feed a suitable voltage buck converter according to the condition of solar cell output

to the inverter, which requires to supply ac voltage for home. voltage. The voltage relationship between input solar cell

Most inverter configures an H-bridge cell controlled by pulse voltage and output dc-link voltage via duty-ratio of QA is

width modulation with high switching frequency. Therefore, it given as

increases dv/dt stress, switching losses, and needs a low pass

filter to get a sinusoidal output voltage with a low total

harmonic distortion resulted in increasing of system size and Vdc = VP DQ A /(1 − DQA ) . (1)

weight. To solve the mentioned above problems, multilevel

inverters are considered for the alternative because a large

number of output voltage levels can mimic a sinusoidal wave

with low switching frequency. So it can reduce the switching

loss, dv/dt stress on switching devices. At the same time, it can

reduce the size of output filter. However, traditional multilevel

inverters need a large number of switching devices, clamping

diodes, flying capacitors, and other components [1], [2].

To minimize the problem, it introduces a PV inverter,

which can produce a multilevel output voltage by adding an Ppv ΔPpv

auxiliary circuit between a buck-boost converter and an H-

bridge inverter. The auxiliary circuit consists of a switch, three

diodes, and two batteries. Maximum power point tracking

algorithm is implemented by the buck-boost converter, and

multilevel output is synthesized by the auxiliary circuit. So the

proposed approach can reduce the switching loss, dv/dt stress,

and output filter size. To verify the validity of the proposed

photovoltaic inverter, simulation and experiment results are

presented with theoretical analysis. Fig. 1. Proposed stend-alone PV inverter generating 5-level output voltage.

978-1-4799-05145-1/14/$31.00 ©2014 IEEE 387

III. SIMULATION AND EXPERIMENT RESULTS

To verify the validity of the proposed approach, we carried

out simulation and experiments. Here, an input voltage Vdc is

set to DC 200[V], PWM switching frequency is set to

10[kHz]. Fig. 4 shows simulation results of inverter output

voltage and drain to source voltage of QF when generating five

(a) (b) output voltage levels. When supplying Vdc level to a load, QF

iterates on and off. During this operation, battery voltage Vdc1

Fig. 2. Operation of auxiliary circuit to generate a multilevel output voltage,

(a) Vdc level, (b) Vdc/2 level. and Vdc2 charge to Vdc/2. When supplying a Vdc/2 level to the

load, QF maintains off state.

Fig. 4. Simulation results for voltage across a switch QF and output voltage of

the inverter before filtering.

ωt

Fig. 5 shows experiment results for the proposed approach.

It shows output voltages before and after filtering. From the

0 π 2π FFT result, we can notice that dv/dt stress has been reduced

below 20 [dB] thanks to the increase of output voltage levels

Fig. 3. Key waveform for generating 5-level output voltage wave. compared to the conventional 3-level PWM inverter.

Fig. 2 shows operational modes when the back-end 200 [V]

inverter generates Vdc and Vdc/2 levels by operating of the vo

-200 [V ]

auxiliary circuit. When QF turns on, Vdc connects to the

inverter. By turning of Q1 and Q4, the inverter output voltage 200 [V ]

v out

becomes a positive Vdc. At the same time, it charges two -200 [V ]

2[m s]

batteries (Vdc1 and Vdc2) connected in series by DH2 as shown in

Fig. 2(a). When QF turns off, paralleled Vdc/2 connects to the v out (FFT )

inverter. In this time, by turning of Q1 and Q4, the inverter 20 [dB ]

output voltage becomes a positive Vdc/2. To produce zero

voltage to the output, Q1 and Q3 (or Q2 and Q4) turn on at the

25[kH z]

same time in order to use voltage cancellation. By iterating on

and off of QF, output voltage of the inverter becomes 5-level Fig. 5. Experimentsl results for output voltage of inverter before and after

as Vdc, Vdc/2, 0, -Vdc/2, -Vdc. PWM switching pattern can be filtering with FFT.

generated by PD (Phase Disposition) modulation technique.

To synthesize five levels on an output voltage wave, one IV. CONCLUSIONS

reference and two carrier waves are used. Hence, the

modulation ratio (Ma) is given by It proposed a PV inverter employing an auxiliary circuit,

which synthesizes a multilevel output voltage to reduce dv/dt

stress, switching loss, and output filter size. Operational

Am modes are explained with theoretical analysis. By simulation

Ma = . (2) and experiment, the validity of the proposed approach was

2 Ac

proved. As a result, we can say that it can be a good candidate

for the alternative to the conventional 3-level PV inverter.

Where Ac is the amplitude of a carrier wave, and Am is

amplitude of a reference wave. QF is controlled by the upper

carrier wave, and the lower carrier wave is used to generate V. REFERENCES

the control signal of Q1 and Q3. Here, the output voltage is

defined by [1] R. Gonzalez, Gubia Eugenio, J. Lopez, and L. Marroyo, “Transformer-

less Single-Phase Multilevel-Based Photovoltaic Inverter,” IEEE Trans.

Ind. Electro., vol. 55, no. 7, pp. 2694-2702, 2008.

vout = M a sin ωt (3) [2] S. Daher, J. Schmid, and F.L.M. Antunes, “Multilevel Inverter

Topologies for Stand-Alone PV Systems,” IEEE Trans. Ind. Electro.,

vol. 55, no. 7, pp. 2703-2712, 2008.

388

S-ar putea să vă placă și

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Double Voltage Step-Up Photovoltaic Microinverter: Diana Lopez, Freddy Flores-Bahamonde, Hugues Renaudineau, Samir KouroDocument6 paginiDouble Voltage Step-Up Photovoltaic Microinverter: Diana Lopez, Freddy Flores-Bahamonde, Hugues Renaudineau, Samir Kourograsia77Încă nu există evaluări

- High-Voltage Pulse Generator Based On Capacitor-Diode Voltage Multiplier Centrally Fed From DC-DC Boost ConverterDocument4 paginiHigh-Voltage Pulse Generator Based On Capacitor-Diode Voltage Multiplier Centrally Fed From DC-DC Boost ConverterNareshÎncă nu există evaluări

- Analysis and Design For 5kw PFC ConverterDocument4 paginiAnalysis and Design For 5kw PFC Converterranjith120198Încă nu există evaluări

- A Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsDocument5 paginiA Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsPhạm Văn TưởngÎncă nu există evaluări

- Non Isolated High Gain DC DC Converters PDFDocument3 paginiNon Isolated High Gain DC DC Converters PDFnkaÎncă nu există evaluări

- ENGG 184.12 Lab Activity 4 - Manlapaz & DolalasDocument3 paginiENGG 184.12 Lab Activity 4 - Manlapaz & DolalasJuan Glicerio C. ManlapazÎncă nu există evaluări

- Main Objective:: Student Name: Ga Name: Matric NumberDocument19 paginiMain Objective:: Student Name: Ga Name: Matric NumberlionÎncă nu există evaluări

- DC DC ConvertersDocument4 paginiDC DC Convertersmurthy237Încă nu există evaluări

- A Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InverterDocument10 paginiA Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InvertererdemsecenÎncă nu există evaluări

- A Modified Quadratic Boost Converter Wit PDFDocument6 paginiA Modified Quadratic Boost Converter Wit PDFkadr sherpaÎncă nu există evaluări

- Chapter 1c (RECTIFIER)Document15 paginiChapter 1c (RECTIFIER)Akmal Amyrul Aizat100% (1)

- A DC-DC Converter With High Voltage Gain and Two Input Boost StagesDocument10 paginiA DC-DC Converter With High Voltage Gain and Two Input Boost Stagesnadeemq_0786Încă nu există evaluări

- Nan Kalayar HlaingDocument5 paginiNan Kalayar HlaingThet TinÎncă nu există evaluări

- Single-Phase Single-Stage Bidirectional Isolated ZVS AC-DC Converter With PFCDocument9 paginiSingle-Phase Single-Stage Bidirectional Isolated ZVS AC-DC Converter With PFCM UMAR ABBASIÎncă nu există evaluări

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocument9 paginiSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDeepak Kumar NayakÎncă nu există evaluări

- Buck BoostDocument11 paginiBuck Boostkima lachgarÎncă nu există evaluări

- Buck RegulatorDocument6 paginiBuck RegulatorBhukya Reethvik RathodÎncă nu există evaluări

- Single Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCDocument8 paginiSingle Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCSamyak ParakhÎncă nu există evaluări

- A Buck-Boost Based DC AC Converter For Residential PV ApplicationsDocument6 paginiA Buck-Boost Based DC AC Converter For Residential PV ApplicationsFrancesco AcunzoÎncă nu există evaluări

- Microcontroller Based DC-DC Cascode Buck-Boost Converter: Sanjeet Kumar Dr. Parsuram ThakuraDocument6 paginiMicrocontroller Based DC-DC Cascode Buck-Boost Converter: Sanjeet Kumar Dr. Parsuram ThakuraNurhayatiÎncă nu există evaluări

- Shyam Course ProjectDocument6 paginiShyam Course ProjectBhukya Reethvik RathodÎncă nu există evaluări

- Power Electronics Interface For PV SysteDocument7 paginiPower Electronics Interface For PV SysteSreepadam PadamÎncă nu există evaluări

- A Novel Buck Boost InverterDocument8 paginiA Novel Buck Boost InverterskrtamilÎncă nu există evaluări

- Solar PDFDocument5 paginiSolar PDFjhony7373Încă nu există evaluări

- Presentation On Single Phase Grid Connected Rooftop IntegratedDocument42 paginiPresentation On Single Phase Grid Connected Rooftop IntegratedmonaÎncă nu există evaluări

- Term Project PowerDocument5 paginiTerm Project PowerThamer SE AlkhamiisÎncă nu există evaluări

- A Zero-Voltage Switching Full-Bridge DC - DC ConverterDocument8 paginiA Zero-Voltage Switching Full-Bridge DC - DC Convertersuresh100% (1)

- New Type Single-Stage DC Ac InverterDocument5 paginiNew Type Single-Stage DC Ac InverterqiwatingÎncă nu există evaluări

- A New Approach For High Efficiency Buck-Boost DC/DC Converters Using Series CompensationDocument7 paginiA New Approach For High Efficiency Buck-Boost DC/DC Converters Using Series CompensationAswin MathewÎncă nu există evaluări

- Photovoltaic Powered DC-DC Boost Converter Based oDocument12 paginiPhotovoltaic Powered DC-DC Boost Converter Based oMeryouma LarbÎncă nu există evaluări

- Inverter Distributed: Controller Generation SystemsDocument7 paginiInverter Distributed: Controller Generation SystemsJohnÎncă nu există evaluări

- A Comparison Between The Buck, Boost and Buck-Boost InvertersDocument6 paginiA Comparison Between The Buck, Boost and Buck-Boost InvertersIndra PratamaÎncă nu există evaluări

- Design, Simulation and Construction of Cockroft Walton Voltage MultiplierDocument5 paginiDesign, Simulation and Construction of Cockroft Walton Voltage MultiplierGRD JournalsÎncă nu există evaluări

- (ALCANTARA - BSEE-2D) Experiment 2 Final ReportDocument11 pagini(ALCANTARA - BSEE-2D) Experiment 2 Final ReportLawrence Abram AlcantaraÎncă nu există evaluări

- Design and Implementation of PV Fed Two Stage DC/DC Converter For Home ApplicationsDocument6 paginiDesign and Implementation of PV Fed Two Stage DC/DC Converter For Home ApplicationsVishal KevatÎncă nu există evaluări

- Comparative Study of MLI and Dual Inverter Using Space Vector Modulation TechniquesDocument8 paginiComparative Study of MLI and Dual Inverter Using Space Vector Modulation Techniquesshiva256Încă nu există evaluări

- Base Paper 7Document13 paginiBase Paper 7Prince RohithÎncă nu există evaluări

- A High Performance Inverter Technology Architecture and Applicat PDFDocument5 paginiA High Performance Inverter Technology Architecture and Applicat PDFAnonimo 01Încă nu există evaluări

- Renewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationDocument3 paginiRenewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationiirÎncă nu există evaluări

- Design of A Power Converter Based On UC3842 For Blade Electric VehicleDocument6 paginiDesign of A Power Converter Based On UC3842 For Blade Electric VehicleHossam SobhyÎncă nu există evaluări

- Chaper 5 Power Conditioning: Presentation #1Document25 paginiChaper 5 Power Conditioning: Presentation #1Sabri BouloumaÎncă nu există evaluări

- Term Project Power D&TDocument6 paginiTerm Project Power D&TThamer SE AlkhamiisÎncă nu există evaluări

- Fuzzy Controlled Cuk Converter For Grid Connected Ev ApplicationsDocument11 paginiFuzzy Controlled Cuk Converter For Grid Connected Ev ApplicationsViswanathanBalajiÎncă nu există evaluări

- Single Phase Grid Interconnected High Gain Boost Converter With Soft Switching CapabilityDocument13 paginiSingle Phase Grid Interconnected High Gain Boost Converter With Soft Switching CapabilityInternational Journal of Advances in Applied Sciences (IJAAS)Încă nu există evaluări

- Photovoltaic-Grid Integrated System: Sameer Khader, Abdel-Karim DaudDocument6 paginiPhotovoltaic-Grid Integrated System: Sameer Khader, Abdel-Karim Daudtariq76Încă nu există evaluări

- Design DC-DC Converter Topology Full-Bridge 24/400 V 300 W 100Khz With Zero Voltage Switching Phase Shift PWM MethodDocument6 paginiDesign DC-DC Converter Topology Full-Bridge 24/400 V 300 W 100Khz With Zero Voltage Switching Phase Shift PWM MethodtriwahonoÎncă nu există evaluări

- Photovoltaic Battery Charging System Based On PIC16F877A MicrocontrollerDocument5 paginiPhotovoltaic Battery Charging System Based On PIC16F877A Microcontrollerluis martinezÎncă nu există evaluări

- The Application of Dynamic Voltage Restorers (DVR) On Power Distribution Systems For Mitigation of Voltage Sags / SwellsDocument7 paginiThe Application of Dynamic Voltage Restorers (DVR) On Power Distribution Systems For Mitigation of Voltage Sags / SwellsIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalÎncă nu există evaluări

- Control of The Output Voltage of The PVDocument10 paginiControl of The Output Voltage of The PVbrightmoreÎncă nu există evaluări

- Design of An Ultracapacitor Based Dynamic Voltage Restorer For Power Quality Enhancement in The Distribution GridDocument7 paginiDesign of An Ultracapacitor Based Dynamic Voltage Restorer For Power Quality Enhancement in The Distribution GridGRD JournalsÎncă nu există evaluări

- Buck ReportDocument9 paginiBuck ReportNaeem GulÎncă nu există evaluări

- A Method of Power Decoupling For Long Life Micro-InverterDocument6 paginiA Method of Power Decoupling For Long Life Micro-InverterMaryam HassanÎncă nu există evaluări

- To Simulate, Design & Implementation of Maximum Power Harvesting of Solar Energy by Using DC-DC ConverterDocument6 paginiTo Simulate, Design & Implementation of Maximum Power Harvesting of Solar Energy by Using DC-DC Convertershrawani rajputÎncă nu există evaluări

- Last PDF of Project ReportDocument18 paginiLast PDF of Project ReportRAVINA MANGAL100% (1)

- A New Approach For High Efficiency Buck-Boost DC-DC Converters Using Series CompensationDocument6 paginiA New Approach For High Efficiency Buck-Boost DC-DC Converters Using Series CompensationBishoo ShenoudaÎncă nu există evaluări

- IAETSD-JARAS High Gain Ratio Hybrid Transformer Based On DC-DC Converter For PV Grid ApplicationsDocument6 paginiIAETSD-JARAS High Gain Ratio Hybrid Transformer Based On DC-DC Converter For PV Grid ApplicationsiaetsdiaetsdÎncă nu există evaluări

- Presentation On Single Phase Grid Connected Rooftop Integrated Solar SystemDocument28 paginiPresentation On Single Phase Grid Connected Rooftop Integrated Solar SystemmonaÎncă nu există evaluări

- CH 2 PDFDocument67 paginiCH 2 PDFmuhammad saeedÎncă nu există evaluări

- Brochure and Schedule AAIPIVSEE - 2021Document4 paginiBrochure and Schedule AAIPIVSEE - 2021knighthood4allÎncă nu există evaluări

- Advanced KP Stellar Astrology User ManualDocument27 paginiAdvanced KP Stellar Astrology User Manualknighthood4all100% (3)

- Jyotish Brighu Prashna Nadi RG Rao 1Document161 paginiJyotish Brighu Prashna Nadi RG Rao 1knighthood4allÎncă nu există evaluări

- Rectification of Birth Time: A New ConceptDocument33 paginiRectification of Birth Time: A New ConceptKaranam.Ramakumar88% (8)

- Mantra Sadana HanumanDocument49 paginiMantra Sadana Hanumanknighthood4allÎncă nu există evaluări

- Advertisement WebsiteDocument1 paginăAdvertisement Websiteknighthood4allÎncă nu există evaluări

- RP Submission Form & MOM - Pratap - NotsignedDocument3 paginiRP Submission Form & MOM - Pratap - Notsignedknighthood4allÎncă nu există evaluări

- K.P. Astrology and Rich PersonsDocument44 paginiK.P. Astrology and Rich Personsknighthood4all100% (8)

- PowerTech 2020 BrochureDocument6 paginiPowerTech 2020 Brochureknighthood4allÎncă nu există evaluări

- AMPS 2020 - IITRoorkee - Brochure PDFDocument5 paginiAMPS 2020 - IITRoorkee - Brochure PDFknighthood4allÎncă nu există evaluări

- Nadi AstrologyDocument8 paginiNadi AstrologyYogesh DhekaleÎncă nu există evaluări

- CH 2 - Op-Amp ApplicationDocument52 paginiCH 2 - Op-Amp Applicationknighthood4all100% (2)

- Nakshtra and LordsDocument1 paginăNakshtra and Lordsknighthood4allÎncă nu există evaluări

- Inverter MoudlesDocument63 paginiInverter Moudlesknighthood4allÎncă nu există evaluări

- Active Filter Id-IqDocument6 paginiActive Filter Id-Iqknighthood4allÎncă nu există evaluări

- AMPS 2020 - IITRoorkee - Brochure PDFDocument5 paginiAMPS 2020 - IITRoorkee - Brochure PDFknighthood4allÎncă nu există evaluări

- 7th CPC Order CftisDocument2 pagini7th CPC Order Cftisknighthood4allÎncă nu există evaluări

- Akagi2010 NPC Active FilterDocument10 paginiAkagi2010 NPC Active Filterknighthood4allÎncă nu există evaluări

- Iempower BrochureDocument2 paginiIempower Brochureknighthood4allÎncă nu există evaluări

- Semikron Datasheet Sk45mlet12scp 24919661Document8 paginiSemikron Datasheet Sk45mlet12scp 24919661knighthood4allÎncă nu există evaluări

- 7th CPC Order CftisDocument2 pagini7th CPC Order Cftisknighthood4allÎncă nu există evaluări

- Ganesha Pancharatham ModifiedDocument2 paginiGanesha Pancharatham Modifiedknighthood4allÎncă nu există evaluări

- Mantra SadanaDocument49 paginiMantra Sadanaknighthood4allÎncă nu există evaluări

- 27 Design and Implementation of A Sensorless Multilevel InverterDocument7 pagini27 Design and Implementation of A Sensorless Multilevel Inverterknighthood4allÎncă nu există evaluări

- UPQCDocument240 paginiUPQCknighthood4allÎncă nu există evaluări

- Power Electronics AdvancedDocument130 paginiPower Electronics AdvancedBhaskar Dandapathak88% (8)

- Comparative Study On Buck and Buck-Boost DC-DC ConDocument7 paginiComparative Study On Buck and Buck-Boost DC-DC Conknighthood4allÎncă nu există evaluări

- An Efficient Multilevel-Synthesis Approach and Its Application To A 27-Level InverterDocument7 paginiAn Efficient Multilevel-Synthesis Approach and Its Application To A 27-Level Inverterknighthood4allÎncă nu există evaluări

- Lecture1 PDFDocument49 paginiLecture1 PDFknighthood4allÎncă nu există evaluări

- Wisdom - Lamp - 4 - Series 2Document18 paginiWisdom - Lamp - 4 - Series 2Sirley Dayana Ochoa SánchezÎncă nu există evaluări

- Fuseless Capacitor Bank Protection2Document7 paginiFuseless Capacitor Bank Protection2Anonymous 9VcxlFErfÎncă nu există evaluări

- 550 K VGISDocument18 pagini550 K VGISMinh VienÎncă nu există evaluări

- Cathodic Protection-Steel Tank Monthly ReportDocument1 paginăCathodic Protection-Steel Tank Monthly Reportdeltz0706Încă nu există evaluări

- 8 Channel BLUETOOTH Dimmer PDFDocument18 pagini8 Channel BLUETOOTH Dimmer PDFAlvaro GonçalvesÎncă nu există evaluări

- STAR ST3 1kva 3kva UPS Service ManualDocument14 paginiSTAR ST3 1kva 3kva UPS Service ManualDoru RazvanÎncă nu există evaluări

- Omega Lighting-Erco Monopoll & Varipoll Linear Cylindrical Systems Catalog 10-86Document44 paginiOmega Lighting-Erco Monopoll & Varipoll Linear Cylindrical Systems Catalog 10-86Alan MastersÎncă nu există evaluări

- Rotating Electrical Machines Standards - Reference TablesDocument3 paginiRotating Electrical Machines Standards - Reference TablesanuragpugaliaÎncă nu există evaluări

- 15 HPL2010-En. TransformadoresDocument20 pagini15 HPL2010-En. TransformadoresDennis GuaniloÎncă nu există evaluări

- Warning & Alarming Instrument 5 & 6Document28 paginiWarning & Alarming Instrument 5 & 6VivekDhameliyaÎncă nu există evaluări

- Power Electronics Converters, Applications, and DesignDocument736 paginiPower Electronics Converters, Applications, and Designaaaravin100% (7)

- 15 TransformersDocument8 pagini15 TransformersDarianomaÎncă nu există evaluări

- CDS Light-Dependent Photoresistors: TokenDocument8 paginiCDS Light-Dependent Photoresistors: TokenAnn Janssen PasaporteÎncă nu există evaluări

- Gei 50261Document24 paginiGei 50261Aquilino Sanchez FosadoÎncă nu există evaluări

- Water Tank Indicator DLD Open EndedDocument3 paginiWater Tank Indicator DLD Open EndedZayd IqbalÎncă nu există evaluări

- SENTRON LV10-PH05 Complete English PDFDocument196 paginiSENTRON LV10-PH05 Complete English PDFcc_bauÎncă nu există evaluări

- Time Current Characteristics of Fuse Using ETAPDocument7 paginiTime Current Characteristics of Fuse Using ETAPAkhter IqbalÎncă nu există evaluări

- Calculate Voltage Drop at TransformerDocument6 paginiCalculate Voltage Drop at TransformerGulzar Ahmad Sarwar0% (1)

- Diodos de MicroondasDocument1 paginăDiodos de MicroondasJose CastellanosÎncă nu există evaluări

- Siemens 3RU11 Overload RelaysDocument2 paginiSiemens 3RU11 Overload Relaysbel90torresÎncă nu există evaluări

- 216, 226, 228, 236, 246, and 248 Skid-Steer Loader Electrical SystemDocument2 pagini216, 226, 228, 236, 246, and 248 Skid-Steer Loader Electrical SystemLiliana Rebeca Santos santos100% (1)

- 3D Schematic LB T282B Wconstant Speed vAA PDFDocument81 pagini3D Schematic LB T282B Wconstant Speed vAA PDFTiago RodriguesÎncă nu există evaluări

- Electric Motor Actuator - LancoDocument3 paginiElectric Motor Actuator - LancoShar MathewÎncă nu există evaluări

- Techtopics No. 125Document2 paginiTechtopics No. 125paijo klimpritÎncă nu există evaluări

- How To Test A Triac. - Electronic Circuits and Diagram-Electronics Projects and DesignDocument21 paginiHow To Test A Triac. - Electronic Circuits and Diagram-Electronics Projects and DesignuzenhoÎncă nu există evaluări

- Features: Vishay SemiconductorsDocument5 paginiFeatures: Vishay SemiconductorsNgaces TerungÎncă nu există evaluări

- ABB LV Low Voltage Fuses & Fuse LinksDocument24 paginiABB LV Low Voltage Fuses & Fuse LinksFiko007Încă nu există evaluări

- Day 4 Practical Exercise QuestionDocument10 paginiDay 4 Practical Exercise QuestionbibinbibinÎncă nu există evaluări

- 15-28 SUPPLEMENT FOR 1989: Wiring Diagram KX80-L3, N3, KX100-A2 (UK)Document1 pagină15-28 SUPPLEMENT FOR 1989: Wiring Diagram KX80-L3, N3, KX100-A2 (UK)PabloÎncă nu există evaluări

- SATIP-P-104-10 Rev 7 FinalDocument2 paginiSATIP-P-104-10 Rev 7 FinalHatemS.MashaGbeh0% (1)