Documente Academic

Documente Profesional

Documente Cultură

Rfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets Features

Încărcat de

aleh sharapovTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Rfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets Features

Încărcat de

aleh sharapovDrepturi de autor:

Formate disponibile

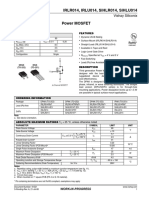

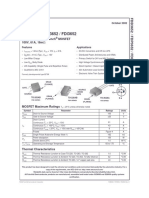

RFD14N05L, RFD14N05LSM, RFP14N05L

Data Sheet November 2004

14A, 50V, 0.100 Ohm, Logic Level, Features

N-Channel Power MOSFETs • 14A, 50V

These are N-channel power MOSFETs manufactured using

• rDS(ON) = 0.100Ω

the MegaFET process. This process, which uses feature

sizes approaching those of LSI integrated circuits, gives • Temperature Compensating PSPICE® Model

optimum utilization of silicon, resulting in outstanding • Can be Driven Directly from CMOS, NMOS, and

performance. They were designed for use in applications TTL Circuits

such as switching regulators, switching converters, motor

• Peak Current vs Pulse Width Curve

drivers and relay drivers. This performance is accomplished

www.DataSheet4U.com

through a special gate oxide design which provides full rated • UIS Rating Curve

conductance at gate bias in the 3V-5V range, thereby

• 175oC Operating Temperature

facilitating true on-off power control directly from logic level

(5V) integrated circuits. • Related Literature

- TB334 “Guidelines for Soldering Surface Mount

Formerly developmental type TA09870. Components to PC Boards”

Ordering Information Symbol

PART NUMBER PACKAGE BRAND

D

RFD14N05L TO-251AA 14N05L

RFD14N05LSM TO-252AA 14N05L

RFP14N05L TO-220AB F14N05L G

NOTE: When ordering, use the entire part number. Add the suffix 9A to

obtain the TO-252AA variant in the tape and reel, i.e., RFD14N05LSM9A. S

Packaging

JEDEC TO-251AA JEDEC TO-252AA

SOURCE DRAIN (FLANGE)

DRAIN

GATE GATE

DRAIN (FLANGE) SOURCE

JEDEC TO-220AB

SOURCE

DRAIN

GATE

DRAIN (FLANGE)

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

Absolute Maximum Ratings TC = 25oC, Unless Otherwise Specified

RFD14N05L, RFD14N05LSM,

RFP14N05L UNITS

Drain to Source Voltage (Note 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDSS 50 V

Drain to Gate Voltage (RGS = 20kΩ) (Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . VDGR 50 V

Gate to Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VGS ±10 V

Continuous Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .ID 14 A

Pulsed Drain Current (Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IDM Refer to Peak Current Curve

Pulsed Avalanche Rating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . EAS Refer to UIS Curve

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . PD 48 W

Derate above 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.32 W/oC

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, TSTG -55 to 175 oC

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s. . . . . . . . . . . . . . . . . . . . . . . . . . . . TL 300 oC

Package Body for 10s, See Techbrief 334 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Tpkg 260 oC

www.DataSheet4U.com

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. TJ = 25oC to 150oC.

Electrical Specifications TC = 25oC, Unless Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain to Source Breakdown Voltage BVDSS ID = 250µA, VGS = 0V, Figure 13 50 - - V

Gate Threshold Voltage VGS(TH) VGS = VDS, ID = 250µA, Figure12 1 - 2 V

Zero Gate Voltage Drain Current IDSS VDS = 40V, VGS = 0V - - 1 µA

VDS = 40V, VGS = 0V, TC = 150oC - - 50 µA

Gate to Source Leakage Current IGSS VGS = ±10V - - ±100 nA

Drain to Source On Resistance (Note 2) rDS(ON) ID = 14A, VGS = 5V, Figures 9, 11 - - 0.100 Ω

Turn-On Time t(ON) VDD = 25V, ID = 7A, - - 60 ns

RL = 3.57Ω, VGS = 5V,

Turn-On Delay Time td(ON) - 13 - ns

RGS = 0.6Ω

Rise Time tr - 24 - ns

Turn-Off Delay Time td(OFF) - 42 - ns

Fall Time tf - 16 - ns

Turn-Off Time t(OFF) - - 100 ns

Total Gate Charge Qg(TOT) VGS = 0V to 10V VDD = 40V, ID = 14A, - - 40 nC

RL = 2.86Ω

Gate Charge at 5V Qg(5) VGS = 0V to 5V - - 25 nC

Figures 20, 21

Threshold Gate Charge Qg(TH) VGS = 0V to 1V - - 1.5 nC

Input Capacitance CISS VDS = 25V, VGS = 0V, f = 1MHz - 670 - pF

Figure 14

Output Capacitance COSS - 185 - pF

Reverse Transfer Capacitance CRSS - 50 - pF

Thermal Resistance Junction to Case RθJC - - 3.125 oC/W

Thermal Resistance Junction to Ambient RθJA TO-251 and TO-252 - - 100 oC/W

RθJA TO-220 - - 80 oC/W

Source to Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Source to Drain Diode Voltage (Note 2) VSD ISD = 14A - - 1.5 V

Diode Reverse Recovery Time trr ISD = 14A, dISD/dt = 100A/µs - - 125 ns

NOTES:

2. Pulse Test: Pulse Width ≤300ms, Duty Cycle ≤2%.

3. Repetitive Rating: Pulse Width limited by max junction temperature. See Transient Thermal Impedance Curve (Figure 3) and Peak Current

Capability Curve (Figure 5).

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

Typical Performance Curves Unless Otherwise Specified

1.2 16

POWER DISSIPATION MULTIPLIER

1.0

ID, DRAIN CURRENT (A)

12

0.8

0.6 8

0.4

4

0.2

www.DataSheet4U.com

0 0

0 25 50 75 100 125 150 175 25 50 75 100 125 150 175

TC , CASE TEMPERATURE (oC) TC, CASE TEMPERATURE (oC)

FIGURE 1. NORMALIZED POWER DISSIPATION vs CASE FIGURE 2. MAXIMUM CONTINUOUS DRAIN CURRENT vs

TEMPERATURE TEMPERATURE

1

THERMAL IMPEDANCE

0.5

Zθ JC, NORMALIZED

0.2

PDM

0.1

0.1

0.05 t1

0.02 t2

0.01

NOTES:

SINGLE PULSE DUTY FACTOR: D = t1/t2

PEAK TJ = PDM x Zθ JC x Rθ JC + TC

0.01

10-5 10-4 10-3 10-2 10-1 100 101

t, RECTANGULAR PULSE DURATION (s)

FIGURE 3. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCE

100 200

TC = 25oC TRANSCONDUCTANCE FOR TEMPERATURES

ABOVE 25oC DERATE PEAK

IDM, PEAK CURRENT CAPABILITY (A)

TJ = MAX. RATED MAY LIMIT CURRENT

IN THIS REGION CURRENT AS FOLLOWS:

ID, DRAIN CURRENT (A)

100 175 - TC

I = I25

150

100µs

10

1ms

10ms

OPERATION IN THIS

AREA MAY BE 100ms VGS = 5V

1

LIMITED BY rDS(ON) DC VGS = 10V

TC = 25oC

0.5 10

1 10 100 10 -5 10-4 10-3 10-2 10-1 100 101

VDS, DRAIN TO SOURCE VOLTAGE (V) t, PULSE WIDTH (s)

FIGURE 4. FORWARD BIAS SAFE OPERATING AREA FIGURE 5. PEAK CURRENT CAPABILITY

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

Typical Performance Curves Unless Otherwise Specified (Continued)

50 35

VGS = 10V VGS = 5V

IAS, AVALANCHE CURRENT (A)

30 VGS = 4.5V

VGS = 4V

ID, DRAIN CURRENT (A)

25

STARTING TJ = 25oC

10 PULSE DURATION = 80µs, TC = 25oC

20

DUTY CYCLE = 0.5% MAX.

15

STARTING TJ = 150oC

10 VGS = 3V

If R = 0

tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD)

5 VGS = 2.5V

If R ≠ 0

tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS-VDD) +1]

1

www.DataSheet4U.com 0

0.01 0.1 1 10 0 1.5 3.0 4.5 6.0 7.5

tAV, TIME IN AVALANCHE (ms) VDS, DRAIN TO SOURCE VOLTAGE (V)

NOTE: Refer to Fairchild Application Notes AN9321 and AN9322.

FIGURE 6. UNCLAMPED INDUCTIVE SWITCHING FIGURE 7. SATURATION CHARACTERISTICS

35 250

IDS(ON), DRAIN TO SOURCE CURRENT (A)

-55oC ID = 28A

ID = 7A ID = 14A

30

25oC 175oC rDS(ON) , DRAIN TO SOURCE 200

ON RESISTANCE (mΩ)

25

150

20

15 ID = 3.5A

100

10

PULSE DURATION = 80µs 50

5 DUTY CYCLE = 0.5% MAX.

PULSE DURATION = 80µs

VDD = 15V

DUTY CYCLE = 0.5% MAX.

0 0

0 1.5 3.0 4.5 6.0 7.5 2.5 3.0 3.5 4.0 4.5 5.0

VGS, GATE TO SOURCE VOLTAGE (V) VGS , GATE TO SOURCE VOLTAGE (V)

FIGURE 8. TRANSFER CHARACTERISTICS FIGURE 9. DRAIN TO SOURCE ON RESISTANCE vs GATE

VOLTAGE AND DRAIN CURRENT

160 2.5

VDD = 25V, ID = 14A, RL = 3.57Ω td(OFF) PULSE DURATION = 80µs

DUTY CYCLE = 0.5% MAX.

NORMALIZED DRAIN TO SOURCE

140

VGS = 10V, ID = 14A

2.0

120

SWITCHING TIME (ns)

ON RESISTANCE

100 1.5

tr

80

tf

1.0

60

40

td(ON) 0.5

20

0 0

0 10 20 30 40 50 -80 -40 0 40 80 120 160 200

RGS , GATE TO SOURCE RESISTANCE (Ω) TJ, JUNCTION TEMPERATURE (oC)

FIGURE 10. SWITCHING TIME vs GATE RESISTANCE FIGURE 11. NORMALIZED DRAIN TO SOURCE ON

RESISTANCE vs JUNCTION TEMPERATURE

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

Typical Performance Curves Unless Otherwise Specified (Continued)

2.0 2.0

VGS = VDS, ID = 250µA ID = 250µA

NORMALIZED DRAIN TO SOURCE

BREAKDOWN VOLTAGE

THRESHOLD VOLTAGE

1.5 1.5

NORMALIZED GATE

1.0 1.0

0.5 0.5

www.DataSheet4U.com

0 0

-80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200

TJ, JUNCTION TEMPERATURE (oC) TJ , JUNCTION TEMPERATURE (oC)

FIGURE 12. NORMALIZED GATE THRESHOLD VOLTAGE vs FIGURE 13. NORMALIZED DRAIN TO SOURCE BREAKDOWN

JUNCTION TEMPERATURE VOLTAGE vs JUNCTION TEMPERATURE

800 50 5

VDS , DRAIN TO SOURCE VOLTAGE (V)

VGS , GATE TO SOURCE VOLTAGE (V)

CISS VDD = BVDSS VDD = BVDSS

40 4

600

C, CAPACITANCE (pF)

VGS = 0V, f = 1MHz 30 3

CISS = CGS + CGD

CRSS = CGD

400

COSS ≈ CDS + CGD 20 2

0.75 BVDSS

0.50 BVDSS

COSS 0.25 BVDSS

200 10 RL = 3.57Ω 1

IG(REF) = 0.4mA

CRSS VGS = 5V

0 0

0 I G ( REF ) I G ( REF )

0 5 10 15 20 25 20 ------------------------- t, TIME (µs) 80 -------------------------

I I

VDS , DRAIN TO SOURCE VOLTAGE (V) G ( ACT ) G ( ACT )

NOTE: Refer to Fairchild Application Notes AN7254 and AN7260,

FIGURE 14. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE FIGURE 15. TRANSCONDUCTANCE vs DRAIN CURRENT

Test Circuits and Waveforms

VDS

BVDSS

L tP

VDS

VARY tP TO OBTAIN IAS

+ VDD

REQUIRED PEAK IAS RG

VDD

VGS -

DUT

tP

0V IAS

0

0.01Ω

tAV

FIGURE 16. UNCLAMPED ENERGY TEST CIRCUIT FIGURE 17. UNCLAMPED ENERGY WAVEFORMS

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

Test Circuits and Waveforms (Continued)

tON tOFF

td(ON) td(OFF)

VDS

tr tf

VDS

90% 90%

RL

VGS

+ 10% 10%

VDD 0

-

DUT 90%

RGS

www.DataSheet4U.com VGS 50% 50%

PULSE WIDTH

VGS 10%

0

FIGURE 18. SWITCHING TIME TEST CIRCUIT FIGURE 19. RESISTIVE SWITCHING WAVEFORMS

VDS

RL VDD Qg(TOT)

VDS

VGS = 10V

VGS Qg(5)

+

VDD

- VGS VGS = 5V

DUT VGS = 1V

IG(REF) 0

Qg(TH)

IG(REF)

0

FIGURE 20. GATE CHARGE TEST CIRCUIT FIGURE 21. GATE CHARGE WAVEFORMS

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

RFD14N05L, RFD14N05LSM, RFP14N05L

PSPICE Electrical Model

.SUBCKT RFP14N05L 2 1 3 ; rev 9/15/94

CA 12 8 1.464e-9

CB 15 14 1.64e-9

DPLCAP 5

CIN 6 8 6.17e-10 DRAIN

10 2

LDRAIN

DBODY 7 5 DBDMOD

DBREAK 5 11 DBKMOD RSCL1

DPLCAP 10 5 DPLCAPMOD RSCL2 DBREAK

+ 51

5

EBREAK 11 7 17 18 65.35 ESCL

51

EDS 14 8 5 8 1 50

11

EGS 13 8 6 8 1 6 RDRAIN + DBODY

ESG

ESG 6 10 6 8 1 8 16 EBREAK 17

+ 18

EVTO 20 6 18 8 1 VTO

+

MOS2

www.DataSheet4U.com EVTO 21

IT 8 17 1 GATE 9 20 +

18 6

1 MOS1

LGATE RGATE 8

LDRAIN 2 5 1e-9

RIN CIN

LGATE 1 9 5.68e-9

LSOURCE 3 7 5.35e-9 RSOURCE LSOURCE

8 7 3

SOURCE

MOS1 16 6 8 8 MOSMOD M = 0.99

MOS2 16 21 8 8 MOSMOD M = 0.01 S1A S2A

12 15 RBREAK

13 14 17

RBREAK 17 18 RBKMOD 1 18

8 13

RDRAIN 50 16 RDSMOD 33.1e-3 S1B S2B

RGATE 9 20 5.85 RVTO

13

RIN 6 8 1e9 CA CB 19

IT

RSCL1 5 51 RSCLMOD 1e-6 + + 14

VBAT

6

RSCL2 5 50 1e3 EGS EDS 5 +

8 8

RSOURCE 8 7 RDSMOD 14.3e-3

RVTO 18 19 RVTOMOD 1

S1A 6 12 13 8 S1AMOD

S1B 13 12 13 8 S1BMOD

S2A 6 15 14 13 S2AMOD

S2B 13 15 14 13 S2BMOD

VBAT 8 19 DC 1

VTO 21 6 0.485

ESCL 51 50 VALUE = {(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)*1e6/46,7))}

.MODEL DBDMOD D (IS = 2.23e-13 RS = 1.15e-2 TRS1 = 1.64e-3 TRS2 = 7.89e-6 CJO = 6.83e-10 TT = 3.68e-8)

.MODEL DBKMOD D (RS = 3.8e-1 TRS1 = 1.89e-3 TRS2 = 1.13e-5)

.MODEL DPLCAPMOD D (CJO = 25.7e-11 IS = 1e-30 N = 10)

.MODEL MOSMOD NMOS (VTO = 1.935 KP = 18.89 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u)

.MODEL RBKMOD RES (TC1 = 7.18e-4 TC2 = 1.53e-6)

.MODEL RDSMOD RES (TC1 = 4.45e-3 TC2 = 2.9e-5)

.MODEL RSCLMOD RES (TC1 = 2.8e-3 TC2 = 6.0e-6)

.MODEL RVTOMOD RES (TC1 = -1.7e-3 TC2 = -2.0e-6)

.MODEL S1AMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -3.55 VOFF= -1.55)

.MODEL S1BMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -1.55 VOFF= -3.55)

.MODEL S2AMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = -2.55 VOFF= 2.45)

.MODEL S2BMOD VSWITCH (RON = 1e-5 ROFF = 0.1 VON = 2.45 VOFF= -2.55)

.ENDS

NOTE: For further discussion of the PSPICE model, consult A New PSPICE Sub-circuit for the Power MOSFET Featuring Global

Temperature Options; authored by William J. Hepp and C. Frank Wheatley.

©2004 Fairchild Semiconductor Corporation RFD14N05L, RFD14N05LSM, RFP14N05L Rev. B1

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is

not intended to be an exhaustive list of all such trademarks.

ACEx™ FAST ISOPLANAR™ Power247™ Stealth™

ActiveArray™ FASTr™ LittleFET™ PowerEdge™ SuperFET™

Bottomless™ FPS™ MICROCOUPLER™ PowerSaver™ SuperSOT™-3

CoolFET™ FRFET™ MicroFET™ PowerTrench SuperSOT™-6

CROSSVOLT™ GlobalOptoisolator™ MicroPak™ QFET SuperSOT™-8

DOME™ GTO™ MICROWIRE™ QS™ SyncFET™

EcoSPARK™ HiSeC™ MSX™ QT Optoelectronics™ TinyLogic

E2CMOS™ I2C™ MSXPro™ Quiet Series™ TINYOPTO™

EnSigna™ i-Lo™ OCX™ RapidConfigure™ TruTranslation™

www.DataSheet4U.com FACT™ ImpliedDisconnect™ OCXPro™ RapidConnect™ UHC™

FACT Quiet Series™ OPTOLOGIC µSerDes™ UltraFET

Across the board. Around the world.™ OPTOPLANAR™ SILENT SWITCHER VCX™

The Power Franchise PACMAN™ SMART START™

Programmable Active Droop™ POP™ SPM™

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY

ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT

CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant into support device or system whose failure to perform can

the body, or (b) support or sustain life, or (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in significant injury to the

user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or This datasheet contains the design specifications for

In Design product development. Specifications may change in

any manner without notice.

Preliminary First Production This datasheet contains preliminary data, and

supplementary data will be published at a later date.

Fairchild Semiconductor reserves the right to make

changes at any time without notice in order to improve

design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild

Semiconductor reserves the right to make changes at

any time without notice in order to improve design.

Obsolete Not In Production This datasheet contains specifications on a product

that has been discontinued by Fairchild semiconductor.

The datasheet is printed for reference information only.

Rev. I13

S-ar putea să vă placă și

- 14N25 FairchildSemiconductorDocument8 pagini14N25 FairchildSemiconductorPaulo Henrique SÎncă nu există evaluări

- RFD15P05, RFD15P05SM, RFP15P05: 15A, 50V, 0.150 Ohm, P-Channel Power Mosfets FeaturesDocument8 paginiRFD15P05, RFD15P05SM, RFP15P05: 15A, 50V, 0.150 Ohm, P-Channel Power Mosfets FeaturesJean Tsuna KalawÎncă nu există evaluări

- RFD15P05, RFD15P05SM, RFP15P05: 15A, 50V, 0.150 Ohm, P-Channel Power Mosfets FeaturesDocument8 paginiRFD15P05, RFD15P05SM, RFP15P05: 15A, 50V, 0.150 Ohm, P-Channel Power Mosfets FeaturesIlyes KHOUILDIÎncă nu există evaluări

- Rfg50N06Le, Rfp50N06Le, Rf1S50N06Lesm: 50A, 60V, 0.022 Ohm, Logic Level N-Channel Power Mosfets FeaturesDocument9 paginiRfg50N06Le, Rfp50N06Le, Rf1S50N06Lesm: 50A, 60V, 0.022 Ohm, Logic Level N-Channel Power Mosfets FeaturesrwylieÎncă nu există evaluări

- DS-MosfetDocument9 paginiDS-MosfetEmin KültürelÎncă nu există evaluări

- RFD8P05 Datasheet (PDF) - Intersil CorporationDocument6 paginiRFD8P05 Datasheet (PDF) - Intersil Corporationrcuvgd-1Încă nu există evaluări

- RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesDocument8 paginiRFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesRoberto DiazÎncă nu există evaluări

- RFD8P05, RFD8P05SM, RFP8P05: Features DescriptionDocument5 paginiRFD8P05, RFD8P05SM, RFP8P05: Features DescriptionRicardo VieiraÎncă nu există evaluări

- IRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesDocument7 paginiIRF9540, RF1S9540SM: 19A, 100V, 0.200 Ohm, P-Channel Power Mosfets FeaturesvetchboyÎncă nu există evaluări

- RFG30P05, RFP30P05, RF1S30P05SM: 30A, 50V, 0.065 Ohm, P-Channel Power Mosfets FeaturesDocument9 paginiRFG30P05, RFP30P05, RF1S30P05SM: 30A, 50V, 0.065 Ohm, P-Channel Power Mosfets Featuresbar catalinÎncă nu există evaluări

- Datasheet RFD16 N05Document8 paginiDatasheet RFD16 N05Nicolau FrançaÎncă nu există evaluări

- RFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets FeaturesDocument8 paginiRFG50N06, RFP50N06, RF1S50N06SM: 50A, 60V, 0.022 Ohm, N-Channel Power Mosfets Featureswert1a2Încă nu există evaluări

- IRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets FeaturesDocument7 paginiIRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets Featuresabduallah muhammadÎncă nu există evaluări

- IRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesDocument8 paginiIRF630, RF1S630SM: 9A, 200V, 0.400 Ohm, N-Channel Power Mosfets FeaturesulisesÎncă nu există evaluări

- Irf 630Document7 paginiIrf 630ban4444Încă nu există evaluări

- Irf 510Document7 paginiIrf 510hayatdoluusÎncă nu există evaluări

- Irf9540, Irf9541, Irf9542, Irf9543, RF1S9540, RF1S9540SMDocument7 paginiIrf9540, Irf9541, Irf9542, Irf9543, RF1S9540, RF1S9540SMcombra24grÎncă nu există evaluări

- Rfp12P08, Rfp12P10: 12A, 80V and 100V, 0.300 Ohm, P-Channel Power Mosfets FeaturesDocument5 paginiRfp12P08, Rfp12P10: 12A, 80V and 100V, 0.300 Ohm, P-Channel Power Mosfets FeaturesOscarVargasÎncă nu există evaluări

- Irf510 PDFDocument7 paginiIrf510 PDFandri SyahputraÎncă nu există evaluări

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Document7 pagini5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Rudi AnotheerÎncă nu există evaluări

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Document7 pagini5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number Data Sheet November 1999Jaricsa BernaolaÎncă nu există evaluări

- RFG40N10, RFP40N10, RF1S40N10, RF1S40N10SM: 40A, 100V, 0.040 Ohm, N-Channel Power Mosfets FeaturesDocument6 paginiRFG40N10, RFP40N10, RF1S40N10, RF1S40N10SM: 40A, 100V, 0.040 Ohm, N-Channel Power Mosfets Featuresnnaans2013Încă nu există evaluări

- Irf540, Irf541, Irf542, Irf543, RF1S540, RF1S540SMDocument7 paginiIrf540, Irf541, Irf542, Irf543, RF1S540, RF1S540SMibnuÎncă nu există evaluări

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesDocument7 paginiIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesAbel RodriguezÎncă nu există evaluări

- Irfr120, Irfu120: 8.4A, 100V, 0.270 Ohm, N-Channel Power Mosfets FeaturesDocument7 paginiIrfr120, Irfu120: 8.4A, 100V, 0.270 Ohm, N-Channel Power Mosfets FeaturesWahyu DiyonoÎncă nu există evaluări

- Datasheet IRFP 9240Document7 paginiDatasheet IRFP 9240AguilaSolitariaÎncă nu există evaluări

- IRF540, RF1S540SM: 28A, 100V, 0.077 Ohm, N-Channel Power Mosfets FeaturesDocument7 paginiIRF540, RF1S540SM: 28A, 100V, 0.077 Ohm, N-Channel Power Mosfets FeaturesJuan Pablo Echeverria CockÎncă nu există evaluări

- IRFR320, IRFU320: 3.1A, 400V, 1.800 Ohm, N-Channel Power Mosfets FeaturesDocument7 paginiIRFR320, IRFU320: 3.1A, 400V, 1.800 Ohm, N-Channel Power Mosfets Featuresmarcodlcruz94Încă nu există evaluări

- 5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number 1573.3 Data Sheet June 1999Document7 pagini5.6A, 100V, 0.540 Ohm, N-Channel Power Mosfet Features: File Number 1573.3 Data Sheet June 1999Rathy VadivelkumarÎncă nu există evaluări

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999Document7 pagini10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: File Number 2311.3 Data Sheet July 1999FadiÎncă nu există evaluări

- RFG70N06, RFP70N06, RF1S70N06Document8 paginiRFG70N06, RFP70N06, RF1S70N06Juan Carlos GarcíaÎncă nu există evaluări

- Datasheet IRF840 MOSFETDocument10 paginiDatasheet IRF840 MOSFETEdwin FlorezÎncă nu există evaluări

- Transistor IRFP350Document7 paginiTransistor IRFP350MiguelAngelCedanoBurrolaÎncă nu există evaluări

- IRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesDocument7 paginiIRFP360: 23A, 400V, 0.200 Ohm, N-Channel Power Mosfet FeaturesFran Javi Vila DiazÎncă nu există evaluări

- 10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Document8 pagini10A, 400V, 0.550 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Lotfi MessaadiÎncă nu există evaluări

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesDocument8 paginiIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesCesar AzcargortaÎncă nu există evaluări

- IRFP140: 31A, 100V, 0.077 Ohm, N-Channel Power Mosfet FeaturesDocument7 paginiIRFP140: 31A, 100V, 0.077 Ohm, N-Channel Power Mosfet Featuresdistribusi.pln.bulukumba ABKÎncă nu există evaluări

- RFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesDocument9 paginiRFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesAnca SterianÎncă nu există evaluări

- 8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Document8 pagini8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Agus SuwardonoÎncă nu există evaluări

- 8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Document8 pagini8A, 500V, 0.850 Ohm, N-Channel Power Mosfet Features: Data Sheet January 2002Chris GuarinÎncă nu există evaluări

- Datasheet For Irfp240Document7 paginiDatasheet For Irfp240Kandeke DaviesÎncă nu există evaluări

- IRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesDocument7 paginiIRFP460: 20A, 500V, 0.270 Ohm, N-Channel Power MOSFET FeaturesAmirÎncă nu există evaluări

- Datasheet IRF840 MOSFETDocument7 paginiDatasheet IRF840 MOSFETEdwin FlorezÎncă nu există evaluări

- Irfp 462Document7 paginiIrfp 462scribderougÎncă nu există evaluări

- Datasheet IRF840 MOSFET LabDocument7 paginiDatasheet IRF840 MOSFET LabEdwin FlorezÎncă nu există evaluări

- IRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesDocument7 paginiIRFP240: 20A, 200V, 0.180 Ohm, N-Channel Power Mosfet FeaturesAdah BumboneÎncă nu există evaluări

- Mosfet Potencia Sihlr014Document8 paginiMosfet Potencia Sihlr014Jorge Martinez PerezÎncă nu există evaluări

- FDB13AN06A0Document11 paginiFDB13AN06A0kamil.smolinski.1980Încă nu există evaluări

- DatasheetDocument7 paginiDatasheetmaximon13Încă nu există evaluări

- IRF7809A/IRF7811A IRF7809A/IRF7811A: Provisional DatasheetDocument4 paginiIRF7809A/IRF7811A IRF7809A/IRF7811A: Provisional DatasheetZak zsÎncă nu există evaluări

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Document8 pagini6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999Încă nu există evaluări

- IRF9520Document7 paginiIRF9520Emilio QuijanoÎncă nu există evaluări

- Datasheet Mosfet 76132PDocument10 paginiDatasheet Mosfet 76132Padam woodÎncă nu există evaluări

- FDP3652Document11 paginiFDP3652Dávid KisÎncă nu există evaluări

- IRFR 420-IRFU 420-SiHFR420-SiHFU420 - MosfetDocument11 paginiIRFR 420-IRFU 420-SiHFR420-SiHFU420 - MosfetTiago LeonhardtÎncă nu există evaluări

- DatasheetDocument12 paginiDatasheetDandy PrasetyoÎncă nu există evaluări

- Icl8038 PDFDocument12 paginiIcl8038 PDFmarcosÎncă nu există evaluări

- FDPF20N50FT D-2312661Document13 paginiFDPF20N50FT D-2312661Fernando GómezÎncă nu există evaluări

- Stfw4N150 Stp4N150, Stw4N150: N-Channel 1500 V, 5, 4 A, Powermesh™ Power Mosfet in To-220, To-247, To-3PfDocument15 paginiStfw4N150 Stp4N150, Stw4N150: N-Channel 1500 V, 5, 4 A, Powermesh™ Power Mosfet in To-220, To-247, To-3PfSidhi SadanÎncă nu există evaluări

- Afc 1563Document10 paginiAfc 1563Eugene FlexÎncă nu există evaluări

- Photolithography Instructor GuideDocument70 paginiPhotolithography Instructor Guidewesene derbeÎncă nu există evaluări

- The Cmos Inverter: OutlineDocument20 paginiThe Cmos Inverter: OutlinehappyharrÎncă nu există evaluări

- Name: K Sai Bhavana Class: Csit Roll No: 21951A3333 SubjectDocument12 paginiName: K Sai Bhavana Class: Csit Roll No: 21951A3333 SubjectK SAI BHAVANAÎncă nu există evaluări

- Team HubbleDocument7 paginiTeam HubbleAnagha MAÎncă nu există evaluări

- d882p PDFDocument3 paginid882p PDFdiego rotpeÎncă nu există evaluări

- Semiconductor Devices - Sample QuestionsDocument3 paginiSemiconductor Devices - Sample QuestionsJohn Idun EssumanÎncă nu există evaluări

- Details PDF: Image Part Number Description Manufacturer QuantityDocument1 paginăDetails PDF: Image Part Number Description Manufacturer QuantityKo MinÎncă nu există evaluări

- VLSI LAB VIVA QUESTIONSDocument2 paginiVLSI LAB VIVA QUESTIONSAbhay Shankar BharadwajÎncă nu există evaluări

- Thyristor Controlled Power For Induction Motor 1 FrontDocument8 paginiThyristor Controlled Power For Induction Motor 1 Frontvidhya associateÎncă nu există evaluări

- Nov Dec 2017Document2 paginiNov Dec 2017manashÎncă nu există evaluări

- BEOL PatterningDocument11 paginiBEOL PatterningBonn QianÎncă nu există evaluări

- Emx1 / Umx1N / Imx1: General Purpose Transistor (Dual Transistors)Document9 paginiEmx1 / Umx1N / Imx1: General Purpose Transistor (Dual Transistors)Juan CarlosÎncă nu există evaluări

- Elctronic Devices and CircuitsDocument14 paginiElctronic Devices and CircuitsVarun TejaÎncă nu există evaluări

- PE MCQ Unit-IIDocument9 paginiPE MCQ Unit-IIKalpesh MahajanÎncă nu există evaluări

- High Current Silicon Darlington Transistors NTE2349 & NTE2350Document2 paginiHigh Current Silicon Darlington Transistors NTE2349 & NTE2350Saem BachÎncă nu există evaluări

- A New Buried-Oxide-In-Drift Region Trench-Gate Power MOSFET With Improved Breakdown VoltageDocument3 paginiA New Buried-Oxide-In-Drift Region Trench-Gate Power MOSFET With Improved Breakdown VoltageMamidala Jagadesh KumarÎncă nu există evaluări

- Electronic Devices Lab - Exp - 8 - Student - Manual (Summer 18-19)Document8 paginiElectronic Devices Lab - Exp - 8 - Student - Manual (Summer 18-19)MD MONIM ISLAMÎncă nu există evaluări

- Psa Modules Wiring Diagrams: Obd2 DB9Document9 paginiPsa Modules Wiring Diagrams: Obd2 DB9simooo32Încă nu există evaluări

- Quiz BuzzerDocument26 paginiQuiz Buzzernaren_cool05100% (2)

- 06 Programmable Logic DevicesDocument28 pagini06 Programmable Logic DevicesChen ShyanÎncă nu există evaluări

- STD17NF03Document9 paginiSTD17NF03VeronicaÎncă nu există evaluări

- Fds6575 Single P-Channel, Logic Level, Powertrench MosfetDocument8 paginiFds6575 Single P-Channel, Logic Level, Powertrench MosfetsilictronicÎncă nu există evaluări

- CMOS Analog Circuit Design (Allen-2016)Document1.412 paginiCMOS Analog Circuit Design (Allen-2016)curliph0% (1)

- Circuit I KZ ManualDocument206 paginiCircuit I KZ ManualGonzález Martínez FranciscoÎncă nu există evaluări

- Lecture 2 The Manufacturing Process 2020Document48 paginiLecture 2 The Manufacturing Process 2020Noam ShemlaÎncă nu există evaluări

- Nasir Ali Bhatti 5120 Bscs C EveningDocument4 paginiNasir Ali Bhatti 5120 Bscs C EveningSadeed AhmadÎncă nu există evaluări

- fqp9n25c fqpf9n25ct Fqpf9n25cydtuDocument10 paginifqp9n25c fqpf9n25ct Fqpf9n25cydtuEsther AsturiasÎncă nu există evaluări

- CEF02N6Document5 paginiCEF02N6Zsolt SzoverfiÎncă nu există evaluări

- EC630L - VLSI Lab Manual CadenceDocument19 paginiEC630L - VLSI Lab Manual CadenceRiya JoshiÎncă nu există evaluări