Documente Academic

Documente Profesional

Documente Cultură

Lab 8 Report

Încărcat de

api-427877684Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lab 8 Report

Încărcat de

api-427877684Drepturi de autor:

Formate disponibile

Lab 8 Report

Author(s): Mikolaj Pal

Course: EE2174

Lab Section: L06

Date of Lab Completion: April 19, 2019

Date Submitted: April 25, 2019

Teaching Assistant: Michael Maurer

Table of Contents

1 Introduction ............................................................................................................................. 3

2 Background .............................................................................................................................. 4

3 Results ..................................................................................................................................... 5

3.1 Part 1 ................................................................................................................................ 5

3.2 Part 2 ................................................................................................................................ 7

3.3 Part 3 ................................................................................................................................ 9

3.4 Part 4 .............................................................................................................................. 10

3.5 Part 5 .............................................................................................................................. 11

3.6 Part 6 .............................................................................................................................. 11

3.7 Part 7 .............................................................................................................................. 12

4 Discussion .............................................................................................................................. 13

5 Conclusion ............................................................................................................................. 13

6 Appendix ............................................................................................................................... 14

Page 2 of 19 Lab 8 Report

1 Introduction

With the Verilog language, the DE2-115 board with the Cyclone IV E FPGA, and the

Quartus Prime software, with Library Parametrized Modules, latches and flip-flops are able to be

programmed to store values and to reset them, which was the goal of this lab. These values were

displayed to the user with the green and red LEDs in and on the seven-segment hexadecimal

displays. To be able to increment and reset the values, SR and D latches would be used for the

storage of the input values, which would be input through the slide switches. With the final

program, the built-in Library Parametrized Modules (LPMs) were used to create counters and

instantiate them through the main program for the part.

Page 3 of 19 Lab 8 Report

2 Background

The DE2-115 board is the main hardware used for Lab 8 and is able to implement logic

circuits for nearly all projects. To connect the board to the computer, a USB cable was used to

program the DE2-115 board with the personal computer in the lab. Across the bottom side of the

board, there are a set of eight green and sixteen red LED lights. They have their own individual

connections and pins, which are labeled at the bottom of each light and are programmable through

the board. To program the Cyclone IV board, Quartus Prime 16.0 CAD software was the software

used and Verilog the programming language. Quartus Prime is able to support various methods of

circuit description, which includes the Verilog language. A hardware description language,

Verilog is specialized for the programming of digital logic circuits and electronics. For this lab,

the programs were created with modular and structural approaches.

On the lower end of the board, a set of 18 vertical slide switches. The switches are

straightforward 1-bit binary input devices with only two settings: DOWN towards the edge and

UP away from the edge. The slide switches were used as inputs for parts 3 through 7 as inputs for

the values for the flip-flop and to increment and reset values. These switches are not debounced,

meaning that they are not corrected for variances that may occur during the changes of their state

by the user. They may wobble between the binary values of 1 and 0, which may cause error. In

Lab 8, a set of debounced inputs were used in parts 5 and 6. These were push-buttons (labeled

KEY on the board) and were used to increment up the values displayed on the red LED lights in

part 5 and the values on the hexadecimal displays in part 6. Above the LEDs and slide switches

are eight 7-segment hexadecimal displays that are in two pairs and a group of four together. Each

segment has a pin connection to the Cyclone IV that is programmable. They are programmable as

a 7 bit value with every bit representing one of the segments on the display. These displays were

used in part 6, where the hexadecimal values from the input were required to be displayed on

displays 0-3 and then copied over to 7-4.

Library Parametrized Modules are custom configurable modules located in the Quartus II

program. There are many different ones that have many different uses, with a counter being created

in the case of this lab. They are configured using a built-in wizard, where the user is able to specify

the inputs, outputs, and their sizes in bits. After completion of the wizard, the code is generated in

a separate program and a template file is created for calling the program through instantiation.

Latches are circuits that are able to store data and contain two stable states. They are used to store

data and to reset the data. A flip-flop is a type of latch that only uses one bit and is used to store a

state.

Page 4 of 19 Lab 8 Report

3 Results

3.1 Part 1

In Part 1, a simple Gated SR Latch was created using the structural sample code provided

in Listing 1 of the lab manual and the actual program code in Listing 6.1 in the Appendix. The

Gated SR Latch is a simple latch consisting of two and gates and two nor gates, and two numerical

inputs and a clock input. It also relies on a previous output value to generate its output, and the

lack of it is shown in Figure 3.1 below. At first the code included a directive in the signals, defined

as wire in the code, stating “/* synthesis keep */”. This directive preserves the signals and the

defined logic as separate elements, called Look Up Tables (LUTs), which is shown in Figure 3.2

on the following page. When this directive was removed from the code, this resulted in a single

LUT to be generated for the entire program, which is shown in Figure 3.3 on the following page.

Figure 3.1: Functional Simulation for Part 1

Page 5 of 19 Lab 8 Report

Figure 3.2: Technology view for Part 1 with synthesis

Figure 3.3: Technology View for Part 1 without Synthesis

Figure 3.4: Implemented Circuit for Part 1

Page 6 of 19 Lab 8 Report

3.2 Part 2

For Part 2, a Gated D Latch was constructed in Quartus Prime by modification of the code

from Part 1. Initially, the “/* synthesis keep */” directive was included in the code, which resulted

in the LUTs and logic elements to be separate, as shown in Figure 3.6 below. This was done to

implement signals Qa, Qb, R_g, S_g, and R, as shown in the Implemented Circuit in Figure 3.5.

Removal of the directive resulted in a single LUT being created, as shown in Figure 3.7 below.

Between the functional and timing simulations, Figures 3.8 and 3.9 respectably, there is a slight

delay in the time where the output is expected. This can be attributed to either the actual physical

limitations of the board that cause these delays, which are taken into account with the timing

simulation, or the “/* synthesis keep */” directive, which results in multiple LUTs to be created

instead of just one, which could take longer to process. Just like the SR Latch in Part 1, a previous

value is required for the output to be generated.

Figure 3.5: Implemented Circuit for Part 2

Figure 3.6: Technology View for Part 2 with synthesis

Figure 3.7: Technology View for Part 2 without synthesis

Page 7 of 19 Lab 8 Report

Figure 3.8: Functional Simulation for Part 2

Figure 3.9: Timing Simulation for Part 2

Page 8 of 19 Lab 8 Report

3.3 Part 3

Part 3 requires the actual physical implementation of the Gated D Latch into the DE2-115

board. The D input was the slide switch SW[0], and the slide switch for the clock input was SW[1].

A single red LED, LEDR[0], was the final output Q, as shown in Listing 6.3 in the Appendix. The

behavior was as expected in Part 2 for the functional simulation, with no significant structural

errors occurring during compilation of the program and the programming of the board.

Page 9 of 19 Lab 8 Report

3.4 Part 4

The creation of a counter, required for Part 4, was completed with a flip-flop and sequential

logic in programming. Code from Listing 3 in the lab manual was used as a starting point for the

implementation of this part, with slide switches SW[1] and SW[0] being used for the clock input

and E input respectably. The output needed to be larger than a single bit, and was set to 16 bits as

instructed by the lab manual. The reset used was an asynchronous low reset, and a clock trigger

set to positive edge. In the code, “<=” was used in place of the standard equal sign to allow the

line of code to be executed independently of the other lines. Through a functional simulation, the

program was determined to function properly, with the increase of values functioning as expected.

Shown in Figure 3.10 below is the functional simulation, where the asynchronous low reset is

shown resetting the entirety of the output Q as expected.

Figure 3.10: Functional Simulation for Part 4

Page 10 of 19 Lab 8 Report

3.5 Part 5

For Part 5, the program from Part 4 was implemented into the DE2-115 board, with the

addition of a second counter that required two instantiations of the main code, resulting in two

counters as shown in Listing 6.5 in the Appendix. Switches SW[0] and SW[1] were the E inputs

while SW[3] was the reset in both instantiations. Switch SW[2] was the clock in the first

instantiation while push button KEY[1] served as the clock in the second instantiation. There were

two outputs in this part, the green LEDs and the red LEDs respectably. They were switched

between with SW[3] with green being active when it was off and red when it was on. The green

LEDs were incremented up by 1 when SW[0] was on and the reds when SW[1] was on. Since the

push buttons were debounced, there was no error or unexpected changes in value when KEY[1]

was triggered. However, when SW[2] was triggered, there were unexpected increases in the value

displayed on the green LEDs when toggled, since additional spikes occurred when the states were

changed.

3.6 Part 6

The aim for Part 6 was to develop a program that displayed the value of a 16 bit input on

the four seven segment displays HEX 4-7, and then copied them onto displays 0-3, while being

able to reset. The value displayed was created through a 16-bit slide switch input, which was copied

onto the 16-bit input B and displayed on HEX 4-7. When push-button KEY[1] was triggered, the

value in B was transferred over to A and displayed on HEX 0-3. KEY[0] was used to reset value

A to zero, and was the asynchronous reset for this program. This was the most complex of all the

programs, as at first the instructions were not clear and resulted in the incorrect program being

created. However, after a considerable effort, this was corrected.

Page 11 of 19 Lab 8 Report

3.7 Part 7

In Part 7, a Library Parametrized Module (LPM) was created to simulate the 16-bit counter

created in part 4. Using the built-in wizard, options were enabled to have the required

asynchronous low resent and the clock enable. In the main program for the part, shown in Listing

6.7 in the Appendix, the created LPM was called upon to do the bulk of the work. In the

instantiation of the LPM, the variables from the main program were input in replace of the

variables provided in the template generated for the program. The LPM operated as expected,

which is shown by the functional simulation in Figure 3.11: Functional Simulation for Part 7

below.

Figure 3.11: Functional Simulation for Part 7

Page 12 of 19 Lab 8 Report

4 Discussion

In the prelab assignment for this lab, it was predicted that a benefit of using the LPM was

the simplification of the main program that used instantiations to call upon it instead of having to

manually write the code within that program. Because of this, it was also predicted that diagnosing

errors and fixing them would be easier due to the lack of a complex code structure in the main

program that would’ve otherwise been compromised. This turned out to be true, as some minor

errors occurred when initially writing the main program, which were able to be quickly resolved

and did not affect the module. Additionally, compilation errors occurred with the counting module,

and those were able to be resolved easily with reconfiguration through the wizard. This also applies

to the modular design approach to coding, as the LPM was called upon in the main program

through an instantiation and the bulk of the work was done within the LPM.

5 Conclusion

Library Parametrized Modules are able to be used to easily create components of a program

in a shorter amount of time that would’ve otherwise been consumed by the manual creation of

these components. Quartus has a large library of various LPMs to suit user needs, so productivity

is increased. These LPMs are separate programs that are called upon through instantiation in the

main program to do a large amount of the work. Latches are used in various applications, and for

this lab were used to create a storage element for the storage of values and their reset. Flip-Flops

are used for these purposes but also for the upwards incrementation of the values, especially for

multi-bit outputs. This can then be used as a counter with a clock input, which are useful for various

real-life situations, such as sorting and digital clocks. Using Verilog and Quartus Prime, these are

able to be created and to help the user further educate themselves in the field of Digital Logic.

Page 13 of 19 Lab 8 Report

6 Appendix

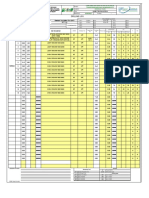

Figure 6.1: First Page of Lab 8 Submission Sheet

Page 14 of 19 Lab 8 Report

Figure 6.2: Second Page of Lab 8 Submission Sheet

module Lab8Part1 (Clk, R, S, Q); //module initialization

input Clk, R, S; //clock and R and S are inputs

output Q;

wire R_g, S_g, Qa, Qb /* Synthesis Keep */; //synthesis kept to have individual gates

and (R_g, R, Clk); //and gate

and (S_g, S, Clk); //and gate

nor (Qa, R_g, Qb); //nor gate

nor (Qb, S_g, Qa);//nor gate, end of SR Latch

assign Q = Qa; //main output assigned to Qa from latch

endmodule

Listing 6.1: Code for Part 1

Page 15 of 19 Lab 8 Report

module Lab8Part2 (Clk, D, Q);

input Clk, D; //input of clock and D

output Q;

wire R, S, R_g, S_g, Qa, Qb /* synthesis keep*/; //synthesis kept to have individual gates

assign S = D; //S is D

assign R = ~D; //R is the opposite of D

nand (R_g, R, Clk); //nand gate

nand (S_g, S, Clk); //nand gate

nand (Qa, S_g, Qb); //nand gate

nand (Qb, R_g, Qa); //nand gate, end of D latch

assign Q = Qa; //main output of Q assigned to Qa output of D latch

endmodule

Listing 6.2: Code for Part 2

module Lab8Part3 (SW, LEDR);

input [1:0]SW; //switches from board are inputs, two bit input

output [1:0]LEDR; //red LEDs are outputs

wire R, S, R_g, S_g, Qa, Qb /* synthesis keep*/; //synthesis kept to have individual gates

assign S = SW[0]; //S is the switch input

assign R = ~SW[0]; //R is the opposite of the switch input

nand (R_g, R, SW[1]); //nand gate

nand (S_g, S, SW[1]); //nand gate

nand (Qa, S_g, Qb); //nand gate

nand (Qb, R_g, Qa); //nand gate

assign LEDR[0] = Qa; //the main output from latch is red LED

endmodule

Listing 6.3: Code for Part 3

Page 16 of 19 Lab 8 Report

module Lab8Part4 (reset, SW, Q);

input reset;

input [1:0]SW;

output reg [15:0]Q;

always @(posedge SW[1] or negedge reset)

begin

if(reset==0)

Q<=0;

else if(SW[0])

Q<=Q+1;

end

endmodule

Listing 6.4: Code for Part 4

module Lab8Part5 (SW, KEY, LEDR, LEDG);

input [3:0]SW; //switches are inputs

input [1:0]KEY; //push buttons are inputs

output reg [15:0]LEDR; //Red LEDs as outputs

output reg [7:0]LEDG; //Green LEDs as outputs

always @(posedge SW[2] or negedge SW[3]) //when switch 2 increases or switch 3

decreases

begin

if(SW[3]==0) //if switch 3 is not activated

LEDG<=0; //all green LEDs off

else if(SW[0]) //else if switch 0 is toggled

LEDG<=LEDG+1; //increment binary value displayed by green LEDs up by 1

end

always @(negedge KEY[1] or posedge SW[3]) //when push button 1 decreases or switch

3 increases

begin

if(SW[3]==1) //if switch 3 is activated

LEDR<=0; //all red LEDs off

else if(SW[1]) //else if switch 1 is toggled

LEDR<=LEDR+1; //increment binary value displayed by red LEDs up by 1

end

endmodule

Listing 6.5: Code for Part 5

Page 17 of 19 Lab 8 Report

module Lab8Part6 (SW, KEY, HEX0, HEX1, HEX2, HEX3, HEX4, HEX5, HEX6, HEX7);

input [15:0]SW; //switches are inputs

input [3:0]KEY; //push buttons are inputs

output [0:6]HEX0, HEX1, HEX2, HEX3, HEX4, HEX5, HEX6, HEX7; //7-segment hex

displays are ouputs

reg [15:0]A, B; //temporary storage values

always @(posedge KEY[0] or negedge KEY[1]) //when push button 1 increases or push

button 2 decreases

begin

A = SW; //values from switch inputs copied over to A

if (KEY[1]==0) //if push button 1 is not activated

begin

B = 0; //displays 5-8 are zero

end

else //if push button 1 is activated

begin

B = A; //values displayed on displays 1-4 are copied over to displays 5-8

end

end

hex7seg inst1(A[3:0], HEX0); //instantiations for value converter program

hex7seg inst2(A[7:4], HEX1);

hex7seg inst3(A[11:8], HEX2);

hex7seg inst4(A[15:12], HEX3);

hex7seg inst5(B[3:0], HEX4);

hex7seg inst6(B[7:4], HEX5);

hex7seg inst7(B[11:8], HEX6);

hex7seg inst8(B[15:12], HEX7);

endmodule

Listing 6.6: Code for Part 6

Page 18 of 19 Lab 8 Report

module Lab8Part7 (reset, SW, Q);

input reset;

input [1:0]SW;

output wire [15:0]Q;

count1 count1_inst (

.aset ( reset ),

.clk_en ( SW[0] ),

.clock ( SW[1] ),

.q ( Q )

);

endmodule

Listing 6.7: Code for Part 7

Page 19 of 19 Lab 8 Report

S-ar putea să vă placă și

- ReportTemplate PracticalTask or ProjectDocument27 paginiReportTemplate PracticalTask or ProjectDony Beast (DurraniFared)Încă nu există evaluări

- Department of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VIDocument53 paginiDepartment of Electronics & Communication Engineering Lab Manual B.Tech Year: 3rd Semester: VImacfready100% (1)

- EEL4742-Lab-Manual-Embedded SystemsDocument101 paginiEEL4742-Lab-Manual-Embedded SystemsSusie KÎncă nu există evaluări

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDe la EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxEvaluare: 4 din 5 stele4/5 (1)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationDe la EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationÎncă nu există evaluări

- How To Convert A Project From IAR To CCS - Texas Instruments WikiDocument11 paginiHow To Convert A Project From IAR To CCS - Texas Instruments Wikiteomondo100% (1)

- Lab Report #2Document9 paginiLab Report #2Noura MDÎncă nu există evaluări

- Laboratory 3Document8 paginiLaboratory 3Xing MingÎncă nu există evaluări

- Lab 6Document11 paginiLab 6vivek2mbÎncă nu există evaluări

- Lab 2: Introduction To Verilog HDL and Quartus: September 8, 2009Document8 paginiLab 2: Introduction To Verilog HDL and Quartus: September 8, 2009N.RAMAKUMARÎncă nu există evaluări

- CPS_LAB_REPORT_FINAL (1)Document38 paginiCPS_LAB_REPORT_FINAL (1)devikam230354ecÎncă nu există evaluări

- Laboratory Manual Rec 451 - Microprocessors & Microcontrollers LabDocument28 paginiLaboratory Manual Rec 451 - Microprocessors & Microcontrollers Lababhishek singhÎncă nu există evaluări

- BME 438 Digital Logic Design and Computer Architecture LabDocument73 paginiBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaÎncă nu există evaluări

- Activity 1 Group 9Document16 paginiActivity 1 Group 9RUEL ALEJANDROÎncă nu există evaluări

- 04using Library ModulesDocument20 pagini04using Library ModulesHaoyuan LiuÎncă nu există evaluări

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 paginiDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveÎncă nu există evaluări

- CE 264 Lab Project: Design of a Digital Circuit for Multiplication and Display of ResultDocument9 paginiCE 264 Lab Project: Design of a Digital Circuit for Multiplication and Display of ResultCalvin SaldanhaÎncă nu există evaluări

- Altera's MAX+plus II and The UP 1 Educational Board: Advanced Logic Design, CPE/EE 422/502Document59 paginiAltera's MAX+plus II and The UP 1 Educational Board: Advanced Logic Design, CPE/EE 422/502IbrahimFaroukSolarÎncă nu există evaluări

- Lab Manual: Microprocessor Theory & InterfacingDocument127 paginiLab Manual: Microprocessor Theory & InterfacingusmanzahidÎncă nu există evaluări

- Design and Implement n-Bit Adder/SubtractorDocument11 paginiDesign and Implement n-Bit Adder/SubtractorMuneeb ahmadÎncă nu există evaluări

- MPMC Sample FileDocument64 paginiMPMC Sample FileAakritiÎncă nu există evaluări

- Microcontrollers 2017-18 Lab ManualDocument58 paginiMicrocontrollers 2017-18 Lab ManualSUNIL KUMAR100% (1)

- Verilog LabDocument70 paginiVerilog Labhkes rcrÎncă nu există evaluări

- Microcontroller Synthesized Function Generator: Visa M. Ibrahim .Oni Taiwo .Uyoata E. UyoataDocument7 paginiMicrocontroller Synthesized Function Generator: Visa M. Ibrahim .Oni Taiwo .Uyoata E. UyoataIJERDÎncă nu există evaluări

- final DDCOLab manual (1)Document31 paginifinal DDCOLab manual (1)susheela NatarajuÎncă nu există evaluări

- Distance Measurement System Project Report - Amit BarDocument32 paginiDistance Measurement System Project Report - Amit BarAmit BarÎncă nu există evaluări

- DLD-2014 - Practical BookDocument75 paginiDLD-2014 - Practical BookMuhammad Ishtiaq0% (1)

- 19 MSP1056 MicroprocessorDocument9 pagini19 MSP1056 Microprocessorsakshi sharmaÎncă nu există evaluări

- ESD Manual StudentsDocument55 paginiESD Manual StudentsNimesh PrajapatiÎncă nu există evaluări

- Application SSC02 eDocument4 paginiApplication SSC02 eDragosFlorinLismanÎncă nu există evaluări

- Tutorial On Simatic s5 Control System :practical Programming and Fault FindingDocument22 paginiTutorial On Simatic s5 Control System :practical Programming and Fault Findingak4dili80% (5)

- Project2 PsocDocument10 paginiProject2 PsocKarthik V KalyaniÎncă nu există evaluări

- Modul FPGA AlteraDocument22 paginiModul FPGA AlteraMichael SiagianÎncă nu există evaluări

- Devloper BoardDocument82 paginiDevloper Boardpukhraj titreÎncă nu există evaluări

- Traffic Controller Using Microprocessor 8085: YEAR-2011Document69 paginiTraffic Controller Using Microprocessor 8085: YEAR-2011Raj LuckyÎncă nu există evaluări

- 32 Bit Multiplication and Division ALU Design Based On RISC StructureDocument4 pagini32 Bit Multiplication and Division ALU Design Based On RISC StructureVishnu Kumar NadarÎncă nu există evaluări

- Vlsi Manual 2013-2014Document36 paginiVlsi Manual 2013-2014hr_suresh_kÎncă nu există evaluări

- Microcontroller Based Digital Code Lock Project ReportDocument50 paginiMicrocontroller Based Digital Code Lock Project ReportjoÎncă nu există evaluări

- Using Library ModulesDocument23 paginiUsing Library ModulesJuan Rafael Villen PulidoÎncă nu există evaluări

- Mini Line Follower Project ReportDocument23 paginiMini Line Follower Project ReportVinod Pathak100% (1)

- LAB 1: TO Fpga Hardware, Control Design and Simulation: ObjectivesDocument13 paginiLAB 1: TO Fpga Hardware, Control Design and Simulation: ObjectivesAidil AzharÎncă nu există evaluări

- MethodologyDocument18 paginiMethodologyDaukan Chavez AlbercaÎncă nu există evaluări

- Internet of Things Lab Manual Up DateDocument53 paginiInternet of Things Lab Manual Up DateASHU KÎncă nu există evaluări

- Microprocessor Lab Manual GuideDocument99 paginiMicroprocessor Lab Manual Guidetest dummyÎncă nu există evaluări

- PCB Lab Manual IIISem ECE PDFDocument46 paginiPCB Lab Manual IIISem ECE PDFDeepak BaghelÎncă nu există evaluări

- Using C With Altera DE2 Board: ContentsDocument11 paginiUsing C With Altera DE2 Board: ContentsHoang TungÎncă nu există evaluări

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 paginiMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyÎncă nu există evaluări

- 03 Development of ScalableDocument15 pagini03 Development of ScalableprjpublicationsÎncă nu există evaluări

- Microprocessor Report 1Document11 paginiMicroprocessor Report 1GREATJUSTGREATÎncă nu există evaluări

- Harsh AlDocument81 paginiHarsh AlSmit VahalkarÎncă nu există evaluări

- Ecen 248 Lab 9 ReportDocument5 paginiEcen 248 Lab 9 Reportapi-241454978Încă nu există evaluări

- Al Azhar University - Gaza: Microcontroller Report "1" WorkshopDocument11 paginiAl Azhar University - Gaza: Microcontroller Report "1" WorkshopMohamed A SbaihÎncă nu există evaluări

- Reconfigurable FPGA Implementation of Digital Communication SystemDocument17 paginiReconfigurable FPGA Implementation of Digital Communication Systemsudha_804331380Încă nu există evaluări

- PD78 Series Microcontroller EEPROM Programmer User's Guide: Engineering Technical LaboratoryDocument14 paginiPD78 Series Microcontroller EEPROM Programmer User's Guide: Engineering Technical LaboratoryDaniel Norberto DemariaÎncă nu există evaluări

- PD78 Series Microcontroller EEPROM Programmer User's Guide: Engineering Technical LaboratoryDocument14 paginiPD78 Series Microcontroller EEPROM Programmer User's Guide: Engineering Technical LaboratoryUbaldo BritoÎncă nu există evaluări

- ES Lab FileDocument37 paginiES Lab FileMøhït JáñgírÎncă nu există evaluări

- VHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaDocument5 paginiVHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaInternational Organization of Scientific Research (IOSR)Încă nu există evaluări

- PCB Lab Manual Iiisem Ece PDFDocument46 paginiPCB Lab Manual Iiisem Ece PDFkathirdcnÎncă nu există evaluări

- Tutorial C30Document7 paginiTutorial C30Fabio Ferreira AngaritaÎncă nu există evaluări

- Lab 6 ReportDocument13 paginiLab 6 Reportapi-427877684Încă nu există evaluări

- Lab 9 ReportDocument24 paginiLab 9 Reportapi-427877684Încă nu există evaluări

- Lab 8 ReportDocument13 paginiLab 8 Reportapi-427877684Încă nu există evaluări

- Pal-Tang Black Box PresentationDocument11 paginiPal-Tang Black Box Presentationapi-427877684Încă nu există evaluări

- Lab 9 ReportDocument8 paginiLab 9 Reportapi-427877684Încă nu există evaluări

- Project Book - Hazard AnalysisDocument2 paginiProject Book - Hazard Analysisapi-427877684Încă nu există evaluări

- HstranscriptDocument2 paginiHstranscriptapi-427877684Încă nu există evaluări

- Project Book - NX ModelDocument3 paginiProject Book - NX Modelapi-427877684Încă nu există evaluări

- Updraft Tower PresentationDocument13 paginiUpdraft Tower Presentationapi-427877684Încă nu există evaluări

- Encabo-Pal FinalrestofpaperDocument56 paginiEncabo-Pal Finalrestofpaperapi-427877684Încă nu există evaluări

- RC EXAM ELEC10 Electronic Devices and Circuits LC CircuitsDocument2 paginiRC EXAM ELEC10 Electronic Devices and Circuits LC CircuitsaljamierÎncă nu există evaluări

- Vba Codes ExcelDocument46 paginiVba Codes ExcelKen Matsuda100% (1)

- Inspiron 15 3552 Laptop Service Manual en UsDocument68 paginiInspiron 15 3552 Laptop Service Manual en UsVladimir DelgadoÎncă nu există evaluări

- Introduction To Hadoop and Mapreduce - VM SetupDocument4 paginiIntroduction To Hadoop and Mapreduce - VM SetupDavid LlanesÎncă nu există evaluări

- Structure Charts: Agenda: - Use of Structure Charts - Symbols - How To CreateDocument12 paginiStructure Charts: Agenda: - Use of Structure Charts - Symbols - How To CreateSujata RoyÎncă nu există evaluări

- Conventional Software Testing Using White Box Method: KINETIK, Vol. 3, No. 1, February 2018, Pp. 65-72Document8 paginiConventional Software Testing Using White Box Method: KINETIK, Vol. 3, No. 1, February 2018, Pp. 65-72Achmad YuszrilÎncă nu există evaluări

- SRS SampleDocument31 paginiSRS SampleAbhishek DuttaÎncă nu există evaluări

- TH L47E5S Panasonic+ (TNPH0993)Document60 paginiTH L47E5S Panasonic+ (TNPH0993)Luiz Gustavo SantosÎncă nu există evaluări

- Learning & Performance Catalog: We Empower People WorldwideDocument56 paginiLearning & Performance Catalog: We Empower People WorldwideStar BreakerÎncă nu există evaluări

- Feedbacks Re Online Appointment System of MECODocument2 paginiFeedbacks Re Online Appointment System of MECORic SaysonÎncă nu există evaluări

- ST 252Document2 paginiST 252jamesyuÎncă nu există evaluări

- Testing Interview Questions: Automation Testing ExperienceDocument14 paginiTesting Interview Questions: Automation Testing ExperienceSuman kulliÎncă nu există evaluări

- ABAP ObjectsDocument3 paginiABAP ObjectsvenkatÎncă nu există evaluări

- 12drilling Log Spt04 160622Document2 pagini12drilling Log Spt04 160622Angelica E. Rabago LopezÎncă nu există evaluări

- Telecommunications LawDocument4 paginiTelecommunications LawSWATIÎncă nu există evaluări

- Default Modem Password ListDocument72 paginiDefault Modem Password ListEmieda EraineÎncă nu există evaluări

- Toughpad Fz-G1 Atex: Atex A Zone 2 Certified Fully Rugged Windows 10 Pro TabletDocument2 paginiToughpad Fz-G1 Atex: Atex A Zone 2 Certified Fully Rugged Windows 10 Pro TabletTop5 In VietnamÎncă nu există evaluări

- Ciena DTM-100G2 - DS PDFDocument2 paginiCiena DTM-100G2 - DS PDFrobert adamsÎncă nu există evaluări

- Universal Remote Instruction Manual: RM24918 RM84918Document16 paginiUniversal Remote Instruction Manual: RM24918 RM84918Antonio GonçalvesÎncă nu există evaluări

- Best Practices For Tensorrt PerformanceDocument20 paginiBest Practices For Tensorrt PerformanceacabaÎncă nu există evaluări

- What is Big Data? Four V's and Uses in BusinessDocument222 paginiWhat is Big Data? Four V's and Uses in BusinessraviÎncă nu există evaluări

- Electronic Hand Control MH 2000Document3 paginiElectronic Hand Control MH 2000Christian ChumpitazÎncă nu există evaluări

- Giddings & Lewis Sect10 MaintenanceDocument10 paginiGiddings & Lewis Sect10 MaintenanceAngel AdautaÎncă nu există evaluări

- BSP - Commercial AAV - 10bar - DataSheet - V1.1 - 11-2022Document1 paginăBSP - Commercial AAV - 10bar - DataSheet - V1.1 - 11-2022j.iqubalÎncă nu există evaluări

- Modeling Simulation and System Engineering Lecture PDFDocument40 paginiModeling Simulation and System Engineering Lecture PDFcemokszÎncă nu există evaluări

- Cpa Is Not DeadDocument3 paginiCpa Is Not DeadAhmed HaaÎncă nu există evaluări

- Résumé For Arjun JayaramanDocument1 paginăRésumé For Arjun JayaramanArjun JayaramanÎncă nu există evaluări

- New Generation of 5-Part: Flexible System Expandability Less Running Costs SpecificationsDocument2 paginiNew Generation of 5-Part: Flexible System Expandability Less Running Costs Specificationsamor kermayaÎncă nu există evaluări

- HD 110 / HD 110K: - Articulated Tandem Roller With Two Vibratory Drums - Articulated Combi Roller With Vibratory DrumDocument2 paginiHD 110 / HD 110K: - Articulated Tandem Roller With Two Vibratory Drums - Articulated Combi Roller With Vibratory DrumSanÎncă nu există evaluări