Documente Academic

Documente Profesional

Documente Cultură

Lab 3-4

Încărcat de

Asad RehanDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Lab 3-4

Încărcat de

Asad RehanDrepturi de autor:

Formate disponibile

Lab Experiment | 3

LAB # 3:

Design the combinational circuit using library building technique of VHDL programming

Objective

To learn to utilize the library functions in VHDL

To learn how to create own library in VHDL

Pre-Lab

Part 1 – Creating your own library components

Frequently used pieces of VHDL code are usually written in the form of

COMPONENTS, FUNCTIONS, or PROCEDURES. Such codes are then placed inside

a PACKAGE and compiled into the destination LIBRARY. The importance of this

technique is that it allows code partitioning, code sharing, and code reuse.

We start by describing the structure of a PACKAGE. Besides COMPONENTS,

FUNCTIONS, and PROCEDURES, it can also contain TYPE and CONSTANT

definitions, among others. Its syntax is presented below

PACKAGE package_name IS

(declarations)

END package_name;

[ PACKAGE BODY package_name IS

(FUNCTION and PROCEDURE descriptions)

END package_name; ]

|CPE343 | Computer Organization & Architecture Lab Manual 25

Lab Experiment | 3

The syntax is composed of two parts: PACKAGE and PACKAGE BODY. The first part

is mandatory and contains all declarations, while the second part is necessary only when

one or more subprograms (FUNCTION or PROCEDURE) are declared in the upper

part, in which case it must contain the descriptions (bodies) of the subprograms.

PACKAGE and PACKAGE BODY must have the same name.

The declaration list can contain the following COMPONENT, FUNCTION,

PROCEDURE, TYPE, CONSTANT etc.

EXAMPLE:

The example below shows a how to use PACKAGE called my_components. It contains

three components inverter, nand_2 and nand_3 in it.

---------------------Code for myinverter.vhd

library IEEE;

use ieee.std_logic_1164.all;

entity myinverter is

port(

inv_in: in std_logic;

inv_out: out std_logic

);

end myinverter;

architecture bhv of myinverter is

begin

inv_out <= not inv_in;

end bhv;

---------------------Code for nand_2.vhd

|CPE343 | Computer Organization & Architecture Lab Manual 26

Lab Experiment | 3

library IEEE;

use ieee.std_logic_1164.all;

entity nand_2 is

port(

nand2_in1: in std_logic;

nand2_in2: in std_logic;

nand2_out: out std_logic

);

end nand_2;

architecture nand_2 of nand_2 is

begin

nand2_out <= NOT (nand2_in1 AND nand2_in2);

end nand_2;

---------------------Code for nand_3.vhd

library IEEE;

use ieee.std_logic_1164.all;

entity nand_3 is

port(

nand3_in1: in std_logic;

nand3_in2: in std_logic;

nand3_in3: in std_logic;

nand3_out: out std_logic

);

end nand_3;

architecture nand_3 of nand_3 is

begin

nand3_out <= NOT (nand3_in1 AND nand3_in2 AND nand3_in3);

end nand_3;

---------------------Code for my_components.vhd

library ieee;

use ieee.std_logic_1164.all;

package my_components is

component myinverter is

port( inv_in: in std_logic; inv_out: out std_logic);

end component;

component nand_2 is

port ( nand2_in1: in std_logic;

nand2_in2: in std_logic;

nand2_out: out std_logic

);

end component;

component nand_3 is

port(

nand3_in1: in std_logic;

nand3_in2: in std_logic;

nand3_in3: in std_logic;

nand3_out: out std_logic

|CPE343 | Computer Organization & Architecture Lab Manual 27

Lab Experiment | 3

);

end component;

end my_components;

Complete the VHDL code for

library ieee;

use ieee.std_logic_1164.all;

use work.my_components.all;

entity my_package is

port( a,b,c,d : in std_logic;

x,y: out std_logic);

end my_package;

architecture bhv1 of my_package is

signal w: std_logic;

begin

U1: myinverter PORT MAP (b,w);

U2: nand_2 PORT MAP(a,b,x);

U3: nand_3 PORT MAP(w,c,d,y);

end bhv1;

a b c d x y

PIN_AD27 PIN_AC27 PIN_AC28 PIN_AB28 PIN_G19 PIN_F19

|CPE343 | Computer Organization & Architecture Lab Manual 28

Lab Experiment | 3

Lab Tasks

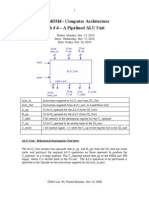

Part 2 -ALU implementation using your library components

Using the techniques, you learned from Part 1, implement a single bit ALU shown below

using VHDL codes and components in your library.

Your library should include

Orgate

Andgate

Nandgate

Halfadder

Fulladder

mux.

The Mux code is given below.

entity MUX_4_1 is

port (

s: in std_logic_vector(1 downto 0); --Mux selector

A, B, C, D: in std_logic; --Mux input data lines

Z: out std_logic); --result

end MUX_4_1;

architecture Behav of MUX_4_1 is

begin

Z <= A when s = “00” else

B when s = “01” else

C when s = “10” else

D;

End behav;

|CPE343 | Computer Organization & Architecture Lab Manual 29

Lab Experiment | 3

Implement the given ALU by writing VHDL modules and storing in the library. Connect the inputs

in1, in2, C_in, and Selector to switches and the outputs, result and C_out, to LEDs as

S1 S0 C_in In2 In1 x y

PIN_AB27 PIN_AD27 PIN_AC27 PIN_AC28 PIN_AB28 PIN_G19 PIN_F19

Lab Assessment

Pre-Lab /1

Performance /3

/10

Results /2

Viva /2

Lab Report /2

Instructor Signature and Comments

|CPE343 | Computer Organization & Architecture Lab Manual 30

Lab Experiment | 4

LAB # 4:

Design the sequential circuit using VHDL programming techniques

Objective

To design sequential circuit using VHDL.

To design a finite state machine using VHDL

Pre-Lab

Part 1 -Familiarize yourself with Sequential Circuit

Introduction:

Combinational circuits and systems produce an output based on input variables only. Sequential

circuits use current input variables and previous input variables by storing the information and

putting back into the circuit on the next clock (activation) cycle.

Fig 4.1 Sequential Circuit

Types of Sequential Circuit:

There are two types of sequential circuit, synchronous and asynchronous.

Synchronous Circuit:

Synchronous types use pulsed or level inputs and a clock input to drive the circuit (with restrictions

on pulse width and circuit propagation).

Fig 4.2 Synchronous

|CPE343 | Computer Organization & Architecture Lab Manual 31

Lab Experiment | 4

Asynchronous Circuit:

Asynchronous sequential circuits do not use a clock signal as synchronous circuits do. Instead the

circuit is driven by the pulses of the inputs. You will not need to know any more about

asynchronous circuits for this course.

Fig 4.3 Asynchronous

Part 2 –Introduction of Latches and Flip Flops

D Latch:

Latch is an electronic device that can be used to store one bit of information. The D latch is used to

capture, or 'latch' the logic level which is present on the Data line when the clock input is high. If

the data on the D line changes state while the clock pulse is high, then the output, Q, follows the

input, D. When the CLK input falls to logic 0, the last state of the D input is trapped and held in

the latch.

Fig 4.4 Latch Timing

|CPE343 | Computer Organization & Architecture Lab Manual 32

Lab Experiment | 4

D Flip Flop:

The working of D flip flop is similar to the D latch except that the output of D Flip Flop takes the

state of the D input at the moment of a positive edge at the clock pin (or negative edge if the clock

input is active low) and delays it by one clock cycle.

Fig 4.5 Flip Flop Timing

Part 3 – Using 50MHz Clock of Quartus Cyclone IV FPGA board

The clock provided by the board is 50MHz, which is too fast for seeing the sequential circuit

output through LEDs for verification. Therefore, we need to divide this clock into a slow clock.

For this, we define two temporary signals.

The slow clock, sclk, is generated through a process and a current statement as shown below:

Note that the 24-bit signal called “clkdiv” is incremented by one per every mclk clock cycle. The

slow clock, sclk, is generated by only copying the 24-th bit of the signal clkdiv. Write a code to

|CPE343 | Computer Organization & Architecture Lab Manual 33

Lab Experiment | 4

use “sclk” to run the arbitrary sequential circuit. This would allow you to see the changes of

sequential circuit through LEDs.

When you run “Implement Design”, it will give a warning message “… have excessive skew” for

the clock division. Ignore this warning message and generate the bit file. When this bit file is

downloaded to the FPGA, you should see the sequential circuit bit patterns on assigned LEDs.

Don’t forget to test the reset button of this circuit

Lab Tasks

Task 1: The complete code for D- Flip Flop (asynchronous) is given below- test it

|CPE343 | Computer Organization & Architecture Lab Manual 34

Lab Experiment | 4

D Btn Mclk Reset Q

Switch Push Button FPGA clock Push Button LED

PIN_AB28 PIN_M23 PIN_Y2 PIN_Y23 PIN_G19

Task 2: Write the code for D- Flip Flop (Synchronous) in the space given below.

|CPE343 | Computer Organization & Architecture Lab Manual 35

Lab Experiment | 4

Task 3: Sequence 1101 Detector:

One of the interesting aspects of using VHDL for implementing a state diagram on a FPGA is

that it does not require the knowledge of flip-flops and the complicated minimization procedures.

The state diagram can be directly implemented using if-then-else (or case-when) constructs,

based on a finite state machine (FSM). For this lab, a counter and a simple sequence detector are

implemented.

A sequence “1101” detector can be designed using the following state diagram.

Figure 4.6 Sequence Detector

In1 Btn Mclk LED

Switch Push Button FPGA clock LED

PIN_AB28 PIN_M23 PIN_Y2 PIN_G19

Important Note:

Notice that you are using a push button switch to generate a slow clock. It is normally zero and

becomes one when pushed. Since the button switch is a mechanical device, it creates oscillation

of signals, called key bouncing, when it is pushed and released. A bouncing waveform is showing

below. The oscillation period is typically less than 20ms.

|CPE343 | Computer Organization & Architecture Lab Manual 36

Lab Experiment | 4

The routine that filters the bouncing waveform is called a debouncing routine. If you do not

debounce the button signal, a single push of a button sometimes will cause to go through multiple

states, equivalent to multiple pushes. Implement the button debouncing by adding the debounce

routine provided in the link to your library and then calling it. An example of debouncing that

rotates LED lights per each push of a button is shown below’.

In the future, use this debouncing routine whenever a mechanical switch is used.

|CPE343 | Computer Organization & Architecture Lab Manual 37

Lab Experiment | 4

Write your VHDL Code for to detect 1101 sequence in Figure 4.6:

|CPE343 | Computer Organization & Architecture Lab Manual 38

Lab Experiment | 4

Lab Assessment

Pre-Lab /1

Performance /3

/10

Results /2

Viva /2

Lab Report /2

Instructor Signature and Comments

|CPE343 | Computer Organization & Architecture Lab Manual 39

S-ar putea să vă placă și

- VLSI Lab Manual V Sem July16Document65 paginiVLSI Lab Manual V Sem July16Aditya RanjanÎncă nu există evaluări

- Index Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ADocument39 paginiIndex Page: S.No. Date Name of The Experiment Marks Awarded Remarks/ Initial's Part - ANaveenÎncă nu există evaluări

- Introduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual LabDocument4 paginiIntroduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual Labdeepakk_alpineÎncă nu există evaluări

- Watchdog Timer Using VHDL For Atm System: Gore S.S., Lokhande A.A., Mahajan S.BDocument5 paginiWatchdog Timer Using VHDL For Atm System: Gore S.S., Lokhande A.A., Mahajan S.BRishikesh kumarÎncă nu există evaluări

- Programming FPGAsDocument38 paginiProgramming FPGAssayuri8910Încă nu există evaluări

- Single Precision Floating Point UnitDocument45 paginiSingle Precision Floating Point UnitSumeet SauravÎncă nu există evaluări

- Using Library ModulesDocument23 paginiUsing Library ModulesJuan Rafael Villen PulidoÎncă nu există evaluări

- Single Precision Floating Point UnitDocument46 paginiSingle Precision Floating Point UnitSumeet SauravÎncă nu există evaluări

- VLSI Design ReportDocument25 paginiVLSI Design ReportLucy HeartfilliaÎncă nu există evaluări

- A Industrial Training Project Report ON: VHDL Coding For Decade Counter On Xilinx and Create Test Waveform"Document40 paginiA Industrial Training Project Report ON: VHDL Coding For Decade Counter On Xilinx and Create Test Waveform"SHADAN khanÎncă nu există evaluări

- Lab 4 Verilog Gate Level ModellingDocument11 paginiLab 4 Verilog Gate Level Modellingsafdarmunir070Încă nu există evaluări

- Vlsi Manual 2013-2014Document36 paginiVlsi Manual 2013-2014hr_suresh_kÎncă nu există evaluări

- Asynchronous Microcontroller Simulation Model in VHDLDocument4 paginiAsynchronous Microcontroller Simulation Model in VHDLIacob CiprianÎncă nu există evaluări

- Design of Very Large Scale Integration CircuitsDocument15 paginiDesign of Very Large Scale Integration CircuitsStudentÎncă nu există evaluări

- CO Lab Manual-MinDocument40 paginiCO Lab Manual-MinMatheen TabidÎncă nu există evaluări

- Lab ManualDocument78 paginiLab Manualgurusandhya11Încă nu există evaluări

- FPGA Lab#1Document8 paginiFPGA Lab#1حساب ويندوزÎncă nu există evaluări

- Lab1 111 PDFDocument16 paginiLab1 111 PDFGoran MiljkovicÎncă nu există evaluări

- 4-8 MarchDocument15 pagini4-8 Marchadyadesai7Încă nu există evaluări

- DCS-2 Practical File Part-1Document26 paginiDCS-2 Practical File Part-1ykr007Încă nu există evaluări

- LabManual 18ECL58Document60 paginiLabManual 18ECL58back spaceÎncă nu există evaluări

- Introduction to VHDL Design and Circuit SimulationDocument46 paginiIntroduction to VHDL Design and Circuit SimulationDyrul SyaznanÎncă nu există evaluări

- DSD Lab ManualDocument49 paginiDSD Lab Manualshailygoyal50% (2)

- Lab9 - Counters, Timers, and Real-Time ClockDocument6 paginiLab9 - Counters, Timers, and Real-Time Clockwert1a2Încă nu există evaluări

- Universidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Document3 paginiUniversidad Del Magdalena Ingeniería Electrónica Diseño de Sistemas Digitales - Actividad Asincrónica 3Angélica SamperÎncă nu există evaluări

- ECE 124 Lab Manual Spring 2014Document29 paginiECE 124 Lab Manual Spring 2014darkmasterzorcÎncă nu există evaluări

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDocument8 paginiECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilÎncă nu există evaluări

- Ecad Lab Manual PvpsitDocument53 paginiEcad Lab Manual PvpsitpriyankaveeramosuÎncă nu există evaluări

- Lab 7 UART DesignDocument6 paginiLab 7 UART Designaditya220Încă nu există evaluări

- DSD Lab Manual Lab 5 6 20042022 022506pmDocument7 paginiDSD Lab Manual Lab 5 6 20042022 022506pmZubair ImranÎncă nu există evaluări

- Identifier: Identifier Are The Names Used To Give For An Object (Such As Signal NameDocument6 paginiIdentifier: Identifier Are The Names Used To Give For An Object (Such As Signal NameAurongo NasirÎncă nu există evaluări

- HDL Lab Manual: Anandanagar, Bangalore-24Document81 paginiHDL Lab Manual: Anandanagar, Bangalore-24Abinet ArbaÎncă nu există evaluări

- Cadence Nclaunch LabDocument86 paginiCadence Nclaunch Labsweety987Încă nu există evaluări

- Computer Organization and Architecture LabExperimentsDocument31 paginiComputer Organization and Architecture LabExperimentsfun time [funny videos]Încă nu există evaluări

- VHDLDocument15 paginiVHDLInd KanakÎncă nu există evaluări

- Fpga IITKDocument45 paginiFpga IITKPriyanshu SilÎncă nu există evaluări

- Using_Library_Modules_VHDLDocument22 paginiUsing_Library_Modules_VHDLcointoinÎncă nu există evaluări

- FPGA Logic Gates & Adder/Subtractor DesignDocument66 paginiFPGA Logic Gates & Adder/Subtractor DesignVishnu Brc57% (14)

- Verilog Basic ExperimentsDocument62 paginiVerilog Basic ExperimentsGaurav Soni0% (1)

- Srayee BanikDocument25 paginiSrayee BanikLucy HeartfilliaÎncă nu există evaluări

- VLSI & Embedded Systems Lab ManualDocument137 paginiVLSI & Embedded Systems Lab Manualganga avinash reddyÎncă nu există evaluări

- Design and implement CMOS digital/analog circuitsDocument86 paginiDesign and implement CMOS digital/analog circuitslakshmikala giddaluruÎncă nu există evaluări

- VLSI Lab Manual Student Copy 21-22 04.10.21Document76 paginiVLSI Lab Manual Student Copy 21-22 04.10.21RanjithÎncă nu există evaluări

- Decoder 2 To 4 With EnableDocument2 paginiDecoder 2 To 4 With EnableKurnia BJÎncă nu există evaluări

- Lect 06 VHDL INTRODocument31 paginiLect 06 VHDL INTROMasoud EsmailiÎncă nu există evaluări

- Lab Sequential CircuitsDocument6 paginiLab Sequential CircuitsMu'izz KaharÎncă nu există evaluări

- ELEC 204 Laboratory Manual Experiment 4Document5 paginiELEC 204 Laboratory Manual Experiment 4SSTGingÎncă nu există evaluări

- Design and Implementation of Traffic Controller Using VHDL: Interim Project ReportDocument21 paginiDesign and Implementation of Traffic Controller Using VHDL: Interim Project ReportAugusto Germano da SilvaÎncă nu există evaluări

- VHDL-Lab1 VivadoDocument14 paginiVHDL-Lab1 VivadoOscar Bruno FhÎncă nu există evaluări

- Ver I Log TutorialDocument18 paginiVer I Log Tutorialritam yadavÎncă nu există evaluări

- DSD Exp 10 - Anurag Bhattacharjee 22051925 CSE38Document6 paginiDSD Exp 10 - Anurag Bhattacharjee 22051925 CSE38routbismay99Încă nu există evaluări

- Electrical Engineering Department Academic SessionDocument17 paginiElectrical Engineering Department Academic SessionShavitra 30Încă nu există evaluări

- Altera Quip TutorialDocument30 paginiAltera Quip TutorialxiaoleicÎncă nu există evaluări

- Ec 452 DC & VHDL Lab Manual FinalDocument51 paginiEc 452 DC & VHDL Lab Manual Finalravic_cietÎncă nu există evaluări

- VLSI Rachana PDocument44 paginiVLSI Rachana PrathiÎncă nu există evaluări

- Experiment3 HAMZADocument14 paginiExperiment3 HAMZAhamzasamara80Încă nu există evaluări

- Ecad & Vlsi Lab Manual - MrecwDocument104 paginiEcad & Vlsi Lab Manual - Mrecwvaseem_ahmedÎncă nu există evaluări

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- Microprocessor System Design: A Practical IntroductionDe la EverandMicroprocessor System Design: A Practical IntroductionÎncă nu există evaluări

- Single and Multi-Chip Microcontroller Interfacing: For the Motorola 6812De la EverandSingle and Multi-Chip Microcontroller Interfacing: For the Motorola 6812Încă nu există evaluări

- Marmara University: EE3082 Midterm ExamDocument2 paginiMarmara University: EE3082 Midterm ExamAsad RehanÎncă nu există evaluări

- Assignment 1-SolutionDocument4 paginiAssignment 1-SolutionAsad RehanÎncă nu există evaluări

- Assignment 5Document1 paginăAssignment 5Asad RehanÎncă nu există evaluări

- Timer & CounterDocument22 paginiTimer & CounterDileep guptaÎncă nu există evaluări

- Lecture 20Document15 paginiLecture 20Asad RehanÎncă nu există evaluări

- 8255 Interfacing ExampleDocument9 pagini8255 Interfacing ExampleAsad RehanÎncă nu există evaluări

- 4x4 Keypad CodeDocument5 pagini4x4 Keypad CodeAsad RehanÎncă nu există evaluări

- TCP Flow Control and Congestion Control: EECS 489 Computer Networks Z. Morley Mao Monday Feb 5, 2007Document55 paginiTCP Flow Control and Congestion Control: EECS 489 Computer Networks Z. Morley Mao Monday Feb 5, 2007Asad RehanÎncă nu există evaluări

- 10.2.2.7 Packet Tracer - DNS and DHCPDocument4 pagini10.2.2.7 Packet Tracer - DNS and DHCPParthPatelÎncă nu există evaluări

- German GramDocument139 paginiGerman GramCustódio GungaÎncă nu există evaluări

- TestDocument2 paginiTestAsad RehanÎncă nu există evaluări

- Design of Gain Compensator: DR Mirza Tariq HamayunDocument19 paginiDesign of Gain Compensator: DR Mirza Tariq HamayunAsad RehanÎncă nu există evaluări

- Lab 5Document8 paginiLab 5Asad RehanÎncă nu există evaluări

- 9Document1 pagină9Asad RehanÎncă nu există evaluări

- Disk Allocation MethodsDocument10 paginiDisk Allocation MethodsAsad RehanÎncă nu există evaluări

- قائمة أساليب مواجهة الضغوطDocument3 paginiقائمة أساليب مواجهة الضغوطFakher KhaliliÎncă nu există evaluări

- Assignment 3 - ADocument1 paginăAssignment 3 - AAsad RehanÎncă nu există evaluări

- CUOnline Student PortalDocument1 paginăCUOnline Student PortalAsad RehanÎncă nu există evaluări

- Lab 5Document8 paginiLab 5Asad RehanÎncă nu există evaluări

- Lab 3-4Document15 paginiLab 3-4Asad RehanÎncă nu există evaluări

- SQL JoinsDocument23 paginiSQL JoinsCh Zaid RazaÎncă nu există evaluări

- Nyquist Sampling Theorem Sampling and ReconstructionDocument7 paginiNyquist Sampling Theorem Sampling and ReconstructionAsad RehanÎncă nu există evaluări

- Aliasing Task4Document6 paginiAliasing Task4Ola SkeikÎncă nu există evaluări

- CPE251 Probability Methods in Engineering Assignment AnalysisDocument3 paginiCPE251 Probability Methods in Engineering Assignment AnalysisAsad RehanÎncă nu există evaluări

- MultiplicationDocument5 paginiMultiplicationSiladittya MannaÎncă nu există evaluări

- Digital Design Using Verilog HDL QBDocument14 paginiDigital Design Using Verilog HDL QBHarishReddyÎncă nu există evaluări

- Digital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedDocument17 paginiDigital Electronics: Flip-Flops - D, T, J-K Types & Waveforms ExplainedRongeet SodhiÎncă nu există evaluări

- TimingDocument15 paginiTimingDeepak ChandaÎncă nu există evaluări

- SR Flip-Flop With Tristate OutputDocument12 paginiSR Flip-Flop With Tristate OutputmamimawÎncă nu există evaluări

- B.tech ECE - Syllabus 2015 Regulation As On 10.05.2016Document193 paginiB.tech ECE - Syllabus 2015 Regulation As On 10.05.2016JANARTHANAN67% (3)

- University Question Papers - VLSIDocument26 paginiUniversity Question Papers - VLSIVijayÎncă nu există evaluări

- UNIT-3: Digital ElectronicsDocument21 paginiUNIT-3: Digital ElectronicsMuthuvel MÎncă nu există evaluări

- Mechanic Medical Electronics.146180428Document37 paginiMechanic Medical Electronics.146180428swami061009Încă nu există evaluări

- Use A Transistor As A Heater PDFDocument5 paginiUse A Transistor As A Heater PDFFlorin Marica100% (1)

- Ring counters and Johnson counters explainedDocument15 paginiRing counters and Johnson counters explainednick_KGECÎncă nu există evaluări

- Counters and Registers 5Document79 paginiCounters and Registers 5Munish GargÎncă nu există evaluări

- DFT - CLK - Mux and DFT - CLK - Chain Data SheetDocument12 paginiDFT - CLK - Mux and DFT - CLK - Chain Data SheetRohit PatelÎncă nu există evaluări

- Flash Memory Programming SpecificationDocument22 paginiFlash Memory Programming SpecificationYonatan José Roche AndradeÎncă nu există evaluări

- Pin Diagram of 8086, MIN Mode - MAX ModeDocument10 paginiPin Diagram of 8086, MIN Mode - MAX Modenskprasad89Încă nu există evaluări

- 1985 Mitsubishi Bipolar Digital IC LSTTL IntegradosDocument498 pagini1985 Mitsubishi Bipolar Digital IC LSTTL Integradosramon navaÎncă nu există evaluări

- 1mrk505265-Ben - en Product Guide Busbar Protection Reb650 Iec PDFDocument61 pagini1mrk505265-Ben - en Product Guide Busbar Protection Reb650 Iec PDFaashish bissaÎncă nu există evaluări

- PDC Lab FullDocument57 paginiPDC Lab FullsubbuÎncă nu există evaluări

- Setup and Hold Time CalculationsDocument33 paginiSetup and Hold Time CalculationsRashmi Periwal100% (11)

- 555 Timer Guide: Features, Pinouts & ApplicationsDocument3 pagini555 Timer Guide: Features, Pinouts & ApplicationschandrakanthÎncă nu există evaluări

- APB Bridge Module Connects AXI and APBDocument25 paginiAPB Bridge Module Connects AXI and APBVikas ZurmureÎncă nu există evaluări

- PIC16F628A ExperimentosDocument11 paginiPIC16F628A ExperimentosCesar Matos100% (2)

- EEE 212 Week 1.Ppt - BilkentDocument53 paginiEEE 212 Week 1.Ppt - Bilkentetilletas98Încă nu există evaluări

- Philips P89C51RD2 6Document52 paginiPhilips P89C51RD2 6api-3726520Încă nu există evaluări

- El Timer 555 PDFDocument28 paginiEl Timer 555 PDFAnonymous 1LD5bpJ15dÎncă nu există evaluări

- BCA - Credit20 Sem II - LCDD PDFDocument8 paginiBCA - Credit20 Sem II - LCDD PDFshruti mankarÎncă nu există evaluări

- M-3311 DNP ProtocolDocument32 paginiM-3311 DNP ProtocolmaheshÎncă nu există evaluări

- Chapter01 - Sequential Logic-Advanced PDFDocument66 paginiChapter01 - Sequential Logic-Advanced PDFTrần Thảo NguyênÎncă nu există evaluări

- NLUJ Course CurriculumDocument68 paginiNLUJ Course CurriculumChetan MitraÎncă nu există evaluări

- Digitals Electronics Important MCQ With SolutionDocument20 paginiDigitals Electronics Important MCQ With SolutionPradeep Singh ThakurÎncă nu există evaluări

- CS302 Collection of Old PapersDocument48 paginiCS302 Collection of Old Paperscs619finalproject.comÎncă nu există evaluări