Documente Academic

Documente Profesional

Documente Cultură

Ijece Iccrest P103

Încărcat de

Hari PrasathTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Ijece Iccrest P103

Încărcat de

Hari PrasathDrepturi de autor:

Formate disponibile

SSRG International Journal of Electronics and Communication Engineering ( SSRG – IJECE ) – Special Issue ICCREST Mar 2019

High Performance Implementation of Image

Scaling Processor in FPGA Using Bilinear

Interpolation

S.Hariprasath1, M.Santhi2,

Department of Electronics and Communication Engineering

1,2

Saranathan College of Engineering,

Trichy, Tamil Nadu, India

Abstract

Image scaling is an imperative task in most of Pei-Yin Chen, Chi-Yuan Lien [3] have proposed a

the machine vision applications like pattern method for implementing edge oriented image scaling

recognition, pattern understanding. The Region of processor. In their implementation, the architecture

Interest (ROI) in the image must be resized before designed has seven stages. A processing rate of about

features are extracted. At different resolutions the 200 MHz is achieved by using TSMC 0.18-mum

region to be processed is described in order to technology.

evaluate the content present in the image under

interest.In this paper, memory efficient and delay Francisco Cardells-Tormo and JordiArnabat-

efficient image scaling algorithm is implemented..The Benedicto [4] have implemented a digital friendly

proposed method consists of four modules namely architecture of two dimensional separable

sharpeningfilter, clamp filter, edge detector and convolutional algorithm for image scaling purpose.

bilinear interpolator. The bilinear interpolation

algorithm is chosen as scale up or scale down In the architecture proposed by Lun Chen [5], low

algorithm due to its simplicity, high quality output cost implementation is taken as design constraint. H.

and less operational cycles consumption in hardware Kim, Y. Cha, and S. Kim [6] have designed curvature

compared other well-known methods like cubic based interpolation method zooming digital images.

interpolation, nearest neighbourhood interpolation. J.W.Han,J.H.Ki[7] have proposed a novel bilateral

Using Verilog HDL, the RTL description of the filter for image zooming.

algorithm is developed and the functional output is

verified using Modelsim10.4a.Using Xilinx 9.2i IDE, For hardware implementation polynomial based

the RTL implementation is verified. The target FPGA methods are generally preferred over Non- polynomial

chosen is Spartan3 XC3S400PG208 board. For the based methods due to less memory requirement and

input images of size 64*64, 8 bit gray scale image,the simple mathematical modeling. Some of the

operating frequency of the design is found to be equal polynomial based methods are nearest neighborhood

to 215.64Mhz. The area occupied for the proposed method, bilinear interpolation, bi-cubic interpolation.

algorithm is less compared exiting implementations. Among these algorithms [8, 9], the nearest

neighborhood method is the simplest and cost

Key words - image processing, scaling, FPGA, effective in terms of logic cells consumption in

Verilog,PSNR. hardware implementation. But the scaled output

images may consist of blocking and aliasing artifacts.

I. INTRODUCTION Shih-LunChen[10] have proposed a adaptive

Image scaling is a significant process for resizing scaling procedure to implement zooming of image

an image. Digital display devices such as liquid pixels.

crystal display(LCD) or plasma display panel(PDP), In Bilinear interpolation,the target pixel is

digital camera, surveillance camera, digital video obtained by performing linear interpolation inboth

recorders, digital photo frame, mobile phone, tablet horizontal and vertical directions. By interpolating the

PC become increasingly popular [1,2] nowadays. image in this manner causes the edges of scaled image

Hence the demand and significance of image scaling to become blurred and aliased. In order to smoothen

are very high. these effects, clamp filters and sharpening spatial

There are various scaling methods which can be filters as pre filters along with an edge detector to

generally classified as polynomial based methods and enhance the edges are used. For real time applications,

non-polynomial based methods [1]. low complex image processing algorithms are needed

for FPGA implementation. This algorithm demands

low computing resources and less memory storage per

Hence in this workbilinear interpolation algorithm is

pixel. The choice of clamp parameter C and

chosen for implementation.

ISSN: 2348 – 8549 www.internationaljournalssrg.org Page 14

SSRG International Journal of Electronics and Communication Engineering ( SSRG – IJECE ) – Special Issue ICCREST Mar 2019

sharpening value S are limited by the above blurring effects. The mask of the sharpening filter in

requirements. spatial domain is given in equation (2).

The rest of the paper is organized as follows. The -1 -1 -1

proposed system model is explained in Section II.

The parameters chosen for achieving low area K c -1 s -1 -----------(2)

implementation are explained in Section III and -1 -1 -1

simulation and synthesis results are explained in

Section IV. Finally the conclusion is presented in The basic model of bilinear interpolation is shown in

Section V. figure 2.

II. METHODOLOGY

The flow diagram of our proposed scaling algorithm

is shown in figure 1.

INPUT IMAGE

CLAMP FILTER

EDGE DETECTOR

SHARPENING Figure.2 Basic bilinear interpolation scheme

SPATIAL FILTER

P ( x ', j) = 1 X f P (i, j) + X f P i 1, j

P x ', j 1 = 1 X f P i, j 1 + X f P i 1, j 1

BILINEAR P ( x ’ , y’ ) = [P ( x ', j)] (1 Y f ) + P x ', j 1 x Y f -- (3 )

INTERPOLATOR

In equation (3), P i , j represents the source

pixel, P x , y

, ,

represents the scaled pixel, Xf and

OUTPUT IMAGE

Yf are the scaling factor along horizontal and vertical

Figure.1 Design Flow diagram direction respectively.As shown in equations (3) the

interpolation operation can be realized by means of

The structure consists of a sharpening spatial Multipliers and a block of adder/subtractor modules.In

filter, a clamp filter and bilinear interpolator. The this proposed work signed adder/subtractor and a

clamp filter is a generalized weighted smoothing filter pipelined MAC unit is used to implement the bi linear

which is used for smoothening uncontrollable interpolation algorithm.

condition known as an aliasing effect. This is followed

by a sharpening spatial filter (high pass filter) to III. IMPLEMENTATION DETAILS

reduce the blurring artifacts. The scaling filter and sharpening filter are

The clamp and sharpening spatial filters are used operating in the spatial domain. Hence the source

as pre-filters.The clamp is used for smoothening and pixel values are stored in a memory withhold time and

to reduce the aliasing artifacts. The clamp filter is setup time specifications. In this proposed scheme, a

implemented in hardware by specifying it as a mask. FIFO of size 64 by 8 is implemented as memory for

The typical mask of clamp filter is given in equation storing and sending values to data path unit.

(1). The filter coefficients are also stored in a 9 by 8

1 1 1 dual port memory designed using Verilog language. A

Mask of 3 by 3 is stored in the dual port memory and

Kc 1 c 1 …….. (1)

upon receiving the enable signal from timing unit, the

1 1 1 mask values are passed to data path unit A single

MAC unit is used here as processing element (PE). A

The sharpening spatial filter is used to enhance the

group of 9 such MAC units form data path unit in this

edges, remove background noise and to reduce the design.

ISSN: 2348 – 8549 www.internationaljournalssrg.org Page 15

SSRG International Journal of Electronics and Communication Engineering ( SSRG – IJECE ) – Special Issue ICCREST Mar 2019

The FPGA implementation is shown in figure 3.

Figure.3 FPGA Implementation diagram Figure 5. RTL view of bilinear interpolator

There are some parameters that affect The bilinear interpolator is implemented using

implemented processor performance. Two noticeable MAC unit. The signed multiplication is implemented

parameters that determine the performance of the for 8 bits since the input image considered is gray

algorithm are Clamp value (C) and Sharpening value scale image. A total of 5 Adder/Sub tractors are

(S) [2, 3, 4]. The blurring effect and clarity vary inferred and 6 Multipliers are inferred for one pixel

according to parameter changes. A tradeoff interpolation task. By pipelining of 2 stages and

relationship exists between (S), (C) and the data repeating the process for 64 clock cycles scaling of an

representation chosen for hardware implementation. input image of size 8 by 8 is achieved.

In this implementation an 8 bit representation is

chosen.

IV. SIMULATION AND SYNTHESIS

RESULTS

The proposed method is simulated using

Modelsim10.3b simulator by applying test fixture file

in Verilog HDL. The entire design of filters and

bilinear interpolator is designed using Verilog HDL..

It is found that the memory unit operates with a

maximum frequency of 415.536 MHz. The bilinear

interpolator operates with a maximum delay of

21.877ns. The RTL diagram of memory unit and

bilinear interpolator are shown in figure 4 and

Figure6.Detailed architecture of bilinear interpolator

5respectively. Figure 6 shows the detailed

architectural view of bilinear interpolator. The simulation result of bilinear interpolator is

given in figure 7. The operational speed achieved for

the overall design is 215.64 MHz. By reducing the

number of multiplications in the case of edge pixels

the speed of operation can be further increased by 30

to 40 percentage.

Figure 7.simulation result of bilinear interpolator

Figure 4. RTL diagram of Memory Unit

ISSN: 2348 – 8549 www.internationaljournalssrg.org Page 16

SSRG International Journal of Electronics and Communication Engineering ( SSRG – IJECE ) – Special Issue ICCREST Mar 2019

The following figure 8 shows the simulation result of Applications‖ , IEEE Transactions On Circuits And Systems

memory unit. For Video Technology, Vol. 23, No. 9, September 2013

Figure 8. Simulation result of memory unit

V. CONCLUSION

The present work hasbeen successfully simulated

and designed using Verilog HDL. The Structure was

designed using MAC unit and input values are stored

in FIFO memory on Spartan 3 board with xcs3004s-

pq208 FPGA with speed grade 5. The board is having

2 in-built block rams which could be used if additional

memory structure is required. By incorporating more

pipelined stages, the speed of operation can be

increased.

REFERENCES

[1] JoannisAndreadis, AngelosAmanatiadis, ―Digital Image

Scaling‖, IMTC 2005 - Inistrumentationi and Measurement

Technology Conference ,Ottawa, Canada 17-19 May 2005

[2] Xiangjun Zhang and Xiaolin Wu, ―Image Interpolation by

Adaptive 2-D Autoregressive Modeling and Soft-Decision

Estimation‖, IEEE Transactions On Image Processing, Vol.

17, No. 6, June 2008

[3] Pei-Yin Chen, Chi-Yuan Lien, and Chi-Pin Lu, ―VLSI

Implementation of an Edge-Oriented Image Scaling

Processor‖, IEEE Transactions On Very Large Scale

Integration (VLSI) Systems, Vol. 17, No. 9, September 2009

[4] Francisco Cardells-Tormo and JordiArnabat-Benedicto,

―Flexible Hardware-Friendly Digital Architecture for 2-D

Separable Convolution-Based Scaling‖, IEEE Transactions

On Circuits And Systems—II: Express Briefs, Vol. 53, No. 7,

July 2006

[5] Lun Chen, ―VLSI Implementation of a Low-Cost High-

Quality Image Scaling Processor‖, IEEE Transactions On

Circuits And Systems II Express Briefs, Vol. 60, No. 1,

January 2013

[6] H. Kim, Y. Cha, and S. Kim, ―Curvature interpolation

method for image zooming,‖ IEEE Trans. Image Process.,

vol. 20, no. 7, pp. 1895–1903, Jul. 2011.

[7] J.W.Han,J.H.Kim,S.H.Cheon,J.O.Kim,andS.J.Ko,―A novel

image interpolation method using the bilateral filter,‖ IEEE

Trans. Consum. Electron., vol. 56, no. 1, pp. 175–181, Feb.

2010.

[8] C. C. Lin, M. H. Sheu, H. K. Chiang, C. Liaw, and Z. C. Wu,

―The efficient VLSI design of BI-CUBIC convolution

interpolation for digital image processing,‖ in Proc. IEEE Int

Conf. Circuits Syst., May 2008, pp. 480–483.

[9] S. L. Chen, H. Y. Huang, and C. H. Luo, ―A low-cost high-

quality adaptive scalar for real-time multimedia

applications,‖ IEEE Trans. Circuits Syst. Video Technol.,

vol. 21, no. 11, pp. 1600–1611, Nov. 2011.

[10] Shih-Lun Chen, ―VLSI Implementation of an Adaptive Edge-

Enhanced Image Scalar for Real-Time Multimedia

ISSN: 2348 – 8549 www.internationaljournalssrg.org Page 17

S-ar putea să vă placă și

- Noc18 Ee33 Assignment8Document7 paginiNoc18 Ee33 Assignment8Hari PrasathÎncă nu există evaluări

- Noc18 Ee33 Assignment6Document5 paginiNoc18 Ee33 Assignment6Hari PrasathÎncă nu există evaluări

- AssDocument7 paginiAssHari PrasathÎncă nu există evaluări

- Noc18 Ee33 Assignment12Document5 paginiNoc18 Ee33 Assignment12Ayush mondalÎncă nu există evaluări

- Noc18 Ee33 Assignment2Document5 paginiNoc18 Ee33 Assignment2Hari Prasath100% (1)

- Noc18 Ee33 Assignment3Document5 paginiNoc18 Ee33 Assignment3Hari PrasathÎncă nu există evaluări

- New Doc 2019-03-25 08.38.13Document1 paginăNew Doc 2019-03-25 08.38.13Hari PrasathÎncă nu există evaluări

- Noc18 Ee33 Assignment5Document6 paginiNoc18 Ee33 Assignment5Hari PrasathÎncă nu există evaluări

- Noc18 Ee33 Assignment7Document6 paginiNoc18 Ee33 Assignment7Hari PrasathÎncă nu există evaluări

- Cu5096 Ia1Document1 paginăCu5096 Ia1Hari PrasathÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- MicrowaveDocument41 paginiMicrowaveMaryem MostafaÎncă nu există evaluări

- Data Mining ConceptsDocument175 paginiData Mining ConceptsNikolya SmirnoffÎncă nu există evaluări

- Completing The Square PDFDocument10 paginiCompleting The Square PDFgreg heffleyÎncă nu există evaluări

- Typeset EquationsDocument26 paginiTypeset EquationsEpic WinÎncă nu există evaluări

- More Practice Multiple ChoiceDocument3 paginiMore Practice Multiple ChoiceHiÎncă nu există evaluări

- Class VI (Second Term)Document29 paginiClass VI (Second Term)Yogesh BansalÎncă nu există evaluări

- WEEK 1, Grade 10Document2 paginiWEEK 1, Grade 10Sheela BatterywalaÎncă nu există evaluări

- Body Deassembly 9 Interior TrimDocument7 paginiBody Deassembly 9 Interior TrimCarlos TecnicÎncă nu există evaluări

- RomerDocument20 paginiRomerAkistaaÎncă nu există evaluări

- MODULAR QUIZ - 57 - Steel DesignDocument9 paginiMODULAR QUIZ - 57 - Steel DesignCornelio J. FernandezÎncă nu există evaluări

- Dual Inverter Gate: Features DescriptionDocument19 paginiDual Inverter Gate: Features DescriptionYaju JotosÎncă nu există evaluări

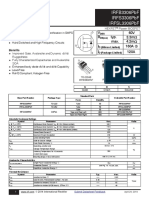

- Irfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADocument12 paginiIrfb3306Pbf Irfs3306Pbf Irfsl3306Pbf: V 60V R Typ. 3.3M: Max. 4.2M I 160A C I 120ADirson Volmir WilligÎncă nu există evaluări

- AlgebraDocument66 paginiAlgebraOliseyenum Precious ChukuemekeÎncă nu există evaluări

- CH 1 Optical Fiber Introduction - 2Document18 paginiCH 1 Optical Fiber Introduction - 2Krishna Prasad PheluÎncă nu există evaluări

- SpaceClaim - Developers Guide-5-6Document2 paginiSpaceClaim - Developers Guide-5-6Alexgh1993Încă nu există evaluări

- Georgi Lecture Notes On Weak Interactions Physics Harvard Web Draft 1998Document167 paginiGeorgi Lecture Notes On Weak Interactions Physics Harvard Web Draft 1998manosmagicas7340Încă nu există evaluări

- Module 1 Grade 8 (De Guzman)Document9 paginiModule 1 Grade 8 (De Guzman)Kim De GuzmanÎncă nu există evaluări

- Data Structures and Other Objects Using C++, Third Edition, by Michael Main and Walter SavitchDocument6 paginiData Structures and Other Objects Using C++, Third Edition, by Michael Main and Walter SavitchMd Rubaiyat BhuiyanÎncă nu există evaluări

- I C Engine LabDocument3 paginiI C Engine LabDevÎncă nu există evaluări

- From Assessment To Purchase - A Three-Stage ModelDocument15 paginiFrom Assessment To Purchase - A Three-Stage ModelRONAL EMERSON NOA ORTEGAÎncă nu există evaluări

- Balancing of Reciprocating MassesDocument74 paginiBalancing of Reciprocating MassesBharaniSai100% (1)

- Translating Trig Graphs PDFDocument4 paginiTranslating Trig Graphs PDFMark Abion ValladolidÎncă nu există evaluări

- Articles On SidisDocument146 paginiArticles On SidisMircea492003100% (1)

- Class - B Complementary Symmetry Power AmplifierDocument3 paginiClass - B Complementary Symmetry Power AmplifierAnonymous SH0A20Încă nu există evaluări

- Serie W11 PDFDocument2 paginiSerie W11 PDFOrlandoÎncă nu există evaluări

- Simple Harmonic Oscillator: 1 HamiltonianDocument10 paginiSimple Harmonic Oscillator: 1 HamiltonianAbdurrahman imamÎncă nu există evaluări

- Tech Specs - TC 5540 PDFDocument2 paginiTech Specs - TC 5540 PDFziaarkiplanÎncă nu există evaluări

- TE-419891-001 - 862-U-2301 - BIOCIDE DOSING PACKAGE - Rev.BDocument12 paginiTE-419891-001 - 862-U-2301 - BIOCIDE DOSING PACKAGE - Rev.Brizwan.zamanÎncă nu există evaluări

- K20 Engine Control Module X3 (Lt4) Document ID# 4739106Document3 paginiK20 Engine Control Module X3 (Lt4) Document ID# 4739106Data TécnicaÎncă nu există evaluări

- Projector Spec 8040Document1 paginăProjector Spec 8040Radient MushfikÎncă nu există evaluări