Documente Academic

Documente Profesional

Documente Cultură

Answers

Încărcat de

Melroy PintoDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Answers

Încărcat de

Melroy PintoDrepturi de autor:

Formate disponibile

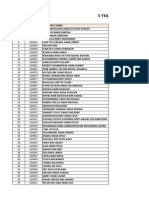

IR DROP

IR drop is the voltage drop across the metal straps that are used in power grids due to the resistance of

these metal straps or metal wires). Instead of actually carrying VDD to the standard cells, it will carry

Vdd – IR drop because of which there may be timing violations since delay is dependant on Vdd and if

there are fluctuations in Vdd, there will be setup and hold timing violations.

2 types:

Static IR Drop – also called as RC drop (due to the RC value of the metal straps used in the power grids)

Static IR drop may be due to long wire length, high fanout nets, high routing congestion

Dynamic IR Drop – also called as Voltage Droop (due to the switching activity of the standard cells)

Here, it actually creates bumps when multiple standard cell capacitances (wire cap) switch from H->L or

L->H asking for high current demand.

Should be checked during different RC corners and different PVT conditions (especially during OCV)

How to reduce IR Drop?

1. Adding more stripes

2. Spread the logic (if hotspots are at congested areas)

3. Using low power cells

4. Adding proper vias

5. Clock gating

6. Proper CTS structure (Minimizing clock buffers in clock tree as they switch very frequently)

CTS

Different types of Clock Trees ?

• H-Tree (easy to implement, low skew, consumes lot of power, lot of routing resource)

• Clock Grid or Mesh (very easy to build, area inefficient, consumes power)

• Reset Tree ( Normally used to reset the flops at release of reset )

Cost function of Simulated Annealing : Area + (lamda) * Wirelength

Electromigration

Electromigration (EM) refers to the unwanted movement of materials in a

semiconductor. If the current density is high enough, there can be a momentum

transfer from moving electrons to the metal ions that make up the lattice of the

interconnect material. The ions will drift in the direction of the electron flow. The

result is the gradual displacement of metal atoms in a semiconductor, potentially

causing open and short circuits.

How to reduce EM?

• Widen the wire to reduce current density

• Reduce the frequency

• Lower the supply voltage

• Keep the wire length short ( this will provide a less reservoir to store knock off ions)

• Reduce buffer size in clock lines

What is Latchup ?

Latch up is the generation of a low-impedance path in CMOS chips between the power supply

and the ground rails due to interaction of parasitic pnp and npn bipolar transistors. These BJTs

for a silicon-controlled rectifier with positive feedback and virtually short circuit the power and

the ground rail.

Antenna Rule Check?

Modern wafer processing happens through Plasma etch. Due to this there is

unintended high field stressing of the gate oxide due to the accumulation of charge

across the metal wires (antenna). The gate of the transistor acts like a capacitor and

there is excess potential build up as these charges flow down to the gate and can

potentially damage the gate in the long run.

For this reason there is an antenna ratio or antenna rule defined which is the ratio

of the area of the metal wire/conductor making up the antenna to the area of the

gate to which this antenna is electrically connected. If this ratio is large(>1000),

there is a high chance of the gate getting damaged.

If Area of metal/Area of gate > 1000, there is violation.

How can we counter Antenna issues ?

Bridging of adding jumpers (Like a metal 2 in between Metal 1 and Metal 3, so that

there is minimal charge accumulation going into the gate since its breaks a long

wire)

Diode insertion (Reverse biased diode)

What DRC issues you face?

- Tap cell issues ( how many to put in design )

- Via should be placed at 5mm and 2mm on either sides

S-ar putea să vă placă și

- Unix Commands Cheat Sheet PDFDocument1 paginăUnix Commands Cheat Sheet PDFRosemond FabienÎncă nu există evaluări

- Unix Commands Cheat Sheet PDFDocument1 paginăUnix Commands Cheat Sheet PDFRosemond FabienÎncă nu există evaluări

- Di Agnt M: Scanned by CamscannerDocument2 paginiDi Agnt M: Scanned by CamscannerMelroy PintoÎncă nu există evaluări

- Guest Lecturer Evaluation Form or Feedback FormDocument2 paginiGuest Lecturer Evaluation Form or Feedback FormMelroy Pinto100% (1)

- BEE - Notes For Mumbai University StudentsDocument61 paginiBEE - Notes For Mumbai University StudentsMelroy PintoÎncă nu există evaluări

- Preparation of Papers For IEEE T and J: (December 2013)Document9 paginiPreparation of Papers For IEEE T and J: (December 2013)Diego AragónÎncă nu există evaluări

- New Pro List 2011Document9 paginiNew Pro List 2011Melroy PintoÎncă nu există evaluări

- Japenese PharesDocument1 paginăJapenese PharesSharon Koh Su WenÎncă nu există evaluări

- IitDocument1 paginăIitMelroy PintoÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Zener DiodeDocument7 paginiZener DiodeMuhammad AsgharÎncă nu există evaluări

- Bai Tap Ve BJT1Document3 paginiBai Tap Ve BJT1nguyenphuonghuy1979Încă nu există evaluări

- Abrupt PN Junctions Analytical SolutionsDocument9 paginiAbrupt PN Junctions Analytical Solutionsombraga1896Încă nu există evaluări

- Strong Fet Irfr7440Pbf Irfu7440Pbf: V 40V R Typ. 1.9Mω Max. 2.4M I 180A I 90ADocument12 paginiStrong Fet Irfr7440Pbf Irfu7440Pbf: V 40V R Typ. 1.9Mω Max. 2.4M I 180A I 90AVíctor LaraÎncă nu există evaluări

- Lecture10 MOS Field Effect Transistors v1Document33 paginiLecture10 MOS Field Effect Transistors v1Dr-Suraj Kumar SawÎncă nu există evaluări

- MOS Transistor Principles and Digital Integrated CircuitsDocument371 paginiMOS Transistor Principles and Digital Integrated CircuitsyeswanthÎncă nu există evaluări

- Phototransistor Optocouplers: Description CNY17-1 CNY17-3 CNY17-2 CNY17-4 FeaturesDocument11 paginiPhototransistor Optocouplers: Description CNY17-1 CNY17-3 CNY17-2 CNY17-4 Featuresluis_mariano8998Încă nu există evaluări

- Vlsi Design ECE5014Document5 paginiVlsi Design ECE5014SriramÎncă nu există evaluări

- 2N3906 PDFDocument6 pagini2N3906 PDFAdilsonAmorimÎncă nu există evaluări

- LM 2023 Gala Night Award RecipientsDocument36 paginiLM 2023 Gala Night Award RecipientsSmigel BuletÎncă nu există evaluări

- NAND Gate Diodes TransistorsDocument8 paginiNAND Gate Diodes TransistorsAnoud AlkabodiÎncă nu există evaluări

- DatasheetDocument1 paginăDatasheetStuxnetÎncă nu există evaluări

- RF Power TransistorDocument6 paginiRF Power TransistorLanteanÎncă nu există evaluări

- Diode:: Unbiased Diode and Depletion LayerDocument10 paginiDiode:: Unbiased Diode and Depletion LayerAnonymous ovAm3yJXÎncă nu există evaluări

- SEMICONDUCTOR KTA1241 TECHNICAL DATA EPITAXIAL PLANAR PNPDocument2 paginiSEMICONDUCTOR KTA1241 TECHNICAL DATA EPITAXIAL PLANAR PNPDeilyn RivasÎncă nu există evaluări

- Field Effect Transistors Analysis Mr. Zeeshan Ali, Asst. Professor Department: B.E. Electronic & Telecommunication Subject: Analog Electronics - I Semester: IIIDocument84 paginiField Effect Transistors Analysis Mr. Zeeshan Ali, Asst. Professor Department: B.E. Electronic & Telecommunication Subject: Analog Electronics - I Semester: IIIAqilAbbasiÎncă nu există evaluări

- Opt Comm C6Document46 paginiOpt Comm C6Arunmetha SundaramoorthyÎncă nu există evaluări

- Solar Cell Efficiency Tables (Version 58)Document11 paginiSolar Cell Efficiency Tables (Version 58)劉鋒Încă nu există evaluări

- High Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MDocument6 paginiHigh Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MMohamed belhasanÎncă nu există evaluări

- ECE 522 Integrated Circuit Fabrication Practice ProblemsDocument2 paginiECE 522 Integrated Circuit Fabrication Practice ProblemsDeeksha MishraÎncă nu există evaluări

- VLSI BJT process steps for transistor fabricationDocument19 paginiVLSI BJT process steps for transistor fabricationJ.V.'S CLASSÎncă nu există evaluări

- Kms U2 p2 q2 Cape May June 2022 FinalDocument5 paginiKms U2 p2 q2 Cape May June 2022 FinalPhilip Moore100% (1)

- Metal Oxide SemiconductorDocument50 paginiMetal Oxide Semiconductorkamal hameed tayyÎncă nu există evaluări

- Electronic devices: Define hybrid parameters (40Document4 paginiElectronic devices: Define hybrid parameters (40Mahendra BabuÎncă nu există evaluări

- Transistores: N0 Ref DescripDocument11 paginiTransistores: N0 Ref DescripPedro AlvarezÎncă nu există evaluări

- Get PDF3Document11 paginiGet PDF3api-19755952Încă nu există evaluări

- SURE Trust - Integrated Diploma in VLSI - Course Content-1 - DFT - ChangesDocument3 paginiSURE Trust - Integrated Diploma in VLSI - Course Content-1 - DFT - ChangesBT21EC026 Siddharth JhaÎncă nu există evaluări

- BE3252 QB Unit4Document2 paginiBE3252 QB Unit4rkanthimathi86Încă nu există evaluări

- Datasheet PDFDocument2 paginiDatasheet PDFalejanÎncă nu există evaluări