Documente Academic

Documente Profesional

Documente Cultură

Tema2 Circuitos Digitales

Încărcat de

Fernando Sobrino-Manzanares MasDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tema2 Circuitos Digitales

Încărcat de

Fernando Sobrino-Manzanares MasDrepturi de autor:

Formate disponibile

Unidad 2.

Circuitos digitales

DAPA

E.T.S.I. Informática

Universidad de Sevilla

Oct. 2015

Jorge Juan <jjchico@dte.us.es> 2010-2016

Esta obra esta sujeta a la Licencia Reconocimiento-CompartirIgual 4.0 Internacional de Creative Commons. Para

ver una copia de esta licencia, visite http://creativecommons.org/licenses/by-sa/4.0/ o envíe una carta Creative

Commons, PO Box 1866, Mountain View, CA 94042, USA.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

●

Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Discrete devices

http://en.wikipedia.org/wiki/File:Splatine.jpg

Departamento de Tecnología Electrónica – Universidad de Sevilla

Circuitos integrados

http://en.wikipedia.org/wiki/Integrated_circuit

Departamento de Tecnología Electrónica – Universidad de Sevilla

Circuitos integrados. Evolución

●

Ley de Moore (1964): “La densidad de integración se duplica

cada 18 meses”.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Evolución

Departamento de Tecnología Electrónica – Universidad de Sevilla

Circuitos digitales: 0s y 1s

X

Analógico

t

X

2

Digital 1

0

(5 valores)

-1 t

-2

Sequence: 0, 1, -2, -2, 1, 2, 2, -1, 1

X

Digital 1

(2 valores) 0

t

Sequence: 0, 1, 0, 0, 1, 0, 1, 1, 0

Departamento de Tecnología Electrónica – Universidad de Sevilla

Circuito digital

+ +

Digital Vout

Vin

electronic circuit

- -

Valor eléctrico (VX) vs valor lógico (X)

VX X

0V 0

3,3V 1

Departamento de Tecnología Electrónica – Universidad de Sevilla

Puertas lógicas. Inversor CMOS

●

Las puertas lógicas realizan operaciones simples sobre señales

digitales.

● La operación digital más simple (salvo la identidad) es la

inversión, implementada por el “inversor”. V CC

Vin = 0V Vout = VCC

in out

VCC

VCC

in out

Vin Vout

0 1

1 0

Vin = VCC Vout = 0

Departamento de Tecnología Electrónica – Universidad de Sevilla

Puertas lógicas. NAND CMOS

x

z

y Las puertas CMOS son

“naturalmente” inversoras (INV,

NAND, NOR, …)

VCC

Vz

0 0 1 1 Vx

0 1 0 1 Vy

0

Departamento de Tecnología Electrónica – Universidad de Sevilla

Puertas lógicas. NOR CMOS

x

z

y

VCC

Vx

Vy Vz

Departamento de Tecnología Electrónica – Universidad de Sevilla

Operadores lógicos básicos

x z

NOT 0 1 z=x x z

1 0

xy z

00 0

x

AND 01 0 z=x·y z

10 0 y

11 1

xy z

00 0

x

OR 01 1 z=x+y z

10 1 y

11 1

Departamento de Tecnología Electrónica – Universidad de Sevilla

Otros operadores lógicos

xy z

00 1

x

NAND 01 1 z=x·y z

10 1 y

11 0

xy z

00 1

x

NOR 01 0 z=x+y z

10 0 y

11 0

xy z

00 0

x

XOR

OR 01 1 z = x ⊕ y = xy + xy z

10 1 y

11 0

xy z

00 1

x

XNOR 01 0 z = x ⊕ y = x y + xy z

10 0 y

11 1

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contacto con el diseño digital

●

Dieseñar un circuito de alarma con un detector de presencia y

un sensor de fuego

● Entradas:

– a: alarma conectada (1) o alarma desconectada (0)

– b: sensor de presencia (1) o no presencial (0)

– c: sensor de fuego (1) o no fuego (0)

● Salida:

– z: alarma activada (1) o no activada (0)

●

Ejercicio:

– Diseñar un circuito electrónico digital que genere la salida correcta

en función del valor de las entradas mediante la interconexión de

puertas lógicas.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

● Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Funciones lógicas. Ejemplo

Descripción verbal Un sistema de alarma digital tiene puede estar activado

o desactivado y dispone de un sensor de presencia y otro

de apertura de puerta. Cuando el sistema está

desactivado, se activará una señal de alarma si se

detecta presencia y la puerta está abierta (se ha

olvidado cerrar la puerta). Cuando el sistema está

activado, se activará la señal de alarma si se detecta

presencia o se abre la puerta.

Descripción formal abc z – Tabla de verdad:

000 0 especificación formal. Valor de

a: 0-desactivado, 1-activado 001 0 la función para cada valor de

b: 0-no presecia, 1-presencia. las variables (n variables: 2 n

c: 0-p. cerrada, 1-p. abierta

010 0 valores).

011 1 – Los circuitos digitales

a 100 0 combinacionales implementan

Función 101 1 funciones lógicas

b z

lógica

c 110 1

111 1

Departamento de Tecnología Electrónica – Universidad de Sevilla

Expresiones lógicas

●

Combinación de operadores AND (·), OR (+) y NOT ( ')

●

Precedencia de · sobre +

– x+(y·z) = x+y·z

● "·" puede ser omitido

– x+y·z = x+yz

● Son una forma de representación de funciones lógicas

f(a,b,c) = (a+b+c) (a + b c) + cd (a+c)

Departamento de Tecnología Electrónica – Universidad de Sevilla

Funciones lógicas. Resumen

●

Es posible construir circuitos elementales que realizan los

operadores lógicos básicos (puertas lógicas)

● El objetivo del diseño combinacional es describir las funciones

lógicas mediante operadores básicos que permitan construir un

circuito digital que realice la función deseada

abc z

000 0

Circuito combinacional

001 0

a

Función 010 0 a

b

b z

lógica 011 1

c

c 100 0 d

101 1

110 1

111 1

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

● Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Formalización: Álgebra de Boole

●

B={0, 1}

●

{B, NOT, AND, OR} forman un Álgebra de Boole

– Caso particular: Álgebra de Conmutación

● Un Álgebra de Boole cumple los siguiente axiomas

George Boole (1815-1864)

Identidad x+0 = x x·1=x

Conmutativa x+y = y+x x·y = y·x

Distributiva x·(y+z) = (x·y)+(x·z) x+(y·z) = (x+y)·(x+z)

Complemento x+x = 1 x·x = 0

Dualidad: si una expresión se cumple, la expresión que

resulta de intercambiar + con · y 0 con 1 también se cumple

Departamento de Tecnología Electrónica – Universidad de Sevilla

Álgebra de Boole. Teoremas

Idempotencia x+x = x x·x = x

Unicidad del complemento x es único

Elementos dominantes x+1 = 1 x·0 = 0

Involución (x) = x

Absorción x+xy = x x·(x+y) = x

Consenso x+xy = x+y x·(x+y) = x·y

Asociativa x+(y+z) = (x+y)+z x·(y·z) = (x·y)·z

De Morgan x·y = x+y x+y = x·y

Reducción xy+xy = x (x+y)(x+y) = x

Departamento de Tecnología Electrónica – Universidad de Sevilla

Conversión. SOP/POS a tabla de

verdad

z(a,b,c) = a + a b c + ac + bc

● z = 1 si y sólo si

– a=1, o bien

– a=1 y b=0 y c=1, o bien

– a=1 y c=1, o bien

– b=0 y c=1

z(a,b,c) = (a+b+c)(a+b)(a+c)

● z = 0 si y sólo si

– a=0 y b=0 y c=0, o bien

– a=0 y b=1, o bien

– a=0 y c=0

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

● Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Diseño de circuitos combinacionales

●

Basado en la síntesis de circuitos a partir de formas

normalizadas (SOP o POS)

● Una expresión más simple dará un circuito más simple

● Las formas normalizadas pueden ser simplificadas de forma

sistemática (automatizable)

● Criterios de simplificación básicos

– Expresiones equivalentes: mismos valores para las mismas

entradas.

– Mínimo número de términos → mínimo número de puertas

– Mínimo número de literales en cada término → mínimo número de

entradas en cada puerta

●

Otros criterios

– Tipos de puertas disponibles

– Facilidad para hacer complementos (inversores)

– Consumo de potencia, velocidad de operación, etc.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Simplificación de formas

normalizadas

xy + xy = x

"x" puede ser cualquier expresión

z = abc + abc + abc + abc términos orden 0

z = bc + ac + ab términos orden 1

Cada término puede ser usado más de una vez

(x+x=x)

Implicante de una función

- Término producto que puede ser parte de una expresión

en forma de SOP de la función.

- Contiene o “cubre” varios mintérminos de la función.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Algoritmo de minimización

Quine-McCluskey (simp.)

1. Comenzar con la lista de los mintérminos de la función

2. Buscar implicantes de primer orden (TO-1)

Aplicando el teorema de reducción a mintérminos adyacentes

3. Eliminar mintérminos cubiertos de la expresión final

No hay que preocuparse de los mintérminos cubiertos porque están

incluídos en los TO-1

4. Buscar implicantes de segundo orden (TO-2)

Aplicando el teorema de reducción a los TO-1 adyacentes

5. Eliminar los TO-1 cubiertos de la expresión final

6. Continuar hasta obtener implicantes del mayor orden posible (implicantes

primos)

Las implicantes primos son los términos más simples que contienen todos

los mintérminos de la función.

Las implicantes primos esenciales son los que contienen mintérminos no

contenidos en ningún otro implicante primo.

7. Selecciona todas las implicantes primos esenciales y/o un número mínimo de

ellos que cubra todos los mintérminos de la función.

Departamento de Tecnología Electrónica – Universidad de Sevilla

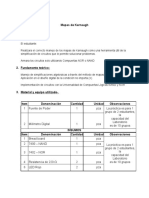

Mapas de Karnaugh (K-mapa)

●

K-mapas: ab

cd 00 01 11 10

– Tabla bidimensional 0 4 12 8

00

– Valores de variables 1 5 13 9

ordenados como en código 01

gray 11

3 7 15 11

– Cada celda corresponde a un 2 6 14 10

10

mintérmino/maxtérmino

– Localización fácil de F(a,b,c,d)

mintérminos y términos de

orden superior F(a,b,c,d) = Σ(0,1,4,9,11,13,15)

– ¡Son cíclicos! ab

– Localización fácil de cd 00 01 11 10

implicantes primos 00 1

0

1

4

0

12

0

8

– Facilitan la simplificación de 1 5 13 9

01 1 0 1 1

expresiones normalizadas 3 7 15 11

mediente el método de 11 0 0 1 1

Quine-McCluskey

2 6 14 10

10 0 0 0 0

F(a,b,c,d)

Departamento de Tecnología Electrónica – Universidad de Sevilla

K-mapas de 1 a 6 variables

a a ab ab

0 1 b 0 1 c 00 01 11 10 cd 00 01 11 10

0 1 0 2 0 2 6 4 0 4 12 8

0 0 00

1 3 1 3 7 5 1 5 13 9

F(a) 1 1 01

3 7 15 11

F(a,b) F(a,b,c) 11

2 6 14 10

10

abc

def 000 001 011 010 110 111 101 100 F(a,b,c,d)

0 8 24 16 48 56 40 32

000

1 9 25 17 49 57 41 33

abc

001 de 000 001 011 010 110 111 101 100

3 11 27 19 51 59 43 35 0 4 12 8 24 28 20 16

011 00

2 10 26 18 50 58 42 34 1 5 13 9 25 28 21 17

010 01

6 14 30 22 54 62 46 38 3 7 15 11 27 31 23 19

110 11

7 15 31 23 55 63 47 39 2 6 14 10 26 30 22 18

111 10

5 13 29 21 53 61 45 37

101 F(a,b,c,d,e)

4 12 28 20 52 60 44 36

100

F(a,b,c,d,e,f)

Departamento de Tecnología Electrónica – Universidad de Sevilla

Diseño “manual” de CC (resumen)

Descripción funcional

(descripción verbal) SOP/POS mínimo

Formalización

● Identificación ent./sal. Selección de puertas

● Inespecificaciones, etc. ● ¿AND-OR o NAND-NAND?

● ¿OR-AND o NOR-NOR?

● ¿Raíl simple o doble?

Tabla de verdad/K-mapa

Circuito

Minimización

● “Sólo NAND” → SOP a

● “Sólo NOR” → POS

b

● “Óptimo” → intentar

SOP&POS c

d

Departamento de Tecnología Electrónica – Universidad de Sevilla

Diseño de circuitos combinacionales

Ejemplo 1

Diseñe un circuito combinacional con cuatro entradas (x3, x2, x1, x0) que

representan los bits de una cifra BCD X, y dos salidas (c1, c0) que representan los

bits de una magnitud C, donde C es el cociente de la división X/3.

Por ejemplo, si X=7 → C=2, esto es, si (x3,x2,x1,x0)=(0,1,1,1) → (c1,c0)=(1,0)

Diseñe un circuito mínimo en dos niveles de puertas, salvo inversores, con entradas

en raíl simple.

Ejemplo 2

Diseñe un circuito combinacional para el ejemplo de la introducción.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

● Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Análisis funcional

●

¿Qué es?

– Obtener la función lógica realizada por un circuito combinacional.

●

Aplicaciones:

– Interpretar la operación y/o utilidad del circuito.

– Rediseñar un circuito equivalente con distintos componentes.

● Método:

– Identificar entradas y salidas.

– Para cada puerta con entradas conocidas, calcular la expresión

lógica de salida de la puerta.

– Repetir hasta que se conocen las expresiones de todas las salidas

del circuito.

– Convertir a una representación más útil: tabla de verdad, K-mapa,

expresión mínima, etc.

– Dar una descripción verbal de la operación del circuito.

Departamento de Tecnología Electrónica – Universidad de Sevilla

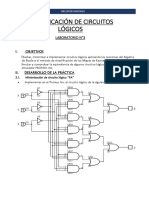

Análisis funcional. Ejemplo

El circuito de la figura corresponde a un sistema de alarma con cuatro entradas y

una salida. Las entras corresponden a:

a: activación del sistema (0 - desactivado, 1 - activado)

b: sensor de fuego (0 - no hay fuego, 1 - sí hay fuego)

c: sensor de puerta de entrada (0 - puerta cerrada, 1 - puerta abierta)

d: sensor de presencia (0 - no hay presencia, 1 - sí hay presencia)

Cuando la salida z se activa (z=1) hace sonar la sirena de la alarma.

a)Analice el circuito y describa su operación con palabras: casos en los que se

activará la alarma, etc.

b)Rediseñe el circuito empleando únicamente puertas NOR.

b

z

c

Departamento de Tecnología Electrónica – Universidad de Sevilla

Contenido

●

Circuitos digitales

●

Funciones lógicas

● Álgebra de Boole

● Diseño combinacional

●

Análisis funcional

●

Análisis temporal

Departamento de Tecnología Electrónica – Universidad de Sevilla

Análisis temporal

●

¿Qué es?

– Estudiar la evolución con el tiempo de las señales internas de un

circuito y de sus salidas para señales de entrada dadas.

– Forma de onda: representación temporal del valor de una señal.

● Aplicaciones

– Calcular o estimar el retraso de propagación de un circuito: tiempo

que tarda en proporcionar un valor de salida correcto.

– Analizar posibles fallos o comportamientos no esperados debido a

características temporales: retraso excesivo, azares, etc.

●

Método “manual”

– Para cada puerta lógica, obtener la ecuación de salida en función

de las entradas de la puerta.

– Sustituir los valores de las señales de entrada que son constantes

(NO SUSTITUIR NADA MÁS)

– Dibujar las formas de onda desde las entradas primarias hasta las

salidas en función de la operación de cada puerta. Aplicar posibles

retrasos de cada puerta. Modelo simple: mismo retraso para todas

las puertas.

Departamento de Tecnología Electrónica – Universidad de Sevilla

Análisis temporal. Ejemplo

I1

x

A1

I2 y=1

z

f(x,y,z) x

y A2 z

∆ ∆

I1 ∆

I1 = x y=1 I1 = x I2

I2 = z I2 = z

A1

A1 = I1 I2 A1 = I1 I2

A2 = x y z A2 = x z A2

f = A1 + A2 f = A1 + A2

f

0 10 20 30 40 50 60 70 80 90 100 t(ns)

Departamento de Tecnología Electrónica – Universidad de Sevilla

S-ar putea să vă placă și

- 100 circuitos de shields para arduino (español)De la Everand100 circuitos de shields para arduino (español)Evaluare: 3.5 din 5 stele3.5/5 (3)

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosDe la EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosEvaluare: 4.5 din 5 stele4.5/5 (14)

- Sistemas Digitales: Circuitos Lógicos CombinacionalesDocument15 paginiSistemas Digitales: Circuitos Lógicos CombinacionalesRicardo SusaÎncă nu există evaluări

- Laboratotio 3Document12 paginiLaboratotio 3OTTO CORDOVA AMASIFUENÎncă nu există evaluări

- Tema 2 Combinacionales MemoriasDocument21 paginiTema 2 Combinacionales MemoriasiriagzÎncă nu există evaluări

- Informe Previo 2Document8 paginiInforme Previo 2joaquinÎncă nu există evaluări

- Tema 01Document19 paginiTema 01Anonymous lrrwBxUYÎncă nu există evaluări

- Informe de Laboratorio 3 Diseño de Circuitos Logicos CombinacionalsDocument5 paginiInforme de Laboratorio 3 Diseño de Circuitos Logicos CombinacionalsAntonio PuentesÎncă nu există evaluări

- CED Tema 8 2011 2012Document45 paginiCED Tema 8 2011 2012mpantunezÎncă nu există evaluări

- Juan Tejada PresaberDocument13 paginiJuan Tejada Presaberjustjuank2010Încă nu există evaluări

- FinalDocument4 paginiFinalAstrid BelloÎncă nu există evaluări

- Estabilidad de Sistemas LinealesDocument12 paginiEstabilidad de Sistemas LinealesTrabajos AcademicosÎncă nu există evaluări

- Practica Calificada Unidad IDocument6 paginiPractica Calificada Unidad ISergio AguilarÎncă nu există evaluări

- CED Tema 4-CIRCUITOS COMBINACIONALESDocument51 paginiCED Tema 4-CIRCUITOS COMBINACIONALESJose OsoresÎncă nu există evaluări

- 2a GUIA DE LABORATORIO ELECTRONICA DEL COMPUTADOR V4Document6 pagini2a GUIA DE LABORATORIO ELECTRONICA DEL COMPUTADOR V4DANIEL ALEJANDRO AVILA JARABAÎncă nu există evaluări

- COMPENDIOSDocument70 paginiCOMPENDIOSADRIANA MICHELLE CAMPOVERDE BALCAZARÎncă nu există evaluări

- Informe 03Document14 paginiInforme 03diegoÎncă nu există evaluări

- LAB # 6 Diseño de Contador Sincro ASCEN y DESCEN Con JKDocument5 paginiLAB # 6 Diseño de Contador Sincro ASCEN y DESCEN Con JKDadÎncă nu există evaluări

- Informe in Electronicos 2Document12 paginiInforme in Electronicos 2David Llerena PonceÎncă nu există evaluări

- Tema 9 Familias Logicas 2020Document92 paginiTema 9 Familias Logicas 2020Eduardo VelezÎncă nu există evaluări

- Practica1 Diseño Digital ModernoDocument10 paginiPractica1 Diseño Digital ModernoJuanVazquezÎncă nu există evaluări

- Practica 3 InformeDocument5 paginiPractica 3 InformeDiego ValdiviezoÎncă nu există evaluări

- 4.practica Cuatro Analisis CircuitosDocument8 pagini4.practica Cuatro Analisis CircuitosJuliana Velásquez EstradaÎncă nu există evaluări

- 4a Clase - #1 - 12-20 - 2020-2Document10 pagini4a Clase - #1 - 12-20 - 2020-2JamesÎncă nu există evaluări

- Familias LógicasDocument14 paginiFamilias LógicasJosé VolcánÎncă nu există evaluări

- Juan Tejada PresaberDocument12 paginiJuan Tejada Presaberjustjuank2010Încă nu există evaluări

- Fisica 1Document21 paginiFisica 1Luis Yucra RamoÎncă nu există evaluări

- Laboratorio TinkercadDocument3 paginiLaboratorio TinkercadJEISSON FERNANDO CAICEDO BURBANOÎncă nu există evaluări

- Trabajo Practico N°3Document8 paginiTrabajo Practico N°3Brayan VQÎncă nu există evaluări

- Flujo Newtoniano Entre Dos Placas PlanasDocument6 paginiFlujo Newtoniano Entre Dos Placas PlanasJuan Manuel OliverosÎncă nu există evaluări

- 06 - Diseño de Circuitos CombinacionalesDocument37 pagini06 - Diseño de Circuitos Combinacionalesgabriel vasquezÎncă nu există evaluări

- Circuitos Digitales PDFDocument10 paginiCircuitos Digitales PDFdanilo100% (1)

- Ced Tema 1-IntroduccionDocument11 paginiCed Tema 1-IntroduccionBella MorenoÎncă nu există evaluări

- Practica 4 Compuertas y Circuitos LogicosDocument3 paginiPractica 4 Compuertas y Circuitos LogicosAlex ReyesÎncă nu există evaluări

- Informe Previo N 01Document8 paginiInforme Previo N 01VR Cinthia0% (1)

- Lab1 Fca2020 IIDocument4 paginiLab1 Fca2020 IIjulio sanchez100% (1)

- Introduccion A Los Sistemas Digitales 2 PDFDocument8 paginiIntroduccion A Los Sistemas Digitales 2 PDFMigue RodrígueÎncă nu există evaluări

- Introduccion A Los Sistemas Digitales 2 PDFDocument8 paginiIntroduccion A Los Sistemas Digitales 2 PDFLIZETH MALLERLY VILLABONÎncă nu există evaluări

- Introducción A Los Sistemas Digitales PDFDocument8 paginiIntroducción A Los Sistemas Digitales PDFANDRESÎncă nu există evaluări

- Examen Practico U1 FinalDocument14 paginiExamen Practico U1 FinalRamón McCartneyÎncă nu există evaluări

- Semana 3 FUNCIONES LOGICAS CON PROGRAMAS 2023IDocument33 paginiSemana 3 FUNCIONES LOGICAS CON PROGRAMAS 2023INury GuevaraÎncă nu există evaluări

- Informe Previo 2Document18 paginiInforme Previo 2tania tarazonaÎncă nu există evaluări

- A6. Evaluación Práctica - Revisión Del IntentoDocument3 paginiA6. Evaluación Práctica - Revisión Del IntentoSussell Ruiz RamirezÎncă nu există evaluări

- Práctica No. 1 (Compuertas Lógicas)Document7 paginiPráctica No. 1 (Compuertas Lógicas)Fernanda PérezÎncă nu există evaluări

- Electrónica DigitalDocument14 paginiElectrónica DigitalDüväń MõńtāñōÎncă nu există evaluări

- Tema 1 Redes MicroondasDocument21 paginiTema 1 Redes MicroondasMaría Jesús García GarcíaÎncă nu există evaluări

- CED Tema 8 2011 2012 2024-01-26 01 - 22 - 11Document45 paginiCED Tema 8 2011 2012 2024-01-26 01 - 22 - 11Bella MorenoÎncă nu există evaluări

- Laboratorio 1 Interfaces DigitalesDocument10 paginiLaboratorio 1 Interfaces DigitalesMitchell Aliaga RiveraÎncă nu există evaluări

- Practica No.2 Saavedra ChristianDocument7 paginiPractica No.2 Saavedra ChristianCHRISTIAN PAUL SAAVEDRA MATUTEÎncă nu există evaluări

- Maquina SecuencialDocument9 paginiMaquina SecuencialPato BautistaÎncă nu există evaluări

- Ene 2023 Daniel Flores y Jorge GodoyDocument11 paginiEne 2023 Daniel Flores y Jorge GodoyPablo BarreraÎncă nu există evaluări

- Modelado Convertidores CCDocument56 paginiModelado Convertidores CCPablo García SuárezÎncă nu există evaluări

- Conf 1 Sistemas y SX en El TiempoDocument78 paginiConf 1 Sistemas y SX en El TiempoAlejandro Rivas GamalloÎncă nu există evaluări

- Compuertas LogicasDocument9 paginiCompuertas Logicasdeyvis1818Încă nu există evaluări

- IntroduccionED PDFDocument27 paginiIntroduccionED PDFFrancisco SosaÎncă nu există evaluări

- Clases Ceiv Temporizador 2021ii 7 Dic 2021Document32 paginiClases Ceiv Temporizador 2021ii 7 Dic 2021eduardo jesusÎncă nu există evaluări

- Examen FinalDocument2 paginiExamen FinalKevin Tintaya VargasÎncă nu există evaluări

- Una introducción a la criptografía de clave pública 2ª. EdDe la EverandUna introducción a la criptografía de clave pública 2ª. EdÎncă nu există evaluări

- 359 - Electrónica Digital 2012-13Document20 pagini359 - Electrónica Digital 2012-13Jose Enrique Nanquen OrtizÎncă nu există evaluări

- TD Apunte8Document23 paginiTD Apunte8Fernando Sobrino-Manzanares MasÎncă nu există evaluări

- Carpeta Taller Electronica DigitalDocument54 paginiCarpeta Taller Electronica DigitaljeserripomaÎncă nu există evaluări

- Maquinas de Estado FinitoDocument14 paginiMaquinas de Estado FinitoPepe Del AngelÎncă nu există evaluări

- UD1 - 1 - Conceptos Basicos Electronica DigitalDocument12 paginiUD1 - 1 - Conceptos Basicos Electronica DigitalFernando Sobrino-Manzanares MasÎncă nu există evaluări

- Tema6 CircuitosSecuencialesSincronosDocument62 paginiTema6 CircuitosSecuencialesSincronosMaria Victoria PadillaÎncă nu există evaluări

- 9 Automatismoelectronico266-312Document48 pagini9 Automatismoelectronico266-312Javier CarrizoÎncă nu există evaluări

- Electronica DigitalDocument20 paginiElectronica DigitalKhristian ChambaÎncă nu există evaluări

- Electronica Digital Libro PDFDocument19 paginiElectronica Digital Libro PDFdianapatriciadoradoÎncă nu există evaluări

- Electrónica Digital (4º ESO)Document16 paginiElectrónica Digital (4º ESO)shensey001Încă nu există evaluări

- Digitpri PDFDocument0 paginiDigitpri PDFToto ComemocosÎncă nu există evaluări

- Diseño de Elenmentos MecanicosDocument9 paginiDiseño de Elenmentos MecanicosGeovannied Zet de SantiagoÎncă nu există evaluări

- Control DigitalDocument23 paginiControl DigitalJesus Grover NinaÎncă nu există evaluări

- Circuitos y Sistemas DigitalesDocument175 paginiCircuitos y Sistemas DigitalesCarlos Espinoza100% (11)

- Sindrome de AspergerDocument1 paginăSindrome de AspergerLaura PerlataÎncă nu există evaluări

- Maquinas de Estado FinitoDocument14 paginiMaquinas de Estado FinitoPepe Del AngelÎncă nu există evaluări

- Manual de Electronic A AnalogicaDocument60 paginiManual de Electronic A AnalogicaBrian AnguloÎncă nu există evaluări

- AspergerDocument21 paginiAspergerlcastillo24100Încă nu există evaluări

- Ejemplo de Maquina de EstadosDocument7 paginiEjemplo de Maquina de Estadoskaggi0Încă nu există evaluări

- Análisis y Diseño de Circuitos DigitalesDocument44 paginiAnálisis y Diseño de Circuitos DigitalesDaniel Bárcenas RosalesÎncă nu există evaluări

- Electronic A DigitalDocument22 paginiElectronic A DigitalJavier TrocelÎncă nu există evaluări

- Circuitos y Sistemas DigitalesDocument175 paginiCircuitos y Sistemas DigitalesCarlos Espinoza100% (11)

- 11-Modelado Con Maquinas de Estados PDFDocument10 pagini11-Modelado Con Maquinas de Estados PDFFernando Sobrino-Manzanares MasÎncă nu există evaluări

- 12-AUTISMO Y S+ìNDROME DE ASPERGERDocument4 pagini12-AUTISMO Y S+ìNDROME DE ASPERGERCristian Arturo Paredes QuijandríaÎncă nu există evaluări

- Epot 1 IntroduccionDocument14 paginiEpot 1 Introduccionglz1Încă nu există evaluări

- Electronica de Potencia PDFDocument65 paginiElectronica de Potencia PDFSaga_10Încă nu există evaluări

- EI Tema 2.intro EPDocument8 paginiEI Tema 2.intro EPDonald Santana BautistaÎncă nu există evaluări

- Teoria de Electron CIA de PotenciaDocument19 paginiTeoria de Electron CIA de PotenciaNelly ChaconÎncă nu există evaluări

- Teoria de Electron CIA de PotenciaDocument19 paginiTeoria de Electron CIA de PotenciaNelly ChaconÎncă nu există evaluări

- Mapas de KarnaughDocument16 paginiMapas de KarnaughRicardo PiscoÎncă nu există evaluări

- Simplificacion de Circuitos LogicosDocument7 paginiSimplificacion de Circuitos LogicosJOSUEÎncă nu există evaluări

- Autoevaluacion 9 FJ2016Document1 paginăAutoevaluacion 9 FJ2016Wilson Daniel Machado ToroÎncă nu există evaluări

- Sistenas Digitales 27 OctDocument8 paginiSistenas Digitales 27 OctCamila LugoÎncă nu există evaluări

- Mapas de KarnaughDocument7 paginiMapas de KarnaughNathaly Freire LopezÎncă nu există evaluări

- Mapas de KarnaughDocument13 paginiMapas de KarnaughRossana Ramirez ZeceñaÎncă nu există evaluări

- Taller Mapas KanaughDocument4 paginiTaller Mapas KanaughMarcos SuarezÎncă nu există evaluări

- Presentacion DigitalDocument6 paginiPresentacion DigitalNelsonÎncă nu există evaluări

- Primera Entrega - TR1 1234Document5 paginiPrimera Entrega - TR1 1234Hean Carlos Condori cantaniÎncă nu există evaluări

- Laboratorio Calificado 1 - 202202 (No Presencial)Document17 paginiLaboratorio Calificado 1 - 202202 (No Presencial)Edgarciito Bryan Nino CcosccoÎncă nu există evaluări

- INFORMEPREVIODIGITALESDocument6 paginiINFORMEPREVIODIGITALESGabriela MoralesÎncă nu există evaluări

- Multiplicador Con Salida en DisplayDocument6 paginiMultiplicador Con Salida en DisplayMario Brossasd0% (1)

- Unidad 3Document11 paginiUnidad 3carlospovedaÎncă nu există evaluări

- Simplificacion - Mapas - KarnaughDocument35 paginiSimplificacion - Mapas - KarnaughYamid GambaÎncă nu există evaluări

- Técnicas Digitales Apunte 4 - Mapas de KarnaughDocument15 paginiTécnicas Digitales Apunte 4 - Mapas de KarnaughProf Matias GarciaÎncă nu există evaluări

- Tema 3. Álgebra Booleana.Document15 paginiTema 3. Álgebra Booleana.Gilbert Beltran CortesÎncă nu există evaluări

- EjerciciosDocument11 paginiEjerciciosJUAN CAMILO MIRANDA MERCADOÎncă nu există evaluări

- Cap 6 Circuitos Combinatorios Definitivo PDFDocument42 paginiCap 6 Circuitos Combinatorios Definitivo PDFStefano GarciaÎncă nu există evaluări

- Circuitos DigitalesDocument3 paginiCircuitos Digitalesbryan puma100% (1)

- Simplificación de Circuitos LógicosDocument13 paginiSimplificación de Circuitos LógicosLeviatannlpÎncă nu există evaluări

- Informe 4Document7 paginiInforme 4Edzel A. Escobar CuetoÎncă nu există evaluări

- Tema6 AlgebraBOOLEDocument29 paginiTema6 AlgebraBOOLEEk LuisÎncă nu există evaluări

- Primer Parcial - Revisión Del Intento ArqDocument6 paginiPrimer Parcial - Revisión Del Intento ArqJonas BritoÎncă nu există evaluări

- Ejercicios de Mapas de Karnaugh 1Document4 paginiEjercicios de Mapas de Karnaugh 1Richy RicardoÎncă nu există evaluări

- Diseño de Circuitos CombinatoriosDocument11 paginiDiseño de Circuitos CombinatoriosKenneth CárdenasÎncă nu există evaluări

- Mapas de KarnaughDocument22 paginiMapas de KarnaughLeonard MoralesÎncă nu există evaluări

- Mapa de KarnaughDocument4 paginiMapa de KarnaughMayra Rivas VillaÎncă nu există evaluări

- Mapas de KarnaughDocument3 paginiMapas de KarnaughEnrique PocerosÎncă nu există evaluări

- Mapas de Karnaugh de Dos Variables GerlysDocument12 paginiMapas de Karnaugh de Dos Variables GerlysLuis Sarmiento BecerraÎncă nu există evaluări

- Compuertas Logicas y Algebra Booleana - Capitulo2 PDFDocument105 paginiCompuertas Logicas y Algebra Booleana - Capitulo2 PDFDarwin NavasÎncă nu există evaluări