Documente Academic

Documente Profesional

Documente Cultură

INF1500 H10 Cours 6

Încărcat de

Mohamed ZarboubiTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

INF1500 H10 Cours 6

Încărcat de

Mohamed ZarboubiDrepturi de autor:

Formate disponibile

INF1500 :

Logique des systèmes numériques

Cours 6: Circuits séquentiels plus

complexes (MSI)

Sylvain Martel - INF1500 1

Registres

Un registre est un ensemble de bascules et de

quelques portes logiques pour garder en mémoire un

code binaire de façon temporaire. Dans ce chapitre,

on considère principalement les registres construits

avec des bascules D.

En plus d’une horloge, un registre a besoin d’un signal

de contrôle pour indiquer quand les données placées à

l’entrée doivent être chargées en mémoire. Une façon

robuste de réaliser ce circuit consiste à placer un

multiplexeur à l’entrée de chaque bascule. Le signal

de contrôle est appliqué à la ligne de sélection du

multiplexeur. Le diagramme suivant représente un

registre à 1 bit.

Sylvain Martel - INF1500 2

Registres - Suite

Le registre est chargé de la valeur D0 sur une transition d’horloge

quand le signal ‘charge’ a la valeur 1. Tant que ‘charge’ vaut 0, le

registre garde en mémoire la valeur qu’il contient.

Sylvain Martel - INF1500 3

Registre à chargement parallèle

En plaçant plusieurs registres à 1 bit en parallèle, on peut garder

en mémoire des codes à plusieurs bits. On obtient ainsi un registre

à chargement parallèle. Le diagramme suivant représente un

registre à chargement parallèle à 4 bits.

Sylvain Martel - INF1500 4

Pentium

Sylvain Martel - INF1500 5

Processeur: Temps par étage du pipeline

(UCT – CPU)

Registre

T1 T2 T3

FREQ = 1 / MAX (T1, T2, T3)

Horloge

Sylvain Martel - INF1500 6

Registre à décalage

(Shift Register)

Un registre à décalage permet

d’effectuer un décalage sériel de

son contenu. Il y a plusieurs

applications pour ce genre de

registre. On pense entre autres

aux communications sérielles RS-

232 et à la multiplication et la

division binaires.

Le décalage peut s’effectuer vers

la droite, la gauche ou les deux.

Sylvain Martel - INF1500 7

Shift-Register (SR)

(4) (2) Copyright © 2000 by Prentice Hall, Inc.

1D D Q 1Q Digital Design Principles and Practices, 3/e

(3)

CLK Q 1Q_L

CLR (a)

(5) (7)

2D D Q 2Q

(6)

CLK Q 2Q_L

CLR

74x175

(b) 9

CLK

(12) (10) 1

3D D Q 3Q CLR

2

(11) 4 1Q

CLK Q 3Q_L 1D 3

1Q

CLR 7

5 2Q

2D 6

2Q

10

12 3Q

(13) (15) 3D 11

4D D Q 4Q 3Q

15

(14) 13 4Q

(9) CLK Q 4Q_L 4D 14

CLK 4Q

CLR

(1)

CLR_L

Sylvain Martel - INF1500 8

Multiplication et Division (SR)

0 0 1 0 =2

0 1 0 0 =2x2=4

0 0 1 0 =4÷2=2

Sylvain Martel - INF1500 9

Pentium

Multiplication

Division

Sylvain Martel - INF1500 10

Compteurs

Un compteur est un registre dont le contenu change

(en général) avec chaque coup d’horloge. Le

compteur passe à travers une séquence prédéfinie

d’états indépendamment de tout signal d’entrée (à

part l’horloge). La sortie du compteur est donnée

directement par ses variables d’état, c’est à dire par

la valeur de chaque bascule.

Par exemple, un compteur binaire à trois bits aurait la

séquence {000, 001, 010, 011, 100, 101, 110, 111,

000, 001, 010, etc.}.

Il y a plusieurs sortes de compteurs et plusieurs

façons de les réaliser.

Sylvain Martel - INF1500 11

Types de compteurs

Compteurs à déferlement (en cascade)

Dans un compteur à déferlement (ripple counter), les

différentes bascules n’ont pas d’horloge commune. La sortie

d’une bascule sert plutôt de signal d’horloge à la bascule

suivante.

Ce genre de circuit n’est pas très fiable, surtout si le

nombre de bascules est grand, parce qu’il est de nature

asynchrone (pas d’horloge commune). Cependant, il est

très simple.

L’utilisation de bascules JK connectées en configuration T

(Toggle) simplifie grandement le circuit par rapport à

l’utilisation de bascules D.

Sylvain Martel - INF1500 12

Types de compteurs - Suite

Compteurs synchrones

Dans un compteur synchrone, les bascules partagent

une horloge commune.

Autres compteurs

Compteurs vers le haut, vers le bas, vers le haut ou le

bas, avec ou sans chargement parallèle, avec ou sans

signal de remise à zéro ou à un, avec ou sans

possibilité de décalage vers la droite ou la gauche,

BCD, avec une séquence arbitraire, alouette, etc.

Sylvain Martel - INF1500 13

Compteurs en cascade (asynchrones)

Q Q0

CLK T

Q

Q Q1

T

Q

Q Q2

T

Q

Q Q3

T

Q

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 14

Compteurs synchrones 2 bits

Next-state Logic F State Memory Output Logic G

output

input MAX

excitation

EN

EN

D0 Q0

D Q

EN′

CLK Q

Q0

Q0′

D1 Q1

D Q

CLK Q

Q1

Q1′

clock signal

current state

CLK

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 15

Compteurs synchrones 4 bits

CNTEN EN Q Q0

CLK T

EN Q Q1

T

EN Q Q2

T

EN Q Q3

T

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 16

Compteur 74LS163

74x163 74x163

2 2

CLK CLOCK CLK

1 1

CLR CLR

9 9

LD LD

7 +5 V 7

ENP R ENP

10 RPU 10

ENT ENT

3 14 3 14

A QA A QA QA

4 13 4 13

B QB B QB QB

5 12 5 12

C QC C QC QC

6 11 6 11

D QD D QD QD

15 15

RCO RCO RCO

U1

Copyright © 2000 by Prentice Hall, Inc. Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 17

Compteur 74LS163 (gate level)

(2)

CLK

(9)

LD_L

(1)

CLR_L

(3)

A

(14)

D Q QA

CK Q

(4)

B

(13)

D Q QB

CK Q

(5)

C

(12)

D Q QC

CK Q

(6)

D

(11)

D Q QD

CK Q

(15)

RCO

(7)

ENP

(10)

ENT

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 18

Compteurs 74LS161 et 74LS163

(timing diagram)

CLK

QA

QB

QC

QD

RCO

COUNT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 19

Montage avec le 74LS163

74x163

2

CLOCK CLK

1

CLR À Q3Q2Q1Q0=1100, on

9

LD recharge DCBA à 0011

7

10

ENP via LD

ENT

+5 V 3 14

R A QA Q0

RPU 4 13

B QB Q1

5 12

C QC Q2

6 11

D QD Q3

15

RCO 74x00

1

3

U1 2

U2

Démarre toujours S11XX_L

à la valeur binaire Copyright © 2000 by Prentice Hall, Inc.

DCBA = 0011 Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 20

Montage avec le 74LS163 - Suite

Un compteur modulo-9 avec la séquence 3,4,…,9,3,4,…

CLOCK

Q0

Q1

Q2

Q3

COUNT 3 4 5 6 7 8 9 10 11 12 3

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 21

Montage en cascade synchrone avec deux

74LS163

74x163 74x163

2 2

CLOCK CLK CLK

1 1

RESET_L CLR CLR

9 9

LOAD_L LD LD

7 7

CNTEN ENP ENP

10 10

ENT ENT

3 14 3 14

D0 A QA Q0 D4 A QA Q4

4 13 4 13

D1 B QB Q1 D5 B QB Q5

5 12 5 12

D2 C QC Q2 D6 C QC Q6

6 11 6 11

D3 D QD Q3 D7 D QD Q7

15 RCO4 15

RCO RCO RCO8

U1 U2

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 22

Montage avec le 74LS163

74x163

+5 V

2

Compteur

CLK

1

CLR

R 9

modulo-193

LD

7

ENP

RPU

avec la

10

ENT

3 14

A QA Q0

séquence

4 13

B QB Q1

5 12

C QC Q2

63,64,…,266,6 6

D QD

11

15

Q3

3,64,…

RCO

CLOCK

U2

RESET_L RCO4

74x00

1

GO_L 3 CNTEN 74x163

2

2

CLK

U1 74x00 1

4 CLR

6 RELOAD_L 9

5 LD

7

ENP

U1 10

ENT

3 14

A QA Q4

4 13

B QB Q5

5 12

C QC Q6

6 11

D QD Q7

15

RCO MAXCNT

U3

Copyright © 2000 by Prentice Hall, Inc.

Sylvain Martel - INF1500 Digital Design Principles and Practices, 3/e 23

Symboles

DFF SPC

D D 4

÷?

Q[3:0]

RST RST (CLR)

COUNTER REG PSC

D[3:0] 4 4 D[3:0] 4

D Q D Q

4

CNT Q[3:0]

Q[3:0]

RST (CLR) LD RST (CLR) RST (CLR)

Sylvain Martel - INF1500 24

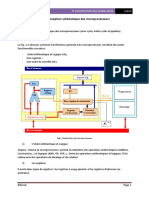

Simple Ordinateur

Mémoire

Mémoire Mémoire

D1 D2 Instructions

Horloge (oscillateur)

Pipeline (UCT (CPU))

Résultats

RESET

Mémoire

Sylvain Martel - INF1500 25

Structure d’un RAM statique (SRAM)

IN OUT

IN

D Q OUT SEL

SEL_L WR

C

WR_L

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 26

RAM statique (SRAM)

DIN3 DIN2 DIN1 DIN0

bit

line word line

0

IN OUT IN OUT IN OUT IN OUT

3-to-8

decoder SEL SEL SEL SEL

WR WR WR WR

1

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

2

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

A2 2 3

IN OUT IN OUT IN OUT IN OUT

A1 1 SEL SEL SEL SEL

WR WR WR WR

A0 0 4

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

5

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

6

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

7

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

WE_L WR_L

CS_L

IOE_L

OE_L

DOUT3 DOUT2 DOUT1 DOUT0

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 27

Structure d’une RAM statique

7

IN OUT IN OUT IN OUT IN OUT

SEL SEL SEL SEL

WR WR WR WR

WE_L

CS_L

OE_L

DIO3 DIO2 DIO1 DIO0

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 28

Diagramme temporel d’une RAM statique, en

lecture

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

ADDR stable stable stable

≥ tAA max(tAA,tACS)

CS_L

Note: WE_L = HIGH tACS tOH

OE_L

tAA tOZ tOE tOZ tOE

DOUT valid valid valid

Sylvain Martel - INF1500 29

Diagramme temporel d’une RAM statique, en

écriture

(WE-controlled write) (CS-controlled write)

ADDR stable stable

tCSW tAS tCSW

CS_L

tAS tWP tAH tWP tAH

WE_L

tDS tDH tDS tDH

DIN valid valid

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e

Sylvain Martel - INF1500 30

Pentium

SRAM (Cache)

Sylvain Martel - INF1500 31

Simple UCT

Adresse SRAM

00 0101 Décodeur EXEC 0

01 0001

Décodeur

Compteur

Data 0

EXEC 15

Data 1

Oscillateur

Sylvain Martel - INF1500 32

Simple UCT (Codes pour les instructions)

SRAM

0101

0001

Sylvain Martel - INF1500 33

Hiérarchie: Registre

PR_L

CLR_L Q

(4) (2) Copyright © 2000 by Prentice Hall, Inc.

CLK QN 1D D Q 1Q Digital Design Principles and Practices, 3/e

(3)

CLK Q 1Q_L

CLR (a)

D

Copyright © 2000 by Prentice Hall, Inc.

Digital Design Principles and Practices, 3/e (5) (7)

2D D Q 2Q

(6)

CLK Q 2Q_L

CLR

74x175

(b) 9

CLK

(12) (10) 1

3D D Q 3Q CLR

2

(11) 4 1Q

CLK Q 3Q_L 1D 3

1Q

CLR 7

5 2Q

2D 6

2Q

10

12 3Q

(13) (15) 3D 11

4D D Q 4Q 3Q

15

(14) 13 4Q

(9) CLK Q 4Q_L 4D 14

CLK 4Q

CLR

(1)

CLR_L

Sylvain Martel - INF1500 34

Exercices

Adresse SRAM

00 0101 Décodeur EXEC 0

01 0001

Décodeur

Compteur

Data 0

EXEC 15

Data 1

Oscillateur

Sylvain Martel - INF1500 35

Sylvain Martel - INF1500 36

S-ar putea să vă placă și

- Logique Séquentielle: Compteurs Intégrés AsynchronesDocument16 paginiLogique Séquentielle: Compteurs Intégrés AsynchronesbejaouiÎncă nu există evaluări

- 4ST ComptDocument7 pagini4ST ComptRouaissi RidhaÎncă nu există evaluări

- A2 1 Compteurs Integrés 17 18Document11 paginiA2 1 Compteurs Integrés 17 18Oumayma Ben MoussaÎncă nu există evaluări

- tp4 2l-Tic-Iot 2020-2021Document2 paginitp4 2l-Tic-Iot 2020-2021talel haninÎncă nu există evaluări

- Electronique Numérique Avancée: FPGA + VHDL: Donner Le Schéma Du Circuit Dont La Description VHDL Est La SuivanteDocument3 paginiElectronique Numérique Avancée: FPGA + VHDL: Donner Le Schéma Du Circuit Dont La Description VHDL Est La SuivanteBoudour BarkiaÎncă nu există evaluări

- PLD-JTAGDocument17 paginiPLD-JTAGdominique.bellayÎncă nu există evaluări

- Sequentiel LioDocument50 paginiSequentiel LioamourgloireÎncă nu există evaluări

- Manuel ProfesseurDocument17 paginiManuel Professeurnouredine akliÎncă nu există evaluări

- tp3 Ing 2015 PDFDocument7 paginitp3 Ing 2015 PDFDorian GreyÎncă nu există evaluări

- Comp Asy Elev 2017Document10 paginiComp Asy Elev 2017Hayet BechedliÎncă nu există evaluări

- Corigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueDocument5 paginiCorigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueHala SaimÎncă nu există evaluări

- BasculesDocument2 paginiBasculesAmine JraifÎncă nu există evaluări

- L5 CompteursDocument6 paginiL5 Compteurskossay laifiÎncă nu există evaluări

- Application À Base de Bascules 3emeDocument4 paginiApplication À Base de Bascules 3emeMed NasrÎncă nu există evaluări

- SondeDocument5 paginiSondekaragaine100% (1)

- Annexe: Extrait de La Fiche Technique Du Circuit 7490Document2 paginiAnnexe: Extrait de La Fiche Technique Du Circuit 7490takecoin767Încă nu există evaluări

- Série-N2 CorrectionDocument4 paginiSérie-N2 CorrectionHabib TrikiÎncă nu există evaluări

- Chapitre 5 Tranfert RegistresDocument37 paginiChapitre 5 Tranfert Registresdetrex kaneÎncă nu există evaluări

- 3 Cours Info Indus Partie3Document25 pagini3 Cours Info Indus Partie3Mourad HoulÎncă nu există evaluări

- Synthese Des Machines A Etats PDFDocument33 paginiSynthese Des Machines A Etats PDFMùstapha MànsouriÎncă nu există evaluări

- Dossier Technique 95spDocument7 paginiDossier Technique 95spouhssainanouarÎncă nu există evaluări

- 3 Compteur Synchrone 2011 2012Document8 pagini3 Compteur Synchrone 2011 2012Mohamed EL MASSOUDIÎncă nu există evaluări

- Exercices de CompteursDocument22 paginiExercices de CompteursRad PAMBUÎncă nu există evaluări

- Chap6 - Les Registres Et CompteursDocument12 paginiChap6 - Les Registres Et CompteursMOHAMED AIT HADDOUCHÎncă nu există evaluări

- Upload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDFDocument14 paginiUpload-Série D'exercices N°2-4tech-Compteur-2014-2015 PDFRached Douahchua100% (1)

- LIFASR3 TD56 CorDocument8 paginiLIFASR3 TD56 CorIbtissem DERRARÎncă nu există evaluări

- Microprocesseur 8086Document79 paginiMicroprocesseur 8086AMIRAFORTASÎncă nu există evaluări

- TP 3Document8 paginiTP 3DixÎncă nu există evaluări

- Compteurs/Décompteurs Intégrés - 2Document4 paginiCompteurs/Décompteurs Intégrés - 2Ali ChourouÎncă nu există evaluări

- Regitre - Dec Ex TpfpgaDocument8 paginiRegitre - Dec Ex TpfpgaZenache AhlemÎncă nu există evaluări

- Upload - Résumé Du Cours-Microcontroleurs - 2016-2017Document7 paginiUpload - Résumé Du Cours-Microcontroleurs - 2016-2017Habib Ben AmmarÎncă nu există evaluări

- (Elec) Elek - DeLPHI Pour Électroniciens 02-10Document4 pagini(Elec) Elek - DeLPHI Pour Électroniciens 02-10Madidj_20140% (1)

- Cours Circuits Numériques (Semestre 2) 1APDocument72 paginiCours Circuits Numériques (Semestre 2) 1APBruno PierreÎncă nu există evaluări

- Devoir de Synthèse N°1 2011 2012 (Taher Elhaded El Hamma)Document5 paginiDevoir de Synthèse N°1 2011 2012 (Taher Elhaded El Hamma)Youssef CherniÎncă nu există evaluări

- Contr Le Electronique Num Rique 2015 2016Document3 paginiContr Le Electronique Num Rique 2015 2016lolÎncă nu există evaluări

- CoursMP 1 ETL427Document24 paginiCoursMP 1 ETL427dbÎncă nu există evaluări

- Chapitre 6 Registre Et CompteursDocument14 paginiChapitre 6 Registre Et CompteursAbdelkerim LemaadiÎncă nu există evaluări

- R R 1) - CKA: Entrée D'horloge (DIV2) - CKB: Entrée D'horloge (DIV8) - Q Q Q QDocument50 paginiR R 1) - CKA: Entrée D'horloge (DIV2) - CKB: Entrée D'horloge (DIV8) - Q Q Q QAndy TchuisseuÎncă nu există evaluări

- Wa0018.Document4 paginiWa0018.ffghjhkkÎncă nu există evaluări

- Chapitre 2 Les Compteurs 2016 2017 (MR Azzem Mohamed) (Metlaoui Gafsa)Document8 paginiChapitre 2 Les Compteurs 2016 2017 (MR Azzem Mohamed) (Metlaoui Gafsa)Azerty QsdfghÎncă nu există evaluări

- Cours1 Muc Mii m1Document20 paginiCours1 Muc Mii m1Hicham BordjÎncă nu există evaluări

- TP1 4Document22 paginiTP1 4Abderrahmane WrÎncă nu există evaluări

- Jeu D'instructions 16F84A 16F628A 16F88 16F876A 16F886Document4 paginiJeu D'instructions 16F84A 16F628A 16F88 16F876A 16F886MoprometheusÎncă nu există evaluări

- TP Liaisons SerieDocument7 paginiTP Liaisons SerieImane SaharÎncă nu există evaluări

- Examen 2013 (ACAD)Document4 paginiExamen 2013 (ACAD)zakiÎncă nu există evaluări

- Devoir de Synthèse N°1 - Génie Mécanique Cellule Flexible - 3ème Technique (2011-2012) MR Hamdi DTDocument5 paginiDevoir de Synthèse N°1 - Génie Mécanique Cellule Flexible - 3ème Technique (2011-2012) MR Hamdi DTYoussef CherniÎncă nu există evaluări

- Chapitre 6 ElectroniqueDocument22 paginiChapitre 6 ElectroniqueimanesaidytÎncă nu există evaluări

- Chapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1Document12 paginiChapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1mohamed ben slimaneÎncă nu există evaluări

- DP 2Document4 paginiDP 2meriembelhadj2024Încă nu există evaluări

- Exercice PipelineDocument3 paginiExercice PipelineHamza Rahali100% (1)

- TDRevisionDocument4 paginiTDRevisionKatia ChalalÎncă nu există evaluări

- Registre A DecalageDocument3 paginiRegistre A Decalagerachid223Încă nu există evaluări

- Usto-Mb/Fac Ge/Eln/ M2 Travaux Pratiques: VHDL Et Fpga 2019-2020 TP1: Circuits Logiques Élémentaires Objectifs Du TPDocument4 paginiUsto-Mb/Fac Ge/Eln/ M2 Travaux Pratiques: VHDL Et Fpga 2019-2020 TP1: Circuits Logiques Élémentaires Objectifs Du TPfatima zahrabrzÎncă nu există evaluări

- DS1-COR-Lavage PrepayeDocument4 paginiDS1-COR-Lavage PrepayeMouad MemniÎncă nu există evaluări

- Le syndrome périodique associé à la cryopyrine (CAPS)De la EverandLe syndrome périodique associé à la cryopyrine (CAPS)Încă nu există evaluări

- Ing Hasna LamraouiDocument88 paginiIng Hasna LamraouiMohamed ZarboubiÎncă nu există evaluări

- Presentation J BerettaDocument55 paginiPresentation J BerettaMohamed ZarboubiÎncă nu există evaluări

- Ms GBM Oucheni+SakerDocument66 paginiMs GBM Oucheni+SakerMohamed ZarboubiÎncă nu există evaluări

- TP E Langage Description VHDL (Warp - 6.3)Document5 paginiTP E Langage Description VHDL (Warp - 6.3)Mohamed ZarboubiÎncă nu există evaluări

- CompressionDocument37 paginiCompressionMohamed ZarboubiÎncă nu există evaluări

- Exercice 1: Soit La Classe Complexe Pour Gérer Les Nombres ComplexesDocument2 paginiExercice 1: Soit La Classe Complexe Pour Gérer Les Nombres ComplexesMohamed ZarboubiÎncă nu există evaluări

- Travaux Diriges Devoir Examen PDFDocument20 paginiTravaux Diriges Devoir Examen PDFTarak Benslimane100% (2)

- Technologie Des Reseaux de CommunicationDocument354 paginiTechnologie Des Reseaux de CommunicationguijjouÎncă nu există evaluări

- Mast GBM Hamza+Ziani-CherifDocument76 paginiMast GBM Hamza+Ziani-CherifMohamed ZarboubiÎncă nu există evaluări

- 1295208Document72 pagini1295208Mohamed ZarboubiÎncă nu există evaluări

- GEII ElecNum TDDocument20 paginiGEII ElecNum TDMohamed Zarboubi100% (1)

- P05c Reg CPTDocument45 paginiP05c Reg CPTMohamed ZarboubiÎncă nu există evaluări

- For CompressionDocument32 paginiFor CompressionMohamed ZarboubiÎncă nu există evaluări

- VHDLDocument168 paginiVHDLMjid SaadiÎncă nu există evaluări

- CompressionDocument26 paginiCompressionMohamed ZarboubiÎncă nu există evaluări

- Efm 10 Corrige Exercice Sous AdressageDocument3 paginiEfm 10 Corrige Exercice Sous Adressageapi-2642018482% (28)

- Cours Filtres 1Document33 paginiCours Filtres 1medlkÎncă nu există evaluări

- La Compression PierreDocument13 paginiLa Compression PierreMohamed ZarboubiÎncă nu există evaluări

- Enoncé Des TP (Codage de Source)Document8 paginiEnoncé Des TP (Codage de Source)Abderrazak AbdÎncă nu există evaluări

- Cours VHD13-14-1Document30 paginiCours VHD13-14-1Mohamed ZarboubiÎncă nu există evaluări

- TP1Document5 paginiTP1Mohamed ZarboubiÎncă nu există evaluări

- La Compression de Donnc3a9esDocument9 paginiLa Compression de Donnc3a9esMohamed ZarboubiÎncă nu există evaluări

- 3 CompressionDocument31 pagini3 CompressionMohamed ZarboubiÎncă nu există evaluări

- Enoncé Des TP (Codage de Source)Document8 paginiEnoncé Des TP (Codage de Source)Abderrazak AbdÎncă nu există evaluări

- 3 CompressionDocument31 pagini3 CompressionMohamed ZarboubiÎncă nu există evaluări

- 726 Exercices Codes CorrecteursDocument6 pagini726 Exercices Codes CorrecteursAli Ben Messaoud79% (14)

- Enoncé Des TP (Codage de Source)Document8 paginiEnoncé Des TP (Codage de Source)Abderrazak AbdÎncă nu există evaluări

- 726 Exercices Codes CorrecteursDocument6 pagini726 Exercices Codes CorrecteursAli Ben Messaoud79% (14)

- Td1 Master TR PDFDocument7 paginiTd1 Master TR PDFabdellahmorÎncă nu există evaluări

- BC402 4.6a FRDocument246 paginiBC402 4.6a FRmhalcan1Încă nu există evaluări

- Prog Parallèle Seance 2 20 21Document191 paginiProg Parallèle Seance 2 20 21FatimaÎncă nu există evaluări

- Travaux Diriges N 1 2 3 Sam Au 2021 2022Document9 paginiTravaux Diriges N 1 2 3 Sam Au 2021 2022Kam ZegÎncă nu există evaluări

- Cours API2Document124 paginiCours API2Mbarek OrabiÎncă nu există evaluări

- Chp4 AutomatismeDocument15 paginiChp4 AutomatismeAbdl Karim Ben AchourÎncă nu există evaluări

- Cours Sur Les Automates Programmables Industriels: LTA-Laboratoire D'automatismesDocument39 paginiCours Sur Les Automates Programmables Industriels: LTA-Laboratoire D'automatismesExode Christ GuielleÎncă nu există evaluări

- Interruptions Et Timers Du 8051Document8 paginiInterruptions Et Timers Du 8051Maha BadriÎncă nu există evaluări

- Cours Arduino PDFDocument8 paginiCours Arduino PDFFrancklin TokimitondrasoaÎncă nu există evaluări

- TP Circuits LogiquesDocument3 paginiTP Circuits LogiquesimenessÎncă nu există evaluări

- MA1Document223 paginiMA1Abdelkrim Lamrous100% (2)

- Introduction PDFDocument30 paginiIntroduction PDFSelima GadriÎncă nu există evaluări

- stm32 PDFDocument29 paginistm32 PDFHaythem ChaouedÎncă nu există evaluări

- Expose Allocation MemoireDocument17 paginiExpose Allocation MemoireNYAMI MBITHEÎncă nu există evaluări

- Cours - Conception Des Systemes EmbarquesDocument36 paginiCours - Conception Des Systemes EmbarquesReda BoutenfitÎncă nu există evaluări

- A1-Présentation Des Machines Virtuelles AzureDocument27 paginiA1-Présentation Des Machines Virtuelles Azureichbin1199Încă nu există evaluări

- Cours 3 - Chapitre III - Jeux D - Instructions - 2020 PDFDocument35 paginiCours 3 - Chapitre III - Jeux D - Instructions - 2020 PDFboujemaa SAADATÎncă nu există evaluări

- Les Microcontroleurs Pic16f84Document28 paginiLes Microcontroleurs Pic16f84Mohssin FsjesÎncă nu există evaluări

- TDBD Part1Document24 paginiTDBD Part1Mbaye Babacar MBODJÎncă nu există evaluări

- Poo 1Document50 paginiPoo 1Sami BrahmiÎncă nu există evaluări

- TP3: Conception Schématique Des Microprocesseurs: ObjectifDocument6 paginiTP3: Conception Schématique Des Microprocesseurs: ObjectifDor SafÎncă nu există evaluări

- TP #1 Montage Et Démontage D'un PCDocument15 paginiTP #1 Montage Et Démontage D'un PCnourÎncă nu există evaluări

- Annales 3Document24 paginiAnnales 3Chafik BerdjouhÎncă nu există evaluări

- COURS ImsetDocument17 paginiCOURS ImsetSkander Ben OthmenÎncă nu există evaluări

- Cours SE1 Chap1Document15 paginiCours SE1 Chap1AmarMadridÎncă nu există evaluări

- Modul4 MotionControl KHI2012 FDocument16 paginiModul4 MotionControl KHI2012 FKhaled OuniÎncă nu există evaluări

- Cours PGM API Chapt2 PDFDocument28 paginiCours PGM API Chapt2 PDFtoto111111111Încă nu există evaluări

- GE MP16bDocument98 paginiGE MP16bSafaa BelagounÎncă nu există evaluări

- Instructions 6809Document2 paginiInstructions 6809Antonio SabaÎncă nu există evaluări

- L'Assembleur Mplab - Ide: Les Outils de DeveloppementDocument13 paginiL'Assembleur Mplab - Ide: Les Outils de DeveloppementTamokoueÎncă nu există evaluări

- Support de Cours: Système D'exploitation IDocument19 paginiSupport de Cours: Système D'exploitation Islim yaichÎncă nu există evaluări