Documente Academic

Documente Profesional

Documente Cultură

ET6218R EtekMicroelectronics

Încărcat de

Hasnah HusnaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

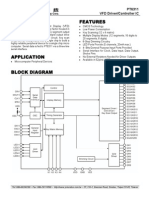

ET6218R EtekMicroelectronics

Încărcat de

Hasnah HusnaDrepturi de autor:

Formate disponibile

Etek

Microelectronics ET6218R

LED Controller/driver

General Description

ET6218R is an LED Controller driver on a 1/7 to 1/8 duty factor. 7 segment output lines, 4 grid output lines,

1 segment/grid output lines, one display memory, control circuit, key scan circuit are all incorporated into a single

chip to build a highly reliable peripheral device for a single chip microcomputer. Serial data is fed to ET6218R via

a three-line serial interface, ET6218R pin assignments and application circuit are optimized for easy PCB Layout

and cost saving advantages.

Features

z CMOS Technology

z Low Power Consumption

z Multiple Display Modes(4~5 Grid, 7~8 segment)

z Key scaning(7×1 Matrix)

z 8-step Dimming Circuitry

z Serial Interface for Clock, Data Input/Output, Strobe Pins

z Available in 18-pin, DIP Package

Pin Configurations

Rev 1.0 2012-4-13

1/15

ET6218R

Pin Description

Pin No. Pin Name I/O Description

Data I/O Pin(N-channel, Open-Drain)

This pin outputs serial data at the falling edge of the shift clock and

5 DI/O(DIN&DOUT) I/O

inputs serial data at the rising edge of the shift clock(starting from the

lower bit)

Clock Input Pin

6 CLK I This pin reads serial data at the rising edge and outputs data at the

falling edge

Serial Interface Strobe Pin

7 STB I The data input after the STB has fallen is processed as a command

When this pin is “HIGH”, CLK is ignored

Key Data Input Pins

8 K1 I The data sent to these pins are latched at the end of the display cycle

(Interface Pull-Low Resistor)

2 GND ─ Ground Pin

SG1/KS1~ Segment Output Pins(p-channel, open drain) Also acts as the Key

10~16 O Source

SG7/KS7

17 SG14/GR5 O Segment/Grid Output Pins

9 VDD ─ Power Supply

1,3,4,18 GR4~GR1 O Grid Output Pins

INPUT/OUTPUT CONFIGURATIONS

The schematic diagrams of the input and output circuits of the logic section are shown below.

1. Input Pins:CLK,STB&DIN(DI/O)

GND

Rev 1.0 2012-4-13

2/15

ET6218R

2. Input Pins:K1

VDD

GND

3. Output Pins:DOUT(DI/O),GR1~GR4

VDD

GND

4. Output Pins:SG1~SG7

VDD

GND

Rev 1.0 2012-4-13

3/15

ET6218R

5. SG14/GR5

VDD

GND

Block Diagram

Rev 1.0 2012-4-13

4/15

ET6218R

Functional Description

COMMANDS

A command is the first byte(b0~b7) inputted to ET6218R via the DI/O Pin after STB Pin has changed from

HIGH to LOW State. If for some reason the STB Pin is set to HIGH while data or commands are being

transmitted, the serial communication is initialized, and the data/commands being transmitted are considered

invalid.

Command 1:Display Mode Setting Commands

ET6218R provides 2 display mode settings as shown in the diagram below:As started earlier a command is

the first one byte(b0~b7) transmitted to ET6218R via the DI/O Pin when STB is LOW. However, for these

commands,the bit 3 to bit 6(b2~b5)are ignored,bit 7&bit 8(b6~b7) are given a value of 0.

The Display Mode Setting Commands determine the number of segments and grids to be used (7 to 8

segments,4 to 5 grids). A display command ON must be excuted in order to resume display. If the same mode

setting is selected, no command execution is take place, therefore, nothing happens. When Power is turned ON,the

7-grid, 10-segment modes is selected.

MSB LSB

0 0 ─ ─ ─ ─ b1 b0

b2~b5:Not Relevant

Display Mode Setting:

b1,b0—0 0:4 Grids,8 Segments

b1,b0—0 1:5 Grids,7 Segments

Command 2:Data Setting Commands

Data Setting Commands executes the Data Write or Data Read Modes for ET6218R. The data Setting

Command, the bits 5 and 6(b4,b5) are ignored, bit 7(b6) is given the value of 1 while bit 8(b7) is given the value

of 0. Please refer to the diagram below. When Power is turned ON, bit 4 to bit 1(b3~b0) are given the value of 0.

MSB LSB

0 1 ─ ─ b3 b2 b1 b0

b4,b5:Not Relevant

Mode Setting: b3 —0:Normal Operation

Mode b3—1:Test Mode

Address Increment Mode Settings(Display Mode):

b2—0:Increment Address after Data has been Written

b2—1:Fixes Address

Data Write&Read Mode Setting:

b1,b0—0 0:Write Data to Display Mode

b1,b0—1 0:Read Key Data

Rev 1.0 2012-4-13

5/15

ET6218R

ET6218R KEY MATRIX&KEY INPUT DATA STORAGE RAM

ET6218R Key Matrix consists of 7×1 array as shown below:

Each data entered by each key is stored as follows and read by a READ Command, starting from the last

significant bit of the next data(b7) is read.

K1 K1

READING

SG1/KS1 SG2/KS2 x SEQUENCE

SG3/KS3 SG4/KS4 x

SG5/KS5 SG6/KS6 x

SG7/KS7 x

b0 b3 b6

Note:b6 do not care.

Command 3:Address Setting Commands

Address Setting Commands are used to set the address of the display memory. The address is considered

valid if it has a value of 00H to 0DH. If the address is set to 0EH or higher,the data is ignored until a valid address

is set. When power is turned ON,the address is set at 00H.

MSB LSB

1 1 ─ ─ b3 b2 b1 b0

b4,b5:Not Relevant

The address of b3~b0:00H~0DH

Rev 1.0 2012-4-13

6/15

ET6218R

DISPLAY MODE AND RAM ADDRESS

Data transmitted from an external device to ET6218R via the interface are stored in the Display RAM and

are assigned address. The RAM addresses of ET6218R are given below in 8 bits unit.

SG1…………SG4 SG5…………SG8 SG9…………SG12 SG13…………SG14

00HL 00HU 01HL 01HU DIG1

02HL 02HU 03HL 03HU DIG2

04HL 04HU 05HL 05HU DIG3

06HL 06HU 07HL 07HU DIG4

08HL 08HU 09HL 09HU DIG5

b0…………….b3 b4………………b7

xxHL xxHU

Lower 4 bits Higher 4 bits

Command 4:Display Control Commands

The Display Control Commands are used to turn ON or OFF a display. It also used to set the pulse width.

Please refer to the diagram below. When the power is turned ON,a 1/16 pulse width is selected and the displayed

is turned OFF(the key scaning is stopped).

MSB LSB

1 0 ─ ─ b3 b2 b1 b0

b4,b5 :Not Relevant

Display Setting: b3—0:Display OFF(Key Scan Continues)

b3—1:Display ON

Dimming Quantity Setting:

000:Pulse width=1/16

001:Pulse width =2/16

010:Pulse width =4/16

011:Pulse width =10/16

100:Pulse width =11/16

101:Pulse width =12/16

110:Pulse width =13/16

111:Pulse width =14/16

Rev 1.0 2012-4-13

7/15

ET6218R

SCANNING AND DISPLAY TIMING

The Key Scanning and Display Timing diagram is given below. One cycle of key scanning consists of 2

frames. The data of the are 7×1 matrix is stored in the RAM.

Tdisplay=500us Key Scan Data

SG Output DIG1 DIG2 DIG3 DIGn DIG1

G1

G2

G3

Gn

1frame=Tdisplay ×(n+1)

Rev 1.0 2012-4-13

8/15

ET6218R

SERIAL COMMUNICATION FORMAT

The following diagram shows the ET6218R serial communication format.The DI/O(DIN,DOUT) Pin is an

N-channel,open-drain pin, therefore, it is highly recommended that an external pull-up resistor(1K~10K) must be

connected to DI/O.

Reception(Data/Command Writer)

If data continues

STB

DIN

b0 b1 b2 b6 b7

CLK

1 2 3 7 8

Transmission(Data Read)

STB

DIN

b0 b1 b2 b3 b4 b5 b6 b7

CLK

1 2 3 4 5 6 7 8 1 2 3 4 5 6

twait

DOUT

b0 b1 b2 b3 b4 b5

Data Read Command is set Data Reading starts

twait(waiting time)≥1µs

It must be noted that when the data is read, the waiting time(twait) between the rising of the eighth clock that

has set the command and the galling of the first clock that has read the data is greater or equal to 1µs.

Rev 1.0 2012-4-13

9/15

ET6218R

SWITCHING CHARACTERISTIC WAVEFORM

ET6218R Switching Characteristics Waveform is given below.

fosc

OSC 50%

PWSTB

STB

PWCLK PWCLK

t CLK-STB

CLK

t setup t hold

DIN

t PZL t PLZ

DOUT

t TZL t TLZ

Gn

90%

10%

10%

90%

Sn

t TZH t THZ

PWCLK(Clock Pulse Width)≥400ns PWSTB(Strobe Pulse Width)≥1µs

tsetup(Data Setup Time)≥100ns thold(Data Hold Time)≥100ns

tCLK-STB(Clock-Strobe Time)≥1µs tTHZ(Fall Time)≤10µs

tTZH(Rise Time)≤1µs tPZL(Propagation Delay Time)≤100ns

fosc=Ocillation Frequency tPLZ(Propagation Delay Time)≤300ns

tTZL<1µs tTLZ<10µs

Rev 1.0 2012-4-13

10/15

ET6218R

Note:Test condition under

tTHZ(Pull low risistor=10kΩ,Loading capacitor=300pf)

tTLZ(Pull low risistor=10 kΩ,Loading capacitor =300pf)

APPLICATION

1. Display memory is updated by incrementing addresses. Please refer to the following diagram.

STB

CLK

DIN Command2 Command3 Data1 Data n Command1 Command4

Command 1:Display Mode Setting Command

Command 2:Data Setting Command

Command 3:Address Setting Command

Data 1~n:Transfer Display Data(14 Bytes max)

Command 4:Display Control Command

2. The following diagram shows the waveform when updating specific addresses.

STB

CLK

DIN Command2 Command3 Data Command3 Data

Command 2:Data Setting

Command Command 3:Address Setting Command

Data:Display Data

Rev 1.0 2012-4-13

11/15

ET6218R

RECOMMENDED SOFTWARE PROGRAMMING FLOWCHART

START

Delay 200 ms

SET

COMMAND2

(Writer Data)

SET

COMMAND3

Clear Display RAM

(See Note 5)

SET

COMMAND1

INITIAL

SETTING

SET

COMMAND4

(88H-87H:Display OFF)

SET

COMMAND1

SET

COMMAND4

(88H-8FH:Display ON)

MAIN PROGRAM

SET

COMMAND2

(READ KEY & WRITER DATA INCLUDED)

MAIN

SET LOOP

COMMAND3

SET

COMMAND1

SET

COMMAND4

END

Rev 1.0 2012-4-13

12/15

ET6218R

Note:1. Command 1:Display Mode Commands

2. Command 2:Data Setting Commands

3. Command 3:Address Setting Commands

4. Command 4:Display Control Commnads

When IC power is applied for the first time, the contents of the Display RAM is not defined; thus, it is

strongly suggested that the contents of the Display RAM must be cleared during the initial setting.

Absolute Maximum Ratings(Ta = 25℃,GND = 0V)

Parameter Symbol Ratings Unit

Supply Voltage VDD -0.5~+7 V

Logic Input Voltage VI -0.5~VDD+0.5 V

IOLGR +250 mA

Driver Output Current

IOHSG -50 mA

Maximum Driver Output Current/Total ITOTAL 400 mA

Operating Temperature Topr -40~+85 ℃

Storage Temperature Tstg -55~+150 ℃

Recommended Operating Range(Ta = -20~+70℃,GND = 0V)

Parameter Symbol Min. Typ. Max. Unit

Logic Supply Voltage VDD 3 5 5.5 V

Dynamic Current(see Note) IDDdyn — — 5 mA

High-Level Input Voltage VIH 0.6VDD — VDD V

Low- Level Input Voltage VIL 0 — 0.3VDD V

Note:Test Condition:Set Display Control Commands=80H(Display Turn OFF State&under no load)

Electrical Characteristics(VDD = 5V,GND = 0V,Ta = 25℃)

Parameter Symbol Test Condition Min. Typ. Max. Unit

VO =VDD-2V,SG1~SG7,

IOHSG1 -20 -25 -40 mA

SG14

High-Level Output Current

VO =VDD-3V,SG1~SG7,

IOHSG2 -25 -30 -50 mA

SG14

Low-Level Output Current IOLGR VO =0.3V,GR1~GR5, 100 140 — mA

Low-Level Output Current IOLDOUT VO =0.4V 4 — — mA

Segment High-Level VO =VDD-3V,SG1~SG7,

ITOLSG — — +5 %

Output Current Tolerance SG14

0.6

High-Level Input Voltage VIH — — 5 V

VDD

0.3

Low-Level Input Voltage VIL — 0 — V

VDD

Oscillation Frequency fosc 350 500 650 kHz

K1 Pull Down Resistor RKN VDD=5V 40 — 100 kΩ

Rev 1.0 2012-4-13

13/15

ET6218R

(VDD=3V, GND=0V, Ta=25℃)

Parameter Symbol Test Condition Min. Typ. Max. Unit

VO= VDD -2V,SG1~SG7,

High-Level Output Current IOHSG1 -15 -20 -35 mA

SG14

Low-Level Output Current IOLGR VO=0.3V,GR1~GR5, 100 140 — mA

Low-Level Output Current IOLDOUT VO=0.4V 4 — — mA

Segment High-Level VO= VDD -3V,SG1~SG7,

ITOLSG — — +5 %

Output Current Tolerance SG14

0.8

High-Level Input Voltage VIH — — 3.3 V

VDD

0.3VD

Low-Level Input Voltage VIL — 0 — V

D

Oscillation Frequency fosc 300 420 580 kHz

K1 Pull Down Resistor RKN VDD =3V 40 — 100 kΩ

Application Circuit

Rev 1.0 2012-4-13

14/15

ET6218R

COMMON CATHODE TYPE LED PANEL

Note :

1. The capacitor(0.1µF)connected between the GND and VDD pins must be located as close as possible to the

ET6218R chip.

Package Dimension

DIP 18

2.54TYP

3.10~3.50

0.51min

3.00min

A A

1.524TYP 7.62TYP

10°max

SECTION A-A

K With Plating

K1

22.70~23.10 Base Metal

J1 J

Dim Min Max

6.30~6.70 J 0.219 0.339

J1 0.219 0.289

K 0.46 0.56

K1 0.46 0.51

Unit:mm

Rev 1.0 2012-4-13

15/15

S-ar putea să vă placă și

- Exploring Arduino: Tools and Techniques for Engineering WizardryDe la EverandExploring Arduino: Tools and Techniques for Engineering WizardryEvaluare: 4.5 din 5 stele4.5/5 (5)

- Digital LED Thermometer with Microcontroller AVR ATtiny13De la EverandDigital LED Thermometer with Microcontroller AVR ATtiny13Evaluare: 5 din 5 stele5/5 (1)

- Att.1 QT1-L-G-020-05-00003, KKS Numbering SystemDocument85 paginiAtt.1 QT1-L-G-020-05-00003, KKS Numbering SystemDoan Ngoc DucÎncă nu există evaluări

- Worksheet 13 PDFDocument4 paginiWorksheet 13 PDFVijay Bhaskar50% (2)

- RS-232 Connection & Operation for Sodick ControlsDocument17 paginiRS-232 Connection & Operation for Sodick ControlsRodrigo Lopez CelisÎncă nu există evaluări

- Datasheet 3L2Document6 paginiDatasheet 3L2juan carlos diaz cardozoÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pagini7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonÎncă nu există evaluări

- Description Features: PT6964 LED Driver ICDocument15 paginiDescription Features: PT6964 LED Driver ICDhivya NÎncă nu există evaluări

- Description Features: PT6961 LED Driver ICDocument18 paginiDescription Features: PT6961 LED Driver ICDhivya NÎncă nu există evaluări

- Description Features: PT6311 VFD Driver/Controller ICDocument22 paginiDescription Features: PT6311 VFD Driver/Controller ICMaciek KuśnierzÎncă nu există evaluări

- PT6311 10Document21 paginiPT6311 10RyanÎncă nu există evaluări

- Pt6315 en PDFDocument26 paginiPt6315 en PDFEnéas BaroneÎncă nu există evaluări

- TM1651 V1.1 enDocument12 paginiTM1651 V1.1 enPriyanka ShanmugamÎncă nu există evaluări

- MC2101 TM1628 PDFDocument22 paginiMC2101 TM1628 PDFPol ErnÎncă nu există evaluări

- Description: Technical DataDocument17 paginiDescription: Technical DataDhivya NÎncă nu există evaluări

- Control LED Drive Circuit: FeaturesDocument14 paginiControl LED Drive Circuit: FeaturesJacksonVelozÎncă nu există evaluări

- LCD 128x64 Tech12864GDocument10 paginiLCD 128x64 Tech12864GMarlon PerinÎncă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pagini7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareÎncă nu există evaluări

- Key Less Doorlock System by Using AudrinoDocument26 paginiKey Less Doorlock System by Using AudrinoyogeshÎncă nu există evaluări

- Description Features: PT6967 LED Driver ICDocument22 paginiDescription Features: PT6967 LED Driver ICDhivya NÎncă nu există evaluări

- s29190 DatasheetDocument44 paginis29190 Datasheetsamsularief03Încă nu există evaluări

- V2.2-En SDI1606 8 Segment & 7 Grid LED Driver With Boost - Jan15 - 18 (XHF)Document16 paginiV2.2-En SDI1606 8 Segment & 7 Grid LED Driver With Boost - Jan15 - 18 (XHF)AnkitShingalaÎncă nu există evaluări

- 2.13inch E-Paper DatasheetDocument26 pagini2.13inch E-Paper Datasheetvjspd hppÎncă nu există evaluări

- TM1628 LED driver chip overviewDocument14 paginiTM1628 LED driver chip overviewIstván FeketeÎncă nu există evaluări

- S-93C46B/56B/66B: Cmos Serial E PromDocument45 paginiS-93C46B/56B/66B: Cmos Serial E PromBruno Garido PerezÎncă nu există evaluări

- Temp Indicator Use AT89C51Document11 paginiTemp Indicator Use AT89C51sumit_saÎncă nu există evaluări

- Nec Ir ProtocolDocument28 paginiNec Ir ProtocolDominic ChanÎncă nu există evaluări

- TM1638 enDocument18 paginiTM1638 enfotakis michaelÎncă nu există evaluări

- Description Features: PT2262 Remote Control EncoderDocument14 paginiDescription Features: PT2262 Remote Control Encoderzbhp zÎncă nu există evaluări

- M XyzsvyuDocument40 paginiM XyzsvyuHossein AskaripoorÎncă nu există evaluări

- PmodCMPS Manual HMC5883Document2 paginiPmodCMPS Manual HMC5883soros4Încă nu există evaluări

- Lab 2 - 7 Segment Display and Analog InputsDocument27 paginiLab 2 - 7 Segment Display and Analog Inputsroger david pimienta barrosÎncă nu există evaluări

- LCD Module 4x20 - 3.73mm Controller KS0073Document4 paginiLCD Module 4x20 - 3.73mm Controller KS0073Narinder Singh100% (2)

- Simple Digital Security System: Detailed DescriptionDocument6 paginiSimple Digital Security System: Detailed DescriptionSatyam TiwariÎncă nu există evaluări

- Experiment-3: Output Devices With NodemcuDocument45 paginiExperiment-3: Output Devices With NodemcubÎncă nu există evaluări

- Week 4 18bce118Document18 paginiWeek 4 18bce118CasinovaÎncă nu există evaluări

- DS1722 Digital Thermometer With SPI/3-Wire Interface: Features Pin AssignmentDocument13 paginiDS1722 Digital Thermometer With SPI/3-Wire Interface: Features Pin AssignmentAfzal ImamÎncă nu există evaluări

- 6-Bit Magnetic Angular Position Encoder With Serial InterfaceDocument11 pagini6-Bit Magnetic Angular Position Encoder With Serial InterfacePankaj D PatelÎncă nu există evaluări

- Infineon TLE6209R DS v03 02 enDocument30 paginiInfineon TLE6209R DS v03 02 enRoger SegoÎncă nu există evaluări

- PT6961Document18 paginiPT69618705211345Încă nu există evaluări

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pagini7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013Încă nu există evaluări

- LCD Module ManualDocument22 paginiLCD Module ManualAlexÎncă nu există evaluări

- Main Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDocument25 paginiMain Features: - Set-Top-Boxes - White Goods - Home Appliances - DVD Players and VcrsDhivya NÎncă nu există evaluări

- 0.96inch OLED User Manual: 1. Key ParametersDocument5 pagini0.96inch OLED User Manual: 1. Key Parameterswondi BETÎncă nu există evaluări

- I2 Sover USBDocument6 paginiI2 Sover USBGian Marco BoÎncă nu există evaluări

- Kt3170 Low Power DTMF Receiver: 18-DIP-300ADocument7 paginiKt3170 Low Power DTMF Receiver: 18-DIP-300AAhmedÎncă nu există evaluări

- Low Power Serial E2PROM with Wide Voltage RangeDocument42 paginiLow Power Serial E2PROM with Wide Voltage RangeCOZLÎncă nu există evaluări

- DatasheetDocument16 paginiDatasheetAndres GuerreroÎncă nu există evaluări

- Interfacing 16×2 LCD With 8051Document39 paginiInterfacing 16×2 LCD With 8051gunda manasaÎncă nu există evaluări

- 7 X 5 Video Matrix Switch TDA 6920: 1 1.1 FeaturesDocument21 pagini7 X 5 Video Matrix Switch TDA 6920: 1 1.1 FeaturesMPIMLACÎncă nu există evaluări

- Gdm0802bflytw 19063127781Document18 paginiGdm0802bflytw 19063127781aristonrafaelÎncă nu există evaluări

- Infineon Tle7230r Ds v03 04 enDocument15 paginiInfineon Tle7230r Ds v03 04 enياسين الطنفوريÎncă nu există evaluări

- Ym12864p-Dalian Good Display PDFDocument10 paginiYm12864p-Dalian Good Display PDFEvgeniyÎncă nu există evaluări

- Alphaforce W160 ACDC CH452A - DebuggingDocument24 paginiAlphaforce W160 ACDC CH452A - DebuggingkevinalleinÎncă nu există evaluări

- CH452A TranslatedDocument36 paginiCH452A TranslatedkevinalleinÎncă nu există evaluări

- DMG85480F050 01WTC-WTCZ01-WTCZ02 数据手册 (DataSheet)Document21 paginiDMG85480F050 01WTC-WTCZ01-WTCZ02 数据手册 (DataSheet)wramadhani65Încă nu există evaluări

- Interfacing The HC05 MCU To A Multichannel Digital-to-Analog Converter Using The MC68HC705C8A and The MC68HC705J1ADocument24 paginiInterfacing The HC05 MCU To A Multichannel Digital-to-Analog Converter Using The MC68HC705C8A and The MC68HC705J1AradaresÎncă nu există evaluări

- TLE7209 R InfineonDocument16 paginiTLE7209 R Infineonmobil benerÎncă nu există evaluări

- #1 Blink An LEDDocument23 pagini#1 Blink An LEDclaire cabatoÎncă nu există evaluări

- 3.6. E32 (400T20S) / E32 (868T20S) / E32 (915T20S) : Pin No. Pin Pin Direction ApplicationDocument1 pagină3.6. E32 (400T20S) / E32 (868T20S) / E32 (915T20S) : Pin No. Pin Pin Direction ApplicationSergey SevruginÎncă nu există evaluări

- FSC-1711VN PC PnPCPUmanualDocument11 paginiFSC-1711VN PC PnPCPUmanualJozef SlivkaÎncă nu există evaluări

- MR 198CVS Video Processor User Manual V1.0 20140505 PDFDocument120 paginiMR 198CVS Video Processor User Manual V1.0 20140505 PDFMauricio DiazÎncă nu există evaluări

- Chapter 8 State Space AnalysisDocument22 paginiChapter 8 State Space AnalysisAli AhmadÎncă nu există evaluări

- RISHMaster 3410 - Digital Multifunctional InstrumentsDocument3 paginiRISHMaster 3410 - Digital Multifunctional InstrumentsAarif PatelÎncă nu există evaluări

- Singapore - Tech Spec For SRD - Short Range DevicesDocument13 paginiSingapore - Tech Spec For SRD - Short Range DevicesneversubmittalÎncă nu există evaluări

- High-Power N-Channel MOSFET TransistorDocument2 paginiHigh-Power N-Channel MOSFET TransistorSaito OtiasÎncă nu există evaluări

- LAPORAN PRAKTIKUM ELEKTRONIKA DASAR 1Document25 paginiLAPORAN PRAKTIKUM ELEKTRONIKA DASAR 1assaÎncă nu există evaluări

- Mps1000 ManualDocument46 paginiMps1000 ManualAnne NicoletaÎncă nu există evaluări

- Technical Data: STS Model DesignationDocument1 paginăTechnical Data: STS Model DesignationGilbert Laurent Atmadja100% (1)

- User Manual Readwell Touch Elisa Plate Analyser Ve - 5ac1cece1723dd45806d81faDocument84 paginiUser Manual Readwell Touch Elisa Plate Analyser Ve - 5ac1cece1723dd45806d81faCarlos ReisÎncă nu există evaluări

- Fitting Instructions: Part No. 29240521RC SuzukiDocument11 paginiFitting Instructions: Part No. 29240521RC SuzukiJohn DoeÎncă nu există evaluări

- Digital Logic Design Course Objectives and UnitsDocument2 paginiDigital Logic Design Course Objectives and UnitsRameshchandra K ECEÎncă nu există evaluări

- Atomic Structure - DPP-02 II NEET Ultimate CC 2023Document4 paginiAtomic Structure - DPP-02 II NEET Ultimate CC 2023vijaylakshmi0727Încă nu există evaluări

- Lesson 6 Connection of Field WindingDocument26 paginiLesson 6 Connection of Field WindingGleden Umayam33% (3)

- 32N50C3 Mos PDFDocument11 pagini32N50C3 Mos PDFHưng HQÎncă nu există evaluări

- ADAM-6000 User Manaul Ed 9Document252 paginiADAM-6000 User Manaul Ed 9fernandoviolante8551Încă nu există evaluări

- Conventional FireDocument5 paginiConventional FiremohammadÎncă nu există evaluări

- DataSheet SRM50-HFA0-K21 1037071 enDocument6 paginiDataSheet SRM50-HFA0-K21 1037071 entrinoÎncă nu există evaluări

- Design of A Seamless Gateway For Mechatrolink : Abstract-Recently, The Real-Time Ethernet Based Protocol HasDocument6 paginiDesign of A Seamless Gateway For Mechatrolink : Abstract-Recently, The Real-Time Ethernet Based Protocol Hasvinhpo51290Încă nu există evaluări

- Properties Of Nλ/2 LinesDocument12 paginiProperties Of Nλ/2 LinesJunar JohnÎncă nu există evaluări

- Seminar ReportDocument21 paginiSeminar ReportRavikumar ParagondÎncă nu există evaluări

- Yta310 & Yta320 YokogawaDocument8 paginiYta310 & Yta320 Yokogawahenryhariyadi100% (1)

- Design and Techno-Economical Optimization For Hybrid PV-wind System Under Various Meteorological ConditionsDocument20 paginiDesign and Techno-Economical Optimization For Hybrid PV-wind System Under Various Meteorological Conditionsjun005Încă nu există evaluări

- OLED Specification SheetDocument27 paginiOLED Specification SheetBianca SandorÎncă nu există evaluări

- Cell-Mobile Phone Repair Technician - 2071 - L-2 - PDFDocument159 paginiCell-Mobile Phone Repair Technician - 2071 - L-2 - PDFManish Meena0% (1)

- Question Bank Me2401Document13 paginiQuestion Bank Me2401Anonymous p8bHAAxÎncă nu există evaluări

- E740163 KX3 Owner's Man Rev C5Document58 paginiE740163 KX3 Owner's Man Rev C5Stephen FergusonÎncă nu există evaluări