Documente Academic

Documente Profesional

Documente Cultură

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos Eeprom

Încărcat de

Pablo Diego Cecere CasadoTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos Eeprom

Încărcat de

Pablo Diego Cecere CasadoDrepturi de autor:

Formate disponibile

IS24C01 IS24C02

IS24C04 IS24C08 IS24C16 ISSI ®

1K-bit/2K-bit/4K-bit/8K-bit/16K-bit

2-WIRE SERIAL CMOS EEPROM APRIL 2002

FEATURES DESCRIPTION

• Low Power CMOS Technology

–Standby Current less than 8 µA (5.5V) The IS24CXX (refers to IS24C01, IS24C02, IS24C04,

–Read Current (typical) less than 1 mA (5.5V) IS24C08, IS24C16) family is a low-cost and low voltage 2-

–Write Current (typical) less than 3 mA (5.5V) wire Serial EEPROM. It is fabricated using ISSI’s advanced

CMOS EEPROM technology and provides a low power and

• Flexible Voltage Operation low voltage operation. The IS24CXX family features a write

–Vcc = 1.8V to 5.5V for –2 version protection feature, and is available in 8-pin DIP and 8-pin

–Vcc = 2.5V to 5.5V for –3 version SOIC packages.

• 400 KHz (I2C Protocol) Compatibility The IS24C01 is a 1K-bit EEPROM; IS24C02 is a 2K-bit

• Hardware Data Protection EEPROM; IS24C04 is a 4K-bit EEPROM; IS24C08 is a 8K-

–Write Protect Pin bit EEPROM; IS24C16 is a 16K-bit EEPROM.

• Sequential Read Feature The IS24C01 and IS24C02 are available in 8-pin MSOP

• Filtered Inputs for Noise Suppression package. The IS24C01, IS24C02, IS24C04, and IS24C08

are available in 8-Pin TSSOP package.

• 8-pin PDIP and 8-pin SOIC packages

• 8-pin TSSOP (1K,2K, 4K & 8K only)

• 8-pin MSOP (1K,2K only) Automotive data is preliminary.

• Self time write cycle with auto clear

5 ms @ 2.5V

• Organization:

–IS24C01 128x8 (one block of 128 bytes)

–IS24C02 256x8 (one block of 256 bytes)

–IS24C04 512x8 (two blocks of 256 bytes)

–IS24C08 1024x8 (four blocks of 256 bytes)

–IS24C16 2048x8 (eight blocks of 256 bytes)

• Page Write Buffer

• Two-Wire Serial Interface

–Bi-directional data transfer protocol

• High Reliability

–Endurance: 1,000,000 Cycles

–Data Retention: 100 Years

• Commercial, Industrial and Automotive tempera-

ture ranges

Copyright © 2002 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time

without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to

obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 1

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

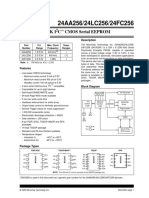

FUNCTIONAL BLOCK DIAGRAM

HIGH VOLTAGE

Vcc 8 GENERATOR,

TIMING & CONTROL

SDA 5

SCL 6 CONTROL

DECODER

WP 7 LOGIC

X

EEPROM

SLAVE ADDRESS ARRAY

REGISTER &

COMPARATOR

WORD ADDRESS

COUNTER Y

DECODER

ACK Clock

GND 4

DI/O

> DATA

REGISTER

nMOS

2 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

PIN CONFIGURATION

8-Pin DIP and SOIC

8 Pin TSSOP (1K, 2K, 4K and 8K)

8-Pin MSOP (1K, 2K)

A0 1 8 VCC

A1 2 7 WP

A2 3 6 SCL

GND 4 5 SDA

PIN DESCRIPTIONS

The IS24C04 uses A1 and A2 pins for hardwire addressing and

A0-A2 Address Inputs a total of four devices may be addressed on a single bus system.

The A0 pin is not used by IS24C04. This pin can be left floating

SDA Serial Address/Data I/O

or tied to GND or Vcc.

SCL Serial Clock Input

The IS24C08 only use A2 input for hardwire addressing and a

WP Write Protect Input total of two devices may be addressed on a single bus system.

Vcc Power Supply The A0 and A1 pins are not used by IS24C08. They may be left

floating or tied to either GND or Vcc.

GND Ground

These pins are not used by IS24C16. A0 and A1 may be left

floating or tied to either GND or Vcc. A2 should be tied to either

SCL GND or Vcc.

This input clock pin is used to synchronize the data

transfer to and from the device. WP

WP is the Write Protect pin. On the 24C01, 24C02, IS24C04

SDA and 24C08, if the WP pin is tied to VCC the entire array

The SDA is a Bi-directional pin used to transfer addresses and data becomes Write Protected (Read only). On the 24C16, if the

into and out of the device. The SDA pin is an open drain output and WP pin is tied to Vcc the upper half array becomes Write

can be wire-Ored with other open drain or open collector outputs. Protected (Read only). When WP is tied to GND or left

The SDA bus requires a pullup resistor to Vcc. floating normal read/write operations are allowed to the

A0, A1, A2 device.

The A0, A1 and A2 are the device address inputs. The IS24C01 and

IS24C02 use the A0, A1, and A2 for hardware addressing and a

total of 8 devices may be used on a single bus system.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 3

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

DEVICE OPERATION

The IS24CXX family features a serial communication and For the IS24C04 out of the next three bytes, B0 is for

supports a bi-directional 2-wire bus transmission protocol. Memory Page Addressing (the IS24C04 is organized as two

blocks of 256 bytes) and A2 and A1 bytes are used as

2-WIRE BUS

device address bytes and must compare to its hard-wire

The two-wire bus is defined as a Serial Data line(SDA), and

inputs pins (A2 and A1). Up to four IS24C04's may be

a Serial Clock Line (SCL). The protocol defines any device

individually addressed by the system. The page addressing

that sends data onto the SDA bus as a transmitter, and the

bytes for IS24Cxx should be considered the most significant

receiving devices as a receiver. The bus is controlled by

bytes of the data word address which follows.

MASTER device which generates the SCL, controls the bus

access and generates the STOP and START conditions. For the IS24C08 out of the next three bytes, B1 and B0 are

The IS24CXX is the SLAVE device on the bus. for memory page addressing (the IS24C08 is organized as

four blocks of 256 bytes) and the A2 bit is used as device

THE BUS PROTOCOL:

address bit and must compare to its hard-wired input pin

-- Data transfer may be initiated only when the bus is not

(A2). Up to two IS24C08 may be individually addressed by

busy

the system. The page addressing bytes for IS24CXX

-- During a data transfer, the data line must remain stable should be considered the most significant bytes of the data

whenever the clock line is high. Any changes in the data word address which follows.

line while the clock line is high will be interpreted as a

START or STOP condition. For the IS24C01 and IS24C02, the A0, A1, and A2 are used

as device address bytes and must compare to its hard-

The state of the data line represents valid data when after wired input pins (A0, A1, and A2) Up to Eight IS24C01 and/

a START condition, the data line is stable for the duration or IS24C02's may be individually addressed by the system.

of the HIGH period of the clock signal. The data on the line

The last bit of the slave address specifies whether a Read

must be changed during the LOW period of the clock signal.

or Write operation is to be performed. When this bit is set

There is one clock pulse per bit of data. Each data transfer

to 1, a Read operation is selected, and when set to 0, a Write

is initiated with a START condition and terminated with a

operation is selected.

STOP condition.

After the MASTER sends a START condition and the

START CONDITION

SLAVE address byte, the IS24CXX monitors the bus and

The START condition precedes all commands to the

responds with an Acknowledge (on the SDA line) when its

devices and is defined as a HIGH to LOW transition of SDA

address matches the transmitted slave address. The

when SCL is HIGH. The IS24CXX monitors the SDA and

IS24CXX pulls down the SDA line during the ninth clock

SCL lines and will not respond until the START condition is

cycle, signaling that it received the eight bytes of data. The

met.

IS24CXX then performs a Read or Write operation depending

STOP CONDITION on the state of the R/W bit.

The STOP condition is defined as a LOW to HIGH transition

of SDA when SCL is HIGH. All operations must end with a WRITE OPERATION

STOP condition. BYTE WRITE

In the Byte Write mode, the Master device sends the

ACKNOWLEDGE

START condition and the slave address information(with

After a successful data transfer, each receiving device is

the R/W set to Zero) to the Slave device. After the Slave

required to generate an acknowledge. The Acknowledging

generates an acknowledge, the Master sends the byte

device pulls down the SDA line.

address that is to be written into the address pointer of the

DEVICE ADDRESSING IS24CXX. After receiving another acknowledge from the

The MASTER begins a transmission by sending a START Slave, the Master device transmits the data byte to be

condition. The MASTER then sends the address of the written into the address memory location. The IS24CXX

particular slave devices it is requesting. The SLAVE acknowledges once more and the Master generates the

address is 8 bytes. STOP condition, at which time the device begins its internal

The four most significant bytes of the address are fixed as programming cycle. While this internal cycle is in progress,

1010 for the IS24CXX. the device will not respond to any request from the Master

device.

For the IS24C16, the bytes(B2, B1 and B0) are used for

memory page addressing (the IS24C16 is organized as

eight blocks of 256 bytes).

4 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

PAGE WRITE

The IS24CXX is capable of page-WRITE (8-byte for 24C01/ condition and the IS24CXX discontinues transmission. If

02 and 16-byte for 24C04/08/16) operation. A page-WRITE 'n' is the last byte of the memory, then the data from location

is initiated in the same manner as a byte write, but instead '0' will be transmitted. (Refer to Current Address Read

of terminating the internal write cycle after the first data word Diagram.)

is transferred, the master device can transmit up to N more

RANDOM ADDRESS READ

bytes (N=7 for 24C01/02 and N=15 for 24C04/08/16). After

Selective READ operations allow the Master device to

the receipt of each data word, the IS24CXX responds

select at random any memory location for a READ operation.

immediately with an ACKnowledge on SDA line, and the

The Master device first performs a 'dummy' write operation

three lower (24C01/24C02) or four lower (24C04/24C08/

by sending the START condition, slave address and word

24C16) order data word address bits are internally

address of the location it wishes to read. After the IS24CXX

incremented by one, while the higher order bits of the data

acknowledge the word address, the Master device resends

word address remain constant. If the master device should

the START condition and the slave address, this time with

transmit more than N+1 (N=7 for 24C01/02 and N=15 for

the R/W bit set to one. The IS24CXX then responds with its

24C04/08/16) words, prior to issuing the STOP condition,

acknowledge and sends the data requested. The master

the address counter will “roll over,” and the previously

device does not send an acknowledge but will generate a

written data will be overwritten. Once all N+1 (N=7 for

STOP condition. (Refer to Random Address Read Diagram.)

24C01/02 and N=15 for 24C04/08/16) bytes are received

and the STOP condition has been sent by the Master, the SEQUENTIAL READ

internal programming cycle begins. At this point, all received Sequential Reads can be initiated as either a Current

data is written to the IS24CXX in a single write cycle. All Address Read or Random Address Read. After the IS24CXX

inputs are disabled until completion of the internal WRITE sends initial byte sequence, the master device now responds

cycle. with an ACKnowledge indicating it requires additional data

ACKNOWLEDGE POLLING from the IS24CXX. The IS24CXX continues to output data

The disabling of the inputs can be used to take advantage for each ACKnowledge received. The master device

of the typical write cycle time. Once the stop condition is terminates the sequential READ operation by pulling SDA

issued to indicate the end of the host's write operation, the HIGH (no ACKnowledge) indicating the last data word to be

IS24CXX initiates the internal write cycle. ACK polling can read, followed by a STOP condition.

be initiated immediately. This involves issuing the start The data output is sequential, with the data from

condition followed by the slave address for a write operation. address n followed by the data from address n+1, ... etc.

If the IS24CXX is still busy with the write operation, no ACK The address counter increments by one automatically,

will be returned. If the IS24CXX has completed the write allowing the entire memory contents to be serially read

operation, an ACK will be returned and the host can then during sequential read operation. When the memory address

proceed with the next read or write operation. boundary (127 for IS24C01; 255 for IS24C02; 511 for

IS24C04; 1023 for IS24C08; 2047 for IS24C16) is reached,

READ OPERATION the address counter “rolls over” to address 0, and the

READ operations are initiated in the same manner as IS24CXX continues to output data for each ACKnowledge

WRITE operations, except that the read/write bit of the received. (Refer to Sequential Read Operation Starting with

slave address is set to “1”. There are three READ operation a Random Address READ Diagram.)

options: current address read, random address read and

sequential read.

CURRENT ADDRESS READ

The IS24CXX contains an internal address counter which

maintains the address of the last byte accessed, incremented

by one. For example, if the previous operation is either a

read or write operation addressed to the address location n,

the internal address counter would increment to address

location n+1. When the IS24CXX receives the Device

Addressing Byte with a READ operation (read/write bit set

to “1”), it will respond an ACKnowledge and transmit the 8-

bit data word stored at address location n+1. The master will

not acknowledge the transfer but does generate a STOP

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 5

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

TYPICAL SYSTEM BUS CONFIGURATION

Vcc

SDA

SCL

Master

Transmitter/ IS24Cxx

Receiver

OUTPUT ACKNOWLEDGE

SCL from

Master 1 8 9

Data Output

from

Transmitter

tAA tAA

Data Output

from ACK

Receiver

START AND STOP CONDITIONS

Condition

SCL

Condition

START

STOP

SDA

6 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

DATA VALIDITY PROTOCOL

Data Change

SCL

Data Stable Data Stable

SDA

SLAVE ADDRESS

BIT 7 6 5 4 3 2 1 0

IS24C01

1 0 1 0 A2 A1 A0 R/W

IS24C02

BIT 7 6 5 4 3 2 1 0

1 0 1 0 A2 A1 B0 R/W IS24C04

BIT 7 6 5 4 3 2 1 0

1 0 1 0 A2 B1 B0 R/W IS24C08

BIT 7 6 5 4 3 2 1 0

1 0 1 0 B2 B1 B0 R/W IS24C16

MSB LSB

BYTE WRITE

S W

T R S

A I T

R Device T O

T Address E Word Address Data P

SDA A A A

Bus C C C

Activity K K K

M L M

S S S

B B B

R/W

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 7

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

PAGE WRITE

S W

T R S

A I T

R Device T O

T Address E Word Address (n) Data (n) Data (n+1) Data (n+P*) P

SDA A A A A A

Bus C C C C C

Activity K K K K K

M L

S S

B B * P = 7 for IS24C01 and IS24C02

R/W P = 15 for IS24C04, IS24C08 and IS24C16

CURRENT ADDRESS READ

S

T R S

A E T

R Device A O

T Address D Data P

SDA A

Bus C

Activity K

M L N

S S O

B B

A

R/W C

K

RANDOM ADDRESS READ

S W S

T R T R S

A I A E T

R Device T Word Device A O

Address R Address

T E Address (n) T D Data n P

SDA A A A

Bus C C C

Activity K K K

M L N

S S O

B B

A

R/W C

K

DUMMY WRITE

8 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

SEQUENTIAL READ

R

E S

Device A T

O

Address D Data Byte n Data Byte n+1 Data Byte n+2 Data Byte n+X P

SDA A A A A

Bus C C C C

Activity K K K K

N

O

R/W A

C

K

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 9

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

ABSOLUTE MAXIMUM RATINGS(1)

Symbol Parameter Value Unit

VS Supply Voltage 0.5 to +6.25 V

VP Voltage on Any Pin –0.5 to Vcc + 0.5 V

TBIAS Temperature Under Bias –40 to +85 °C

TSTG Storage Temperature –65 to +150 °C

IOUT Output Current 5 mA

Notes:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

OPERATING RANGE

(IS24C01-2, IS24C02-2, IS24C04-2 IS24C08-2, & IS24C16-2)

Range Ambient Temperature VCC

Commercial 0°C to +70°C 1.8V to 5.5V

Industrial –40°C to +85°C 1.8V to 5.5V

OPERATING RANGE

(IS24C01-3, IS24C02-3, IS24C04-3, IS24C08-3, & IS24C16-3)

Range Ambient Temperature VCC

Commercial 0°C to +70°C 2.5V to 5.5V

Industrial –40°C to +85°C 2.5V to 5.5V

Automotive –40°C to +125°C 2.7V to 5.5V

Note: Automotive data is preliminary.

OPERATING RANGE

(IS24C01-5, IS24C02-5, IS24C04-5 IS24C08-5, & IS24C16-5)

Range Ambient Temperature VCC

Auromotive –40°C to +125°C 4.5V to 5.5V

Note: Automotive data is preliminary.

10 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

DC ELECTRICAL CHARACTERISTICS

Symbol Parameter Test Conditions Min. Max. Unit

VOL1 Output LOW Voltage VCC = 1.8V, IOL = 0.15 mA — 0.2 V

VOL2 Output LOW Voltage VCC = 2.5V, IOL = 1.0 mA — 0.4 V

VIH Input HIGH Voltage VCC X 0.7 VCC + 0.5 V

VIL Input LOW Voltage –1.0 VCC X 0.3 V

ILI Input Leakage Current VIN = VCC max. — 3 µA

ILO Output Leakage Current — 3 µA

Notes: VIL min and VIH max are reference only and are not tested.

POWER SUPPLY CHARACTERISTICS

Symbol Parameter Test Conditions Min. Max. Unit

ICC1 Vcc Operating Current READ at 100 KHz (Vcc = 5V) — 1.0 mA

ICC2 Vcc Operating Current WRITE at 100 KHz (Vcc = 5V) — 3.0 mA

ISB1 Standby Current Vcc = 1.8V — 4.0 µA

ISB2 Standby Current Vcc = 5.5V — 8.0 µA

CAPACITANCE(1,2)

Symbol Parameter Conditions Max. Unit

CIN Input Capacitance VIN = 0V 6 pF

COUT Output Capacitance VOUT = 0V 8 pF

Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions: TA = 25°C, f = 1 MHz, Vcc = 5.0V.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 11

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

AC ELECTRICAL CHARACTERISTICS (Over Operating Rnage)

Commercial (TA = 0°C to +70°C) Industrial (TA = –40°C to +85°C)

1.8V-5.5V 2.5V-5.5V

Symbol Parameter Test Conditions Min. Max. Min. Max. Unit

fSCL SCL Clock Frequency 0 100 0 400 KHz

T Noise Suppression Time(1) — 100 — 50 ns

tLOW Clock LOW Period 4.7 — 1.2 — µs

tHIGH Clock HIGH Period 4 — 0.6 — µs

tBUF Bus Free Time Before New Transmission(1) 4.7 — 1.2 — µs

tSU:STA Start Condition Setup Time 4.7 — 0.6 — µs

tSU:STO Stop Condition Setup Time 4.7 — 0.6 — µs

tHD:STA Start Condition Hold Time 4 — 0.6 — µs

tHD:STO Stop Condition Hold Time 4 — 0.6 — µs

tSU:DAT Data In Setup Time 200 — 100 — ns

tHD:DAT Data In Hold Time 0 — 0 — ns

tDH Data Out Hold Time SCL LOW to SDA Data Out Change 100 — 50 — ns

tAA Clock to Output SCL LOW to SDA Data Out Valid 0.1 4.5 0.1 0.9 µs

tR SCL and SDA Rise Time(1) — 1000 — 300 ns

tF SCL and SDA Fall Time(1) — 300 — 300 ns

tWR Write Cycle Time — 10 — 5 ms

Note:

1. This parameter is characterized but not 100% tested.

AC ELECTRICAL CHARACTERISTICS (Over Operating Range)

Automotive (TA = –40°C to +125°C)

2.7V-5.5V 4.5V-5.5V

Symbol Parameter Test Conditions Min. Max. Min. Max. Unit

fSCL SCL Clock Frequency 0 100 0 400 KHz

T Noise Suppression Time(1) — 100 — 50 ns

tLOW Clock LOW Period 4.7 — 1.2 — µs

tHIGH Clock HIGH Period 4 — 0.6 — µs

tBUF Bus Free Time Before New Transmission(1) 4.7 — 1.2 — µs

tSU:STA Start Condition Setup Time 4.7 — 0.6 — µs

tSU:STO Stop Condition Setup Time 4.7 — 0.6 — µs

tHD:STA Start Condition Hold Time 4 — 0.6 — µs

tHD:STO Stop Condition Hold Time 4 — 0.6 — µs

tSU:DAT Data In Setup Time 200 — 100 — ns

tHD:DAT Data In Hold Time 0 — 0 — ns

tDH Data Out Hold Time SCL LOW to SDA Data Out Change 100 — 50 — ns

tAA Clock to Output SCL LOW to SDA Data Out Valid 0.1 4.5 0.1 0.9 µs

tR SCL and SDA Rise Time(1) — 1000 — 300 ns

tF SCL and SDA Fall Time(1) — 300 — 300 ns

tWR Write Cycle Time — 10 — 10 ms

Note:

1. This parameter is characterized but not 100% tested.

2. Automotive data is preliminary.

12 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

AC WAVEFORMS

BUS TIMING

tR tF tHIGH tLOW tSU:STO

SCL

tSU:STA tHD:DAT tBUF

tHD:STA tSU:DAT

SDAIN

tAA tDH

SDAOUT

WRITE CYCLE TIMING

SCL

SDA 8th BIT ACK

WORD n tWR

STOP START

Condition Condition

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 13

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

ORDERING INFORMATION

Commercial Range: 0°C to +70°C

Voltage

Frequency Range Part Number Package

100 KHz 1.8V IS24C01-2P 300-mil Plastic DIP

to 5.5V IS24C01-2G Small Outline (JEDEC STD)

IS24C01-2S MSOP

IS24C01-2Z TSSOP

100 KHz 1.8V IS24C02-2P 300-mil Plastic DIP

to 5.5V IS24C02-2G Small Outline (JEDEC STD)

IS24C02-2S MSOP

IS24C02-2Z TSSOP

100 KHz 1.8V IS24C04-2P 300-mil Plastic DIP

to 5.5V IS24C04-2G Small Outline (JEDEC STD)

IS24C04-2Z TSSOP

100 KHz 1.8V IS24C08-2P 300-mil Plastic DIP

to 5.5V IS24C08-2G Small Outline (JEDEC STD)

IS24C08-2Z TSSOP

100 KHz 1.8V IS24C16-2P 300-mil Plastic DIP

to 5.5V IS24C16-2G Small Outline (JEDEC STD)

400 KHz 2.5V IS24C01-3P 300-mil Plastic DIP

to 5.5V IS24C01-3G Small Outline (JEDEC STD)

IS24C01-3S MSOP

IS24C01-3Z TSSOP

400 KHz 2.5V IS24C02-3P 300-mil Plastic DIP

to 5.5V IS24C02-3G Small Outline (JEDEC STD)

IS24C02-3S MSOP

IS24C02-3Z TSSOP

400 KHz 2.5V IS24C04-3P 300-mil Plastic DIP

to 5.5V IS24C04-3G Small Outline (JEDEC STD)

IS24C04-3Z TSSOP

400 KHz 2.5V IS24C08-3P 300-mil Plastic DIP

to 5.5V IS24C08-3G Small Outline (JEDEC STD)

IS24C08-3Z TSSOP

400 KHz 2.5V IS24C16-3P 300-mil Plastic DIP

to 5.5V IS24C16-3G Small Outline (JEDEC STD)

14 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

ORDERING INFORMATION

Industrial Range: –40°C to +85°C

Voltage

Frequency Range Part Number Package

100 KHz 1.8V IS24C01-2PI 300-mil Plastic DIP

to 5.5V IS24C01-2GI Small Outline (JEDEC STD)

IS24C01-2SI MSOP

IS24C01-2ZI TSSOP

100 KHz 1.8V IS24C02-2PI 300-mil Plastic DIP

to 5.5V IS24C02-2GI Small Outline (JEDEC STD)

IS24C02-2SI MSOP

IS24C02-2ZI TSSOP

100 KHz 1.8V IS24C04-2PI 300-mil Plastic DIP

to 5.5V IS24C04-2GI Small Outline (JEDEC STD)

IS24C04-2ZI TSSOP

100 KHz 1.8V IS24C08-2PI 300-mil Plastic DIP

to 5.5V IS24C08-2GI Small Outline (JEDEC STD)

IS24C08-2ZI TSSOP

100 KHz 1.8V IS24C16-2PI 300-mil Plastic DIP

to 5.5V IS24C16-2GI Small Outline (JEDEC STD)

400 KHz 2.5V IS24C01-3PI 300-mil Plastic DIP

to 5.5V IS24C01-3GI Small Outline (JEDEC STD)

IS24C01-3SI MSOP

IS24C01-3ZI TSSOP

400 KHz 2.5V IS24C02-3PI 300-mil Plastic DIP

to 5.5V IS24C02-3GI Small Outline (JEDEC STD)

IS24C02-3SI MSOP

IS24C02-3ZI TSSOP

400 KHz 2.5V IS24C04-3PI 300-mil Plastic DIP

to 5.5V IS24C04-3GI Small Outline (JEDEC STD)

IS24C04-3ZI TSSOP

400 KHz 2.5V IS24C08-3PI 300-mil Plastic DIP

to 5.5V IS24C08-3GI Small Outline (JEDEC STD)

IS24C08-3ZI TSSOP

400 KHz 2.5V IS24C16-3PI 300-mil Plastic DIP

to 5.5V IS24C16-3GI Small Outline (JEDEC STD)

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 15

Rev. D

06/25/02

IS24C01 IS24C02 IS24C04 IS24C08 IS24C16 ISSI ®

ORDERING INFORMATION

Automotive Range: –40°C to +125°C

Voltage

Frequency Range Part Number Package

100 KHz 2.7V IS24C01-3PA 300-mil Plastic DIP

to 5.5V IS24C01-3GA Small Outline (JEDEC STD)

IS24C01-3SA MSOP

IS24C01-3ZA TSSOP

100 KHz 2.7V IS24C02-3PA 300-mil Plastic DIP

to 5.5V IS24C02-3GA Small Outline (JEDEC STD)

IS24C02-3SA MSOP

IS24C02-3ZA TSSOP

100 KHz 2.7V IS24C04-3PA 300-mil Plastic DIP

to 5.5V IS24C04-3GA Small Outline (JEDEC STD)

IS24C04-3ZA TSSOP

100 KHz 2.7V IS24C08-3PA 300-mil Plastic DIP

to 5.5V IS24C08-3GA Small Outline (JEDEC STD)

IS24C08-3ZA TSSOP

100 KHz 2.7V IS24C16-3PA 300-mil Plastic DIP

to 5.5V IS24C16-3GA Small Outline (JEDEC STD)

400 KHz 4.5V IS24C01-5PA 300-mil Plastic DIP

to 5.5V IS24C01-5GA Small Outline (JEDEC STD)

IS24C01-5SA MSOP

IS24C01-5ZA TSSOP

400 KHz 4.5V IS24C02-5PA 300-mil Plastic DIP

to 5.5V IS24C02-5GA Small Outline (JEDEC STD)

IS24C02-5SA MSOP

IS24C02-5ZA TSSOP

400 KHz 4.5V IS24C04-5PA 300-mil Plastic DIP

to 5.5V IS24C04-5GA Small Outline (JEDEC STD)

IS24C04-5ZA TSSOP

400 KHz 4.5V IS24C08-5PA 300-mil Plastic DIP

to 5.5V IS24C08-5GA Small Outline (JEDEC STD)

IS24C08-5ZA TSSOP

400 KHz 4.5V IS24C16-5PA 300-mil Plastic DIP

to 5.5V IS24C16-5GA Small Outline (JEDEC STD)

Note: Automotive data is preliminary.

16 Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

06/25/02

S-ar putea să vă placă și

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 paginiIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoÎncă nu există evaluări

- 24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMDocument12 pagini24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMmacepaÎncă nu există evaluări

- Datasheet PDFDocument26 paginiDatasheet PDFNicoli LourençoÎncă nu există evaluări

- 24LC08 PDFDocument30 pagini24LC08 PDFJaime BarrancoÎncă nu există evaluări

- 24AA08/24LC08B: 8KI C Serial EEPROMDocument30 pagini24AA08/24LC08B: 8KI C Serial EEPROMjoseÎncă nu există evaluări

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 paginiCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaÎncă nu există evaluări

- 24aa08 - 24lc08 Eeprom PDFDocument40 pagini24aa08 - 24lc08 Eeprom PDFEdgar DauzonÎncă nu există evaluări

- 8K/16K 5.0V I C Serial Eeproms: Features Package TypesDocument13 pagini8K/16K 5.0V I C Serial Eeproms: Features Package Typesarunan55Încă nu există evaluări

- Ic PDFDocument36 paginiIc PDFdharamÎncă nu există evaluări

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pagini24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezÎncă nu există evaluări

- At24c02a 04a 08aDocument16 paginiAt24c02a 04a 08aretno.endah ekowatiÎncă nu există evaluări

- 24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dDocument28 pagini24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dAbhishek BhattacharjeeÎncă nu există evaluări

- X24C04 4K 512 X 8 Bit: 3839 FHD F01Document19 paginiX24C04 4K 512 X 8 Bit: 3839 FHD F01Legna80Încă nu există evaluări

- EEPROM 24LC256 - Microchip PDFDocument28 paginiEEPROM 24LC256 - Microchip PDFValdir DerlannÎncă nu există evaluări

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pagini32K 5.0V I C Serial EEPROM: Features Package TypesChrono GtzÎncă nu există evaluări

- 24LC04B PDFDocument22 pagini24LC04B PDFEddy RosarioÎncă nu există evaluări

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument12 pagini24Lc04B/08B: 4K/8K 2.5V I C Serial Eepromsjiaxin zhangÎncă nu există evaluări

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 paginiAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevÎncă nu există evaluări

- 2-Wire Serial EEPROM: FeaturesDocument22 pagini2-Wire Serial EEPROM: FeaturesNikolay MikolkinÎncă nu există evaluări

- 24 LC 256Document38 pagini24 LC 256johnÎncă nu există evaluări

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 paginiTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64AmedÎncă nu există evaluări

- AT25080A, 160A, 320A, 640A Rev04Document23 paginiAT25080A, 160A, 320A, 640A Rev04Bobby HancockÎncă nu există evaluări

- Item 11 X24C16PDocument15 paginiItem 11 X24C16Pdifa20061168Încă nu există evaluări

- 24AA256/24LC256: 256K I C Cmos Serial EepromDocument12 pagini24AA256/24LC256: 256K I C Cmos Serial EepromWelleyÎncă nu există evaluări

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pagini24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezÎncă nu există evaluări

- I2c EEPROM 24xx256 DsDocument28 paginiI2c EEPROM 24xx256 DsRizwan AmirÎncă nu există evaluări

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pagini24AA02/24LC02B: 2KI C Serial EEPROMhanifÎncă nu există evaluări

- Two-Wire Serial Eeprom: FeaturesDocument19 paginiTwo-Wire Serial Eeprom: Featuresvladimir_p80Încă nu există evaluări

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pagini24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaÎncă nu există evaluări

- Write Protect Pin For Hardware Data ProtectionDocument16 paginiWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 paginiTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2Încă nu există evaluări

- 24C08 AtmelDocument19 pagini24C08 AtmelCarlos Daniel Nery de OliveiraÎncă nu există evaluări

- At24c08 PDFDocument23 paginiAt24c08 PDFVeronicaGonzalezÎncă nu există evaluări

- 2-Wire Serial EEPROM: FeaturesDocument19 pagini2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesÎncă nu există evaluări

- 25AA256/25LC256: 256K SPI Bus Serial EEPROMDocument32 pagini25AA256/25LC256: 256K SPI Bus Serial EEPROMmelquisedecÎncă nu există evaluări

- SST26VF064BDocument76 paginiSST26VF064Bmar_barudjÎncă nu există evaluări

- Datasheet 24c01 EepromDocument26 paginiDatasheet 24c01 EepromItalo Vasquez LeonÎncă nu există evaluări

- k24c02c K LineDocument20 paginik24c02c K LineTeman NgopiÎncă nu există evaluări

- Bus Serial EEPROMDocument12 paginiBus Serial EEPROMMatiasÎncă nu există evaluări

- 24C320-EP MicrochipTechnologyDocument12 pagini24C320-EP MicrochipTechnologyMateus CorrêaÎncă nu există evaluări

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pagini25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoÎncă nu există evaluări

- 24aa515, 24LC515, 24FC515Document20 pagini24aa515, 24LC515, 24FC515dorudÎncă nu există evaluări

- Atmel 752 24c08aDocument13 paginiAtmel 752 24c08aEngin UzunÎncă nu există evaluări

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pagini25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86Încă nu există evaluări

- 24l1026i Memoria EEPROM 1024kDocument28 pagini24l1026i Memoria EEPROM 1024kMarta_d_eÎncă nu există evaluări

- 24AA04/24LC04B/24FC04: 4KI C Serial EEPROMDocument45 pagini24AA04/24LC04B/24FC04: 4KI C Serial EEPROMDinu Racautanu MironÎncă nu există evaluări

- EEPROM 24C256 - Atmel PDFDocument20 paginiEEPROM 24C256 - Atmel PDFValdir DerlannÎncă nu există evaluări

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pagini25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийÎncă nu există evaluări

- 24AA256/24LC256/24FC256: 256K I C Serial EEPROMDocument42 pagini24AA256/24LC256/24FC256: 256K I C Serial EEPROMAbhishek BhattacharjeeÎncă nu există evaluări

- 24C32Document12 pagini24C32SilviuCocoloșÎncă nu există evaluări

- 24AA024 MicrochipTechnologyDocument22 pagini24AA024 MicrochipTechnologydasdracheÎncă nu există evaluări

- AT24C1024B - DatasheetDocument25 paginiAT24C1024B - DatasheetEngin UzunÎncă nu există evaluări

- 24lc512 DatasheetDocument27 pagini24lc512 DatasheetLeonardo QuevedoÎncă nu există evaluări

- 21073K PDFDocument24 pagini21073K PDFadfumegaÎncă nu există evaluări

- Two-Wire Serial EEPROM: FeaturesDocument28 paginiTwo-Wire Serial EEPROM: FeaturesThế TùngÎncă nu există evaluări

- CAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesDocument9 paginiCAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesTeyfik koyuncuÎncă nu există evaluări

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pagini32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86Încă nu există evaluări

- Mikroe 5623-3132216Document32 paginiMikroe 5623-3132216yajujotosÎncă nu există evaluări

- 8051 Microcontroller: An Applications Based IntroductionDe la Everand8051 Microcontroller: An Applications Based IntroductionEvaluare: 5 din 5 stele5/5 (6)

- Microprocessor System Design: A Practical IntroductionDe la EverandMicroprocessor System Design: A Practical IntroductionÎncă nu există evaluări

- 93C56 EepromDocument37 pagini93C56 EepromPablo Diego Cecere CasadoÎncă nu există evaluări

- Series/Parallel Equivalent Circuits in Excel: Summer CircuitscollectionDocument1 paginăSeries/Parallel Equivalent Circuits in Excel: Summer CircuitscollectionPablo Diego Cecere CasadoÎncă nu există evaluări

- Dual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LDocument4 paginiDual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LPablo Diego Cecere CasadoÎncă nu există evaluări

- Dual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LDocument4 paginiDual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LPablo Diego Cecere CasadoÎncă nu există evaluări

- 3400 9LDocument3 pagini3400 9LPablo Diego Cecere CasadoÎncă nu există evaluări

- Convert Mobile Charger To Audio AmplifierDocument7 paginiConvert Mobile Charger To Audio AmplifierPablo Diego Cecere CasadoÎncă nu există evaluări

- TQ2 9V PDFDocument7 paginiTQ2 9V PDFPablo Diego Cecere CasadoÎncă nu există evaluări

- ST 2SC828 / 828A: G S P Form A Is AvailableDocument2 paginiST 2SC828 / 828A: G S P Form A Is AvailablePablo Diego Cecere Casado100% (1)

- Dual Operational AmplifierDocument5 paginiDual Operational AmplifierPablo Diego Cecere CasadoÎncă nu există evaluări

- TVR07471Document43 paginiTVR07471Willians RodriguesÎncă nu există evaluări

- TO-251 Plastic-Encapsulate Transistors: Jiangsu Changjiang Electronics Technology Co., LTDDocument3 paginiTO-251 Plastic-Encapsulate Transistors: Jiangsu Changjiang Electronics Technology Co., LTDPablo Diego Cecere CasadoÎncă nu există evaluări

- 2N3903, 2N3904 General Purpose Transistors: NPN SiliconDocument7 pagini2N3903, 2N3904 General Purpose Transistors: NPN SiliconMiguelito Pa Q MasÎncă nu există evaluări

- 2-Wire Serial Eeprom: FeaturesDocument10 pagini2-Wire Serial Eeprom: FeaturesPablo Diego Cecere CasadoÎncă nu există evaluări

- TSP12N60M / TSF12N60M TSP12N60M / TSF12N60M: 600V N-Channel MOSFETDocument7 paginiTSP12N60M / TSF12N60M TSP12N60M / TSF12N60M: 600V N-Channel MOSFETPablo Diego Cecere CasadoÎncă nu există evaluări

- 2N3906 General Purpose Transistors: PNP SiliconDocument7 pagini2N3906 General Purpose Transistors: PNP SiliconJose G. Cantillo L.Încă nu există evaluări

- 7805 Datasheet FairchildDocument29 pagini7805 Datasheet FairchildsumitseghalÎncă nu există evaluări

- Ka78Xxe / Ka78Xxae 3-Terminal 1 A Positive Voltage RegulatorDocument28 paginiKa78Xxe / Ka78Xxae 3-Terminal 1 A Positive Voltage RegulatorPablo Diego Cecere CasadoÎncă nu există evaluări

- 3400 9LDocument3 pagini3400 9LPablo Diego Cecere CasadoÎncă nu există evaluări

- Voltage Regulators: TAITRON Components IncorporatedDocument1 paginăVoltage Regulators: TAITRON Components IncorporatedPablo Diego Cecere CasadoÎncă nu există evaluări

- KA358A Amplif Operacional PDFDocument14 paginiKA358A Amplif Operacional PDFPablo Diego Cecere CasadoÎncă nu există evaluări

- 2SD1701 Transistor SiliconaDocument2 pagini2SD1701 Transistor SiliconaPablo Diego Cecere CasadoÎncă nu există evaluări

- Dual Operational AmplifierDocument5 paginiDual Operational AmplifierPablo Diego Cecere CasadoÎncă nu există evaluări

- Dual Operational Amplifier: Features DescriptionsDocument10 paginiDual Operational Amplifier: Features DescriptionsPablo Diego Cecere CasadoÎncă nu există evaluări

- 93C56 EepromDocument37 pagini93C56 EepromPablo Diego Cecere CasadoÎncă nu există evaluări

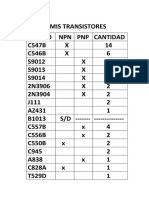

- TRANSISTORESDocument2 paginiTRANSISTORESPablo Diego Cecere CasadoÎncă nu există evaluări

- HT6P20X Series 2 OTP Encoder: FeaturesDocument13 paginiHT6P20X Series 2 OTP Encoder: FeaturesPablo Diego Cecere CasadoÎncă nu există evaluări

- Atlas Cable 4device PDFDocument52 paginiAtlas Cable 4device PDFPablo Diego Cecere CasadoÎncă nu există evaluări

- Datasheet PDFDocument8 paginiDatasheet PDFTuribio Almeida BarbosaÎncă nu există evaluări

- Brochure Shield PowerDocument2 paginiBrochure Shield PowerRizki Heru HermawanÎncă nu există evaluări

- Sumitomo Type 39Document2 paginiSumitomo Type 39Hans IgelerÎncă nu există evaluări

- AE1C Kit AmpliDocument109 paginiAE1C Kit AmpliJoseba LizarragaÎncă nu există evaluări

- SMPS Trainer Kit ComputersDocument1 paginăSMPS Trainer Kit ComputersChandrakant ChatterjeeÎncă nu există evaluări

- 07 k275 VaristorDocument27 pagini07 k275 VaristorJorge Ugaz La RosaÎncă nu există evaluări

- Process Control Concepts, Dynamics and Applications PDFDocument734 paginiProcess Control Concepts, Dynamics and Applications PDFAfzaalUmair71% (7)

- HV857 High Voltage EL Lamp Driver For Low Noise ApplicationsDocument14 paginiHV857 High Voltage EL Lamp Driver For Low Noise ApplicationsMaxim FalchenkoÎncă nu există evaluări

- Marshalling KioskDocument4 paginiMarshalling KioskThant Zin100% (1)

- Optical Encoder For Motion Control Through ArduinoDocument4 paginiOptical Encoder For Motion Control Through ArduinoMary LongÎncă nu există evaluări

- Application of Numerical Relays For HV Shunt Reactor ProtectionDocument5 paginiApplication of Numerical Relays For HV Shunt Reactor Protectionalex696Încă nu există evaluări

- Fei Yuan-CMOS Active Inductors and Transformers - Principle, Implementation, and Applications-Springer (2008)Document298 paginiFei Yuan-CMOS Active Inductors and Transformers - Principle, Implementation, and Applications-Springer (2008)PromachÎncă nu există evaluări

- AC Hipots 15-200kVDocument4 paginiAC Hipots 15-200kVHung NguyenÎncă nu există evaluări

- DatasheetDocument4 paginiDatasheetGrupo EpufmÎncă nu există evaluări

- 88° Panel Antenna: General SpecificationsDocument2 pagini88° Panel Antenna: General SpecificationsDuke QuaresmaÎncă nu există evaluări

- DX20VC: High-Efficiency, Communicating, Variable-Speed, Inverter Drive Split System Air Conditioner Up To 24.5 SEERDocument20 paginiDX20VC: High-Efficiency, Communicating, Variable-Speed, Inverter Drive Split System Air Conditioner Up To 24.5 SEERJohn AristaÎncă nu există evaluări

- CSS - Proper Use and Maintenance of ToolsDocument1 paginăCSS - Proper Use and Maintenance of ToolsRowell Marquina100% (1)

- CHAPTER VII Direct Current CircuitsDocument28 paginiCHAPTER VII Direct Current CircuitsNandya GuvitaÎncă nu există evaluări

- Da2011-35576-Ericsson Review Vol 58 1981 PDFDocument218 paginiDa2011-35576-Ericsson Review Vol 58 1981 PDFnubertus sautÎncă nu există evaluări

- Re NR 67370001Document7 paginiRe NR 67370001Mauro PerezÎncă nu există evaluări

- Free Space Radar: Product Selection Guide - Installation and ApplicationDocument2 paginiFree Space Radar: Product Selection Guide - Installation and ApplicationGabriela JimenezÎncă nu există evaluări

- Reference Letter TemplateDocument2 paginiReference Letter TemplateAnant Pratap Srivastava100% (3)

- Metal Cutting SourceDocument24 paginiMetal Cutting SourceSamÎncă nu există evaluări

- V 0130 GB Modulation Techniques - ModulatorsDocument266 paginiV 0130 GB Modulation Techniques - Modulatorsحسين حيدر آلوس عباسÎncă nu există evaluări

- Communication Interface Technology PDFDocument2 paginiCommunication Interface Technology PDFDariusÎncă nu există evaluări

- Expt 8 Act 3 and 5 & ApplicationsDocument5 paginiExpt 8 Act 3 and 5 & ApplicationsWÎncă nu există evaluări

- Lightolier Night Magic Landscape Lighting Brochure 1988Document34 paginiLightolier Night Magic Landscape Lighting Brochure 1988Alan MastersÎncă nu există evaluări

- Logic GateDocument12 paginiLogic Gateapi-254068557Încă nu există evaluări

- Protection Instrument TransformersDocument21 paginiProtection Instrument TransformersSyed Muzammil AliÎncă nu există evaluări

- Electrical Load List: Mohammed N.M. Al-Baddah & PartnerDocument12 paginiElectrical Load List: Mohammed N.M. Al-Baddah & PartnerJesÎncă nu există evaluări

- 873P Ultrasonic Sensors With Dual Discrete/Single Analog OutputsDocument4 pagini873P Ultrasonic Sensors With Dual Discrete/Single Analog Outputsmanduca matthewÎncă nu există evaluări