Documente Academic

Documente Profesional

Documente Cultură

Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015

Încărcat de

Sivanantham SadhasivamDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015

Încărcat de

Sivanantham SadhasivamDrepturi de autor:

Formate disponibile

ECE5015 DIGITAL IC DESIGN L T P J C

3 0 0 4 4

Pre-requisite Nil Version 1.0

Course Objective :

The course is aimed to

1. apply the models for state-of-the-art VLSI components, fabrication steps, hierarchical

design flow and semiconductor business economics to judge the manufacturability of a

design and assess its manufacturing costs.

2. focus on the systematic analysis and design of basic digital integrated circuits in CMOS

technology.

3. enhance problem solving and creative circuit design techniques.

4. emphasize on the layout design of various digital integrated circuits.

5. focus on the methodologies and design techniques related to digital integrated circuits.

Expected Course Outcome :

At the end of the course the student will be able to

1. Understand design metric and MOS physics

2. Design layout for various digital integrated circuits.

3. Design the CMOS inverter with optimized power, area and timing.

4. Design static and dynamic digital CMOS circuits.

5. Understand the timing concepts in latch and flip-flops.

6. Design CMOS memory arrays.

7. Understand interconnect and clocking issues.

Student Learning Outcomes (SLO): 5,6,14

5. Having design thinking capability.

6. Having an ability to design a component or a product applying all the relevant standards and

with realistic constraints.

14. Having an ability to design and conduct experiments, as well as to analyze and interpret data.

Module:1 Introduction: 3 hours

Issues in Digital IC Design- Quality Metrics of a Digital Design - MOS Transistor Theory.

Module:2 Fabrication Technologies: 7 hours

VLSI Manufacturing Process Steps - Crystal Growth - Wafer cleaning – Oxidation - Thermal

Diffusion - Ion Implantation – Lithography –Epitaxy – Metallization -Dry and Wet etching and

Packaging.

Fabrication of MOSFET with Metal Gate and Self-aligned Poly-Gate Processes with details on

CMOS Design Rules and Layouts, Fabrication of CMOS inverter with details on Design Rules

and Layouts.

Module:3 The CMOS Inverter: 5 hours

Static CMOS Inverter- Static and Dynamic Behavioural Practices of CMOS Inverter – Noise

Margin.

Components of Energy and Power – Switching -Short-Circuit and Leakage Components.

Technology scaling and its impact on the inverter metrics - Passive and Active Devices.

Module:4 Static & Dynamic CMOS Design: 8 hours

Complementary CMOS -Ratioed Logic (Pseudo NMOS, DCVSL) - Pass Transistor Logic -

Transmission gate logic - Dynamic Logic Design Considerations - Speed and Power Dissipation

of Dynamic logic -Signal integrity issues -Domino Logic.

Module:5 CMOS Sequential Logic Circuit Design: 5 hours

Introduction - Static Latches and Registers - Dynamic Latches and Registers - Pulse Based

Registers - Sense Amplifier based registers -Latch vs. Register based pipeline structures.

Module:6 Designing Memory & Array structures: 7 hours

SRAM and DRAM Memory Core - memory peripheral circuitry - Memory reliability and yield -

Power dissipation in memories.

Module:7 Interconnects and Timing Issues: 8 hours

Resistive, Capacitive and Inductive Parasitics - Computation of R, L and C for given inter-

connects - Buffer Chains - Timing classification of digital systems - Synchronous Design - Origins

of Clock Skew/Jitter and impact on Performance - Clock Distribution Techniques - Latch based

clocking - Synchronizers and Arbiters -Clock Synthesis and Synchronization using a Phase-

Locked Loop.

Module:8 Contemporary issues: 2 hours

Total Lecture hours: 45 hours

Text Book(s)

1. Jan M. Rabaey, AnanthaChadrakasan, BorivojeNikolic, Digital Integrated Circuits: A

Design Perspective, PHI, Second Edition, 2016.

2. Neil.H, E.Weste, David Harris, Ayan Banerjee, CMOS VLSI Design: A Circuit and

Systems Perspective, Pearson Education, Fourth Edition, 2011.

Reference Books

1. Sung-Mo Kang, Yusuf Leblebici, CMOS Digital Integrated Circuits - Analysis and

Design, McGraw-Hill, Fourth Edition, 2014.

2. Sorab K Gandhi, VLSI Fabrication Principles: Si and GaAs, John Wiley and Sons, Second

Edition, 2010.

Mode of Evaluation:Continuous Assessment Test –I (CAT-I) , Continuous Assessment Test –II

(CAT-II), Seminar / Challenging Assignments / Completion of MOOC / Innovative ideas leading

to solutions for industrial problems, Final Assessment Test (FAT).

List of Projects (Indicative)

1. Design and simulate a 16-bit comparator by using 8T full adders

2. Pass transistor logic based ALU design using low power full adder design

3. Design of high performance power efficient flip-flop using transmission gates

4. Design of high performance 5:32 decoder using 2:4,3:8 mixed logic line decoders.

5. Design of current comparator using FINFET

6. Analysis of leakage current and leakage power reduction during reduction in CMOS

SRAM cell

7. Design of encoder for a 5GS/S 5 bit flash ADC

8. Design a 65 nm reliable 6T CMOS SRAM cell with minimum size transistors

Mode of Evaluation:Review I, II and III

Approved by Academic Council No. 40 Date: 18.03.2016

S-ar putea să vă placă și

- BECE303LDocument3 paginiBECE303LKAVIYA DIASÎncă nu există evaluări

- VLSI System Design SyllabusDocument2 paginiVLSI System Design SyllabusGaneshChandraÎncă nu există evaluări

- ECE3002Document2 paginiECE3002Ritayan PatraÎncă nu există evaluări

- Proposed - BE E & TC 2019 - VLSI SyllabusDocument3 paginiProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeÎncă nu există evaluări

- VlsiDocument3 paginiVlsiMayank Karwa 16BEC0067Încă nu există evaluări

- Prerequisite:: VLSI Design (404201)Document2 paginiPrerequisite:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument122 paginiSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HÎncă nu există evaluări

- SoC SyllabusDocument2 paginiSoC SyllabuslokeshÎncă nu există evaluări

- Vit Ece 5th Year SyllabusDocument16 paginiVit Ece 5th Year Syllabuspranavateja12399Încă nu există evaluări

- Ece3002 Vlsi-system-Design Eth 1.2 49 Ece3002 41Document2 paginiEce3002 Vlsi-system-Design Eth 1.2 49 Ece3002 41SMÎncă nu există evaluări

- VLSI DesignDocument1 paginăVLSI Designडाँ सूर्यदेव चौधरीÎncă nu există evaluări

- Vlsi SyllabusDocument3 paginiVlsi SyllabusmadhurÎncă nu există evaluări

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 paginiNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: Text BooksDocument2 paginiPrerequisite: Course Objectives: Course Outcomes:: Text BooksSaurabhMoharirÎncă nu există evaluări

- SyllabusDocument1 paginăSyllabusRajalingam BossÎncă nu există evaluări

- Ece 2003Document3 paginiEce 2003gokulÎncă nu există evaluări

- Unit I: Introduction To VLSI Circuits 7LDocument2 paginiUnit I: Introduction To VLSI Circuits 7LSaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Ece2008 Vlsi System Design SyllabusDocument2 paginiEce2008 Vlsi System Design Syllabusyaswanth rÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes: Unit I: Introduction To VLSI Circuits 7LDocument2 paginiPrerequisite: Course Objectives: Course Outcomes: Unit I: Introduction To VLSI Circuits 7LSaurabhMoharirÎncă nu există evaluări

- EC8095 SyllabusDocument2 paginiEC8095 Syllabusjames RÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Curriculum: Revised Model Syllabus For Type II (Incorporating System Design Courses)Document23 paginiCurriculum: Revised Model Syllabus For Type II (Incorporating System Design Courses)learn it nowÎncă nu există evaluări

- Vlsi ch1Document64 paginiVlsi ch1Nihar ranjan AditÎncă nu există evaluări

- Eee4028 Vlsi-Design Eth 2.0 39 Eee4028Document3 paginiEee4028 Vlsi-Design Eth 2.0 39 Eee4028Abhishek RajÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Prerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)Document2 paginiPrerequisite: Course Objectives: Course Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- Course Outcomes:: VLSI Design (404201)Document2 paginiCourse Outcomes:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Document2 paginiEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaÎncă nu există evaluări

- Prerequisite:: VLSI Design (404201)Document2 paginiPrerequisite:: VLSI Design (404201)SaurabhMoharirÎncă nu există evaluări

- M.Tech 2nd SemesterDocument14 paginiM.Tech 2nd SemesterSivaramsharma RupavathamÎncă nu există evaluări

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 paginiFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04Încă nu există evaluări

- 21ec503 Vlsi Design Unit 1Document110 pagini21ec503 Vlsi Design Unit 1santhoshiniÎncă nu există evaluări

- SUMSEM2-2017-18 ECE5025 TH TT530A VL2017189000177 Reference Material I ECE5025 System-On-Chip-Design TH 1 AC40Document2 paginiSUMSEM2-2017-18 ECE5025 TH TT530A VL2017189000177 Reference Material I ECE5025 System-On-Chip-Design TH 1 AC40DarshilShahÎncă nu există evaluări

- 6th Sem SyllabusDocument13 pagini6th Sem SyllabusAbhishek GuptaÎncă nu există evaluări

- VLSI ModulesDocument28 paginiVLSI Modulessai_karthik89Încă nu există evaluări

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedDocument37 paginiVTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedAshik PadmanabhaÎncă nu există evaluări

- HDL Modeling and Design Flow: Symbiosis Institute of Technology SITDocument4 paginiHDL Modeling and Design Flow: Symbiosis Institute of Technology SITtarunr5191Încă nu există evaluări

- Revised Syllabus MicroelectronicsDocument19 paginiRevised Syllabus MicroelectronicsBaluvu JagadishÎncă nu există evaluări

- Vlsi DesignDocument3 paginiVlsi DesignGokulÎncă nu există evaluări

- Btech New SyllabusDocument8 paginiBtech New SyllabusDrBhoopal RaoÎncă nu există evaluări

- SyllabusDocument3 paginiSyllabusrishi tejuÎncă nu există evaluări

- CMOS VLSI and Aspect of ASIC DesignDocument3 paginiCMOS VLSI and Aspect of ASIC DesignBittU BhagatÎncă nu există evaluări

- Course Pre-Requisite: BE Electronics Engineering (R-2012)Document24 paginiCourse Pre-Requisite: BE Electronics Engineering (R-2012)Hannan SatopayÎncă nu există evaluări

- Vlsi NotesDocument5 paginiVlsi NotesDiwakar TiwaryÎncă nu există evaluări

- Analog and Digital ElectronicsDocument19 paginiAnalog and Digital ElectronicsRuthwik S GowdaÎncă nu există evaluări

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LDocument3 paginiFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichÎncă nu există evaluări

- Semester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Document19 paginiSemester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Sneha NargundkarÎncă nu există evaluări

- Analog VLSI Design: Technology TrendsDocument25 paginiAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajÎncă nu există evaluări

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsDe la EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsÎncă nu există evaluări

- VLSI Technology and DesignDocument2 paginiVLSI Technology and DesignJigar PatelÎncă nu există evaluări

- COAVITDocument3 paginiCOAVITnikshithÎncă nu există evaluări

- Bangalore Universty: University Visvesvaraya College of EngineeringDocument8 paginiBangalore Universty: University Visvesvaraya College of Engineeringsaurav bsÎncă nu există evaluări

- Modern Component Families and Circuit Block DesignDe la EverandModern Component Families and Circuit Block DesignEvaluare: 5 din 5 stele5/5 (1)

- On-Chip Communication Architectures: System on Chip InterconnectDe la EverandOn-Chip Communication Architectures: System on Chip InterconnectÎncă nu există evaluări

- Registration FormatDocument1 paginăRegistration FormatSivanantham SadhasivamÎncă nu există evaluări

- Vlsid2021 CFP V1 PDFDocument2 paginiVlsid2021 CFP V1 PDFSivanantham SadhasivamÎncă nu există evaluări

- CSIR JRF GuidelinesDocument13 paginiCSIR JRF GuidelinesSivanantham SadhasivamÎncă nu există evaluări

- Vlsid2021 CFP V1 PDFDocument2 paginiVlsid2021 CFP V1 PDFSivanantham SadhasivamÎncă nu există evaluări

- Semiconductor IndustryDocument2 paginiSemiconductor IndustrySivanantham SadhasivamÎncă nu există evaluări

- RC DFT GuideDocument58 paginiRC DFT GuideSivanantham Sadhasivam0% (1)

- Vlsi Qa2 PDFDocument19 paginiVlsi Qa2 PDFamiteshtripathiÎncă nu există evaluări

- Verilog Tutorial 1Document6 paginiVerilog Tutorial 1Sivanantham SadhasivamÎncă nu există evaluări

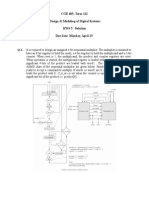

- COE 405, Term 122 Design & Modeling of Digital Systems HW# 5 Solution Due Date: Monday, April 15Document6 paginiCOE 405, Term 122 Design & Modeling of Digital Systems HW# 5 Solution Due Date: Monday, April 15Sivanantham SadhasivamÎncă nu există evaluări

- Hierarchical ModelingDocument23 paginiHierarchical ModelingSivanantham SadhasivamÎncă nu există evaluări

- QuestionDocument16 paginiQuestionSivanantham SadhasivamÎncă nu există evaluări

- 4106 Revised Syllabus Spring08Document9 pagini4106 Revised Syllabus Spring08Sivanantham SadhasivamÎncă nu există evaluări

- v1Document5 paginiv1Sivanantham SadhasivamÎncă nu există evaluări

- Lecture 22Document41 paginiLecture 22Sivanantham SadhasivamÎncă nu există evaluări

- VLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueDocument11 paginiVLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueSivanantham SadhasivamÎncă nu există evaluări

- Verilog Lecture-Sequential LogicDocument41 paginiVerilog Lecture-Sequential LogicSivanantham SadhasivamÎncă nu există evaluări

- School of Electronics EngineeringDocument1 paginăSchool of Electronics EngineeringSivanantham SadhasivamÎncă nu există evaluări

- Keshab K Parhi Digital Signal Processing Architecture Chapter 3 SolutionDocument7 paginiKeshab K Parhi Digital Signal Processing Architecture Chapter 3 SolutionNESEGA29% (7)

- Silicon NPN Power Transistors: BD249/A/B/CDocument3 paginiSilicon NPN Power Transistors: BD249/A/B/CElton De Souza CouraÎncă nu există evaluări

- Pv507ba UnikcDocument8 paginiPv507ba UnikcDoddy PrasetyaÎncă nu există evaluări

- Transformable Junctionless Transistor (T-JLT)Document6 paginiTransformable Junctionless Transistor (T-JLT)Rakesh KumarÎncă nu există evaluări

- Data Sheet: NPN Power TransistorDocument8 paginiData Sheet: NPN Power Transistoryuni supriatinÎncă nu există evaluări

- Vlsi QP 1Document6 paginiVlsi QP 1Sailesh PosaniÎncă nu există evaluări

- TC5565Document9 paginiTC5565MiniLabÎncă nu există evaluări

- CH11 ThyristorsDocument86 paginiCH11 Thyristorsmiathegirl9Încă nu există evaluări

- Flash Memories: Detlev RichterDocument287 paginiFlash Memories: Detlev RichterdarÎncă nu există evaluări

- 7 NM Lithography Process - WikiChipDocument9 pagini7 NM Lithography Process - WikiChipKrisumraj PurkaitÎncă nu există evaluări

- ECE 027 - Module 3 - Introduction of Bipolar Junction Transistors (BJT)Document58 paginiECE 027 - Module 3 - Introduction of Bipolar Junction Transistors (BJT)Miyuki NakiriÎncă nu există evaluări

- History of Embedded Systems.Document2 paginiHistory of Embedded Systems.Eragon ShadeSlayerÎncă nu există evaluări

- History of IOTDocument1 paginăHistory of IOTDhiyaÎncă nu există evaluări

- NPN Diffused Type (Darlington Power) : Silicon TripleDocument3 paginiNPN Diffused Type (Darlington Power) : Silicon TriplePablo AllosiaÎncă nu există evaluări

- IGBT: Insulated-Gate Bipolar Transistor: - Combination BJT and MOSFETDocument15 paginiIGBT: Insulated-Gate Bipolar Transistor: - Combination BJT and MOSFETamit kumarÎncă nu există evaluări

- MOS Logic FamilyDocument35 paginiMOS Logic Familyvinayak mastaÎncă nu există evaluări

- ThyristorDocument7 paginiThyristorDraganJordanovÎncă nu există evaluări

- 08 Lecture Power Transistors (IGBT)Document22 pagini08 Lecture Power Transistors (IGBT)Abid Hasan HimelÎncă nu există evaluări

- Unisonic Technologies Co., LTD: 4.2A, 20V P-CHANNEL Power MosfetDocument4 paginiUnisonic Technologies Co., LTD: 4.2A, 20V P-CHANNEL Power MosfetMelissa Melissa100% (1)

- Transistors ProductsDocument2 paginiTransistors ProductsJose GuerreroÎncă nu există evaluări

- Mos Two Input Nor and Nand GateDocument12 paginiMos Two Input Nor and Nand GateSimran SÎncă nu există evaluări

- FormulaDocument4 paginiFormulamargaret_navaeiÎncă nu există evaluări

- MOS GATE Video SolutionDocument11 paginiMOS GATE Video SolutionGayatri BagadeÎncă nu există evaluări

- Peavey Semiconductor Cross Reference ListDocument24 paginiPeavey Semiconductor Cross Reference Listren_theoriginalpunks100% (10)

- Fdp52N20 / Fdpf52N20T: UnifetDocument10 paginiFdp52N20 / Fdpf52N20T: UnifetJoão de barroÎncă nu există evaluări

- 051790e1.sch-1 - Wed Oct 01 10:10:48 2003Document19 pagini051790e1.sch-1 - Wed Oct 01 10:10:48 2003Italo BocattuÎncă nu există evaluări

- Practical Work 4 - CMOS + Rubrics PDFDocument23 paginiPractical Work 4 - CMOS + Rubrics PDFRiki SmithÎncă nu există evaluări

- Semiconductors DiscretesDocument96 paginiSemiconductors Discretespacho2117100% (4)

- Arun Kumar-White PaperDocument1 paginăArun Kumar-White PaperAmitÎncă nu există evaluări

- FALLSEM2019-20 ECE5018 TH VL2019201007688 Reference Material I 16-Oct-2019 MOSFET-2 2 PDFDocument12 paginiFALLSEM2019-20 ECE5018 TH VL2019201007688 Reference Material I 16-Oct-2019 MOSFET-2 2 PDFAnonymous ptSFzcfÎncă nu există evaluări

- Reemplazos Componentes PDFDocument5 paginiReemplazos Componentes PDFTJEPL128Încă nu există evaluări