Documente Academic

Documente Profesional

Documente Cultură

EEPROM 24WC256 - Catalyst

Încărcat de

Valdir DerlannDrepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

EEPROM 24WC256 - Catalyst

Încărcat de

Valdir DerlannDrepturi de autor:

Formate disponibile

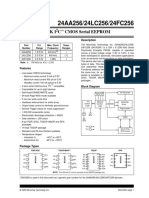

Preliminary

CAT24WC256

256K-Bit I2C Serial CMOS E2PROM

FEATURES

■ 1MHz I2C Bus Compatible* ■ Write Protect Feature

■ 1.8 to 6 Volt Operation – Entire Array Protected When WP at VIH

■ Low Power CMOS Technology ■ 100,000 Program/Erase Cycles

■ 64-Byte Page Write Buffer ■ 100 Year Data Retention

■ Self-Timed Write Cycle with Auto-Clear ■ 8-Pin DIP or 8-Pin SOIC

■ Commercial, Industrial and Automotive

Temperature Ranges

DESCRIPTION

The CAT24WC256 is a 256K-bit Serial CMOS E2PROM CAT24WC256 features a 64-byte page write buffer. The

internally organized as 32,768 words of 8 bits each. device operates via the I2C bus serial interface and is

Catalyst’s advanced CMOS technology substantially available in 8-pin DIP or 8-pin SOIC packages.

reduces device power requirements. The

PIN CONFIGURATION BLOCK DIAGRAM

DIP Package (P) EXTERNAL LOAD

1 8 VCC DOUT SENSE AMPS

A0

SHIFT REGISTERS

A1 2 7 WP ACK

NC 3 6 SCL VCC

VSS 4 5 SDA

VSS WORD ADDRESS COLUMN

BUFFERS DECODERS

512

SOIC Package (K) SDA START/STOP

LOGIC

A0 1 8 VCC

A1 2 7 WP

E2PROM

NC 3 6 SCL XDEC 512 512X512

VSS 4 5 SDA CONTROL

24WC256 F01 WP LOGIC

PIN FUNCTIONS

Pin Name Function

DATA IN STORAGE

A0, A1 Address Inputs

SDA Serial Data/Address

HIGH VOLTAGE/

SCL Serial Clock TIMING CONTROL

WP Write Protect

SCL STATE COUNTERS

VCC +1.8V to +6.0V Power Supply

A0 SLAVE

VSS Ground A1 ADDRESS

COMPARATORS

NC No Connect

24WC256 F02

* Catalyst Semiconductor is licensed by Philips Corporation to carry the I2C Bus Protocol.

© 1998 by Catalyst Semiconductor, Inc. Doc. No. 25061-00 6/99 S-1

Characteristics subject to change without notice 1

CAT24WC256 Preliminary

ABSOLUTE MAXIMUM RATINGS* *COMMENT

Temperature Under Bias ................. –55°C to +125°C Stresses above those listed under “Absolute Maximum

Storage Temperature ....................... –65°C to +150°C Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation of

Voltage on Any Pin with the device at these or any other conditions outside of those

Respect to Ground(1) ........... –2.0V to +VCC + 2.0V listed in the operational sections of this specification is not

VCC with Respect to Ground ............... –2.0V to +7.0V implied. Exposure to any absolute maximum rating for

extended periods may affect device performance and

Package Power Dissipation reliability.

Capability (Ta = 25°C) ................................... 1.0W

Lead Soldering Temperature (10 secs) ............ 300°C

Output Short Circuit Current(2) ........................ 100mA

RELIABILITY CHARACTERISTICS

Symbol Parameter Min. Max. Units Reference Test Method

NEND(3) Endurance 100,000 Cycles/Byte MIL-STD-883, Test Method 1033

TDR (3) Data Retention 100 Years MIL-STD-883, Test Method 1008

VZAP (3) ESD Susceptibility 2000 Volts MIL-STD-883, Test Method 3015

ILTH (3)(4) Latch-up 100 mA JEDEC Standard 17

D.C. OPERATING CHARACTERISTICS

VCC = +1.8V to +6.0V, unless otherwise specified.

Limits

Symbol Parameter Min. Typ. Max. Units Test Conditions

ICC1 Power Supply Current - Read 1 mA fSCL = 100 KHz

VCC=5V

ICC2 Power Supply Current - Write 3 mA fSCL = 100KHz

VCC=5V

ISB(5) Standby Current 0 µA VIN = GND or VCC

VCC=5V

ILI Input Leakage Current 1 µA VIN = GND to VCC

ILO Output Leakage Current 1 µA VOUT = GND to VCC

VIL Input Low Voltage –1 VCC x 0.3 V

VIH Input High Voltage VCC x 0.7 VCC + 0.5 V

VOL1 Output Low Voltage (VCC = +3.0V) 0.4 V IOL = 3.0 mA

VOL2 Output Low Voltage (VCC = +1.8V) 0.5 V IOL = 1.5 mA

CAPACITANCE TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol Test Max. Units Conditions

CI/O(3) Input/Output Capacitance (SDA) 8 pF V I/O = 0V

CIN (3) Input Capacitance (SCL, WP, A0, A1) 6 pF V IN = 0V

Note:

(1) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is VCC +0.5V, which may overshoot to VCC + 2.0V for periods of less than 20ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to VCC +1V.

(5) Standby current (ISB ) = 0 µA (<900 nA).

Doc. No. 25061-00 6/99 S-1

2

Preliminary CAT24WC256

A.C. CHARACTERISTICS

VCC = +1.8V to +6V, unless otherwise specified

Output Load is 1 TTL Gate and 100pF

Read & Write Cycle Limits

Symbol Parameter VCC=1.8V - 6.0V VCC=2.5V - 6.0V VCC=3.0V - 5.5V

Min. Max. Min. Max. Min. Max. Units

FSCL Clock Frequency 100 400 1000 kHz

tAA SCL Low to SDA Data Out 0.1 3.5 0.05 0.9 0.05 0.55 µs

and ACK Out

tBUF(2) Time the Bus Must be Free Before 4.7 1.2 0.5 µs

a New Transmission Can Start

tHD:STA Start Condition Hold Time 4.0 0.6 0.25 µs

tLOW Clock Low Period 4.7 1.2 0.6 µs

tHIGH Clock High Period 4.0 0.6 0.4 µs

tSU:STA Start Condition Setup Time 4.0 0.6 0.25 µs

(for a Repeated Start Condition)

tHD:DAT Data In Hold Time 0 0 0 ns

tSU:DAT Data In Setup Time 100 100 100 ns

tR(2) SDA and SCL Rise Time 1.0 0.3 0.3 µs

tF(2) SDA and SCL Fall Time 300 300 100 ns

tSU:STO Stop Condition Setup Time 4.7 0.6 0.25 µs

tDH Data Out Hold Time 100 50 50 ns

tWR Write Cycle Time 10 10 5 ms

Power-Up Timing (2)(3)

Symbol Parameter Max. Units

tPUR Power-Up to Read Operation 1 ms

tPUW Power-Up to Write Operation 1 ms

Note:

(1) AC measurement conditions:

RL (connects to VCC): 0.3VCC to 0.7 VCC

Input rise and fall times: < 50ns

Input and output timing reference voltages: 0.5 VCC

(2) This parameter is tested initially and after a design or process change that affects the parameter.

(3) tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated.

The write cycle time is the time from a valid stop interface circuits are disabled, SDA is allowed to remain

condition of a write sequence to the end of the internal high, and the device does not respond to its slave

program/erase cycle. During the write cycle, the bus address.

3 Doc. No. 25061-00 6/99 S-1

CAT24WC256 Preliminary

FUNCTIONAL DESCRIPTION SDA: Serial Data/Address

The bidirectional serial data/address pin is used to

The CAT24WC256 supports the I2C Bus data transmis- transfer all data into and out of the device. The SDA pin

sion protocol. This Inter-Integrated Circuit Bus protocol is an open drain output and can be wire-ORed with other

defines any device that sends data to the bus to be a open drain or open collector outputs.

transmitter and any device receiving data to be a re-

ceiver. The transfer is controlled by the Master device WP: Write Protect

which generates the serial clock and all START and

STOP conditions for bus access. The CAT24WC256 This input, when tied to GND, allows write operations to

operates as a Slave device. Both the Master device and the entire memory. When this pin is tied to Vcc, the

Slave device can operate as either transmitter or re- entire memory is write protected. When left floating,

ceiver, but the Master device controls which mode is memory is unprotected.

activated.

A0, A1: Device Address Inputs

PIN DESCRIPTIONS These pins are hardwired or left connected. When

hardwired, up to four CAT24WC256's may be addressed

SCL: Serial Clock on a single bus system. When the pins are left uncon-

The serial clock input clocks all data transferred into or nected, the default values are zero.

out of the device.

Figure 1. Bus Timing

tF tHIGH tR

tLOW tLOW

SCL

tSU:STA tHD:DAT

tHD:STA tSU:DAT tSU:STO

SDA IN

tBUF

tAA tDH

SDA OUT

5020 FHD F03

Figure 2. Write Cycle Timing

SCL

SDA 8TH BIT ACK

BYTE n

tWR

STOP START ADDRESS

CONDITION CONDITION

5020 FHD F04

Figure 3. Start/Stop Timing

SDA

SCL

5020 FHD F05

START BIT STOP BIT

Doc. No. 25061-00 6/99 S-1

4

Preliminary CAT24WC256

I2C BUS PROTOCOL

The features of the I2C bus protocol are defined as many as four devices on the same bus. These bits must

follows: compare to their hardwired input pins. The last bit of the

slave address specifies whether a Read or Write opera-

(1) Data transfer may be initiated only when the bus is tion is to be performed. When this bit is set to 1, a Read

not busy. operation is selected, and when set to 0, a Write opera-

tion is selected.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any changes After the Master sends a START condition and the slave

in the data line while the clock line is high will be address byte, the CAT24WC256 monitors the bus and

interpreted as a START or STOP condition. responds with an acknowledge (on the SDA line) when

its address matches the transmitted slave address. The

START Condition

CAT24WC256 then performs a Read or Write operation

The START Condition precedes all commands to the depending on the state of the R/W bit.

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT24WC256 monitors Acknowledge

the SDA and SCL lines and will not respond until this After a successful data transfer, each receiving device is

condition is met. required to generate an acknowledge. The Acknowledg-

ing device pulls down the SDA line during the ninth clock

STOP Condition

cycle, signaling that it received the 8 bits of data.

A LOW to HIGH transition of SDA when SCL is HIGH

determines the STOP condition. All operations must end The CAT24WC256 responds with an acknowledge after

with a STOP condition. receiving a START condition and its slave address. If the

device has been selected along with a write operation,

it responds with an acknowledge after receiving each 8-

DEVICE ADDRESSING bit byte.

The bus Master begins a transmission by sending a When the CAT24WC256 begins a READ mode it trans-

START condition. The Master sends the address of the mits 8 bits of data, releases the SDA line, and monitors

particular slave device it is requesting. The five most the line for an acknowledge. Once it receives this ac-

significant bits of the 8-bit slave address are fixed as knowledge, the CAT24WC256 will continue to transmit

10100(Fig. 5). The CAT24WC256 uses the next two bits data. If no acknowledge is sent by the Master, the device

as address bits. The address bits A1 and A0 allow as

Figure 4. Acknowledge Timing

SCL FROM 1 8 9

MASTER

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

START ACKNOWLEDGE

5020 FHD F06

Figure 5. Slave Address Bits

1 0 1 0 0 A1 A0 R/W

5027 FHD F07

5 Doc. No. 25061-00 6/99 S-1

CAT24WC256 Preliminary

terminates data transmission and waits for a STOP If the Master transmits more than 64 bytes before sending

condition. the STOP condition, the address counter ‘wraps around’,

and previously transmitted data will be overwritten.

WRITE OPERATIONS

When all 64 bytes are received, and the STOP condition

Byte Write has been sent by the Master, the internal programming

In the Byte Write mode, the Master device sends the cycle begins. At this point, all received data is written to

START condition and the slave address information the CAT24WC256 in a single write cycle.

(with the R/W bit set to zero) to the Slave device. After

Acknowledge Polling

the Slave generates an acknowledge, the Master sends

two 8-bit address words that are to be written into the Disabling of the inputs can be used to take advantage of

address pointers of the CAT24WC256. After receiving the typical write cycle time. Once the stop condition is

another acknowledge from the Slave, the Master device issued to indicate the end of the host's write operation,

transmits the data to be written into the addressed CAT24WC256 initiates the internal write cycle. ACK

memory location. The CAT24WC256 acknowledges polling can be initiated immediately. This involves issu-

once more and the Master generates the STOP condi- ing the start condition followed by the slave address for

tion. At this time, the device begins an internal program- a write operation. If CAT24WC256 is still busy with the

ming cycle to nonvolatile memory. While the cycle is in write operation, no ACK will be returned. If

progress, the device will not respond to any request from CAT24WC256 has completed the write operation, an

the Master device. ACK will be returned and the host can then proceed with

the next read or write operation.

Page Write

The CAT24WC256 writes up to 64 bytes of data, in a WRITE PROTECTION

single write cycle, using the Page Write operation. The

page write operation is initiated in the same manner as The Write Protection feature allows the user to protect

the byte write operation, however instead of terminating against inadvertent programming of the memory array.

after the initial byte is transmitted, the Master is allowed If the WP pin is tied to VCC, the entire memory array is

to send up to 63 additional bytes. After each byte has protected and becomes read only. The CAT24WC256

been transmitted, CAT24WC256 will respond with an will accept both slave and byte addresses, but the

acknowledge, and internally increment the six low order memory location accessed is protected from program-

address bits by one. The high order bits remain un- ming by the device’s failure to send an acknowledge

changed. after the first byte of data is received.

Figure 6. Byte Write Timing

S

T S

BUS ACTIVITY: A SLAVE BYTE ADDRESS T

MASTER R ADDRESS A15–A8 A7–A0 DATA O

T P

SDA LINE S P

*

A A A A

C C C C

K K K K

24WC256 F08

*=Don't Care Bit

Figure 7. Page Write Timing

S

T S

BUS ACTIVITY: A SLAVE BYTE ADDRESS T

MASTER R ADDRESS A15–A8 A7–A0 DATA DATA n DATA n+63 O

T P

SDA LINE S P

*

A A A A A A A

C C C C C C C

K K K K K K K

24WC256F09

*=Don't Care Bit

Doc. No. 25061-00 6/99 S-1

6

Preliminary CAT24WC256

READ OPERATIONS wishes to read. After CAT24WC256 acknowledges, the

Master device sends the START condition and the slave

The READ operation for the CAT24WC256 is initiated in address again, this time with the R/W bit set to one. The

the same manner as the write operation with one excep- CAT24WC256 then responds with its acknowledge and

tion, that R/W bit is set to one. Three different READ sends the 8-bit byte requested. The master device does

operations are possible: Immediate/Current Address not send an acknowledge but will generate a STOP

READ, Selective/Random READ and Sequential READ. condition.

Immediate/Current Address Read Sequential Read

The CAT24WC256’s address counter contains the ad- The Sequential READ operation can be initiated by

dress of the last byte accessed, incremented by one. In either the Immediate Address READ or Selective READ

other words, if the last READ or WRITE access was to operations. After the CAT24WC256 sends the initial 8-

address N, the READ immediately following would ac- bit byte requested, the Master will respond with an

cess data from address N+1. If N=E (where E=32767), acknowledge which tells the device it requires more

then the counter will ‘wrap around’ to address 0 and data. The CAT24WC256 will continue to output an 8-bit

continue to clock out data. After the CAT24WC256 byte for each acknowledge sent by the Master. The

receives its slave address information (with the R/W bit operation will terminate when the Master fails to respond

set to one), it issues an acknowledge, then transmits the with an acknowledge, thus sending the STOP condition.

8 bit byte requested. The master device does not send

an acknowledge, but will generate a STOP condition. The data being transmitted from CAT24WC256 is out-

putted sequentially with data from address N followed by

Selective/Random Read data from address N+1. The READ operation address

Selective/Random READ operations allow the Master counter increments all of the CAT24WC256 address bits

device to select at random any memory location for a so that the entire memory array can be read during one

READ operation. The Master device first performs a operation. If more than E (where E=32767) bytes are

‘dummy’ write operation by sending the START condi- read out, the counter will ‘wrap around’ and continue to

tion, slave address and byte addresses of the location it clock out data bytes.

Figure 8. Immediate Address Read Timing

S

T S

BUS ACTIVITY: A SLAVE T

MASTER R ADDRESS DATA O

T P

SDA LINE S P

A N

C O

K A

C

K

SCL 8 9

SDA 8TH BIT

DATA OUT NO ACK STOP

24WC128 F10 24WC256 F10

7 Doc. No. 25061-00 6/99 S-1

CAT24WC256 Preliminary

Figure 9. Selective Read Timing

S S

T T S

BUS ACTIVITY: A SLAVE BYTE ADDRESS A SLAVE T

MASTER R ADDRESS A15–A8 A7–A0 R ADDRESS DATA O

T T P

SDA LINE S

* S P

A A A A N

C C C C O

K K K K A

C

K

*=Don't Care Bit

24WC256 FIG. 11

24WC128 F11

Figure 10. Sequential Read Timing

S

BUS ACTIVITY: SLAVE T

MASTER ADDRESS DATA n DATA n+1 DATA n+2 DATA n+x O

P

SDA LINE P

A A A A N

C C C C O

K K K K

A

C

K

5020 FHD F12

ORDERING INFORMATION

Prefix Device # Suffix

CAT 24WC256 K I -1.8 TE13

Optional Product Temperature Range Tape & Reel

Company ID Number Blank = Commercial (0˚ - 70˚C) TE13: 2000/Reel

I = Industrial (-40˚ - 85˚C)

A = Automotive (-40˚ - 105˚C)*

Package Operating Voltage

P: PDIP Blank: 2.5 to 6.0V

K: SOIC (EIAJ) 1.8: 1.8 to 6.0V

3: 3.0V to 5.5V

* -40˚ to +125˚C is available upon request

24WC256 FIG. 13

Notes:

(1) The device used in the above example is a 24WC256KI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt Operating

Voltage, Tape & Reel)

Doc. No. 25061-00 6/99 S-1

8

S-ar putea să vă placă și

- ELECTRICAL CIRCUITS AND COMPONENTSDocument22 paginiELECTRICAL CIRCUITS AND COMPONENTSCedric Zamora100% (1)

- CAT24WC256: 256K-Bit I C Serial Cmos EepromDocument10 paginiCAT24WC256: 256K-Bit I C Serial Cmos EepromAntonio ManuelÎncă nu există evaluări

- 24WC01 PDFDocument10 pagini24WC01 PDFneko1212121515123001Încă nu există evaluări

- CAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesDocument10 paginiCAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesAgustin AndrokaitesÎncă nu există evaluări

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pagini24AA02/24LC02B: 2KI C Serial EEPROMhanifÎncă nu există evaluări

- Datasheet PDFDocument26 paginiDatasheet PDFNicoli LourençoÎncă nu există evaluări

- 1K 5.0V I C™ Serial EEPROM: Features: DescriptionDocument36 pagini1K 5.0V I C™ Serial EEPROM: Features: DescriptionDanna PerezÎncă nu există evaluări

- 24AA02H 24LC02BH 2K I2C Serial EEPROM With Half Array Write Protect 20002105BDocument40 pagini24AA02H 24LC02BH 2K I2C Serial EEPROM With Half Array Write Protect 20002105BAlhassan Ahmed OmranÎncă nu există evaluări

- 24C02BN Su18Document26 pagini24C02BN Su18Dwp BhaskaranÎncă nu există evaluări

- At Melee Prom DatasheetDocument26 paginiAt Melee Prom Datasheetlodde2Încă nu există evaluări

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 paginiCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaÎncă nu există evaluări

- 24aa512 Mic PDFDocument28 pagini24aa512 Mic PDFkt2018Încă nu există evaluări

- Atmel 8517 Seeprom At24c01b 02b 04b 08b Auto DatasheetDocument18 paginiAtmel 8517 Seeprom At24c01b 02b 04b 08b Auto DatasheetAlhassan Ahmed OmranÎncă nu există evaluări

- Item 11 X24C16PDocument15 paginiItem 11 X24C16Pdifa20061168Încă nu există evaluări

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pagini24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezÎncă nu există evaluări

- Atmlh034 Atmel PDFDocument12 paginiAtmlh034 Atmel PDFAlexander RinconÎncă nu există evaluări

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pagini24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezÎncă nu există evaluări

- 24AA256/24LC256: 256K I C Cmos Serial EepromDocument12 pagini24AA256/24LC256: 256K I C Cmos Serial EepromWelleyÎncă nu există evaluări

- 24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738Document32 pagini24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738İbrahim DemircioğluÎncă nu există evaluări

- Features: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryDocument23 paginiFeatures: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryLi JamesÎncă nu există evaluări

- 16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangesDocument22 pagini16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangeshcarcaroÎncă nu există evaluări

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pagini25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoÎncă nu există evaluări

- 64k Nonvolatile SRAM DatasheetDocument10 pagini64k Nonvolatile SRAM DatasheetJosé AdelinoÎncă nu există evaluări

- Write Protect Pin For Hardware Data ProtectionDocument16 paginiWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- 24LC08 PDFDocument30 pagini24LC08 PDFJaime BarrancoÎncă nu există evaluări

- 32K 2.5V I C Serial EEPROM: Features Package TypesDocument12 pagini32K 2.5V I C Serial EEPROM: Features Package Typesinsomnium86Încă nu există evaluări

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument24 pagini24AA02/24LC02B: 2KI C Serial EEPROMMayk OzÎncă nu există evaluări

- 24aa515, 24LC515, 24FC515Document20 pagini24aa515, 24LC515, 24FC515dorudÎncă nu există evaluări

- 24LC21 1K 2.5V Dual Mode I2C Serial EEPROMDocument12 pagini24LC21 1K 2.5V Dual Mode I2C Serial EEPROMVictor TruccoÎncă nu există evaluări

- At24c02a 04a 08aDocument16 paginiAt24c02a 04a 08aretno.endah ekowatiÎncă nu există evaluări

- 24AA08/24LC08B: 8KI C Serial EEPROMDocument30 pagini24AA08/24LC08B: 8KI C Serial EEPROMjoseÎncă nu există evaluări

- 24AA16 24LC16B 24FC16 16K I2C Serial EEPROM 20001703PDocument49 pagini24AA16 24LC16B 24FC16 16K I2C Serial EEPROM 20001703Pmarko.jojicoo777Încă nu există evaluări

- Atmel 24c02 PDFDocument30 paginiAtmel 24c02 PDFMAX GÎncă nu există evaluări

- 21711c PDFDocument24 pagini21711c PDFAbdessamad EladakÎncă nu există evaluări

- CAT 28256 - EepromDocument20 paginiCAT 28256 - EepromTiago LeonhardtÎncă nu există evaluări

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pagini24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaÎncă nu există evaluări

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pagini32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86Încă nu există evaluări

- Ic PDFDocument36 paginiIc PDFdharamÎncă nu există evaluări

- 24aa08 - 24lc08 Eeprom PDFDocument40 pagini24aa08 - 24lc08 Eeprom PDFEdgar DauzonÎncă nu există evaluări

- 25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMDocument26 pagini25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMmuglanÎncă nu există evaluări

- 2-Wire Serial Eeprom: FeaturesDocument20 pagini2-Wire Serial Eeprom: FeaturesAgustin AndrokaitesÎncă nu există evaluări

- 93C66Document12 pagini93C66Alex AlvarezÎncă nu există evaluări

- Low Voltage 2-Wire Serial EEPROM with 16K MemoryDocument11 paginiLow Voltage 2-Wire Serial EEPROM with 16K Memoryjavier venturaÎncă nu există evaluări

- DatasheetDocument12 paginiDatasheetKlan ZangoÎncă nu există evaluări

- HN58X24128I/HN58X24256I: Two-Wire Serial Interface 128k EEPROM (16-Kword 8-Bit) 256k EEPROM (32-Kword 8-Bit)Document22 paginiHN58X24128I/HN58X24256I: Two-Wire Serial Interface 128k EEPROM (16-Kword 8-Bit) 256k EEPROM (32-Kword 8-Bit)Ernesto K. OshiroÎncă nu există evaluări

- Two-Wire Serial Eeprom: FeaturesDocument19 paginiTwo-Wire Serial Eeprom: FeaturesVikrant SharmaÎncă nu există evaluări

- At 25080Document21 paginiAt 25080sabÎncă nu există evaluări

- 24C32Document12 pagini24C32SilviuCocoloșÎncă nu există evaluări

- 2-Wire Serial EEPROM: FeaturesDocument22 pagini2-Wire Serial EEPROM: FeaturesNikolay MikolkinÎncă nu există evaluări

- 25 LC 1024Document28 pagini25 LC 1024hyd27Încă nu există evaluări

- 8K/16K 5.0V SPI Bus Serial EEPROM: Features Package TypesDocument12 pagini8K/16K 5.0V SPI Bus Serial EEPROM: Features Package Typesrıdvan71Încă nu există evaluări

- 24FC1025 EepromDocument28 pagini24FC1025 EepromAnirudh ReddyÎncă nu există evaluări

- 2-Wire Serial Eeproms: FeaturesDocument16 pagini2-Wire Serial Eeproms: FeaturesTuan Pham AnhÎncă nu există evaluări

- 1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeDocument8 pagini1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeHarris RaoÎncă nu există evaluări

- 8K/16K 5.0V I C Serial Eeproms: Features Package TypesDocument13 pagini8K/16K 5.0V I C Serial Eeproms: Features Package Typesarunan55Încă nu există evaluări

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pagini25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийÎncă nu există evaluări

- 24l1026i Memoria EEPROM 1024kDocument28 pagini24l1026i Memoria EEPROM 1024kMarta_d_eÎncă nu există evaluări

- 24C64 - EepromDocument20 pagini24C64 - Eepromropay61705Încă nu există evaluări

- 24LC04B PDFDocument22 pagini24LC04B PDFEddy RosarioÎncă nu există evaluări

- 24c1024 Ic DatasheetDocument20 pagini24c1024 Ic DatasheetVikas AttardeÎncă nu există evaluări

- Infineon 6ED003L0x F2 DS v02 09 enDocument19 paginiInfineon 6ED003L0x F2 DS v02 09 enValdir DerlannÎncă nu există evaluări

- Fanuc Manuals 520Document268 paginiFanuc Manuals 520danielstancu883296100% (2)

- Cabo Programacao Drive St10-PlusDocument1 paginăCabo Programacao Drive St10-PlusValdir DerlannÎncă nu există evaluări

- Infineon IFCM15S60GD DataSheet v02 04 enDocument26 paginiInfineon IFCM15S60GD DataSheet v02 04 enValdir DerlannÎncă nu există evaluări

- User Manual: Divisione S.B.CDocument95 paginiUser Manual: Divisione S.B.CRenato MeloÎncă nu există evaluări

- AC and DC Drives Applications: Power Line ConsiderationsDocument3 paginiAC and DC Drives Applications: Power Line ConsiderationsValdir DerlannÎncă nu există evaluări

- Powertools Pro Application Note: Ptan #2, Rev.1, 3/30/2009Document17 paginiPowertools Pro Application Note: Ptan #2, Rev.1, 3/30/2009Valdir DerlannÎncă nu există evaluări

- Green-Mode PWM Controller: General Description FeaturesDocument10 paginiGreen-Mode PWM Controller: General Description FeaturesValdir DerlannÎncă nu există evaluări

- EATON Diesel Plus Diesel Engine Fire Pump Controller: O & M Manual IM05805019KDocument32 paginiEATON Diesel Plus Diesel Engine Fire Pump Controller: O & M Manual IM05805019KValdir DerlannÎncă nu există evaluări

- PBBAA Cable Drawing PDFDocument1 paginăPBBAA Cable Drawing PDFValdir DerlannÎncă nu există evaluări

- PTAN14 Latency Settings PowerTools ProDocument5 paginiPTAN14 Latency Settings PowerTools ProValdir DerlannÎncă nu există evaluări

- STEP 7 Basic V12 enUS en-US PDFDocument3.934 paginiSTEP 7 Basic V12 enUS en-US PDFValdir DerlannÎncă nu există evaluări

- PTAN1 RealTimeandCyclicalProgramsDocument9 paginiPTAN1 RealTimeandCyclicalProgramsValdir DerlannÎncă nu există evaluări

- Alternate Master Setup for EP-P Drive and EZ-ModuleDocument5 paginiAlternate Master Setup for EP-P Drive and EZ-ModuleValdir DerlannÎncă nu există evaluări

- Easy USB to Serial Adapter Setup for Windows VistaDocument3 paginiEasy USB to Serial Adapter Setup for Windows VistaGilmar SantosÎncă nu există evaluări

- USB 2.0 Serial Adapter User Installation Manual: ContentsDocument6 paginiUSB 2.0 Serial Adapter User Installation Manual: ContentsAlexandre Da Silva PintoÎncă nu există evaluări

- dsPIC33F FRM Section 3. Data Memory (DS70202B)Document26 paginidsPIC33F FRM Section 3. Data Memory (DS70202B)Franco ApolinarioÎncă nu există evaluări

- FRM CodeSafe 70199B PDFDocument40 paginiFRM CodeSafe 70199B PDFValdir DerlannÎncă nu există evaluări

- Section 20. Data Converter Interface (DCI) : HighlightsDocument50 paginiSection 20. Data Converter Interface (DCI) : HighlightsValdir DerlannÎncă nu există evaluări

- dsPIC33F FRM Section 2. CPU (DS70204A)Document45 paginidsPIC33F FRM Section 2. CPU (DS70204A)Franco ApolinarioÎncă nu există evaluări

- Position Guide LowresDocument68 paginiPosition Guide LowresaaaÎncă nu există evaluări

- Section 16. Analog-to-Digital Converter (ADC) : HighlightsDocument66 paginiSection 16. Analog-to-Digital Converter (ADC) : HighlightsValdir DerlannÎncă nu există evaluări

- OPA350 OPA2350 OPA4350 High-Speed, Single-Supply, Rail-to-Rail Operational Amplifiers SeriesDocument22 paginiOPA350 OPA2350 OPA4350 High-Speed, Single-Supply, Rail-to-Rail Operational Amplifiers SeriesValdir DerlannÎncă nu există evaluări

- PCF 8583Document28 paginiPCF 8583Wassim ZouchÎncă nu există evaluări

- Eeprom 24c04a - MicrochipDocument12 paginiEeprom 24c04a - MicrochipHugo LeonardoÎncă nu există evaluări

- EEPROM 24LC256 - Microchip PDFDocument28 paginiEEPROM 24LC256 - Microchip PDFValdir DerlannÎncă nu există evaluări

- EEPROM 24C256 - Atmel PDFDocument20 paginiEEPROM 24C256 - Atmel PDFValdir DerlannÎncă nu există evaluări

- Fanuc Manuals 520Document268 paginiFanuc Manuals 520danielstancu883296100% (2)

- User Manual: Divisione S.B.CDocument95 paginiUser Manual: Divisione S.B.CRenato MeloÎncă nu există evaluări

- Q3 - Science5 - Week 7Document14 paginiQ3 - Science5 - Week 7Maria Ronavie Davalos MantesÎncă nu există evaluări

- Cadweld JointsDocument56 paginiCadweld Jointsgadgil_vikrantÎncă nu există evaluări

- Bor CelleDocument11 paginiBor CelleAdi KhardeÎncă nu există evaluări

- Appendix B Data Pscad DataDocument10 paginiAppendix B Data Pscad DatakuchowÎncă nu există evaluări

- Antenna Theory and Applications - 2012 - Visser - Appendix A Effective Aperture and DirectivityDocument3 paginiAntenna Theory and Applications - 2012 - Visser - Appendix A Effective Aperture and Directivitybeatriz diasÎncă nu există evaluări

- EES005 Electrical Protection and Earthing GuidelineDocument37 paginiEES005 Electrical Protection and Earthing GuidelineSuresh K KrishnasamyÎncă nu există evaluări

- Bulletin 2881BDocument2 paginiBulletin 2881Bsylvi293Încă nu există evaluări

- Iscn-Channel Mosfet Transistor: Inchange SemiconductorDocument2 paginiIscn-Channel Mosfet Transistor: Inchange SemiconductorLEONERÎncă nu există evaluări

- Motor Test Instructions PDFDocument2 paginiMotor Test Instructions PDFAriel DimacaliÎncă nu există evaluări

- Basic Question Bank With Answers and ExplanationsDocument275 paginiBasic Question Bank With Answers and ExplanationsAnonymous eWMnRr70qÎncă nu există evaluări

- PQube 3 Instruction Manual - Revision 1.9Document103 paginiPQube 3 Instruction Manual - Revision 1.9John LadinoÎncă nu există evaluări

- GUESH FINAL REPORT ON APF (Repaired) Alex PowerDocument40 paginiGUESH FINAL REPORT ON APF (Repaired) Alex PowerBelayneh Tadesse100% (3)

- WF101GTYAPLNG0Document7 paginiWF101GTYAPLNG0Jorge ArijaÎncă nu există evaluări

- NEC Article 620: Elevators, Part 1: Continuing Education: Codes & StandardsDocument10 paginiNEC Article 620: Elevators, Part 1: Continuing Education: Codes & StandardsMenaÎncă nu există evaluări

- REG Emergency Power Supply, Light Grey: CharacteristicsDocument1 paginăREG Emergency Power Supply, Light Grey: CharacteristicsCarlos HerreraÎncă nu există evaluări

- Gutor TechnologyDocument2 paginiGutor TechnologyFELIXDEJÎncă nu există evaluări

- Amplitude ControlDocument3 paginiAmplitude ControlgadhaÎncă nu există evaluări

- T Rec K.26 200804 I!!pdf eDocument8 paginiT Rec K.26 200804 I!!pdf ejmrs7322Încă nu există evaluări

- Residential Code Update Part 1 of 2 HrsDocument103 paginiResidential Code Update Part 1 of 2 HrsTakumi FujiwaraÎncă nu există evaluări

- 1N5913B Series 3 W DO-41 Surmetic 30 Zener Voltage RegulatorsDocument9 pagini1N5913B Series 3 W DO-41 Surmetic 30 Zener Voltage RegulatorsRiko HusinÎncă nu există evaluări

- Product Detail - RCFDocument1 paginăProduct Detail - RCFRamadhani UtomoÎncă nu există evaluări

- The Basics of Testing A Mass Air Flow (MAF) SensorDocument5 paginiThe Basics of Testing A Mass Air Flow (MAF) SensorbroÎncă nu există evaluări

- Using The Power MOSFET As A SwitchDocument5 paginiUsing The Power MOSFET As A SwitchNgoc Nguyen HaÎncă nu există evaluări

- 5th IPhO 1971 IPhO SolutionsDocument8 pagini5th IPhO 1971 IPhO SolutionsPopovici DraganÎncă nu există evaluări

- Application Note: Guidance On Selecting and Handling Coaxial RF Connectors Used With Rohde & Schwarz Test EquipmentDocument19 paginiApplication Note: Guidance On Selecting and Handling Coaxial RF Connectors Used With Rohde & Schwarz Test EquipmentMạnh Huy BùiÎncă nu există evaluări

- Emd ManualDocument17 paginiEmd ManualBina HinglajiyaÎncă nu există evaluări

- Durosite Series Led High Bay: For Industrial & Commercial ApplicationsDocument8 paginiDurosite Series Led High Bay: For Industrial & Commercial ApplicationsTiagohowpy RamosÎncă nu există evaluări

- Mid ExamDocument3 paginiMid ExamAbdulhakim heboÎncă nu există evaluări

- Capacitor ESR MeterDocument2 paginiCapacitor ESR MeterMarkoÎncă nu există evaluări