Documente Academic

Documente Profesional

Documente Cultură

D D D D D D D D: TLV4110, TLV4111, TLV4112, TLV4113 Family of High Output Drive Operational Amplifiers With Shutdown

Încărcat de

Andrew AguilarTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

D D D D D D D D: TLV4110, TLV4111, TLV4112, TLV4113 Family of High Output Drive Operational Amplifiers With Shutdown

Încărcat de

Andrew AguilarDrepturi de autor:

Formate disponibile

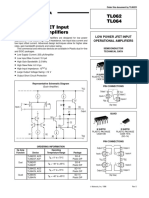

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

D High Output Drive . . . >300 mA TLV4112

D Rail-To-Rail Output

D, DGN, OR P PACKAGE

(TOP VIEW)

D Unity-Gain Bandwidth . . . 2 MHz

D Slew Rate . . . 1.5 V/µs 1OUT 1 8 VDD

D Supply Current . . . 700-µA/Per Channel

1IN –

1IN +

2

3

7

6

2OUT

2IN –

D Supply Voltage Range . . . 2.5 V to 6 V GND 4 5 2IN+

D Specified Temperature Range:

– TA = 0°C to 70°C . . . Commercial Grade

– TA = –40°C to 125°C . . . Industrial Grade

D Universal OpAmp EVM

description

The TLV411x single supply operational amplifiers provide output currents in excess of 300 mA at 5 V. This

enables standard pin-out amplifiers to be used as high current buffers or in coil driver applications. The TLV4110

and TLV4113 comes with a shutdown feature.

The TLV411x is available in the ultra small MSOP PowerPAD package, which offers the exceptional thermal

impedance required for amplifiers delivering high current levels.

All TLV411x devices are offered in PDIP, SOIC (single and dual) and MSOP PowerPAD (dual).

FAMILY PACKAGE TABLE

NUMBER OF PACKAGE TYPES UNIVERSAL

DEVICE SHUTDOWN

CHANNELS MSOP PDIP SOIC EVM BOARD

TLV4110† 1 8 8 8 Yes

TLV4111† 1 8 8 8 — Refer to the EVM

Selection Guide

TLV4112 2 8 8 8 — (Lit# SLOU060)

TLV4113† 2 10 14 14 Yes

† This device is in the Product Preview stage of development. Contact the local TI sales office for more

information.

HIGH-LEVEL OUTPUT VOLTAGE LOW-LEVEL OUTPUT VOLTAGE

vs vs

HIGH-LEVEL OUTPUT CURRENT LOW-LEVEL OUTPUT CURRENT

3.0 1.0

V OH – High-Level Output Voltage – V

VDD = 3 V

VOL – Low-Level Output Voltage – V

2.9 VDD = 3 V 0.9

2.8 0.8 TA = 70°C

2.7 0.7 TA = 25°C

TA = 125°C TA = 0°C

2.6 0.6

TA = –40°C TA = –40°C

2.5 0.5

TA = 0°C TA = 125°C

2.4 TA = 25°C 0.4

2.3 TA = 70°C 0.3

2.2 0.2

2.1 0.1

2.0 0.0

0 50 100 150 200 250 300 0 50 100 150 200 250 300

IOH – High-Level Output Current – mA IOL – Low-Level Output Current – mA

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date. Copyright 2000, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

TLV4110 AND TLV4111 AVAILABLE OPTIONS

PACKAGED DEVICES

TA SMALL OUTLINE SMALL OUTLINE PLASTIC DIP

SYMBOL

(D)†‡ (DGN)† (P)

TLV4110CD TLV4110CDGN xxTIAHL TLV4110CP

0°C to 70°C

TLV4111CD TLV4111CDGN xxTIAHN TLV4111CP

TLV4110ID TLV4110IDGN xxTIAHM TLV4110IP

– 40°C to 125°C

TLV4111ID TLV4111IDGN xxTIAHO TLV4111IP

† This package is available taped and reeled. To order this packaging option, add an R suffix to the part

number (e.g., TLV4110CDR).

‡ In the SOIC package, the maximum RMS output power is thermally limited to 350 mW; 700 mW peaks can be driven, as

long as the RMS value is less than 350 mW.

TLV4112 AND TLV4113 AVAILABLE OPTIONS

PACKAGED DEVICES

TA SMALL OUT-

SMALL OUTLINE SMALL OUTLINE PLASTIC DIP

LINE SYMBOL SYMBOL

(D)†§ (DGQ)† (P)

(DGN)†

TLV4112CD TLV4112DGN xxTIAHP — — TLV4112CP

0°C to 70°C

TLV4113CD‡ — — TLV4113CDGN‡ xxTIAHR TLV4113CN‡

TLV4112ID TLV4112IDGN xxTIAHQ — — TLV4112IP

– 40°C to 125°C

TLV4113ID‡ — — TLV4113IDGN‡ xxTIAHS TLV4113IN‡

† This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TLV4112CDR).

‡ This device is in the Product Preview stage of development. Contact the local TI sales office for more information.

§ In the SOIC package, the maximum RMS output power is thermally limited to 350 mW; 700 mW peaks can be driven, as long as the

RMS value is less than 350 mW.

TLV411x PACKAGE PINOUTS

TLV4110 TLV4111 TLV4112

D, DGN OR P PACKAGE D, DGN OR P PACKAGE D, DGN, OR P PACKAGE

(TOP VIEW) (TOP VIEW) (TOP VIEW)

NC 1 8 SHDN NC 1 8 NC 1OUT 1 8 VDD

IN – 2 7 NC IN – 2 7 VDD 1IN – 2 7 2OUT

IN + 3 6 VDD IN + 3 6 OUT 1IN + 3 6 2IN –

GND 4 5 OUT GND 4 5 NC GND 4 5 2IN+

TLV4113 TLV4113

DGQ PACKAGE D OR N PACKAGE

(TOP VIEW) (TOP VIEW)

1OUT 1 10 VDD+ 1OUT 1 14 VDD

1IN – 2 9 2OUT 1IN – 2 13 2OUT

1IN+ 3 8 2IN – 1IN+ 3 12 2IN –

GND 4 7 2IN+

GND 4 11 2IN+

1SHDN 5 6 2SHDN

NC 5 10 NC

1SHDN 6 9 2SHDN

NC 7 8 NC

NC – No internal connection

2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage, VDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Differential input voltage, VID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± VDD

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± VDD

Output current,IO (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 800 mA

Continuous /RMS output current, IO (each output of amplifier): TJ ≤ 105°C . . . . . . . . . . . . . . . . . . . . 350 mA

TJ ≤ 150°C . . . . . . . . . . . . . . . . . . . . 110 mA

Peak output current, IO (each output of amplifier: TJ ≤ 105°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 mA

TJ ≤ 150°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155 mA

Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Table

Operating free-air temperature range, TA: C suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

I suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 40°C to 125°C

Maximum junction temperature, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 65°C to 150°C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to GND.

2. To prevent permanent damage the die temperature must not exceed the maximum junction temperature.

DISSIPATION RATING TABLE

θJC θJA TA ≤ 25°C

PACKAGE

(°C/W) (°C/W) POWER RATING

D (8) 38.3 176 710 mW

D (14) 26.9 122.3 1022 mW

DGN (8)‡ 4.7 52.7 2.37 W

DGQ (10)‡ 4.7 52.3 2.39 W

P (8) 41 104 1200 mW

N (14) 32 78 1600 mW

‡ See The Texas Instruments document, PowerPAD Thermally Enhanced Package Application

Report (literature number SLMA002), for more information on the PowerPAD package. The

thermal data was measured on a PCB layout based on the information in the section entitled

Texas Instruments Recommended Board for PowerPAD on page 33 of the before mentioned

document.

recommended operating conditions

MIN MAX UNIT

Supply voltage, VDD 2.5 6 V

Common-mode input voltage range, VICR 0 VDD–1.5 V

C-suffix 0 70

Operating free-air

free air temperature,

temperature TA °C

I-suffix –40 125

VDD = 3 V 2.1

V(on)

VDD = 5 V 3.8

Shutdown turn on/off voltage level§ V

VDD = 3 V 0.9

V(off)

VDD = 5 V 1.65

§ Relative to GND

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

electrical characteristics at recommend operating conditions, VDD = 3 V and 5 V (unless otherwise

noted)

dc performance

PARAMETER TEST CONDITIONS TA† MIN TYP MAX UNITS

25°C 175 3500

VIO Input offset voltage VIC = VDD/2,

/2 VO = VDD/2 , µV

Full range 4000

Ω,

RL = 100 Ω RS = 50 Ω

αVIO Offset voltage draft 25°C 3 µV/°C

VDD = 3 V, VIC = 0 to 2 V,

25°C 63

RS = 50 Ω

CMRR Common mode rejection ratio

Common-mode dB

VDD = 5 V, VIC = 0 to 4 V,

25°C 68

RS = 50 Ω

25°C 78 84

RL=100 Ω

VDD = 3 V,, Full range 67

VO(PP)=0 to 1V 25°C 85 100

RL=10 kΩ

Large-signal

g g differential voltage

g Full range 75

AVD dB

amplification 25°C 88 94

RL=100 Ω

VDD = 5 V,, Full range 75

VO(PP)=0 to 3V 25°C 90 110

RL=10 kΩ

Full range 85

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

input characteristics

PARAMETER TEST CONDITIONS TA† MIN TYP MAX UNITS

0

25°C and

VDD = 3 V to

Measured over Full range

1.5

VICR Common mode input voltage range

Common-mode CMRR range,

range V

RS = 50 Ω 0

25°C and

VDD = 5 V to

Full range

3.5

25°C 0.3 25

IIO Input offset current VIC = VDD/2 TLV411xC 50

Full range

TLV411xI 250

pA

25°C 0.3 50

/2

VO = VDD/2,

IIB Input bias current TLV411xC 100

RS = 50 Ω Full range

TLV411xI 500

ri(d) Differential input resistance 25°C 1000 GΩ

CIC Common-mode input capacitance f = 100 Hz 25°C 5 pF

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

electrical characteristics at specified free-air temperature, VDD = 3 V and 5 V (unless otherwise

noted) (continued)

output characteristics

PARAMETER TEST CONDITIONS TA† MIN TYP MAX UNITS

25°C 2.7 2.97

IOH = –10

10 mA

Full range 2.7

VDD = 3 V

V, VIC = VDD/2 V

25°C 2.6 2.73

IOH =–100

= 100 mA

Full range 2.6

25°C 4.7 4.96

10 mA

IOH = –10

VOH High-level output voltage Full range 4.7

25°C 4.6 4.76

IOH = –100

100 mA

VDD = 5 V, VIC = VDD/2 Full range 4.6 V

25°C 4.45 4.6

IOH = –200 mA –40°C to

4.35

85°C

25°C 0.03 0.1

IOL = 10 mA

VDD = 3 V and 5 V,, Full range 0.1

VIC = VDD/2 25°C 0.33 0.4

IOL = 100 mA

VOL Low–level output voltage Full range 0.55 V

25°C 0.38 0.6

VDD = 5 V, VIC = VDD/2 IOL = 200 mA –40°C to

0.7

85°C

VDD = 3 V ±220

IO Output current‡ Measured at 0.5

0 5 V from rail 25°C mA

VDD = 5 V ±320

Sourcing 800

IOS Short circuit output current‡

Short-circuit 25°C mA

Sinking 800

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

‡ When driving output currents in excess of 200 mA, the MSOP PowerPAD package is required for thermal dissipation.

power supply

PARAMETER TEST CONDITIONS TA MIN TYP MAX UNITS

25°C 700 1000

IDD Supply current (per channel) VO = VDD/2 µA

Full range 1500

VDD =2.7 to 3.3 V,, No load,, 25°C 70 82

VIC = VDD/2 V Full range 65

KSVR Power supply rejection ratio (∆VDD / ∆VIO) dB

VDD =4.5 to 5.5 V, No load, 25°C 70 79

VIC = VDD/2 V Full range 65

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

electrical characteristics at specified free-air temperature, VDD = 3 V and 5 V (unless otherwise

noted) (continued)

dynamic performance

PARAMETER TEST CONDITIONS TA† MIN TYP MAX UNITS

GBWP Gain bandwidth product RL=100 Ω CL=10 pF 25°C 2.7 MHz

25°C 0.8 1.57

Vo(pp) = 2 V, VDD = 3 V

Full range 0.55

SR Slew rate at unity gain RL = 100 Ω,

Ω V/µs

CL = 10 pF

F 25°C 1 1.57

VDD = 5 V

Full range 0.7

φM Phase margin 66

RL = 100 Ω,

Ω CL = 10 pF 25°C

Gain margin 16 dB

V(STEP)pp = 1 V,

0.1% 0.7

AV = –1,

ts Settling time 25°C µs

CL = 10 pF,

RL = 100 Ω 0.01% 1.3

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

noise/distortion performance

PARAMETER TEST CONDITIONS TA MIN TYP MAX UNITS

VO(pp) = VDD/2 V, AV = 1 0.025

THD+N Total harmonic distortion plus noise RL = 100 Ω, AV = 10 0.035

f = 100 Hz AV = 100 0.15

25°C

f = 100 Hz 55

Vn Equivalent input noise voltage nV/√Hz

f = 10 kHz 10

In Equivalent input noise current f = 1 kHz 0.31 fA/√Hz

shutdown characteristics

PARAMETER TEST CONDITIONS TA† MIN TYP MAX UNITS

Supply

y current in shutdown mode (per

( channel)) 25°C TBD

IDD(SHDN) SHDN = 0 V µA

(TLV4110, TLV4113) Full range TBD

t(ON) Amplifier turnon time‡ TBD

RL = 100 Ω 25°C µs

t(Off) Amplifier turnoff time‡ TBD

† Full range is 0°C to 70°C for C suffix and – 40°C to 125°C for I suffix. If not specified, full range is –40°C to 125°C.

‡ Disable time and enable time are defined as the interval between application of the logic signal to SHDN and the point at which the supply current

has reached half its final value.

6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

TYPICAL CHARACTERISTICS

Table of Graphs

FIGURE

VIO Input offset voltage vs Common-mode input voltage 1, 2

CMRR Common-mode rejection ratio vs Frequency 3

VOH High-level output voltage vs High-level output current 4, 6

VOL Low-level output voltage vs Low-level output current 5, 7

Zo Output impedance vs Frequency 8

IDD Supply current vs Supply voltage 9

kSVR Supply voltage rejection ratio vs Frequency 10

AVD Differential voltage amplification and phase vs Frequency 11

Gain-bandwidth product vs Supply voltage 12

vs Supply voltage 13

SR Slew rate

vs Temperature 14

Total harmonic distortion+noise vs Frequency 15

Vn Equivalent input voltage noise vs Frequency 16

Phase margin vs Capacitive load 17

Voltage-follower signal pulse response vs Time 18, 19

Inverting large-signal pulse response vs Time 20, 21

Small-signal inverting pulse response vs Time 22

Crosstalk vs Frequency 23

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

TYPICAL CHARACTERISTICS

INPUT OFFSET VOLTAGE INPUT OFFSET VOLTAGE COMMON-MODE REJECTION RATIO

vs vs vs

COMMON-MODE INPUT VOLTAGE COMMON-MODE INPUT VOLTAGE FREQUENCY

6000 6000 120

CMRR – Common-Mode Rejection Ratio – dB

VDD = 3 V VDD = 5 V VDD = 3 V

TA = 25°C 110

V IO – Input Offset Voltage – µ V

TA = 25°C

V IO – Input Offset Voltage – µ V

4000 TA = 25°C

4000

100

2000 2000

90

0 0 80

70

–2000 –2000

60

–4000 –4000

50

–6000 –6000 40

–0.2 0 0.4 0.8 1.2 1.6 2 2.4 2.8 3.2 –0.2 0 0.4 1.0 1.6 2.2 2.8 3.4 4.0 4.6 5.2 100 1k 10 k 100 k 1M 10 M

VICR – Common-Mode Input Voltage – V VICR – Common-Mode Input Voltage – V f – Frequency – Hz

Figure 1 Figure 2 Figure 3

HIGH-LEVEL OUTPUT VOLTAGE LOW-LEVEL OUTPUT VOLTAGE HIGH-LEVEL OUTPUT VOLTAGE

vs vs vs

HIGH-LEVEL OUTPUT CURRENT LOW-LEVEL OUTPUT CURRENT HIGH-LEVEL OUTPUT CURRENT

3.0 1.0 5.0

V OH – High-Level Output Voltage – V

VDD = 3 V

VOL – Low-Level Output Voltage – V

2.9

V OH – High-Level Output Voltage – V

VDD = 3 V 0.9 4.9 VDD = 5 V

2.8 0.8 TA = 70°C 4.8

2.7 0.7 TA = 25°C

4.7 TA = 125°C

TA = 125°C TA = 0°C

2.6 0.6 4.6

TA = –40°C TA = –40°C TA = –40°C

2.5 0.5 4.5

TA = 0°C TA = 125°C

TA = 0°C

2.4 TA = 25°C 0.4 4.4

TA = 25°C

2.3 TA = 70°C 0.3 4.3

TA = 70°C

2.2 0.2 4.2

2.1 0.1 4.1

2.0 0.0 4.0

0 50 100 150 200 250 300 0 50 100 150 200 250 300 0 50 100 150 200 250 300

IOH – High-Level Output Current – mA IOL – Low-Level Output Current – mA IOH – High-Level Output Current – mA

Figure 4 Figure 5 Figure 6

LOW-LEVEL OUTPUT VOLTAGE OUTPUT IMPEDANCE SUPPLY CURRENT

vs vs vs

LOW-LEVEL OUTPUT CURRENT FREQUENCY SUPPLY VOLTAGE

1.0 100 1200

VDD = 5 V

VOL – Low-Level Output Voltage – V

0.9 VDD = 3 & 5 V AV = 1 TA = 125°C

TA = 25°C VIN = VDD/2 V

Z o – Output Impedance – Ω

0.8 1000

I DD – Supply Current – µ A

TA = 70°C

0.7 TA = 70°C

10

TA = 25°C 800 TA = 25°C

0.6

TA = 0°C

0.5 TA = 0°C

TA = –40°C 600

0.4

TA = 125°C A = 100 TA = –40°C

0.3 1

400

0.2

A = 10

0.1 200

A=1

0.0 0.10

0 50 100 150 200 250 300 0

100 1k 10k 100k 1M 10M 0 1 2 3 4 5 6

IOL – Low-Level Output Current – mA f – Frequency – Hz VDD – Supply Voltage – V

Figure 7 Figure 8 Figure 9

8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

TYPICAL CHARACTERISTICS

SUPPLY VOLTAGE REJECTION RATIO AMPLIFICATION AND PHASE GAIN-BANDWIDTH PRODUCT

vs vs vs

FREQUENCY FREQUENCY SUPPLY VOLTAGE

A VD – Differential Voltage Amplification – dB

100 120 135 4.0

k SVR – Supply Voltage Rejection Ratio – V

VDD = 3 & 5 V

90 RF = 1 kΩ 100 3.5

Gain-Bandwidth Product – MHz

80 RI = 100 Ω PHASE

VIN = 0 V 80 3.0

Phase Margin – °

90

70 TA = 25°C

60 2.5

60

50 40 GAIN 45 2.0

40 20 1.5 TA = 25°C

30 VDD = 3 & 5 V RL = 100 Ω

0 0 1.0 CL = 10 pF

RL = 100 kΩ

20

CL = 10 pF f = 1 kHz

–20 0.5 AV =open loop

10 TA = 25°C

0 –40 –45 0.0

100 1k 10 k 100 k 1M 10 M 100 1k 10 k 100 k 1M 10 M 2.5 3 3.5 4 4.5 5 5.5

f – Frequency – Hz f – Frequency – Hz VDD – Supply Voltage – V

Figure 10 Figure 11 Figure 12

SLEW RATE SLEW RATE

vs vs TOTAL HARMONIC DISTORTION+NOISE

SUPPLY VOLTAGE TEMPERATURE vs

FREQUENCY

2.00

2.00 10

AV = 1

THD+N –Total Harmonic Distortion + Noise

1.75 VDD = 3 & 5 V

RL = 100 Ω 1.75 VDD = 5 V

AV = 1

CL = 10 pF SR+ RL = 100 Ω

1.50 SR+ RL = 100 Ω

SR – Slew Rate – V/ µ s

1.50 VO(PP) = VDD/2

SR – Slew Rate – V/ µ s

CL = 10 pF

AV = 1, 10, & 100

1.25 1

1.25

SR– SR–

1.00

1.00

A = 100

0.75

0.75

0.1

0.50

0.50

A = 10

0.25

0.25

0.00 A=1

2.5 3 3.5 4 4.5 5 5.5 6 0.00 0.01

–40 –25 –10 5 20 35 50 65 80 95 110 125 10 100 1k 10 k 100 k

VDD – Supply Voltage – V

TA – Temperature – °C f – Frequency – Hz

Figure 13 Figure 14 Figure 15

EQUIVALENT INPUT VOLTAGE NOISE PHASE MARGIN

vs vs

FREQUENCY CAPACITIVE LOAD

100

160

VDD = 3 & 5 V

90

140 TA = 25°C

VDD = 5 V

80

Hz

RL = 100

120 70

Phase Margin – °

V n – Voltage Noise – nV/

VDD = 3 V RL = 600 RNULL = 20

100 60

50

80

40 RNULL = 20

60

30

RNULL = 0

40 20

RNULL = 0

20 10

0 0

10 100 1k 10 k 100 k

10 100 1k 10 k 100 k

Capacitive Load – pF

f – Frequency – Hz

Figure 16 Figure 17

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 9

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

TYPICAL CHARACTERISTICS

VOLTAGE-FOLLOWER VOLTAGE-FOLLOWER INVERTING LARGE-SIGNAL

LARGE-SIGNAL PULSE RESPONSE SMALL-SIGNAL PULSE RESPONSE PULSE RESPONSE

V O – Output Voltage – V V – Input Voltage – V

V O – Output Voltage – V V I – Input Voltage – V

V O – Output Voltage – V V I – Input Voltage – V

5 2.6 3

VIN

4 2

VIN 2.55

3 VDD = 5 V 1

VDD = 5 V

2.5 AV = 1 0 AV = –1

2

RL = 100 Ω RL = 100 Ω

–1 VIN

1 CL = 10 pF CL = 50 pF

2.45

I

VO TA = 25°C –2

0 TA = 25°C

VIN = 100 mV 5 VIN = 2.5 V

2.55

4

VDD = 5 V 4

3 VO

AV = 1 2.5 3

2 RL = 100 Ω 2 VO

CL = 10 pF 2.45

1 1

TA = 25°C

0 2.4 0

–2 0 2 4 6 8 10 12 14 –0.2 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 –1 0 1 2 3 4 5 6 7 8

t – TIME – µs t – TIME – µs t – TIME – µs

Figure 18 Figure 19 Figure 20

CROSSTALK

INVERTING LARGE-SIGNAL SMALL-SIGNAL INVERTING vs

PULSE RESPONSE PULSE RESPONSE FREQUENCY

V O – Output Voltage – V V I – Input Voltage – V

3

V O – Output Voltage – V V I – Input Voltage – V

2.58 0

2 VDD = 3 & 5 V

2.54

1 VIN –20 RL = 100 Ω

VDD = 5 V

0 2.5 All Channels

AV = –1

–1 RL = 100 Ω VIN VDD = 5 V

Crosstalk – dB

2.46 –40

CL = 50 pF AV = –1

–2

TA = 25°C RL = 100 Ω

2.42 –60

5 VIN = 2.5 V CL = 50 pF

4 2.54 TA = 25°C

VIN = 2.5 V –80 VIN = 4 VPP

3

2.5

2 VO VO

2.46 –100

1

VIN = 2 VPP

0 2.42

–1 0 1 2 3 4 5 6 7 8 –120

0 0.2 0.6 1.0 1.4 1.8 2.2 2.6 3.0

10 100 1k 10 k 100 k

t – TIME – µs t – TIME – µs f – Frequency – Hz

Figure 21 Figure 22 Figure 23

10 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

shutdown function

Two members of the TLV411x family (TLV4110/3) have a shutdown terminal for conserving battery life in

portable applications. When the shutdown terminal is tied low, the supply current is reduced to just nano amps

per channel, the amplifier is disabled, and the outputs are placed in a high impedance mode. In order to save

power in shutdown mode, an external pullup resistor is required, thererfore, to enable the amplifier the shutdown

terminal must be pulled high. When the shutdown terminal is left floating, care should be taken to ensure that

parasitic leakage current at the shutdown terminal does not inadvertently place the operational amplifier into

shutdown.

driving a capacitive load

When the amplifier is configured in this manner, capacitive loading directly on the output will decrease the

device’s phase margin leading to high frequency ringing or oscillations. Therefore, for capacitive loads of greater

than 1 nF, it is recommended that a resistor be placed in series (RNULL) with the output of the amplifier, as shown

in Figure 24. A maximum value of 20 Ω should work well for most applications.

RF RF

RG RG

Input – RNULL Input – RNULL

Output Output

+ +

RL CLOAD Snubber RL CL

C

(a) (b)

Figure 24. Driving a Capacitive Load

offset voltage

The output offset voltage, (VOO) is the sum of the input offset voltage (VIO) and both input bias currents (IIB) times

the corresponding gains. The following schematic and formula can be used to calculate the output offset

voltage:

RF

IIB–

RG

+ –

VI VO

+

RS

ǒ ǒ ǓǓ ǒ ǒ ǓǓ

IIB+

V

OO

+ VIO 1 ) R

R

F " IIB) RS 1 ) R

R

F " IIB– RF

G G

Figure 25. Output Offset Voltage Model

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 11

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

_ Rnull

+

RL CL

Figure 26

general power design considerations

When driving heavy loads at high junction temperatures there is an increased probability of electromigration

affecting the long term reliability of ICs. Therefore for this not to be an issue either

D the output current must be limited (at these high junction temperatures) or

D the junction temperature must be limited.

The maximum continuous output current at a die temperature 150°C will be 1/3 of the current at 105°C.

The junction temperature will be dependent on the ambient temperature around the IC, thermal impedance from

the die to the ambient and power dissipated within the IC.

TJ = TA + θJA × PDIS

Where

PDIS is the IC power dissipation and is equal to the output current multiplied by the voltage dropped across the

output of the IC.

θJA is the thermal impedance between the junction and the ambient temperature of the IC.

TJ is the junction temperature.

TA is the ambient temperature.

Reducing one or more of these factors will result in a reduced die temperature. The 8-pin SOIC (small outline

integrated circuit) has a thermal impedance from junction to ambient of 176°C/W. For this reason we

recommend that the maximum power dissipation of the 8-pin SOIC package be limited to 350 mW, with peak

dissipation of 700 mW as long as the RMS value is less than 350 mW.

The use of the MSOP PowerPAD dramatically reduces the thermal impedance from junction to case. And with

correct mounting, the reduced thermal impedance will greatly increase the IC’s permissible power dissipation

and output current handling capability. For example, the power dissipation of the PowerPAD is increased to

above 1 W. Sinusoidal and pulse-width modulated output signals will also increase the output current capability.

The equivalent dc current is proportional to the square-root of the duty cycle:

I

DC(EQ)

+ ICont Ǹ(duty cycle)

CURRENT DUTY CYCLE EQUIVALENT DC CURRENT

AT PEAK RATED CURRENT AS A PERCENTAGE OF PEAK

100 100

70 84

50 71

Note that with an operational amplifier, a duty cycle of 70% would often result in the op amp sourcing current

70% of the time and sinking current 30%, therefore, the equivalent dc current would still be 0.84 times the

continuous current rating at a particular junction temperature.

12 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

general PowerPAD design considerations

The TLV411x is available in a thermally-enhanced PowerPAD family of packages. These packages are

constructed using a downset leadframe upon which the die is mounted [see Figure 27(a) and Figure 27(b)]. This

arrangement results in the lead frame being exposed as a thermal pad on the underside of the package [see

Figure 27(c)]. Because this thermal pad has direct thermal contact with the die, excellent thermal performance

can be achieved by providing a good thermal path away from the thermal pad.

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation.

During the surface-mount solder operation (when the leads are being soldered), the thermal pad can also be

soldered to a copper area underneath the package. Through the use of thermal paths within this copper area,

heat can be conducted away from the package into either a ground plane or other heat dissipating device.

The PowerPAD package represents a breakthrough in combining the small area and ease of assembly of

surface mount with the, heretofore, awkward mechanical methods of heatsinking.

DIE

Side View (a) Thermal

Pad

DIE

End View (b) Bottom View (c)

NOTE A: The thermal pad is electrically isolated from all terminals in the package.

Figure 27. Views of Thermally Enhanced DGN Package

Although there are many ways to properly heatsink the PowerPAD package, the following steps illustrate the

recommended approach.

Thermal Pad Area

Single or Dual

68 mils x 70 mils) with 5 vias

(Via diameter = 13 mils

Figure 28. PowerPAD PCB Etch and Via Pattern

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 13

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

general PowerPAD design considerations (continued)

1. Prepare the PCB with a top side etch pattern as shown in Figure 28. There should be etch for the leads as

well as etch for the thermal pad.

2. Place five holes (dual) or nine holes (quad) in the area of the thermal pad. These holes should be 13 mils

in diameter. Keep them small so that solder wicking through the holes is not a problem during reflow.

3. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. This helps

dissipate the heat generated by the TLV411x IC. These additional vias may be larger than the 13-mil

diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad

area to be soldered so that wicking is not a problem.

4. Connect all holes to the internal ground plane.

5. When connecting these holes to the ground plane, do not use the typical web or spoke via connection

methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat

transfer during soldering operations. This makes the soldering of vias that have plane connections easier.

In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore,

the holes under the TLV411x PowerPAD package should make their connection to the internal ground plane

with a complete connection around the entire circumference of the plated-through hole.

6. The top-side solder mask should leave the terminals of the package and the thermal pad area with its five

holes (dual) or nine holes (quad) exposed. The bottom-side solder mask should cover the five or nine holes

of the thermal pad area. This prevents solder from being pulled away from the thermal pad area during the

reflow process.

7. Apply solder paste to the exposed thermal pad area and all of the IC terminals.

8. With these preparatory steps in place, the TLV411x IC is simply placed in position and run through the solder

ǒ Ǔ

reflow operation as any standard surface-mount component. This results in a part that is properly installed.

For a given θJA, the maximum power dissipation is shown in Figure 30 and is calculated by the following formula:

P

D

+ T –T

MAX A

q JA

Where:

PD = Maximum power dissipation of TLV411x IC (watts)

TMAX = Absolute maximum junction temperature (150°C)

TA = Free-ambient air temperature (°C)

θJA = θJC + θCA

θJC = Thermal coefficient from junction to case

θCA = Thermal coefficient from case to ambient air (°C/W)

14 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

general PowerPAD design considerations (continued)

MAXIMUM POWER DISSIPATION

vs

FREE-AIR TEMPERATURE

4

TJ = 150°C

Maximum Power Dissipation – W 3.5

DGN Package

3 Low-K Test PCB

θJA = 52.7°C/W

2.5 PDIP Package

Low-K Test PCB

θJA = 104°C/W

2

SOIC Package

Low-K Test PCB

1.0 θJA = 176°C/W

0.5

0

–55 –40 –25 –10 5 20 35 50 65 80 95 110 125

TA – Free-Air Temperature – °C

NOTE A: Results are with no air flow and using JEDEC Standard Low-K test PCB.

Figure 29. Maximum Power Dissipation vs Free-Air Temperature

The next consideration is the package constraints. The two sources of heat within an amplifier are quiescent

power and output power. The designer should never forget about the quiescent heat generated within the

device, especially muti-amplifier devices. Because these devices have linear output stages (Class A-B), most

of the heat dissipation is at low output voltages with high output currents.

The other key factor when dealing with power dissipation is how the devices are mounted on the PCB. The

PowerPAD devices are extremely useful for heat dissipation. But, the device should always be soldered to a

copper plane to fully use the heat dissipation properties of the PowerPAD. The SOIC package, on the other

hand, is highly dependent on how it is mounted on the PCB. As more trace and copper area is placed around

the device, θJA decreases and the heat dissipation capability increases. The currents and voltages shown in

these graphs are for the total package. For the dual or quad amplifier packages, the sum of the RMS output

currents and voltages should be used to choose the proper package.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 15

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

APPLICATION INFORMATION

macromodel information

Macromodel information provided was derived using Microsim Parts , the model generation software used

with Microsim PSpice . The Boyle macromodel (see Note 3) and subcircuit in Figure 30 are generated using

the TLV411x typical electrical and operating characteristics at TA = 25°C. Using this information, output

simulations of the following key parameters can be generated to a tolerance of 20% (in most cases):

D Maximum positive output voltage swing D Unity-gain frequency

D Maximum negative output voltage swing D Common-mode rejection ratio

D Slew rate D Phase margin

D Quiescent power dissipation D DC output resistance

D Input bias current D AC output resistance

D Open-loop voltage amplification D Short-circuit output current limit

NOTE 3: G. R. Boyle, B. M. Cohn, D. O. Pederson, and J. E. Solomon, “Macromodeling of Integrated Circuit Operational Amplifiers,” IEEE Journal

of Solid-State Circuits, SC-9, 353 (1974).

3 99

VDD

+

rd1 rd2 rss css egnd fb ro2

rp

c1 –

7

11 12 +

1 c2 vlim

IN+ + 9 r2 6

–

vc

D D + 8

–

2 vb ga

G G

IN– 53 – gcm ioff ro1

S S

OUT

dp dlp dln 5

10 91 90 92

iss dc + + –

vlp hlim vln

GND – – +

4 – + 54

ve de

* TLV4112_5V operational amplifier ”macromodel” subcircuit iss 10 4 dc 13.800E–6

* updated using Model Editor release 9.1 on 01/18/00 at 15:50 hlim 90 0 vlim 1K

Model Editor is an OrCAD product. ioff 0 6 dc 75E–9

* j1 11 2 10 jx1

* connections: non–inverting input J2 12 1 10 jx2

* | inverting input r2 6 9 100.00E3

* | | positive power supply rd1 3 11 5.9386E3

* | | | negative power supply rd2 3 12 5.9386E3

* | | | | output ro1 8 5 10

* || | | | ro2 7 99 10

.subckt TLV4112_5V 12345 rp 3 4 3.3333E3

* rss 10 99 14.493E6

c1 11 12 2.2439E–12 vb 9 0 dc 0

c2 6 7 10.000E–12 vc 3 53 dc .86795

css 10 99 454.55E–15 ve 54 4 dc .86795

dc 5 53 dy vlim 7 8 dc 0

de 54 5 dy vlp 91 0 dc 300

dlp 90 91 dx vln 0 92 dc 300

dln 92 90 dx .model dx D(Is=800.00E–18)

dp 4 3 dx .model dy D(Is=800.00E–18 Rs=1m Cjo=10p)

egnd 99 0 poly(2) (3,0) (4,0) 0 .5 .5 .model jx1 NJF(Is=150.00E–12 Beta=2.0547E–3 +Vto=–1)

fb 7 99 poly(5) vb vc ve vlp vln 0 .model jx2 NJF(Is=150.00E–12 Beta=2.0547E–3 + Vto=–1)

+ 33.395E6 –1E3 1E3 33E6 –33E6 .ends

ga 6 0 11 12 168.39E–6 *$

gcm 0 6 10 99 168.39E–12

Figure 30. Boyle Macromodel and Subcircuit

PSpice and Parts are trademarks of MicroSim Corporation.

16 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

MECHANICAL DATA

D (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

14 PIN SHOWN

0.050 (1,27)

0.020 (0,51)

0.010 (0,25) M

0.014 (0,35)

14 8

0.008 (0,20) NOM

0.244 (6,20)

0.228 (5,80)

0.157 (4,00)

0.150 (3,81)

Gage Plane

0.010 (0,25)

1 7

0°– 8°

0.044 (1,12)

A 0.016 (0,40)

Seating Plane

0.010 (0,25) 0.004 (0,10)

0.069 (1,75) MAX

0.004 (0,10)

PINS **

8 14

DIM

0.197 0.344

A MAX

(5,00) (8,75)

0.189 0.337

A MIN

(4,80) (8,55)

4040047 / D 10/96

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-012

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 17

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

MECHANICAL INFORMATION

DGN (S-PDSO-G8) PowerPAD PLASTIC SMALL-OUTLINE PACKAGE

0,38

0,65 0,25 M

0,25

8 5

Thermal Pad

(See Note D)

0,15 NOM

3,05 4,98

2,95 4,78

Gage Plane

0,25

1 4 0°– 6°

0,69

3,05 0,41

2,95

Seating Plane

0,15

1,07 MAX 0,10

0,05

4073271/A 04/98

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions include mold flash or protrusions.

D. The package thermal performance may be enhanced by attaching an external heat sink to the thermal pad.

This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

E. Falls within JEDEC MO-187

PowerPAD is a trademark of Texas Instruments.

18 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

MECHANICAL INFORMATION

N (R-PDIP-T**) PLASTIC DUAL-IN-LINE PACKAGE

16 PIN SHOWN

PINS **

14

DIM

0.775

A A MAX

(19,69)

16 9 0.745

A MIN

(18,92)

0.260 (6,60)

0.240 (6,10)

1 8

0.070 (1,78) MAX

0.310 (7,87)

0.035 (0,89) MAX 0.020 (0,51) MIN

0.290 (7,37)

0.200 (5,08) MAX

Seating Plane

0.125 (3,18) MIN

0.100 (2,54)

0°– 15°

0.021 (0,53)

0.010 (0,25) M 0.010 (0,25) NOM

0.015 (0,38)

14/18 PIN ONLY

4040049/C 08/95

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 19

TLV4110, TLV4111, TLV4112, TLV4113

FAMILY OF HIGH OUTPUT DRIVE OPERATIONAL

AMPLIFIERS WITH SHUTDOWN

SLOS289A – DECEMBER 1999 – REVISED APRIL 2000

MECHANICAL INFORMATION

P (R-PDIP-T8) PLASTIC DUAL-IN-LINE PACKAGE

0.400 (10,60)

0.355 (9,02)

8 5

0.260 (6,60)

0.240 (6,10)

1 4

0.070 (1,78) MAX

0.310 (7,87)

0.020 (0,51) MIN

0.290 (7,37)

0.200 (5,08) MAX

Seating Plane

0.125 (3,18) MIN

0.100 (2,54) 0°– 15°

0.021 (0,53)

0.010 (0,25) M

0.015 (0,38) 0.010 (0,25) NOM

4040082 / B 03/95

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001

20 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

S-ar putea să vă placă și

- TLC27L4, TLC27L4A, TLC27L4B, TLC27L4Y, TLC27L9 Lincmos Precision Quad Operational AmplifiersDocument43 paginiTLC27L4, TLC27L4A, TLC27L4B, TLC27L4Y, TLC27L9 Lincmos Precision Quad Operational AmplifiersMedo AntikaÎncă nu există evaluări

- TLC 27 L 4Document44 paginiTLC 27 L 4Hendra KosasihÎncă nu există evaluări

- D D D D D D D D: Peripheral Drivers For High-Voltage High-Current Driver ApplicationsDocument16 paginiD D D D D D D D: Peripheral Drivers For High-Voltage High-Current Driver ApplicationsTiago PremerlÎncă nu există evaluări

- Low Power Jfet Input Operational Amplifiers: Semiconductor Technical DataDocument12 paginiLow Power Jfet Input Operational Amplifiers: Semiconductor Technical DataRama Tenis CopecÎncă nu există evaluări

- Electrical Knowledge Base - Quad General Purpose Operational AmplifierDocument5 paginiElectrical Knowledge Base - Quad General Purpose Operational AmplifierRobert GargetÎncă nu există evaluări

- UWR Series: Single Output, High Reliability, 2" X 2", 14-20 Watt, DC/DC ConvertersDocument7 paginiUWR Series: Single Output, High Reliability, 2" X 2", 14-20 Watt, DC/DC ConvertersAsad AhmedÎncă nu există evaluări

- Features Description: D D D DDocument25 paginiFeatures Description: D D D DDavid O'NeillÎncă nu există evaluări

- LM 3900Document16 paginiLM 3900Anderson gonçalvesÎncă nu există evaluări

- D D D D D D D: LM2900, LM3900 Quadruple Norton Operational AmplifiersDocument16 paginiD D D D D D D: LM2900, LM3900 Quadruple Norton Operational AmplifiersjoelpalzaÎncă nu există evaluări

- LM 3900Document16 paginiLM 3900Fredy CasillaÎncă nu există evaluări

- TLC274, TLC274A, TLC274B, TLC274Y, TLC279 Lincmos Precision Quad Operational AmplifiersDocument42 paginiTLC274, TLC274A, TLC274B, TLC274Y, TLC279 Lincmos Precision Quad Operational AmplifiersrobertodexÎncă nu există evaluări

- LF441CNDocument10 paginiLF441CNingucvÎncă nu există evaluări

- 2A H-Bridge Driver: Features DescriptionDocument5 pagini2A H-Bridge Driver: Features DescriptionSero StivÎncă nu există evaluări

- uA9637AC Dual Differential Line Receiver: DescriptionDocument12 paginiuA9637AC Dual Differential Line Receiver: DescriptionMa GabbyÎncă nu există evaluări

- TLC4501 OpampDocument38 paginiTLC4501 OpampCartoon KidsÎncă nu există evaluări

- Display Panel Voltmeter DMS-40PC PDFDocument6 paginiDisplay Panel Voltmeter DMS-40PC PDFafonsomoutinhoÎncă nu există evaluări

- Step-Up DC-DC MAX8752Document13 paginiStep-Up DC-DC MAX8752Peter PicalÎncă nu există evaluări

- D D D D D D D: MC3487 Quadruple Differential Line DriverDocument7 paginiD D D D D D D: MC3487 Quadruple Differential Line DriverRichard Andrianjaka LuckyÎncă nu există evaluări

- Amoled Driver IC tps65138Document24 paginiAmoled Driver IC tps65138analog changeÎncă nu există evaluări

- Not Recommended For New Designs: UWR SeriesDocument7 paginiNot Recommended For New Designs: UWR SeriesAsad AhmedÎncă nu există evaluări

- In-Plug Series: IPS201: Revision 4Document10 paginiIn-Plug Series: IPS201: Revision 4chafic WEISSÎncă nu există evaluări

- Max8901 Max8901bDocument14 paginiMax8901 Max8901bPM AlejandroÎncă nu există evaluări

- Opa 445Document28 paginiOpa 445Be OshoÎncă nu există evaluări

- srv25 4Document9 paginisrv25 4Aditya SrivatsavÎncă nu există evaluări

- TL 496Document7 paginiTL 496Emiliano CuscuetaÎncă nu există evaluări

- Universal Temperature Converter KFD2-UT2-2: FunctionDocument4 paginiUniversal Temperature Converter KFD2-UT2-2: FunctionAlamsyah SyamsuddinÎncă nu există evaluări

- Features Applications: D D D D D D D D D D D D D D DDocument15 paginiFeatures Applications: D D D D D D D D D D D D D D DĐịnh Xuân HàÎncă nu există evaluări

- Data Acquisition and Control Interface: Transformer 5Document8 paginiData Acquisition and Control Interface: Transformer 5Nobin ahmedÎncă nu există evaluări

- SAE J1772-Compliant Electric Vehicle Service Equipment Reference Design For Level 1 and 2 EV ChargerDocument38 paginiSAE J1772-Compliant Electric Vehicle Service Equipment Reference Design For Level 1 and 2 EV ChargerErik SolisÎncă nu există evaluări

- D D D D D D: NE556, SA556, SE556 Dual Precision TimersDocument5 paginiD D D D D D: NE556, SA556, SE556 Dual Precision TimerssomtchekusÎncă nu există evaluări

- Tps 2044548Document29 paginiTps 2044548NJ BorgesÎncă nu există evaluări

- Single Supply, Low Power Dual Comparators: Semiconductor Technical DataDocument6 paginiSingle Supply, Low Power Dual Comparators: Semiconductor Technical DataNick DÎncă nu există evaluări

- Current Driver/Repeater KFD0-CS-Ex2.51P: FunctionDocument4 paginiCurrent Driver/Repeater KFD0-CS-Ex2.51P: FunctionMas AgusÎncă nu există evaluări

- DC Isolating Transmitter Kusam MecoDocument2 paginiDC Isolating Transmitter Kusam MecoindustrialindiaÎncă nu există evaluări

- Features Description: D D D D D D D D D D D D D D D DDocument24 paginiFeatures Description: D D D D D D D D D D D D D D D DHammer CarabaliÎncă nu există evaluări

- Switch Amplifier KFD2-ST2-Ex1.LB: FunctionDocument5 paginiSwitch Amplifier KFD2-ST2-Ex1.LB: Functionk OÎncă nu există evaluări

- Universal Temperature Converter KFD2-UT2-Ex1: FunctionDocument5 paginiUniversal Temperature Converter KFD2-UT2-Ex1: FunctionsadeghebrdvrÎncă nu există evaluări

- Opa 37Document24 paginiOpa 37tpf2312Încă nu există evaluări

- Opa 37Document24 paginiOpa 37asp.tec06Încă nu există evaluări

- Power Factor Corrector: 1 FeaturesDocument13 paginiPower Factor Corrector: 1 Featuresdeilyn rivasÎncă nu există evaluări

- Pin Connections: Order This Document by MC34181/DDocument12 paginiPin Connections: Order This Document by MC34181/DCharbel TadrosÎncă nu există evaluări

- TLC555CPDocument20 paginiTLC555CPmadindeheadÎncă nu există evaluări

- SC452 Dual Phase Single Chip IMVP 6 VcorDocument37 paginiSC452 Dual Phase Single Chip IMVP 6 VcorspotÎncă nu există evaluări

- Programmable Switching D.C. Power SupplyDocument1 paginăProgrammable Switching D.C. Power SupplyRAPETI SAI KUMAR (N160490)Încă nu există evaluări

- DV 610av S PDFDocument74 paginiDV 610av S PDFkumbrovÎncă nu există evaluări

- Non-Isolated Led Lighting Drive Ic With Built-In High-Voltage Mosfet, High PFC and High Constant Current AccuracyDocument4 paginiNon-Isolated Led Lighting Drive Ic With Built-In High-Voltage Mosfet, High PFC and High Constant Current AccuracyRRCServiceTeam AhmedabadÎncă nu există evaluări

- OP07 Opamp Is Still EvolvingDocument8 paginiOP07 Opamp Is Still EvolvingSuresh - Vispra solarÎncă nu există evaluări

- MST6M181VSDocument9 paginiMST6M181VSWitFÎncă nu există evaluări

- TDA8359JDocument21 paginiTDA8359JCesar HernandezÎncă nu există evaluări

- Triple Output: 8-11 Watt, DC/DC ConvertersDocument5 paginiTriple Output: 8-11 Watt, DC/DC ConvertersDaniel Martinez CollazoÎncă nu există evaluări

- Power Amplifier: Toa 900 Series IiDocument12 paginiPower Amplifier: Toa 900 Series IiRamiro Gonzalez MÎncă nu există evaluări

- Page 2Document1 paginăPage 2PeterÎncă nu există evaluări

- Iso1176 PDFDocument39 paginiIso1176 PDFshekoofe danaÎncă nu există evaluări

- SMART Transmitter Power Supply KFD2-STC5-Ex2: FunctionDocument5 paginiSMART Transmitter Power Supply KFD2-STC5-Ex2: FunctionRavi Kant GuptaÎncă nu există evaluări

- RC 4136Document9 paginiRC 4136message2tejaÎncă nu există evaluări

- RC4136 etcTIDocument8 paginiRC4136 etcTIJoimir PerezÎncă nu există evaluări

- Single Line Diagram 1 MV Softstater Drive 2 Unit Medium VOltage AC MotorDocument1 paginăSingle Line Diagram 1 MV Softstater Drive 2 Unit Medium VOltage AC MotorJohan HendrawanÎncă nu există evaluări

- Quantities Survey MethodsDocument73 paginiQuantities Survey MethodsparvezÎncă nu există evaluări

- Physical Quantities and Unit: 9th GradeDocument28 paginiPhysical Quantities and Unit: 9th GradeAlexanderÎncă nu există evaluări

- Awodey, Categories For Everybody - PsDocument196 paginiAwodey, Categories For Everybody - PsΣωτήρης Ντελής100% (3)

- Hot and Cold ApplicDocument33 paginiHot and Cold Appliccamille_12_15100% (1)

- Automatic Pneumatic Bumper Mission: International Journal of Pure and Applied Mathematics No. 16 2017, 137-140Document4 paginiAutomatic Pneumatic Bumper Mission: International Journal of Pure and Applied Mathematics No. 16 2017, 137-140VinayÎncă nu există evaluări

- Python Unit 1Document18 paginiPython Unit 1Rtr. Venkata chetan Joint secretaryÎncă nu există evaluări

- An Experimental Analysis of Clustering Algorithms in Data Mining Using Weka ToolDocument6 paginiAn Experimental Analysis of Clustering Algorithms in Data Mining Using Weka Toolmishranamit2211Încă nu există evaluări

- Nav 2000Document4 paginiNav 2000Balaji TriplantÎncă nu există evaluări

- TOFD Dead Zone CalculatorDocument4 paginiTOFD Dead Zone CalculatorWill SmithÎncă nu există evaluări

- FlopX NT5.1 Patch V1aDocument5 paginiFlopX NT5.1 Patch V1aAmilcar AndradeÎncă nu există evaluări

- W.R. Klemm (Auth.) - Atoms of Mind - The - Ghost in The Machine - Materializes-Springer Netherlands (2011)Document371 paginiW.R. Klemm (Auth.) - Atoms of Mind - The - Ghost in The Machine - Materializes-Springer Netherlands (2011)El equipo de Genesis ProjectÎncă nu există evaluări

- JPSP - 2022 - 698Document10 paginiJPSP - 2022 - 698hifeztobgglÎncă nu există evaluări

- Chem Cheat Sheet MasterDocument6 paginiChem Cheat Sheet MasteradamhamelehÎncă nu există evaluări

- 00.concrete Mix Design-RailwayDocument38 pagini00.concrete Mix Design-RailwaySoundar PachiappanÎncă nu există evaluări

- Hazardous Area ClassificationDocument36 paginiHazardous Area Classificationvenkeeku100% (1)

- Gas Welding Equipment PowerpointDocument12 paginiGas Welding Equipment PowerpointChristian RexÎncă nu există evaluări

- FP - ES - 28 - Rindu Grahabhakti Intani - PERMEABLE ENTRY CHARACTERIZATION AT DARAJAT FIELD, WEST JAVA PDFDocument4 paginiFP - ES - 28 - Rindu Grahabhakti Intani - PERMEABLE ENTRY CHARACTERIZATION AT DARAJAT FIELD, WEST JAVA PDFrindu_intaniÎncă nu există evaluări

- Math Formula SheetDocument8 paginiMath Formula SheetHidayah TeacherÎncă nu există evaluări

- DS1103 Datasheet PDFDocument6 paginiDS1103 Datasheet PDFRosario RiveraÎncă nu există evaluări

- Os ND06Document3 paginiOs ND06kevinbtechÎncă nu există evaluări

- Solution Manual For Investment Science by David LuenbergerDocument94 paginiSolution Manual For Investment Science by David Luenbergerkoenajax96% (28)

- C V RamanDocument8 paginiC V RamanJayesh KomalwarÎncă nu există evaluări

- PR100 BrochureDocument28 paginiPR100 Brochuregus289Încă nu există evaluări

- Psychometric Development and Validation of GaslightingDocument15 paginiPsychometric Development and Validation of GaslightingYang ZhangÎncă nu există evaluări

- Form in MusicDocument8 paginiForm in MusicAndri KurniawanÎncă nu există evaluări

- 16 - Bit RISC Processor Design For Convolution Application Using Verilog HDLDocument64 pagini16 - Bit RISC Processor Design For Convolution Application Using Verilog HDLchandra sekhar100% (1)

- Introduction To DatabasesDocument33 paginiIntroduction To Databases米皮皮Încă nu există evaluări

- Biomechanics of The KneeDocument8 paginiBiomechanics of The KneeJorge LopezÎncă nu există evaluări

- Presentation: Isa Test Sets Training Course - 2014Document5 paginiPresentation: Isa Test Sets Training Course - 2014Sultan Uddin KhanÎncă nu există evaluări