Documente Academic

Documente Profesional

Documente Cultură

Flip Flop RS (4.2)

Încărcat de

gerarb19Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Flip Flop RS (4.2)

Încărcat de

gerarb19Drepturi de autor:

Formate disponibile

Flip Flop tipo RS.

Objetivo: comprender el funcionamiento del Flip – Flop RS.

Consideraciones teóricas: El flip flop RS es el más sencillo y recibe su nombre de sus

entradas, Set y Reset. El circuito básico para la implementación del latch RS empleando

compuertas nand se muestra en la figura 1.1 (4.2)

Figura 1.1 (4.2)

Primero analizaremos el comportamiento del latch tipo RS, para eso procederemos a

llenar su tabla de verdad, la cual se muestra en 1.2 (4.2)

N R S Q Q́

0 0 1

1 0 0 Tabla 1.1 (4.2)

2 1 0

3 0 0

4 1 1

Al ejecutar los estados de la tabla de valores obtenemos lo siguientes estados cuales se

muestran en la figura 1.3 (4.2)

a) Figura 1.2 (4.2)

b) Figura 1.2 (4.2)

c) Figura 1.2 (4.2)

d) Figura 1.2 (4.2)

e) Figura 1.2 (4.2)

Del latch RS obtenemos la siguiente tabla de verdad

R S Q Q́

FIJAR 0 1 1 0

MEMORI 0 0 Estado anterior

A

BORRAR 1 0 0 1 Tabla 1.2 (4.2)

MEMORI 0 0 Estado anterior Flip- Flop RS con Reloj

A

1 1 Indefinido El circuito RS con reloj se observa

en la figura 1.3 (4.1)

Figura 1.3 (4.2)

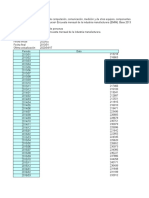

Tabla de verdad:

Q S R

0 0 0 0

1 0 0 1 Tabla 1.3 (4.2)

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

Al ejecutar el estado 1 obtenemos:

Figura 1.4 (4.2)

El estado número 2 es (1,0), pero podemos observar de la tabla 1.2 (4.2) que (1,0) Es

fijar, es decir, Q=1 por lo tanto tenemos lo siguiente:

Figura 1.5 (4.2)

De la figura 1.5 (4.2) podemos observar que Q= 1 por lo tanto saltaremos al estado

número 4 (0,0):

De la tabla 1.2 (4.2) podemos observar que (0,0) es memoria por lo tanto obtendremos el

mismo valor:

Figura 1.6 (4.2)

Finalmente al ejecutar el estado número 6 obtenemos:

Figura 1.7 (4.2)

De la tabla 1.2 (4.2) podemos observar que cuando R y S, son igual a 1 obtenemos un estado

indefinido por lo tanto nuestra tabla de valores queda de la siguiente manera:

Q S R Q(T+1)

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 INDETERMINDADO Al pasar la tabla 1.4

1 0 0 1 (4.2) a un mapa de

Tabla 1.4 (4.2)

1 0 1 0 karnaugh

1 1 0 1 obtenemos la

1 1 1 INDETERMINADO siguiente expresión

Booleana:

Q (t+1) = S + Q Ŕ Ecuación 1.4 (4.2)

S-ar putea să vă placă și

- Practica Contador 7490Document7 paginiPractica Contador 7490Arnoldo ZereceroÎncă nu există evaluări

- Laboratorio de Codificador y DecodificadorDocument11 paginiLaboratorio de Codificador y DecodificadorRonald Martínez RiveraÎncă nu există evaluări

- Lab N 7 Electronica DigitalDocument7 paginiLab N 7 Electronica DigitalSan Maycol FielÎncă nu există evaluări

- Diagrama Multiplexor 74151 de 8 A 1Document4 paginiDiagrama Multiplexor 74151 de 8 A 1Crhistian Gopar Rodriguez100% (1)

- Configuracion CascadaDocument7 paginiConfiguracion CascadaKely Estefani Alcántara PinedoÎncă nu există evaluări

- Funcionamiento de flip-flops y registros digitalesDocument11 paginiFuncionamiento de flip-flops y registros digitalesBilly Markos Felix GutierrezÎncă nu există evaluări

- SENA automatismo selladoDocument15 paginiSENA automatismo selladoDeiby FernandoÎncă nu există evaluări

- Lab 4 - ADC-DAC-2018 - 2Document3 paginiLab 4 - ADC-DAC-2018 - 2fieeg4Încă nu există evaluări

- Curvas I vs V en diodos, rectificadores y filtros RCDocument16 paginiCurvas I vs V en diodos, rectificadores y filtros RCAndrés YáñezÎncă nu există evaluări

- Circuitos secuencialesDocument4 paginiCircuitos secuencialesaparejat100% (1)

- Mux y DemuxDocument13 paginiMux y DemuxfrandyÎncă nu există evaluări

- Informe 7 PDFDocument2 paginiInforme 7 PDFMega descargasÎncă nu există evaluări

- Introducción al software Circuit Maker para simulación de circuitos eléctricosDocument11 paginiIntroducción al software Circuit Maker para simulación de circuitos eléctricosHECTOR GREGORIO QUISPE FLORESÎncă nu există evaluări

- Laboratorio Seguidor de LineaDocument16 paginiLaboratorio Seguidor de LineaDaniel ZapataÎncă nu există evaluări

- Informe 6Document2 paginiInforme 6Dario OroscoÎncă nu există evaluări

- Sistemas Programables Práctica #3Document4 paginiSistemas Programables Práctica #3Jesus Solis CervantesÎncă nu există evaluări

- Proyecto Circuito Contador AutomaticoDocument4 paginiProyecto Circuito Contador AutomaticoSantiago Xavier Yepez LeitonÎncă nu există evaluări

- Implementación de una cerradura con huellas dactilaresDocument7 paginiImplementación de una cerradura con huellas dactilaresHugo Anthony Delgado SantanaÎncă nu există evaluări

- Laboratoriio #7 - Contadores - v2017Document16 paginiLaboratoriio #7 - Contadores - v2017carlos sanchezÎncă nu există evaluări

- Informe N°2 Latch y Flip FlopDocument6 paginiInforme N°2 Latch y Flip FlopranmelasÎncă nu există evaluări

- Código HammingDocument3 paginiCódigo HammingandresspatooÎncă nu există evaluări

- Mux y DemuxDocument13 paginiMux y DemuxfrandyÎncă nu există evaluări

- Practica 2 DisplayDocument2 paginiPractica 2 DisplayKevin DavidÎncă nu există evaluări

- PRACTICA InductanciaDocument6 paginiPRACTICA InductanciaLeidy RuizÎncă nu există evaluări

- Lab 12Document15 paginiLab 12Yosimar Antonio Martel HuertasÎncă nu există evaluări

- Andy Ramirez Parte III InteresanteDocument25 paginiAndy Ramirez Parte III InteresanteGERARDO CABRERAÎncă nu există evaluări

- Amplificadores OperacionalesDocument4 paginiAmplificadores OperacionalesCesar AndresÎncă nu există evaluări

- Circuito Integrado 74155.74154Document6 paginiCircuito Integrado 74155.74154Pao GómezÎncă nu există evaluări

- Circuitos Logicos MsiDocument32 paginiCircuitos Logicos MsiAndrés ArbeláezÎncă nu există evaluări

- Amplificadores Operacionales para Acondicionamiento de SeñalesDocument16 paginiAmplificadores Operacionales para Acondicionamiento de SeñalesSevas MarcosÎncă nu există evaluări

- Polos y CerosDocument18 paginiPolos y Cerosramon infanteÎncă nu există evaluări

- Laboratorio de Circuitos DigitalesDocument2 paginiLaboratorio de Circuitos DigitalesEdward Martin Julca SánchezÎncă nu există evaluări

- Informe de Reloj Digital DDocument17 paginiInforme de Reloj Digital DRenato TrujilloÎncă nu există evaluări

- FLIP Flop RsDocument4 paginiFLIP Flop RsEgtm Tmeg100% (1)

- Lab #1 - Compuertas Lógicas - Tabla de Verdad (Recuperado Automáticamente)Document5 paginiLab #1 - Compuertas Lógicas - Tabla de Verdad (Recuperado Automáticamente)ZAITÎncă nu există evaluări

- Practica-Convertidores ADC y DAC - I UNIDADDocument8 paginiPractica-Convertidores ADC y DAC - I UNIDADBryanMendezReynosoÎncă nu există evaluări

- Informe 1 PotenciaDocument3 paginiInforme 1 PotenciaDanny MantillaÎncă nu există evaluări

- Informe de Laboratorio DecodificadoresDocument7 paginiInforme de Laboratorio DecodificadoresAndres DGÎncă nu există evaluări

- Informe Final Laboratorio N - 3Document18 paginiInforme Final Laboratorio N - 3Michael Alexander0% (1)

- LatchesDocument9 paginiLatchesFabio LópezÎncă nu există evaluări

- Lab 08 " (B) Tratamiento de Señales Analógicas" COMPACDocument9 paginiLab 08 " (B) Tratamiento de Señales Analógicas" COMPACAlberto Miguel Quispe LimaÎncă nu există evaluări

- Practica Lab5Document3 paginiPractica Lab5Jhon Anghel PeñalozaÎncă nu există evaluări

- Proyecto Básico Con PICDocument3 paginiProyecto Básico Con PICOscar Ramos VeraÎncă nu există evaluări

- Microprocesadores-II: Interfaz Paralela Programable 8255Document12 paginiMicroprocesadores-II: Interfaz Paralela Programable 8255O GAÎncă nu există evaluări

- Tabla Comparativa de Las Compuertas Logicas PDFDocument6 paginiTabla Comparativa de Las Compuertas Logicas PDFKarla Yalmeth Figueredo CoronadoÎncă nu există evaluări

- Sumador RestadorDocument16 paginiSumador RestadorOsky Qe'100% (1)

- Circuito multiplexor división 3Document7 paginiCircuito multiplexor división 3Christian Barba Yañiquez33% (3)

- PRÁCTICA 9 FLIP-FLOPSDocument18 paginiPRÁCTICA 9 FLIP-FLOPSChamín AlcántaraÎncă nu există evaluări

- Oscilador Con UjtDocument3 paginiOscilador Con UjtLuisÎncă nu există evaluări

- Informe Previo 5Document13 paginiInforme Previo 5Felipe SanchezÎncă nu există evaluări

- Laboratorio de Logica CombinacionalDocument6 paginiLaboratorio de Logica CombinacionalAbimael Erasmo Huamani MallmaÎncă nu există evaluări

- Flip Flops D, J-K, y T.Document14 paginiFlip Flops D, J-K, y T.AnaKarenHsÎncă nu există evaluări

- Diseño de Una Puerta Electrónica para Un GarajeDocument7 paginiDiseño de Una Puerta Electrónica para Un GarajeTrabajos Academicos0% (1)

- Spasado15-2 ELT2590Document35 paginiSpasado15-2 ELT2590Elvis C CÎncă nu există evaluări

- Informe de CodificadorDocument19 paginiInforme de CodificadoreliseoÎncă nu există evaluări

- Contador de 0 A 9 Con Display de 7 Segmentos de Catodo ComúnDocument2 paginiContador de 0 A 9 Con Display de 7 Segmentos de Catodo ComúnPedro SánchezÎncă nu există evaluări

- Aplicaciones Basicas El Oscilador de Schmitt y Generador de FuncionesDocument8 paginiAplicaciones Basicas El Oscilador de Schmitt y Generador de FuncionesDiego CandoÎncă nu există evaluări

- Maquinas Secuenciales SincronicasDocument30 paginiMaquinas Secuenciales SincronicasIvanovichÎncă nu există evaluări

- Digitales 4Document7 paginiDigitales 4george guerraÎncă nu există evaluări

- Flip FLOPDocument8 paginiFlip FLOPCarlos RamosÎncă nu există evaluări

- Tipos de Sensores y de ContactoDocument2 paginiTipos de Sensores y de Contactogerarb19Încă nu există evaluări

- Parametro de RedDocument3 paginiParametro de Redgerarb19Încă nu există evaluări

- Derivadas (Calculo Diferencial)Document26 paginiDerivadas (Calculo Diferencial)gerarb19Încă nu există evaluări

- Simulaciones ProteusDocument3 paginiSimulaciones Proteusgerarb19Încă nu există evaluări

- Estadistica ProblemarioDocument8 paginiEstadistica Problemariogerarb19Încă nu există evaluări

- Programacion en #CDocument1 paginăProgramacion en #Cgerarb19Încă nu există evaluări

- Programacion en #CDocument1 paginăProgramacion en #Cgerarb19Încă nu există evaluări

- MecanicaDocument3 paginiMecanicagerarb19Încă nu există evaluări

- Mantiene Sistemas Electrónicos de Uso Industrial: ProfesorDocument4 paginiMantiene Sistemas Electrónicos de Uso Industrial: Profesorgerarb19Încă nu există evaluări

- Estadistica InferencialDocument3 paginiEstadistica Inferencialgerarb19Încă nu există evaluări

- Heroína DrogaDocument6 paginiHeroína Drogagerarb19Încă nu există evaluări

- Estadistica InferencialDocument3 paginiEstadistica Inferencialgerarb19Încă nu există evaluări

- Actividad 2 InegiDocument20 paginiActividad 2 Inegigerarb19Încă nu există evaluări

- Tarea Calculo Diferencial e IntegralDocument11 paginiTarea Calculo Diferencial e Integralgerarb19Încă nu există evaluări

- ProbabilidadDocument6 paginiProbabilidadgerarb19Încă nu există evaluări

- Tipos de Roles de TrabajoDocument7 paginiTipos de Roles de Trabajogerarb19Încă nu există evaluări

- ProbabilidadDocument6 paginiProbabilidadgerarb19Încă nu există evaluări

- Tarea Calculo DiferencialDocument8 paginiTarea Calculo Diferencialgerarb19Încă nu există evaluări

- Instrumentos de MedicionDocument10 paginiInstrumentos de Mediciongerarb19Încă nu există evaluări

- MDocument1 paginăMgerarb19Încă nu există evaluări

- Actividad 2 Inegi 2Document1 paginăActividad 2 Inegi 2gerarb19Încă nu există evaluări

- Liderazgo transformador: el tipo que contribuye al desarrollo integralDocument5 paginiLiderazgo transformador: el tipo que contribuye al desarrollo integralEmanuelenkov Dextrovich0% (1)

- FIDEOSDocument4 paginiFIDEOSgerarb19Încă nu există evaluări

- Heroína DrogaDocument6 paginiHeroína Drogagerarb19Încă nu există evaluări

- Trabajo ProbabilidadDocument7 paginiTrabajo Probabilidadgerarb19Încă nu există evaluări

- Universidad Tecnológica de Puebla: Nombre Del Estudiante Teléfono de Contacto Correo Electrónico EquipoDocument3 paginiUniversidad Tecnológica de Puebla: Nombre Del Estudiante Teléfono de Contacto Correo Electrónico Equipogerarb19Încă nu există evaluări

- Flip - Flop D (4.1)Document5 paginiFlip - Flop D (4.1)gerarb19Încă nu există evaluări

- Arquitectura de Los Controladores Logicos ProbamablesDocument3 paginiArquitectura de Los Controladores Logicos Probamablesgerarb19Încă nu există evaluări

- Tipos de Roles de TrabajoDocument7 paginiTipos de Roles de Trabajogerarb19Încă nu există evaluări

- Catalogo Alcodm Lamparas 2021Document84 paginiCatalogo Alcodm Lamparas 2021MOTORES, MOTORREDUCTORES Y COMPONENTES GUADALAJARAÎncă nu există evaluări

- Tarjeta Azul BBVA: Pagina 1 / 5Document5 paginiTarjeta Azul BBVA: Pagina 1 / 5José Manuel Perera GarcíaÎncă nu există evaluări

- ECONOMIADocument3 paginiECONOMIAJuliana CalderónÎncă nu există evaluări

- Informe DataminingDocument15 paginiInforme Dataminingluis mÎncă nu există evaluări

- Guía acústica 11Document11 paginiGuía acústica 11Luisa De La VegaÎncă nu există evaluări

- Guia 3 Mecanismos de Transporte Celular Grado SextoDocument5 paginiGuia 3 Mecanismos de Transporte Celular Grado SextoCarlos andres OcoroÎncă nu există evaluări

- Practica Distribuciones Numericas PDFDocument1 paginăPractica Distribuciones Numericas PDFGuillermo Canchaya Osorio100% (1)

- Las Matematicas en El PentagramaDocument8 paginiLas Matematicas en El PentagramaHector M. LLactaÎncă nu există evaluări

- Examen Parcial Curso: Procesos de Manufactura I CODIGO: MC-213 A/B/C Ciclo Academico: 2018 - 1Document20 paginiExamen Parcial Curso: Procesos de Manufactura I CODIGO: MC-213 A/B/C Ciclo Academico: 2018 - 1RicardoÎncă nu există evaluări

- Diapositivas Tesis UltimasDocument22 paginiDiapositivas Tesis UltimasVictor MoÎncă nu există evaluări

- Raz. Verbal I Guía Verano 2 2023 - 5Document3 paginiRaz. Verbal I Guía Verano 2 2023 - 5Jhade CruzÎncă nu există evaluări

- Memoria de Cálculo Estructural Prototipo 1N2R2B 51.11 M2Document29 paginiMemoria de Cálculo Estructural Prototipo 1N2R2B 51.11 M2Victor Alfonso Lopez OrtegaÎncă nu există evaluări

- Resumen 1o parcial IPC antiguaDocument18 paginiResumen 1o parcial IPC antiguaCecilia VillalbaÎncă nu există evaluări

- Sistema de Recolecion de Aguas ResidualesDocument39 paginiSistema de Recolecion de Aguas ResidualesMartin SalinasÎncă nu există evaluări

- Demo Vulcan Drill and Blast DetalleDocument30 paginiDemo Vulcan Drill and Blast DetalleKevin Sebastian Aldea PerezÎncă nu există evaluări

- Redvit ProyectoDocument14 paginiRedvit ProyectoYarinia MontesinosÎncă nu există evaluări

- Angulos en El Espacio - PoliedrosDocument10 paginiAngulos en El Espacio - PoliedrosMontt SenpaiÎncă nu există evaluări

- Catálogo de Empacadores y Accesorios de ProducciónDocument10 paginiCatálogo de Empacadores y Accesorios de ProducciónJuan PerezÎncă nu există evaluări

- Mio Cine TicaDocument77 paginiMio Cine TicaAnaÎncă nu există evaluări

- Fisica 3Document26 paginiFisica 3ronyÎncă nu există evaluări

- Espectroscopía atómica y molecularDocument6 paginiEspectroscopía atómica y molecularFranÎncă nu există evaluări

- Diccionario: Afinidad ElectrónicaDocument11 paginiDiccionario: Afinidad ElectrónicaBrayelis paola Quiroz torresÎncă nu există evaluări

- Paralaje Estelar, BesselDocument3 paginiParalaje Estelar, BesselDaniel MirandaÎncă nu există evaluări

- Horario de Clases 1er Ciclo 2022Document8 paginiHorario de Clases 1er Ciclo 2022Alfonso EspinozaÎncă nu există evaluări

- Medidas centrales zanahoriasDocument8 paginiMedidas centrales zanahoriasCarrillo JacÎncă nu există evaluări

- Polietileno espumado para aislamiento térmico y acústicoDocument1 paginăPolietileno espumado para aislamiento térmico y acústicoJohana GiraldoÎncă nu există evaluări

- Ventajas, desventajas y opinión de corrientes filosóficasDocument1 paginăVentajas, desventajas y opinión de corrientes filosóficasarmy exo-lÎncă nu există evaluări

- Folleto Prev Incen Acs Hal 2015Document2 paginiFolleto Prev Incen Acs Hal 2015Daniel Menejes MontesinosÎncă nu există evaluări

- Tema N°2 Lenguaje C WordDocument27 paginiTema N°2 Lenguaje C WordLuis MurilloÎncă nu există evaluări