Documente Academic

Documente Profesional

Documente Cultură

Ass 9

Încărcat de

VLSITitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Ass 9

Încărcat de

VLSIDrepturi de autor:

Formate disponibile

EE529 EMBEDDED SYSTEMS

Assignment-9

Fast Fourier Transform (FFT) is an algorithm to compute the discrete Fourier transform (DFT) and it’s

inverse. Basically, the computational problem for the DFT is to compute the sequence {X(k)} {

of N complex-valued

valued numbers given another sequence of data {x(n)}

{ )} of length N, according to the

formula:

In general, the data sequence x(n plex valued. Similarly, The inverse discrete

n) is also assumed to be complex

Fourier Transform (IDFT) is given by:

Direct computation of the DFT is basically inefficient and happens in O(N2) primarily because it does not

exploit the symmetry and periodicity properties

prop of the phase factor (Twiddle factor) WN. In particular,

these two properties are:

Symmetry Property: WNk+N/2 = -WNk

Periodicity Property: WNk+N = WNk

Exploiting these, we get computationally efficient algorithms, known collectively as fast Fourier

Transform (FFT) working in computational complexity of O(N log N).

F by the divide and conquer approach

Consider the computation of the N = 8 point FFT approach. Divide the N-point

input sequence into two N/2-point

point data sequences f1(n) and f2(n), corresponding to the even-numbered

even and

odd-numbered samples of the input sequence x(n), respectively, that is,

f1(n) = x(2n)

f2(n) = x(2n +1)

Thus f1(n) and f2(n)) are obtained by decimating or dividing x(n)) by a factor of 2, and hence the resulting

FFT algorithm is called a decimation-in-time

decimation algorithm. Repeat the division recursively till you get

(x,N,s), where x is the input

sequences of 1 dimension. To do the recursion, define a function ditfft(x,N,s)

sequence, N is the number of samples and s is the step size. The equation of FFT can then be expressed

as:

X0, X1, X2………XN-1 <= ditfft(x,N,s)

(x,N,s) :where Xi is the FT of xi

Now, divide the sequence into two subsequences:

X0……N/2-1 <= ditfft(x,N/2,2s)

XN/2….N-1 <= ditfft(x,N/2,2s)

Now, loop K=0 to N/2-1

T = XK

XK = T + exp(-2jπK/N) * XK+N/2

XK+N/2 = T – exp(-2jπK/N) * XK+N/2

Compute the time complexity of FFT based on the above equation.

The FFT equation can be summarized

summari as:

Figure 1 explains this process in detail.

Fig 1: N=8 Point Decimation in Time FFT

For implementation on a reconfigurable

reconfig hardware like an FPGA, modular components are to be formed

which are to be mapped with the re required signals. The main unit is a component for doing the butterfly

formulations,

mulations, which essentially did the calculations depicted in Figure 2.

Fig 2: Butterfly Component

It has been proven that FFT is a computationally intensive operation. To optimize its run time, we have to

systematically assess all the daughter processes that run underneath. Once their characteristics are

identified, we can divide the algorithm to run on an FPGA (hardware) and a processor (software)

simultaneously.. For an 8 point FFT

FFT,, it can be seen that the algorithm involves 3 stages (Figure 1). Stage 1

involves 4 complex multiplications (with WN0 = 1) and 8 complex summations (4 addition and 4

subtraction). The next stage too involves 4 complex multiplications, but this time the T Twiddle factor is

not of unit magnitude, and 8 summations. This is also true for stage 3. Hence we can conclude that the

major component of this implementation is the complex summation and multiplication.

The complex summation does not require a large execution time; it is the multiplication that forms the

bottleneck. Hence it is wise to shift multiplication from software and implement it on hardware. Also, it

has been found that if a task interacts with external signals or is a custom task, like multiplication with

Twiddle factors, it is suited for

or hardware implementation. Design the he complex multiplier using the

architecture shown in figure 3:

Fig 3: Schematic of complex multiplier

software co-design to implement FFT was as follows: the input sequence,

Implement the hardware-software

each number is 16 bits:: 8 bit real and 8 bit imaginary) will be stored on the

consisting 8 numbers, (each

processor (an Atmega16 microcontroller).

microcontroller) The addition and

nd subtraction for each stage will be done on the

ler. While the multiplication will be performed on the FPGA (a Nexys 2 Spartan 3E FPGA).

microcontroller.

The Twiddle factors will be pre-calculated

pre calculated and stored in the ROM of the FPGA. This forms one

multiplicand, the other is sent from the microcontroller to the FPGA. For this, this you may use the

ation protocol to enable the microcontroller and FPGA talk to each other

following communication other.

microcontroller FPGA communication. The

Figure 4 shows the system architecture used to establish microcontroller-FPGA

communication protocol that you will employ will be a hybrid one, a mixture of a parallel and serial

(UART-Universal

Universal Asynchronous Receiver Transmitter) communication. The data from microcontroller

will be sent to the FPGA through the UART (serially). You may decide on tthe baud rate and fix

beforehand

and (since Atmega16 runs on 16 MHz while Spartan 3E on 50 MHz). z). Once data is received, it will

be multiplied with the pre-calculated

calculated twiddle factors and the product will be ready to be transmitted. This

value will be sent onn parallel transmission lines. An interrupt will also be generated. When this interrupt

is received on the microcontroller, the value on the microcontroller port, to which communication

commun lines

are connected, will be read and in turn stored in a variable.

Fig 4: System Architecture

Now perform the following experiments:

1. Compute the cycle count and time of computation of 8 point FFT.

2. co design of FFT.

Estimate the resources utilized on FPGA for the hardware software co-design

3. Estimate the power dissipation of the FFT system.

4. Repeat experiments 1,2 and 3 for complete hardware implementation of 8 point FFT.

5. ware implementation of 8 point FFT.

Repeat experiments 1,2 and 3 for complete software

6. Compare the results of complete hardware, complete software and hardware

hardware-software co-design

of FFT system.

S-ar putea să vă placă și

- SSRN-id3869494Document5 paginiSSRN-id3869494Prabhu SÎncă nu există evaluări

- DSP Asignment1 - ID - 117020990036Document20 paginiDSP Asignment1 - ID - 117020990036FRANCK MOREL BENE FANKEMÎncă nu există evaluări

- FFT128 ProjectDocument70 paginiFFT128 ProjectBảo Ngọc LêÎncă nu există evaluări

- Discrete Fourier Transform (DFT) : Dr. Parul Tyagi (Asso. Prof.) & Dr. Neha Singh (Asst. Prof.)Document65 paginiDiscrete Fourier Transform (DFT) : Dr. Parul Tyagi (Asso. Prof.) & Dr. Neha Singh (Asst. Prof.)Rõçky StrâñgëÎncă nu există evaluări

- Designing and Simulation of 32 Point FFT Using Radix-2 Algorithm For FpgaDocument9 paginiDesigning and Simulation of 32 Point FFT Using Radix-2 Algorithm For FpgaInternational Organization of Scientific Research (IOSR)Încă nu există evaluări

- Base Paper FPR FFTDocument5 paginiBase Paper FPR FFTOleti GowthamiÎncă nu există evaluări

- Exp 6Document5 paginiExp 6TARUN SINGH SVNITÎncă nu există evaluări

- Comparative Study of Various FFT Algorithm Implementation On FPGADocument4 paginiComparative Study of Various FFT Algorithm Implementation On FPGAInternational Journal of Emerging Trends in Signal Processing (IJETSP)Încă nu există evaluări

- Implementation of FFT by Using Matlab: Simulink On Xilinx Virtex-4 Fpgas: Performance of A Paired Transform Based FFTDocument7 paginiImplementation of FFT by Using Matlab: Simulink On Xilinx Virtex-4 Fpgas: Performance of A Paired Transform Based FFTKevin McintoshÎncă nu există evaluări

- VHDL Implementation of A Flexible and Synthesizable FFT ProcessorDocument5 paginiVHDL Implementation of A Flexible and Synthesizable FFT ProcessorHarrySchrovskiÎncă nu există evaluări

- AN4255Document43 paginiAN4255Achriyatul SetyoriniÎncă nu există evaluări

- Design and Simulation of 32-Point FFT Using Radix-2 Algorithm For FPGA 2012Document5 paginiDesign and Simulation of 32-Point FFT Using Radix-2 Algorithm For FPGA 2012mohamedÎncă nu există evaluări

- Hardware Implementation Low Power High Speed FFT CoreDocument7 paginiHardware Implementation Low Power High Speed FFT CoreAndrew TheKanenasÎncă nu există evaluări

- Frequency AnalyzerDocument4 paginiFrequency AnalyzerJosnaveÎncă nu există evaluări

- Department of Electronics and Communication Engineering: Digital Signal ProcessingDocument25 paginiDepartment of Electronics and Communication Engineering: Digital Signal ProcessingSETNHILÎncă nu există evaluări

- VD 02 Design and Implement of FFT Processor For OFDMA SystemDocument3 paginiVD 02 Design and Implement of FFT Processor For OFDMA Systembmss58Încă nu există evaluări

- Course Material (Question Bamk)Document4 paginiCourse Material (Question Bamk)lakshmiÎncă nu există evaluări

- Design and Implementation of Pipelined FFT Processor: D.Venkata Kishore, C.Ram KumarDocument4 paginiDesign and Implementation of Pipelined FFT Processor: D.Venkata Kishore, C.Ram KumarShakeel RanaÎncă nu există evaluări

- FFTDocument4 paginiFFTJasim ArÎncă nu există evaluări

- FFT Algorithms PDFDocument37 paginiFFT Algorithms PDFIqbal NovramadaniÎncă nu există evaluări

- On-Chip Implementation of High Speed and High Resolution Pipeline Radix 2 FFT AlgorithmDocument3 paginiOn-Chip Implementation of High Speed and High Resolution Pipeline Radix 2 FFT AlgorithmDr. Rozita teymourzadeh, CEng.Încă nu există evaluări

- Implementation of Fast Fourier Transform (FFT) Using VHDLDocument71 paginiImplementation of Fast Fourier Transform (FFT) Using VHDLCutie93% (30)

- Malaysia SITIS 437 PDFDocument7 paginiMalaysia SITIS 437 PDFsateesh83Încă nu există evaluări

- Project report-FFT1Document25 paginiProject report-FFT1Sriram KumaranÎncă nu există evaluări

- Efficient FPGA Implementation of FFT/IFFT Processor: Ahmed Saeed, M. Elbably, G. Abdelfadeel, and M. I. EladawyDocument8 paginiEfficient FPGA Implementation of FFT/IFFT Processor: Ahmed Saeed, M. Elbably, G. Abdelfadeel, and M. I. Eladawyfadhil78Încă nu există evaluări

- DIT Radix-2Document7 paginiDIT Radix-2Suha NoriÎncă nu există evaluări

- Exp 6Document4 paginiExp 6Dipesh RanaÎncă nu există evaluări

- FPGA Implementation of FFT for Embedded SystemsDocument16 paginiFPGA Implementation of FFT for Embedded SystemsgalaxystarÎncă nu există evaluări

- Configurable 2K/4K/8K Fft-Ifft Core For DVB-T and DVB-HDocument4 paginiConfigurable 2K/4K/8K Fft-Ifft Core For DVB-T and DVB-HQuân NguyễnÎncă nu există evaluări

- Fast Fourier TransformDocument15 paginiFast Fourier TransformRusith DilshanÎncă nu există evaluări

- Digital Signal Processing Two Mark Question With Answer Unit IIIDocument4 paginiDigital Signal Processing Two Mark Question With Answer Unit IIIsarathbabumjÎncă nu există evaluări

- High-Throughput VLSI Architecture For FFT ComputationDocument5 paginiHigh-Throughput VLSI Architecture For FFT ComputationSureshÎncă nu există evaluări

- Lab 6 DFT and FFTDocument16 paginiLab 6 DFT and FFTZia UllahÎncă nu există evaluări

- DSP Lab Report # 04Document23 paginiDSP Lab Report # 04Abdul BasitÎncă nu există evaluări

- Course Material (Question Bamk)Document4 paginiCourse Material (Question Bamk)Guna PriyaÎncă nu există evaluări

- Performance Analysis of 8-Point FFT Using Approximate Radix-8 Booth MultiplierDocument4 paginiPerformance Analysis of 8-Point FFT Using Approximate Radix-8 Booth MultiplierAvinash YadavalliÎncă nu există evaluări

- FFT DSP QuestionsDocument22 paginiFFT DSP QuestionsokhtayaÎncă nu există evaluări

- FFT ModuleDocument22 paginiFFT ModuleRamya C.N.Încă nu există evaluări

- 3F3 3 Fast Fourier TransformDocument50 pagini3F3 3 Fast Fourier TransformChalani PremadasaÎncă nu există evaluări

- 097 3Document8 pagini097 3Ashish BeckhamÎncă nu există evaluări

- 2019 ISCAS Reconfigurable Radix-2k3 Feedforward FFT ArchitecturesDocument5 pagini2019 ISCAS Reconfigurable Radix-2k3 Feedforward FFT ArchitecturesTsukasa BerryÎncă nu există evaluări

- Two Marks DSPDocument16 paginiTwo Marks DSPReeshma.GogulaÎncă nu există evaluări

- Theoretical Review of FFT ImplementationsDocument4 paginiTheoretical Review of FFT Implementationsanon_83420803Încă nu există evaluări

- 9 HRTHDocument22 pagini9 HRTHNithindev GuttikondaÎncă nu există evaluări

- Sang PSRDocument5 paginiSang PSRaatityasriÎncă nu există evaluări

- Fpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)Document7 paginiFpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)soumyaÎncă nu există evaluări

- John Glossner, Jesse Thilo, and Stamatis VassiliadisDocument5 paginiJohn Glossner, Jesse Thilo, and Stamatis VassiliadisvmacariÎncă nu există evaluări

- Fast Approximate Fourier Transform via WaveletsDocument10 paginiFast Approximate Fourier Transform via WaveletsTabassum Nawaz BajwaÎncă nu există evaluări

- Impact of DPU 2017Document6 paginiImpact of DPU 2017mdzakir_hussainÎncă nu există evaluări

- Fast Fourier Transform (FFT) AlgorithmDocument2 paginiFast Fourier Transform (FFT) AlgorithmAbhinav PathakÎncă nu există evaluări

- Exp#02 Analysing Biomedical Signal Using DFT and Reconstruct The Signal Using IDFTDocument6 paginiExp#02 Analysing Biomedical Signal Using DFT and Reconstruct The Signal Using IDFTMuhammad Muinul IslamÎncă nu există evaluări

- Design of 16-Point Radix4 Fast Fourier Transform IDocument7 paginiDesign of 16-Point Radix4 Fast Fourier Transform IAyush anandÎncă nu există evaluări

- +j2 הnk/NDocument27 pagini+j2 הnk/NRahulMunthaÎncă nu există evaluări

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDDe la EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDÎncă nu există evaluări

- Digital Signal Processing: Instant AccessDe la EverandDigital Signal Processing: Instant AccessEvaluare: 3.5 din 5 stele3.5/5 (2)

- LTE Signaling: Troubleshooting and Performance MeasurementDe la EverandLTE Signaling: Troubleshooting and Performance MeasurementÎncă nu există evaluări

- Nonlinear Control Feedback Linearization Sliding Mode ControlDe la EverandNonlinear Control Feedback Linearization Sliding Mode ControlÎncă nu există evaluări

- Ansaldo Electric Drives 15/30 kW Technical SpecsDocument4 paginiAnsaldo Electric Drives 15/30 kW Technical SpecsMr.K ch50% (2)

- Degaussing Coil in CRT TelevisionDocument2 paginiDegaussing Coil in CRT TelevisionSanie D. AbarrientosÎncă nu există evaluări

- PWM8 XDocument8 paginiPWM8 XRyan FullerÎncă nu există evaluări

- Vec 1180 KDocument35 paginiVec 1180 Kyu3zaÎncă nu există evaluări

- Gate 2014 Syllabus For Instrumentation Engineering inDocument6 paginiGate 2014 Syllabus For Instrumentation Engineering inrahulchangderÎncă nu există evaluări

- Datasheet 3L2Document6 paginiDatasheet 3L2juan carlos diaz cardozoÎncă nu există evaluări

- CW Drive Test and Model Tuning ReportDocument21 paginiCW Drive Test and Model Tuning Reportabhay100% (4)

- Module 6 - Current Divider RuleDocument10 paginiModule 6 - Current Divider RuleNoel Jr. CornelioÎncă nu există evaluări

- GSM Frequency Bands Table ExplainedDocument2 paginiGSM Frequency Bands Table Explainedamits_aumÎncă nu există evaluări

- Coax Connectors - RF TypesDocument6 paginiCoax Connectors - RF TypesMicah WilsonÎncă nu există evaluări

- Carrier PARTS 4 2010Document16 paginiCarrier PARTS 4 2010ricodavidÎncă nu există evaluări

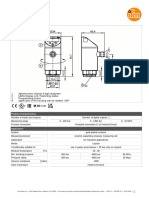

- PN7092 Pressure Sensor DisplayDocument5 paginiPN7092 Pressure Sensor DisplayEslam YehiaÎncă nu există evaluări

- Foundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of ApplicationsDocument4 paginiFoundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of Applicationssandeep_sggsÎncă nu există evaluări

- Service Guide Rev E - Invivo Expression PDFDocument96 paginiService Guide Rev E - Invivo Expression PDFBalaji BalasubramanianÎncă nu există evaluări

- Avionics Unit-2 PRINCIPLES: of Digital SystemsDocument144 paginiAvionics Unit-2 PRINCIPLES: of Digital SystemsVignesh Moorthy100% (3)

- CT100B System User ManualDocument22 paginiCT100B System User ManualJose RojasÎncă nu există evaluări

- VLT Micro DriveDocument11 paginiVLT Micro DriveMiguel E RosasÎncă nu există evaluări

- Gps Final Year ProjectDocument52 paginiGps Final Year ProjectPramod Niraula100% (1)

- AMB4520R1 (G+Usplit)Document2 paginiAMB4520R1 (G+Usplit)Thaw GyiÎncă nu există evaluări

- Bill of Quantity Electrical Work (Boq) 18-05-2007Document21 paginiBill of Quantity Electrical Work (Boq) 18-05-2007Imam Safii SoewarjoÎncă nu există evaluări

- Global Positioning System Fill in The Blanks Unit I: IntroductionDocument15 paginiGlobal Positioning System Fill in The Blanks Unit I: IntroductionHoney Durga Tiwari100% (1)

- L Series - Operating Manual.0.8Document55 paginiL Series - Operating Manual.0.8PaMe LiTaÎncă nu există evaluări

- J449 NecDocument8 paginiJ449 Necnaude visserÎncă nu există evaluări

- PLC ProjectDocument69 paginiPLC Projectsovon adhikaryÎncă nu există evaluări

- Instructions For Continued Airworthiness Maintenance Manual Supplement Concorde Valve Regulated Lead-Acid Main BatteryDocument11 paginiInstructions For Continued Airworthiness Maintenance Manual Supplement Concorde Valve Regulated Lead-Acid Main BatteryESAVEÎncă nu există evaluări

- Mps1000 ManualDocument46 paginiMps1000 ManualAnne NicoletaÎncă nu există evaluări

- UPS SPEC TECHNICAL SPECDocument26 paginiUPS SPEC TECHNICAL SPECengrrafÎncă nu există evaluări

- LPDDR 4Document1 paginăLPDDR 4SamÎncă nu există evaluări

- Design of Sensor Nodes in Underwater Sensor Networks: Yu Yang, Zhang Xiaomin, Peng BO, Fu YujingDocument5 paginiDesign of Sensor Nodes in Underwater Sensor Networks: Yu Yang, Zhang Xiaomin, Peng BO, Fu Yujinghari9923Încă nu există evaluări

- Tiger TO-92 Plastic Transistor SpecsDocument3 paginiTiger TO-92 Plastic Transistor SpecsVinod kumarÎncă nu există evaluări