Documente Academic

Documente Profesional

Documente Cultură

Comparison of Three Sinusoidal Pulse Width Modulation Techniques For Five-Level Cascaded Inverter Using Simulink

Încărcat de

Skp FATitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Comparison of Three Sinusoidal Pulse Width Modulation Techniques For Five-Level Cascaded Inverter Using Simulink

Încărcat de

Skp FADrepturi de autor:

Formate disponibile

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/277979702

Comparison of Three Sinusoidal Pulse Width Modulation Techniques for Five-

Level Cascaded Inverter using Simulink

Article · May 2015

DOI: 10.17577/IJERTV4IS051337

CITATIONS READS

0 1,436

4 authors, including:

Savyasachi G.K Avinash Ramesh

Vidyavardhaka College Of Engineering Vidyavardhaka College Of Engineering

7 PUBLICATIONS 4 CITATIONS 2 PUBLICATIONS 3 CITATIONS

SEE PROFILE SEE PROFILE

Apoorva. G.K

2 PUBLICATIONS 0 CITATIONS

SEE PROFILE

Some of the authors of this publication are also working on these related projects:

FACTS CONTROLLERS View project

All content following this page was uploaded by Savyasachi G.K on 23 June 2015.

The user has requested enhancement of the downloaded file.

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

Comparison of Three Sinusoidal Pulse Width

Modulation Techniques for Five- L evel Cascaded

Inverter using Simulink

Savyasachi. G. K1 Avinash. R2

Dept. of Electrical and Electronics Engineering, Dept. of Electrical and Electronics Engineering,

Vidyavardhaka College of Engineering, Vidyavardhaka College of Engineering,

Mysuru, Karnataka, India. Mysuru, Karnataka, India.

Rakshith. P3 Apoorva. G. K4

Dept. of Electrical and Electronics Engineering, Dept. of Electrical and Electronics Engineering,

Vidyavardhaka College of Engineering, PES Institute of Technology and Management,

Mysuru, Karnataka, India. Shivamogga, Karnataka, India.

Abstract— Multi-level inverters are becoming very popular renewable unit, has critical impacts on providing electricity to

nowadays due to the usage of low rating devices for high rating the consumers connected to the grid.

applications, which overcome the limitation imposed by the

rating of the semiconductor switches. In this paper, a The multi-level inverter system is used when high power

comparative study of three different SPWM techniques for five- with reduced harmonic content is required. But, as the output

level cascaded inverter is presented. Simulink is used for voltage level increases, the number of semiconductor

simulation. Simulation results; waveforms and THD graphs are switches in the circuit increases. In case of multi-level

obtained. Harmonics of three SPWM techniques are tabulated inverter system, the loss of semiconductor devices cannot be

for comparison. analyzed by conventional methods.

Keywords— Multi-level Inverter, SPWM, THD, Simulink. The elementary concept of a multilevel inverter is to

achieve higher power by using a series of semiconductor

I. INTRODUCTION switches with several low voltage dc sources for the power

conversion by synthesizing staircase voltage waveforms.

Inverter application is increasing as most of the loads

used are of alternating current loads and the renewable In this paper, a basic Simulink models for generating

energy sources like wind, solar, etc., gives the direct current conventional SPWM and waveforms are presented for better

outputs. Many inverter topologies and different firing understanding of the further discussion. Then simulation of a

techniques were introduced in last few decades. cascaded five-level inverter for three different SPWM

techniques is presented.

In paper [1], a simulation of Unipolar-SPWM strategy for

single phase full bridge inverter is presented. Different three- The objectives of this paper are as follows: Simulation of

level inverter topologies with SPWM technique that conventional method of generation of SPWM is presented in

minimize the harmonic distortion in the output of the inverter Section II. Simulation of three SPWM techniques has been

has been simulated in paper [2]. presented in Section III. Simulation results for five-level

cascaded inverter for three different SPWM techniques are

In paper [3], the basic theory of a single-phase SPWM

given in Section IV and harmonics are tabulated for

inverter, its Simulink modeling is presented. A new reliability

comparison.

evaluation technique on the basis of the state enumeration

approach for multi-level inverters engages harmonic

distortion levels produced by the inverter in the reliability II. SIMULATION OF GENARATING CONVENTIONAL

index calculation is presented in [4]. Paper [5] proposes a SINUSOIDAL PULSE WIDTH MODULATION WAVEFORM

new multi-level inverter topology based on H-bridge with Sinusoidal Pulse Width Modulation techniques are

DC-link switches. The output voltage is closer to sinusoidal characterized by pulses with different duty cycle but constant

wave. A new PWM method based on Phase Opposition amplitude for each period. Pulse width is modulated in order

Disposition modulation is which requires only one carrier to obtain controlled output voltage and reduced harmonics.

signal is suggested. SPWM is the most commonly used method for motor control

and inverter applications. To generate the SPWM signal,

Multi-level inverters play an important role in micro-grids conventionally, carrier triangle wave is compared with the

which integrates several renewable energy sources. The sine wave of operating frequency.

reliability of multi-level inverters which interface different

IJERTV4IS051337 www.ijert.org 1294

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

1

-K- 1

s

Out1

Pulse Integrator Gain

Generator

Constant Scope

Fig. 1: Simulink model for generating triangular wave as in Fig. 2

Fig. 6: Sine output of Signal Generator1 (red) and Triangular output of Tri 1

(pink) and Tri 2 (aqua blue).

Fig. 2: Output waveform of model in Fig.1.

1

-K- 1

s

Out1

Pulse Integrator Gain

Generator Fig. 7: SPWM output of model shown in Fig. 5 (Out 1 & Out 2).

1

Fig.5 shows the conventional method of generating

Constant Scope SPWM waveform. In this figure, Tri 1 and Tri 2 are the

Fig. 3: Simulink model for generating triangular wave as in Fig.4. triangular wave generators whose Simulink modeling is

shown in Fig. 1 and Fig.3 respectively which gives carrier

signal at 10 kHz. Signal Generator1 gives the sinusoidal wave

of operating frequency (50 Hz) with magnitude of -1 to +1, as

shown in Fig. 6. The two triangular waves and sine wave is

compared as shown in Fig. 5 and the output is the SPWM

waveform as shown in Fig.7.

III. SIMULATION MODELS OF THREE SPWM TECHNIQUES

Fig. 4: Output waveform of model in Fig.3.

In this section, three different SPWM techniques used to

control five-level cascaded inverter are presented. The three

different techniques are as follows:

Out1

Signal

Generator1 Out2

1 SPWM

Out1 Generator

Sign1 Saturation

Out1 AND 1

Out1

Logical

Tri 1 Scope Pulse Operator

Generator

2

Out2 AND 2

Sign2 Saturation1

Out1 Out2

Logical

Pulse

Operator1

Generator1

Tri 2

Fig. 5: Simulink model for generating SPWM as in Fig. 7. AND 3

Pulse Out3

Logical

Fig.1 shows the Simulink model for generating triangular Generator2

Operator2

wave as shown in Fig.2. Triangular wave generated has

magnitude from 0 to 1 volt. AND 4

Pulse Out4

Logical

Fig.3 shows the Simulink model for generating triangular Generator3

Operator3

wave as shown in Fig.4. Triangular wave generated has Fig. 8: Simulink Model of S-SPWM gate pulses generation for five-level

magnitude from -1 to 0 volt. cascaded inverter.

IJERTV4IS051337 www.ijert.org 1295

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

International Journal of Engineering Research & Technology (IJERT)

ISSN: 2278-0181

Vol. 4 Issue 05, May-2015

A. Technique-1: Selective-SPWM (S-SPWM) C. Technique-3: Multi-carrier SPWM (MC-SPWM)

In this technique, the SPWM generated by conventional In this technique, four triangular carrier waves are compared

method as show in Fig. 7 is logically AND with the PWM with a sinusoidal wave of fundamental frequency (operating

pulses of desired pulse width as shown in Fig. 12 to select the frequency=50Hz) as shown in Fig. 20 using the model as in

portion of SPWM as gate pulses by using model as shown in

Fig. 10 to get the gate pulses shown in Fig. 21

Fig. 8 is as shown in Fig. 13.

B. Technique-2: Phase-Shift SPWM (PS-SPWM) Signal

Generator1

In this technique, two triangular carrier waves and two 1

sinusoidal waves are used as shown in Fig. 16. Here one sine Out1

Sign1 Saturation

Out1

wave lags the other by 900. Thus the output gate pulses of

model in Fig. 9, will also have the phase shift of 90 0 between Tri 1

2

two sets of SPWM waveforms as shown in Fig. 17. Out2

Sign2 Saturation1

Out1

Tri 2

Scope

Signal 3

Generator 1

Out3

Out1 Sign3 Saturation2

Out1 Out1

Sign1 Saturation1

Tri 1

Tri 3

4

Out1

2 Scope Out4

Sign4 Saturation3

Out1

Tri 2 Out2

Sign2 Saturation2

Tri 4

Fig. 10: Simulink Model of MC-SPWM gate pulses generation for five-level

90 degree 3

cascaded inverter.

phase delay Out3

Sign3 Saturation3 IV. SIMULATION RESULTS

Fig.11 shows a Simulink model of five-level cascaded

4

Scope1 inverter. It consists of two H-bridge with four semiconductor

Out4

Sign4 Saturation4 switch each, with separate DC voltage sources of 115V. Two

Fig. 9: Simulink Model of PS-SPWM gate pulses generation for five-level H-bridges are operated with either of three SPWM techniques

cascaded inverter. mentioned earlier.

Dis cre te ,

T s = 5e -06 s .

po we rgui

D

D

g

S11 S12

S

Vdc1

Out1

D

D

g

Out2

S13 S14

Out3

S

Out4

+

Pul se Gate - v

Generator Pul ses

THD

Vout

D

D

g

S21 S22

S

Vdc2

D

D

g

S23 S24

S

Fig. 11: Simulink model of five-level cascaded inverter.

IJERTV4IS051337 www.ijert.org 1296

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

200

100

-100 International Journal of Engineering Research & Technology (IJERT)

-200 ISSN: 2278-0181

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

Time (s) Vol. 4 Issue 05, May-2015

Fig. 12, 16 & 20 shows the basic waveforms used to Fundamental (50Hz) = 182.8 , THD= 48.04%

generates gating signals as shown in Fig. 13, 17 & 21 using 25

models shown in Fig. 8 (S-SPWM), 9 (PS-SPWM) &10

Mag (% of Fundamental)

20

(MC-SPWM) respectively. When these gating pulses are used 15

in the model shown in Fig. 11, it gives the output voltage

waveforms as shown in Fig. 14, 18 & 22 respectively. 10

5

Harmonics graphs for these three SPWM gate pulse

techniques are shown in Fig. 15, 19 and 23 respectively. The 0

0 1 2 3 4 5 6 7 8 9 10

Harmonic order

fundamental components and harmonics are tabulated in

Fig. 15: FFT analysis of output voltage waveform as in Fig. 14.

Table-I for comparison.

Fig. 16: Sine output of Signal Generator (red), with phase delay of 900 (blue),

Triangular output of Tri 1 (pink) and Tri 2 (aqua blue).

Fig. 12: Output of SPWM generator and Pulse generators shown in Fig. 8.

Fig. 17: Gating pulses generated by the model shown in Fig. 9, (PS-SPWM).

Selected signal: 50 cycles. FFT window (in red): 2 cycles

200

100

-100

Fig. 13: Gating pulses generated by the model shown in Fig. 8, (S-SPWM). -200

Fig. 018: Output

0.1 Voltage

0.2 of

0.3 inverter

0.4 shown0.5 in Fig.

0.6 11 0.7

for the 0.8

gating pulses

0.9 as1

Time (s)

shown in Fig. 17, (PS-SPWM).

Fundamental (50Hz) = 161.2 , THD= 61.61%

1

0.8

Mag (% of Fundamental)

0.6

0.4

0.2

0

0 1 2 3 4 5 6 7 8 9 10

Harmonic order

Fig. 14: Output Voltage of inverter shown in Fig. 11 for the gating pulses as Fig. 19: FFT analysis of output voltage waveform as in Fig. 18.

shown in Fig. 13, (S-SPWM).

IJERTV4IS051337 www.ijert.org 1297

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

200

100

-100

International Journal of Engineering Research & Technology (IJERT)

-200 ISSN: 2278-0181

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

Time (s) Vol. 4 Issue 05, May-2015

Fundamental (50Hz) = 229.5 , THD= 26.62%

0.35

0.3

Mag (% of Fundamental)

0.25

0.2

0.15

0.1

0.05

0

0 1 2 3 4 5 6 7 8 9 10

Harmonic order

Fig. 23: FFT analysis of output voltage waveform as in Fig. 22.

In all three techniques THD is high due to the harmonic of

Fig. 20: Sine output of Signal Generator1 (blue) and Triangular outputs of

order 200 i.e., 10 kHz, which is the frequency of carrier

Tri 1 (pink), Tri 2 (aqua blue), Tri 3 (red) and Tri 4 (green). triangular signal.

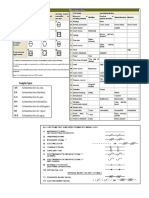

TABLE I. PERCENTAGE HARMONICS IN OUTPUT VOLTAGE (VOUT)

SPWM Fundamental Harmonic order THD

Technique (50Hz) 3 5 7 9 (%)

S-SPWM 182.8 V 24.90% 7.59% 5.13% 8.57% 48.04

PS-SPWM 161.2 V 0.88% 0.93% 0.63% 0.74% 61.61

MC-SPWM 229.5V 0.30% 0.34% 0.31% 0.29% 26.62

From Table I, it can be seen that the MC-SPWM has good

fundamental component and less harmonics. The S-SPWM

technique results in more harmonics. PS-SPWM has very less

harmonics (less than 1%), almost nearer to MC-SPWM. THD

can be reduced by a greater extent using proper filter design.

V. SUMMARY AND CONCLUSION

Fig. 21: Gating pulses generated by the model shown in Fig. 10, (MC- This paper has done a comparative analysis of three

SPWM). sinusoidal pulse width modulation techniques. The

waveforms and harmonic analysis for the three techniques,

using Simulink, are tabulated for comparison. From the

harmonics table it can be observed that Multi-carrier

sinusoidal pulse width modulation technique (MC-SPWM)

results in fewer harmonic compared to other two techniques.

REFERENCES

(1) Sachin Maheshri and Prabodh Khampariya, “Simulation of single phase

SPWM (Unipolar) inverter”, International Journal of Innovative

Research in Advanced Engineering (IJIRAE), Volume 1, Issue 9, pp.

12-18, October 2014.

(2) Kapil Jain, Pradyumn Chaturvedi, “MATLAB-based Simulation &

Fig. 22: Output Voltage of inverter shown in Fig. 11 for the gating pulses as Analysis of Three-Level SPWM Inverter”, International Journal of Soft

shown in Fig. 21. (MC-SPWM). Computing and Engineering (IJSCE), Volume-2, Issue-1, pp. 56-59,

March 2012.

(3) Sandeep Phogat, “Analysis of Single-Phase SPWM Inverter”,

International Journal of Science and Research (IJSR), Volume 3, Issue

8, pp. 1793-1798, August 2014.

(4) S. M. Sadat Kiaee, A. Namadmalan, J. Shokrollahi Moghani, “A New

Reliability Evaluation Technique for multilevel Inverters”, 4th Power

Electronics, Drive Systems & Technologies Conference

(PEDSTC2013), IEEE, pp. 361-366, Feb l3-14, 2013, Tehran, Iran.

(5) Ho-Dong Sun, Min-Young Park, Jong-Hyoung Park, Heung-Geun

Kim, Tae-Won Chun, Eui-Cheol Nho, “Novel H-bridge Multi-level

Inverter with DC-link Switches”, 8th International Conference on Power

Electronics –ECCE Asia, IEEE, pp. 1734-1741, May 30-June 3, 2011,

The Shilla Jeju, Korea.

IJERTV4IS051337 www.ijert.org 1298

(This work is licensed under a Creative Commons Attribution 4.0 International License.)

View publication stats

S-ar putea să vă placă și

- SVPWM For 3-Phase 3-Level Neutral Point Clamped Inverter Fed Induction Motor ControlDocument9 paginiSVPWM For 3-Phase 3-Level Neutral Point Clamped Inverter Fed Induction Motor ControljamalÎncă nu există evaluări

- Implementation of SPWM Technique For Inverter: October 2016Document6 paginiImplementation of SPWM Technique For Inverter: October 2016يوسف خضر النسورÎncă nu există evaluări

- Implementation of SPWM Technique For Inverter: October 2016Document6 paginiImplementation of SPWM Technique For Inverter: October 2016يوسف خضر النسورÎncă nu există evaluări

- Trofazni Invertor SPWMDocument6 paginiTrofazni Invertor SPWMBorislav BrnjadaÎncă nu există evaluări

- 32 Paper 60Document5 pagini32 Paper 60shankul.saurabhÎncă nu există evaluări

- Control of Voltage Source Inverters Using PWMDocument48 paginiControl of Voltage Source Inverters Using PWMManohar DakaÎncă nu există evaluări

- CascadeH-BridgeMultilevelInverter in MATLABDocument6 paginiCascadeH-BridgeMultilevelInverter in MATLABEnock MwebesaÎncă nu există evaluări

- Phase I.M DriveDocument4 paginiPhase I.M DriveJournalNX - a Multidisciplinary Peer Reviewed JournalÎncă nu există evaluări

- 7 LevelDocument5 pagini7 LevelACHREF RIHANIÎncă nu există evaluări

- Art05 IDocument12 paginiArt05 IArsyad CahyaÎncă nu există evaluări

- Final Phase 1 PPT Major ProjectDocument21 paginiFinal Phase 1 PPT Major ProjectSpandana priyaÎncă nu există evaluări

- Analysis Hardware Implementation of Three Phase Voltage Source Inverter IJERTV2IS50796Document10 paginiAnalysis Hardware Implementation of Three Phase Voltage Source Inverter IJERTV2IS50796Paul Mathew 21PHD1086Încă nu există evaluări

- Small Signal Stability Analysis of Multi Machine Power Systems Interfaced With Micro Grid IJERTV3IS080275Document8 paginiSmall Signal Stability Analysis of Multi Machine Power Systems Interfaced With Micro Grid IJERTV3IS080275Emílio CamargoÎncă nu există evaluări

- Arduino Based V/F Drive For A Three Phase Induction Motor Using Single Phase SupplyDocument6 paginiArduino Based V/F Drive For A Three Phase Induction Motor Using Single Phase SupplyRai Nazer Hussain KharlÎncă nu există evaluări

- Ijetr022623 PDFDocument5 paginiIjetr022623 PDFerpublicationÎncă nu există evaluări

- Recent Advances in MLIDocument3 paginiRecent Advances in MLIclementÎncă nu există evaluări

- Implement SPWM with Arduino HILDocument10 paginiImplement SPWM with Arduino HILAbdullah Al MamunÎncă nu există evaluări

- Application of SRF-PI Current Control in The Design of A Single-Phase Asymmetrical Inverter For Use in Weak Grid EnvironmentsDocument17 paginiApplication of SRF-PI Current Control in The Design of A Single-Phase Asymmetrical Inverter For Use in Weak Grid EnvironmentsResearch ParkÎncă nu există evaluări

- Different Modulation Techniques PDFDocument5 paginiDifferent Modulation Techniques PDFnaseer m a abdul khadarÎncă nu există evaluări

- Final Phase 1 PPT Major ProjectDocument21 paginiFinal Phase 1 PPT Major ProjectSpandana priyaÎncă nu există evaluări

- Synchronization of Three Phase Inverter With Electrical Grid IJERTV4IS050938Document8 paginiSynchronization of Three Phase Inverter With Electrical Grid IJERTV4IS050938Dung Vu DinhÎncă nu există evaluări

- Technical Paper Presentation of FPGA Based SVM ControllerDocument5 paginiTechnical Paper Presentation of FPGA Based SVM ControllerShiva Prasad MÎncă nu există evaluări

- A Novel Dynamic Voltage RestorerDocument6 paginiA Novel Dynamic Voltage RestorerIJIERT-International Journal of Innovations in Engineering Research and TechnologyÎncă nu există evaluări

- A Hybrid Polygonal SV Structure For TheDocument13 paginiA Hybrid Polygonal SV Structure For Themahmoud yarahmadiÎncă nu există evaluări

- A Simple Space Vector PWM Generation Scheme For Any General N-Level InverterDocument9 paginiA Simple Space Vector PWM Generation Scheme For Any General N-Level InverterAhmad MqdadÎncă nu există evaluări

- SSRN Id3159787Document8 paginiSSRN Id3159787Gopal BÎncă nu există evaluări

- Anfis Controller For Solar Powered Cascade Multilevel InverterDocument7 paginiAnfis Controller For Solar Powered Cascade Multilevel InverterIAEME PublicationÎncă nu există evaluări

- AUPEC 2020 Shuvra FinalDocument7 paginiAUPEC 2020 Shuvra FinalAK KhanÎncă nu există evaluări

- CHB InverterDocument6 paginiCHB InverterSateesh KumarÎncă nu există evaluări

- Random PWM Techniques Spread Harmonic SpectrumDocument10 paginiRandom PWM Techniques Spread Harmonic SpectrumALiftsÎncă nu există evaluări

- Impulse Voltage Generator Modelling Using MATLAB PDFDocument8 paginiImpulse Voltage Generator Modelling Using MATLAB PDFAsmaÎncă nu există evaluări

- Minimising Industrial Power Consumption Penalty by Engaging APFC UnitDocument17 paginiMinimising Industrial Power Consumption Penalty by Engaging APFC UnitPratima ChavanÎncă nu există evaluări

- A Review On Current Source Inverter Fed Ac Drives and Multilevel Current SourceDocument8 paginiA Review On Current Source Inverter Fed Ac Drives and Multilevel Current SourceIAEME PublicationÎncă nu există evaluări

- Design of SPWM Based Three Phase Inverter Model: Tanuhsree Bhattacharjee Dr. Majid Jamil Dr. Anup JanaDocument6 paginiDesign of SPWM Based Three Phase Inverter Model: Tanuhsree Bhattacharjee Dr. Majid Jamil Dr. Anup JanaandersonÎncă nu există evaluări

- Solar Smart Inverter - A Novel Design Using Multi Level Topology and PulseWidth Modulation With Load Detection PDFDocument5 paginiSolar Smart Inverter - A Novel Design Using Multi Level Topology and PulseWidth Modulation With Load Detection PDFmuhammad mamoonÎncă nu există evaluări

- Solar Energy Conversion Systemwith Maximum Power Point TrackingDocument7 paginiSolar Energy Conversion Systemwith Maximum Power Point Trackingshahid.msee187Încă nu există evaluări

- Literature Review On Variable Frequency Drive For Induction MotorDocument2 paginiLiterature Review On Variable Frequency Drive For Induction MotorPravin LandgeÎncă nu există evaluări

- "Short Term Price Forecasting": BY Pravesh Srivastava (Roll No.-14335) Mr. Ankit Kumar SrivastavaDocument29 pagini"Short Term Price Forecasting": BY Pravesh Srivastava (Roll No.-14335) Mr. Ankit Kumar SrivastavaPravesh SrivastavaÎncă nu există evaluări

- Simulaciones de Electrónica de Potencia en PspiceDocument63 paginiSimulaciones de Electrónica de Potencia en PspiceCarlos Iván RuedaÎncă nu există evaluări

- DC-BusVoltageRangeExtensionin1500V JSTPE Dec2015Document18 paginiDC-BusVoltageRangeExtensionin1500V JSTPE Dec2015Manoja Kumar BeheraÎncă nu există evaluări

- Field Oriented Control of Permanent Magnet PDFDocument8 paginiField Oriented Control of Permanent Magnet PDFLê Đức ThịnhÎncă nu există evaluări

- Multi Level InverterDocument4 paginiMulti Level InverterabsalnabiÎncă nu există evaluări

- Design_and_Implementation_of_Switched_Capacitor_BaDocument15 paginiDesign_and_Implementation_of_Switched_Capacitor_BaDEEPAK PRAJAPATIÎncă nu există evaluări

- Hybrid System MonitoringDocument3 paginiHybrid System MonitoringJournalNX - a Multidisciplinary Peer Reviewed JournalÎncă nu există evaluări

- Power Electronics Converters and their Control for Renewable Energy ApplicationsDe la EverandPower Electronics Converters and their Control for Renewable Energy ApplicationsArezki FekikÎncă nu există evaluări

- High-Frequency Modeling For Cable and Induction Motor Overvoltage Studies in Long Cable DrivesDocument10 paginiHigh-Frequency Modeling For Cable and Induction Motor Overvoltage Studies in Long Cable DrivesRodrigo AndradeÎncă nu există evaluări

- Dual Voltage Source Inverter Using Hybrid Energy Source InverterDocument14 paginiDual Voltage Source Inverter Using Hybrid Energy Source Inverterchauhanravi762Încă nu există evaluări

- Self Excited Induction Generator: A Review: ArticleDocument7 paginiSelf Excited Induction Generator: A Review: ArticleMoyasserengAlattarÎncă nu există evaluări

- Voltage Icker Mitigation in Electric Arc Furnace Using D-STATCOMDocument9 paginiVoltage Icker Mitigation in Electric Arc Furnace Using D-STATCOMTrisna GayatriÎncă nu există evaluări

- A6 - Three Phase Inverter PDFDocument40 paginiA6 - Three Phase Inverter PDFPedro Carvalho100% (2)

- Reduced Switching-Frequency-Modulation Algorithm For High-Power Multilevel InvertersDocument7 paginiReduced Switching-Frequency-Modulation Algorithm For High-Power Multilevel InvertersCaroline CvasnayaÎncă nu există evaluări

- Back-To-Back Converter Design and Control For Synchronous Generator-Based Wind TurbinesDocument8 paginiBack-To-Back Converter Design and Control For Synchronous Generator-Based Wind TurbinesBinh NgoÎncă nu există evaluări

- Harmonic Analysis of Three Phase SPWM and SVPWM ConvertersDocument9 paginiHarmonic Analysis of Three Phase SPWM and SVPWM ConvertersMuhammad ZamanÎncă nu există evaluări

- Design of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsDocument6 paginiDesign of Multi-Level Inverter and Its Application As Statcom To Compensate Voltage Sags Due To FaultsManpreet SinghÎncă nu există evaluări

- Ijmer 46016571 PDFDocument7 paginiIjmer 46016571 PDFSifat Binta HabibÎncă nu există evaluări

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsDe la EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsÎncă nu există evaluări

- Power System Protection in Future Smart Grids: Achieving Reliable Operation with Renewable Energy, Electric Vehicles, and Distributed GenerationDe la EverandPower System Protection in Future Smart Grids: Achieving Reliable Operation with Renewable Energy, Electric Vehicles, and Distributed GenerationTaha Selim UstunÎncă nu există evaluări

- Modeling and Control of Power Electronics Converter System for Power Quality ImprovementsDe la EverandModeling and Control of Power Electronics Converter System for Power Quality ImprovementsEvaluare: 5 din 5 stele5/5 (1)

- Computer Methods in Power Systems Analysis with MATLABDe la EverandComputer Methods in Power Systems Analysis with MATLABÎncă nu există evaluări

- Control of Power Electronic Converters and Systems: Volume 4De la EverandControl of Power Electronic Converters and Systems: Volume 4Încă nu există evaluări

- A Review of Single-Phase Grid-Connected Inverters For PV ModulesDocument15 paginiA Review of Single-Phase Grid-Connected Inverters For PV Modulesuama87Încă nu există evaluări

- Guo Liping 41 PDFDocument127 paginiGuo Liping 41 PDFYassine EL HoumÎncă nu există evaluări

- S8AENDocument8 paginiS8AENSkp FAÎncă nu există evaluări

- Design and Simulation of Flyback Converter in MATLAB Using PID ControllerDocument6 paginiDesign and Simulation of Flyback Converter in MATLAB Using PID ControllerSkp FAÎncă nu există evaluări

- Implementation of Electronic Load Controller For Control of Micro Hydro Power PlantDocument6 paginiImplementation of Electronic Load Controller For Control of Micro Hydro Power PlantSkp FAÎncă nu există evaluări

- Differences in The Impact of Harmonic Distortion Due To The Installation of Electronic Load Controller in Self-Excited Induction Generator and Synchronous GeneratorDocument13 paginiDifferences in The Impact of Harmonic Distortion Due To The Installation of Electronic Load Controller in Self-Excited Induction Generator and Synchronous GeneratorIAES IJPEDSÎncă nu există evaluări

- PID ResumenDocument6 paginiPID ResumenSkp FAÎncă nu există evaluări

- MPPT-based solar PV system simulationDocument16 paginiMPPT-based solar PV system simulationSkp FAÎncă nu există evaluări

- Incremental Conductance MPPT Algorithm for PV System Using Buck and Boost ConvertersDocument10 paginiIncremental Conductance MPPT Algorithm for PV System Using Buck and Boost ConvertersSkp FAÎncă nu există evaluări

- ARM Based Electronic Load Controller For Micro-HydDocument11 paginiARM Based Electronic Load Controller For Micro-HydSkp FAÎncă nu există evaluări

- Good Explanation ELCDocument12 paginiGood Explanation ELCCY KangÎncă nu există evaluări

- New Single-Stage Soft-Switching Flyback Inverter For AC Module Application With Simple CircuitDocument6 paginiNew Single-Stage Soft-Switching Flyback Inverter For AC Module Application With Simple CircuitSkp FAÎncă nu există evaluări

- Electronic Load Controllers For Self Excited Induction GeneratorDocument5 paginiElectronic Load Controllers For Self Excited Induction GeneratorSkp FAÎncă nu există evaluări

- Design of A Simple Electronic Load Controlled With Configurable Load ProfileDocument6 paginiDesign of A Simple Electronic Load Controlled With Configurable Load ProfileSkp FAÎncă nu există evaluări

- Design and Simulation of Flyback Converter in MATLAB Using PID ControllerDocument6 paginiDesign and Simulation of Flyback Converter in MATLAB Using PID ControllerSkp FAÎncă nu există evaluări

- Edm Flyback Converter 6680-14547-2-PB PDFDocument7 paginiEdm Flyback Converter 6680-14547-2-PB PDFSimon NgigiÎncă nu există evaluări

- 06 HAL TheoryDocument26 pagini06 HAL TheorySkp FAÎncă nu există evaluări

- Dynamic Modeling and Controller Design For A SinglDocument13 paginiDynamic Modeling and Controller Design For A SinglSkp FAÎncă nu există evaluări

- 06 HAL TheoryDocument26 pagini06 HAL TheorySkp FAÎncă nu există evaluări

- Stm32f4 LabsDocument430 paginiStm32f4 LabsBui Van Phat100% (4)

- Paper8 PDFDocument14 paginiPaper8 PDFSkp FAÎncă nu există evaluări

- 1 - Proton Compiler ManualDocument456 pagini1 - Proton Compiler ManualSkp FAÎncă nu există evaluări

- Portafolios Apreciación CinematográficaDocument9 paginiPortafolios Apreciación CinematográficaSkp FAÎncă nu există evaluări

- Human Detection Robot For Natural Calamity Rescue Operation - 2019Document5 paginiHuman Detection Robot For Natural Calamity Rescue Operation - 2019Pratik GadilkarÎncă nu există evaluări

- Casio tv-1900bxm SMDocument21 paginiCasio tv-1900bxm SMДмитрий АртюхÎncă nu există evaluări

- PLL Serial MC145170 Instruction SetDocument8 paginiPLL Serial MC145170 Instruction SetStephen Dunifer100% (4)

- A Compact Circular-Ring Antenna For Ultra-Wideband ApplicationsDocument6 paginiA Compact Circular-Ring Antenna For Ultra-Wideband Applicationsameya1981Încă nu există evaluări

- Lspcad 6 TutorialDocument30 paginiLspcad 6 Tutorialzonepress100% (1)

- Satellite Router Quick Start: Odin GuideDocument2 paginiSatellite Router Quick Start: Odin GuideAhmadHambaliÎncă nu există evaluări

- SDH vs SONET: Understanding the Differences Between Synchronous Digital Hierarchy and Synchronous Optical NetworkDocument30 paginiSDH vs SONET: Understanding the Differences Between Synchronous Digital Hierarchy and Synchronous Optical NetworkReynald John PastranaÎncă nu există evaluări

- Understanding MSK PDFDocument13 paginiUnderstanding MSK PDFSanjib ChaudhuryÎncă nu există evaluări

- Survey On Anti-Drone Systems Components Designs AnDocument25 paginiSurvey On Anti-Drone Systems Components Designs AnORLANDO CASTILLOÎncă nu există evaluări

- A 13 2 4 Technical Description BS241 IIDocument70 paginiA 13 2 4 Technical Description BS241 IIwilinux100% (1)

- hw1 SolDocument11 paginihw1 Solvictrongkhang1100% (1)

- MTI G09RRH-43 LTE RRH Band 8 Datasheet V1.0Document2 paginiMTI G09RRH-43 LTE RRH Band 8 Datasheet V1.0mohsin881Încă nu există evaluări

- List of Contents: S/No. Subject Page NumberDocument24 paginiList of Contents: S/No. Subject Page NumberAbdelrahman DaakirÎncă nu există evaluări

- 5 Phasor DiagramDocument18 pagini5 Phasor DiagramTiisetso MokwaneÎncă nu există evaluări

- Nemo Outdoor 7.0.0.9 Compatible Devices 18th April 2013Document6 paginiNemo Outdoor 7.0.0.9 Compatible Devices 18th April 2013ppat503Încă nu există evaluări

- PTP 820S Licensed Microwave Radio: All-OutdoorDocument7 paginiPTP 820S Licensed Microwave Radio: All-Outdoorjavierdb2012Încă nu există evaluări

- Module - 1: Drawbacks of IGDocument53 paginiModule - 1: Drawbacks of IGgokulaÎncă nu există evaluări

- Texas A&M VCO Lab: CMOS LC Oscillator Analysis & SimulationDocument8 paginiTexas A&M VCO Lab: CMOS LC Oscillator Analysis & SimulationRekha YadavÎncă nu există evaluări

- DL8 Datalink - User Guide - 20210804Document15 paginiDL8 Datalink - User Guide - 20210804Rodrigo AzevedoÎncă nu există evaluări

- MIT Radiaton Lab Series V8 Principles of Microwave CircuitsDocument504 paginiMIT Radiaton Lab Series V8 Principles of Microwave Circuitskgrhoads100% (1)

- IEEE Guide For Partial Discharge Measurement in Power SwitchgearDocument24 paginiIEEE Guide For Partial Discharge Measurement in Power SwitchgearHafiziAhmadÎncă nu există evaluări

- 1480 Diagnostic Trouble Code ChartDocument1 pagină1480 Diagnostic Trouble Code ChartIwan ThomasÎncă nu există evaluări

- Features DescriptionDocument9 paginiFeatures DescriptionAnonymous Uk3JxlHAÎncă nu există evaluări

- UNNPX206R3Document2 paginiUNNPX206R3Jose Zamora CampanaÎncă nu există evaluări

- Vidf 20180924Document1 paginăVidf 20180924anoopÎncă nu există evaluări

- Lec10 PDFDocument29 paginiLec10 PDFNaresh BirudalaÎncă nu există evaluări

- Optibox MP - Cenovnik Februar, 2013Document23 paginiOptibox MP - Cenovnik Februar, 2013Max MaximÎncă nu există evaluări

- Microstrip Patch Antenna: A Review and The Current State of The ArtDocument16 paginiMicrostrip Patch Antenna: A Review and The Current State of The ArtThanh HoàngÎncă nu există evaluări

- Rficdesign - Interview Question 5Document2 paginiRficdesign - Interview Question 5prodip7Încă nu există evaluări

- PWM Generator Using 741 Op Amp Comparator CircuitDocument3 paginiPWM Generator Using 741 Op Amp Comparator CircuitsamironiÎncă nu există evaluări