Documente Academic

Documente Profesional

Documente Cultură

Informe Multietapa

Încărcat de

Juan PabloTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Informe Multietapa

Încărcat de

Juan PabloDrepturi de autor:

Formate disponibile

Diseño multietapa: BJT y Darlington.

Juan Pablo Bernal Gómez 20181005140

Jean Sebastian Posada Neira 20181005059

Resumen

En esta práctica de laboratorio se realizará el diseño de una

multietapa amplificadora, con dos transistores BJT en emisor

común y un transistor Darlington. El circuito deberá

amplificar corriente y voltaje, los dos estarán en fase con

respecto a la señal de entrada. El transistor Darlington

disminuirá la ganancia de voltaje debido a las resistencias hie

que hay en su interior, en cambio la ganancia de corriente la

aumentará de forma gigantesca.

1. INTRODUCCIÓN

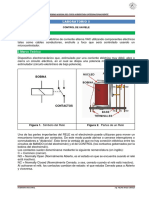

Los transistores BJT y Darlington tienen la misma

representación en AC por ende se analizan de igual manera.

Los transistores BJT en la configuración de emisor común

amplifican tanto voltaje como corriente, pero al momento de

amplificar el voltaje este se desfasa con respecto a la señal

de entrada, Estos transistores se pueden polarizar de

diferentes maneras, en este practica se utilizara la Fig 1. Transistor en la configuración de emisor común.

polarización por divisor de voltaje. El transistor Darlington se Configuración de polarización por medio

utilizara en la configuración de colector común. del divisor de voltaje:

2. OBJETIVO PRINCIPAL Y/O PREGUNTA

DE INVESTIGACIÓN

Entender el funcionamiento de una multietapa.

Analizar los amplificadores diseñados con

anterioridad.

Contrastar las ganancias obtenidas teóricamente con

las experimentales.

3. MARCO TEÓRICO

Configuración Emisor Común:

La configuración de transistor que más frecuentemente se

encuentra aparece en la figura 3.13 para los transistores pnp y Fig 2. Polarización por divisor de voltaje.

npn. Se llama configuración en emisor común porque el Para diseñar amplificadores con esta polarización se deben

emisor es común o sirve de referencia para las terminales de seguir los siguientes consejos:

entrada y salida (en este caso es común para las terminales

base y colector). Establecer los valores de voltaje de ventana (Vce) y

corriente de colector y emisor.

El voltaje de ventana debe ser la mitad del voltaje

Vcc.

Asignar los voltajes que caerán en las resistencias de

colector y emisor.

El valor de la resistencia R2 es igual 0.1βRe.

Hallar la corriente de base y la corriente que pasa

por la resistencia de R2.

El voltaje que cae en R2 es igual al voltaje Vbe mas

el voltaje que cae en la resistencia de emisor.

Obtener el voltaje y la corriente en R1 conociendo

que el voltaje es igual a Vcc menos el voltaje en R2

y la corriente es la corriente de R2 mas la corriente Hallar R1:

de base.

10.3 V

Hallar la resistencia R2 con los valores obtenidos en R 1= =28.6 kΩ

el inciso anterior. 0.36 mA

Circuito equivalente hibrido: Diseño Transistor-2 BJT y Darlington.

Vce=6 v ¿=180Ω Vced=6 v

Ic=2 mA

Hallar Re:

Vre 1.4 v

ℜ= = =7 00 Ω

Fig 3. Circuito hibrido equivalente. Ic 2 mA

Hallar Ied:

4. METODOLOGÍA EXPERIMENTAL Vre d 6v

Ir e d= = =33.33 mA

Montar el circuito de la siguiente figura: ¿ 180 Ω

Hallar Irc:

Ir c=Ic−Ibd =2 mA−33.3 uA=1.9667 mA

Diseñar los amplificadores que se muestran en la anterior Hallar Rc:

figura.

Visualizar las señales de entrada y salida de la etapa Vrc 4.6 v

amplificadora. Rc= = =2. 33 kΩ

I r c 1.9667 mA

5. ANÁLISIS DE RESULTADOS Hallar Ib:

Ic

Ib= =20 uA

Diseño Transistor-1 BJT β

Hallar Vr2:

Vce=6 v V r c=5 v V r e=1 V Vr 2=Vre+Vbe=2.1 V

Ic=2 mA Hallar R2:

Hallar Re: R 2=0.1 βRe=7 kΩ

Vre 1v Hallar Ir2:

ℜ= = =500Ω

Ic 2 mA 2.1V

Ir 2= =0.3 mA

Hallar Rc: 7k

Vr c 5v Hallar Ir1:

R c= = =2.5 k Ω

Ic 2mA Ir 1=Ir 2+ Ib=0 . 3 2mA

Hallar Ib: Hallar Vr1:

Ic Vr 1=Vcc−Vr 2=9.9 V

Ib= =20 uA

β Hallar R1:

Hallar Vr2: 9.9 V

R 1= =30.9 kΩ

Vr 2=Vre+Vbe=1.7 V 0.3 2 mA

Hallar R2: El circuito en Ac es el siguiente:

R 2=0.1 βRe=5 kΩ

Hallar Ir2:

1.7 V

I r 2= =0.34 mA

5k

Hallar Ir1:

I r 1=Ir 2+ Ib=0 . 36 m A

Hallar Vr1:

Vr 1=Vcc−Vr 2=10.3 V

[1] M. Autin, M. Biey, M. Hasler, “Order of discrete time

nonlinear systems determined from input-output signals”,

Proc. IEEE Int. Symp. Circ. Syst., San Diego, 1992, pp. 296-

299

[2] L. Ljung, System Identification-Theory for the User, Prentice

Hall, 1987

[3] S.K. Rao, T. Kailath, “Orthogonal digital filters for VLSI

implementation”, IEEE Trans. Circuits Syst., CAS-31, 1984,

pp. 933-945

Fig 4. Circuito hibrido equivalente del amplificador

multietapa.

Las señales de entrada y salida obtenidas experimental son

las siguientes:

Fig 5.Señal de entrada y salida del amplificador.

Las ganancias de voltaje y corriente obtenidas teóricamente

son las siguientes:

Ganancia Voltaje (Av) Gancia Corriente (Ai)

11.77 40330.60

6. Conclusiones

Referencias

Para las referencias se utilizará una fuente Times New Roman 9.

Deberán figurar en el mismo orden en el cual han aparecido en el

texto.

S-ar putea să vă placă și

- Tarea 2 Fisica Electronica - Sebastian Ortega - Grupo191Document5 paginiTarea 2 Fisica Electronica - Sebastian Ortega - Grupo191Neider SebastianÎncă nu există evaluări

- Fisica Electronica AvancesDocument9 paginiFisica Electronica AvancesNeider Sebastian67% (3)

- Tema07-14 Ejercicios Circuitos Con Transistores BipolaresDocument7 paginiTema07-14 Ejercicios Circuitos Con Transistores Bipolaresodin_auerÎncă nu există evaluări

- Tarea2 Sergio RubioDocument5 paginiTarea2 Sergio RubioPedro Luis Cuspoca TovarÎncă nu există evaluări

- Anexo 2 Formato IEEE DarDocument4 paginiAnexo 2 Formato IEEE DardarinelÎncă nu există evaluări

- Informe Previo Numero 6 HuablochoDocument6 paginiInforme Previo Numero 6 Huablochofieeg4Încă nu există evaluări

- Practica 1 - PolarizacionDocument11 paginiPractica 1 - Polarizacionjrockb1234Încă nu există evaluări

- Tarea 2 - Fabian Escobar - 99Document4 paginiTarea 2 - Fabian Escobar - 99Alexis EscobarÎncă nu există evaluări

- Pre Informe N2Document9 paginiPre Informe N2Walter QuispeÎncă nu există evaluări

- Pre Informe N2Document9 paginiPre Informe N2Walter QuispeÎncă nu există evaluări

- Procedimiento ElectronicaDocument12 paginiProcedimiento ElectronicaHumberto MartinezÎncă nu există evaluări

- Informe Final N 01 Configuracion en CascadaDocument9 paginiInforme Final N 01 Configuracion en CascadacuevaÎncă nu există evaluări

- Anexo 2 Formato IEEE - ...Document4 paginiAnexo 2 Formato IEEE - ...JONATHAN PEREZÎncă nu există evaluări

- Laboratorio 9 de Circuitos Electronicos I Fiee UniDocument6 paginiLaboratorio 9 de Circuitos Electronicos I Fiee UniRuyelMasgoCampos100% (1)

- Informe Nro 4Document18 paginiInforme Nro 4Alexander VinuezaÎncă nu există evaluări

- Practica 7 P60Document6 paginiPractica 7 P60Daniel TacuriÎncă nu există evaluări

- Informe Laboratorio Transistores Polarizado en Divisor de VoltajeDocument4 paginiInforme Laboratorio Transistores Polarizado en Divisor de VoltajeDjjose Meneses Castro67% (3)

- Tarea 1. Individual - Ecuaciones Del Transistor. (Sin Formato)Document4 paginiTarea 1. Individual - Ecuaciones Del Transistor. (Sin Formato)Erick GNÎncă nu există evaluări

- Sesion Vi Circuitos de Corriente Directa-2022-IDocument41 paginiSesion Vi Circuitos de Corriente Directa-2022-IJames Quispe PalizaÎncă nu există evaluări

- Exp Sem 2Document37 paginiExp Sem 2MARIA VICTORIA ALVARADO SOLANOÎncă nu există evaluări

- Informe P 6 Configuracion en CascadaDocument8 paginiInforme P 6 Configuracion en CascadaDany RamosÎncă nu există evaluări

- Practica 0Document11 paginiPractica 0Andy CruzÎncă nu există evaluări

- Unidad 3EADocument53 paginiUnidad 3EAVictor ReyesÎncă nu există evaluări

- LA8 Vicente Moll - Mohamed Azkou Práctica 3 PDFDocument5 paginiLA8 Vicente Moll - Mohamed Azkou Práctica 3 PDFVicente Moll ZamoranoÎncă nu există evaluări

- Oscilador de RelajacionDocument13 paginiOscilador de RelajacionPedro José DuarteÎncă nu există evaluări

- Capitulo4 Análisis y Diseño LaboratorioDocument22 paginiCapitulo4 Análisis y Diseño LaboratorioNICOLAS SOPO BOBADILLAÎncă nu există evaluări

- Practica Amplificador Emisor ComunDocument16 paginiPractica Amplificador Emisor ComunOriana Alejandra Hunca HuisaÎncă nu există evaluări

- Calculo de Un AmplificadorDocument7 paginiCalculo de Un AmplificadorSulen González50% (2)

- EAu-EXO-1213-Examen Ordinario 2013Document7 paginiEAu-EXO-1213-Examen Ordinario 2013Omar RabanalÎncă nu există evaluări

- Cuad Ej An Circ S 1 PDFDocument7 paginiCuad Ej An Circ S 1 PDFMon MoralesÎncă nu există evaluări

- 1565966071ejercicios Ii 2019 Etn 503Document35 pagini1565966071ejercicios Ii 2019 Etn 503Jhan KanamaÎncă nu există evaluări

- Labo 2 FinalDocument7 paginiLabo 2 FinalFrancois ZavaletaÎncă nu există evaluări

- Guia 2 Electronica PDFDocument11 paginiGuia 2 Electronica PDFYojan Peña BerroaÎncă nu există evaluări

- Laboratorio N3 RectificadorDocument11 paginiLaboratorio N3 RectificadorJesus CastilloÎncă nu există evaluări

- FISICADocument2 paginiFISICALina Fernanda Rojas GarciaÎncă nu există evaluări

- Informe Final y Previo N°5Document14 paginiInforme Final y Previo N°5carlos ramirez100% (1)

- Práctica #2 - TransistoresDocument6 paginiPráctica #2 - TransistoresAlvaro CerveraÎncă nu există evaluări

- Electronica - Guía22 - TBJ - RceDocument6 paginiElectronica - Guía22 - TBJ - RcePablo SaquettoÎncă nu există evaluări

- Polarización de TransistoresDocument8 paginiPolarización de TransistoresAxlejandro TKDÎncă nu există evaluări

- Trabajo Electro III Fuentes de CorrienteDocument7 paginiTrabajo Electro III Fuentes de CorrienteDaniel Camilo Malaver MendoaÎncă nu există evaluări

- Vega Angel L5Document18 paginiVega Angel L5JonathanÎncă nu există evaluări

- Informe PR Ctica I Circuitos OsciladoresDocument5 paginiInforme PR Ctica I Circuitos OsciladoresAndrés GómezÎncă nu există evaluări

- LAB2Document10 paginiLAB2Joel Llutari0% (1)

- Laboratorio 2. Circuitos Sujetadores y RecortadoresDocument8 paginiLaboratorio 2. Circuitos Sujetadores y RecortadoresLuis miguel CoteÎncă nu există evaluări

- Informe Electronica (Transistores)Document11 paginiInforme Electronica (Transistores)Juan PedreraÎncă nu există evaluări

- Gabinet2 16 PDFDocument11 paginiGabinet2 16 PDFThaylor EscÎncă nu există evaluări

- Informe Final 4 PapitaDocument8 paginiInforme Final 4 Papitacristhian_sacramentoÎncă nu există evaluări

- Laboratorio de Amplificación de Dos Etapas Con BJT en Emisor ComúnDocument10 paginiLaboratorio de Amplificación de Dos Etapas Con BJT en Emisor ComúnCARLOS REINEL DUARTE PERALTAÎncă nu există evaluări

- Electronica Circuito AstableDocument9 paginiElectronica Circuito AstableIvelisse Aguilar MontillaÎncă nu există evaluări

- Informe Giro Del MotorDocument14 paginiInforme Giro Del MotorRhony IzurietaÎncă nu există evaluări

- Tarea 2 - Luis TimanaDocument4 paginiTarea 2 - Luis TimanaLuis Freddy Timana MoraÎncă nu există evaluări

- Practica 1Document6 paginiPractica 1Jhonny AlvarezÎncă nu există evaluări

- Tarea 6 - Aislamiento ElectricoDocument2 paginiTarea 6 - Aislamiento ElectricoCesar Mauricio DavidÎncă nu există evaluări

- Tarea 1. Individual - Ecuaciones Del Transistor.Document3 paginiTarea 1. Individual - Ecuaciones Del Transistor.Erick GNÎncă nu există evaluări

- CalculosDocument16 paginiCalculosJonathan GualotuñaÎncă nu există evaluări

- Lab 04Document15 paginiLab 04Esteban MontesÎncă nu există evaluări

- Tarea TransistoresDocument6 paginiTarea TransistoresAdolfo QuenallataÎncă nu există evaluări

- Practica 7Document22 paginiPractica 7EverezÎncă nu există evaluări

- Armónicas en Sistemas Eléctricos IndustrialesDe la EverandArmónicas en Sistemas Eléctricos IndustrialesEvaluare: 4.5 din 5 stele4.5/5 (12)

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaDe la EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaÎncă nu există evaluări

- SemiconductoresDocument3 paginiSemiconductoresJuan PabloÎncă nu există evaluări

- Examen FinalDocument3 paginiExamen FinalJuan PabloÎncă nu există evaluări

- Pensum Ing Electronica2015IIIDocument1 paginăPensum Ing Electronica2015IIIMiguel Angel Rodriguez FuentesÎncă nu există evaluări

- Proyecto 04 - 20Document4 paginiProyecto 04 - 20Juan PabloÎncă nu există evaluări

- Magnitudes Fundamentales de La FísicaDocument2 paginiMagnitudes Fundamentales de La FísicaJuan PabloÎncă nu există evaluări

- Manual Analizador PDFDocument111 paginiManual Analizador PDFAlexanderGongoraÎncă nu există evaluări

- TallerDocument1 paginăTallerJuan PabloÎncă nu există evaluări

- EjerciciosDocument3 paginiEjerciciosJuan PabloÎncă nu există evaluări

- Plantilla RateDocument2 paginiPlantilla RateJuan PabloÎncă nu există evaluări

- Entrada y SalidaDocument22 paginiEntrada y SalidaJuan PabloÎncă nu există evaluări

- Problemas Resueltos Cap 15 Fisica Edic 6 SerwayDocument4 paginiProblemas Resueltos Cap 15 Fisica Edic 6 SerwayWill F. Piedrahita94% (16)

- Pensum Ing Electronica2015IIIDocument1 paginăPensum Ing Electronica2015IIIMiguel Angel Rodriguez FuentesÎncă nu există evaluări

- G3-Labo 4 FinalDocument11 paginiG3-Labo 4 FinalDavid LizarmeÎncă nu există evaluări

- Proyecto Termo Inalámbrico para Mantener Agua CalienteDocument52 paginiProyecto Termo Inalámbrico para Mantener Agua CalienteLucio Gastón AbrateÎncă nu există evaluări

- Informe Final Diodos RectificadoresDocument10 paginiInforme Final Diodos RectificadoresSergio MarceloÎncă nu există evaluări

- Practica Campo Electrico 2Document6 paginiPractica Campo Electrico 2Veronica Patiño ArancibiaÎncă nu există evaluări

- Radiaciones No Ionizantes - P3Document13 paginiRadiaciones No Ionizantes - P3luis rodriguezÎncă nu există evaluări

- Santiago - Martinez - Laboratorio Fisica - Electronica - Grupo - 17Document5 paginiSantiago - Martinez - Laboratorio Fisica - Electronica - Grupo - 17santiago martinez bocanegraÎncă nu există evaluări

- Lista Temas TG GISEL-2020-2Document7 paginiLista Temas TG GISEL-2020-2Juan MorenoÎncă nu există evaluări

- DiacDocument6 paginiDiacapi-275653499Încă nu există evaluări

- Informe Resitividad y Ley de Ohm-1Document5 paginiInforme Resitividad y Ley de Ohm-1Cuenta Secundaria100% (1)

- Informe Control6Document6 paginiInforme Control6Giovanna Sandoval IriarteÎncă nu există evaluări

- Laboratorio 5Document4 paginiLaboratorio 5Felipe ApazaÎncă nu există evaluări

- Ingeniería de Control Moderna Ogata 5a EdDocument6 paginiIngeniería de Control Moderna Ogata 5a EdGenaro LopezÎncă nu există evaluări

- Actividad 13. Ley de FaradayDocument4 paginiActividad 13. Ley de FaradayMichelle HoranÎncă nu există evaluări

- TPP1 Electrostática 2021Document6 paginiTPP1 Electrostática 2021Marcos Horacio SarasolaÎncă nu există evaluări

- Actividad7 FisicaDocument6 paginiActividad7 FisicaEquipo 1Încă nu există evaluări

- Translate - SueloDocument9 paginiTranslate - SueloGabrielaÎncă nu există evaluări

- Evaluación Parcial - Control IDocument5 paginiEvaluación Parcial - Control IChristian Guzman TrilloÎncă nu există evaluări

- Examen de Instalciones Electricas IDocument2 paginiExamen de Instalciones Electricas IRossel Chipana100% (1)

- Arrancadores Magnéticos A Tensión ReducidaDocument13 paginiArrancadores Magnéticos A Tensión ReducidaOmar GeedorahÎncă nu există evaluări

- Tema 01 Carga y Fuerza Electrica - ProblemasDocument13 paginiTema 01 Carga y Fuerza Electrica - Problemaspaul caicayÎncă nu există evaluări

- Exposicion - Proteccion de Lineas de Media TensiónDocument60 paginiExposicion - Proteccion de Lineas de Media Tensióncjvl1Încă nu există evaluări

- Antena Loop para Onda CortaDocument11 paginiAntena Loop para Onda CortaMonchouno100% (1)

- Megóhmetro Electronico Circutor Mi-5500Document18 paginiMegóhmetro Electronico Circutor Mi-5500Alejandro Guzmán SantosÎncă nu există evaluări

- Lab 10 - 090725Document31 paginiLab 10 - 090725William Rafael GonzalesÎncă nu există evaluări

- Física 5to AñoDocument4 paginiFísica 5to Añocarolina0% (1)

- YS K32.zh-CN - EsDocument13 paginiYS K32.zh-CN - Esatom2013xdÎncă nu există evaluări

- Sec 4to Ses Fìsica s31Document14 paginiSec 4to Ses Fìsica s31Greisy AdrianaÎncă nu există evaluări

- Problema de Magnetismo y Induccion MagneticasDocument10 paginiProblema de Magnetismo y Induccion MagneticasEva Janet Chávez CamposÎncă nu există evaluări

- Avance Curricular: Universidad Nacional de IngenieriaDocument3 paginiAvance Curricular: Universidad Nacional de IngenieriaMarco RafaelÎncă nu există evaluări

- 03 Problema G.S Operacion Paralelo Teorema PullenDocument8 pagini03 Problema G.S Operacion Paralelo Teorema PullenNestorMartinHuapayaÎncă nu există evaluări