Documente Academic

Documente Profesional

Documente Cultură

50992227FMJN - Digital Principles & System Design - Solution Manual

Încărcat de

Vimal RajDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

50992227FMJN - Digital Principles & System Design - Solution Manual

Încărcat de

Vimal RajDrepturi de autor:

Formate disponibile

1 Review of Number Systems

Solutions of Selected Examples for Practice

Example 1.3.16

Solution : Integer part : Conversion of integer part by successive division method.

Q R

8 153 1 LSD

8 19 3

8 2 2 MSD

Fig. 1.1

\ (153) 10 = (231) 8

Fractional part : Conversion of fractional part by successive multiplication method.

Fraction Base Product MSD

0.513 × 8 = 4 . 104 4

0

0.104 × 8 = 0 . 832

6

0.832 × 8 = 6 . 656

5

0.656 × 8 = 5 . 248 LSD

Fig. 1.2

\ (0.513) 10 = (0.4065) 8

\ (153.513) 10 = (231.4065) 8

(1 - 1) TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 1-2 Review of Number Systems

Example 1.3.17

Solution : i) Hexadecimal to binary conversion

Step 1 : Write equivalent 4-bit binary number of each hexadecimal digit.

Step 2 : Remove any leading or trailing zero.

1 0 1 0 . 1 0

Step 1. 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 . 0 0 0 1 0 0 0 0

Step 2. 1 0 0 0 0 0 0 0 1 0 0 0 0 . 0 0 0 1

Leading Trailing

zeros zeros

Fig. 1.3

\ (1010.10) 16 = (1000000010000.0001) 2

ii) Binary to octal conversion

Step 1 : Make group of 3-bits starting from LSB for integer part and MSB for fractional

part by adding 0s at the end, if required.

Step 2 : Write equivalent octal number for each group of 3-bits.

Binary

Step 1 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 × 0 0 0 1 0 0 (Base 2)

× Octal

Step 2 1 0 0 2 0 0 4 (Base 8)

Adding 0s to make Adding 0s to make

a group of 3-bits a group of 3-bits

Fig. 1.4

\ (1000000010000.0001) 2 = (10020.04) 8

iii) Octal to decimal conversion

N = 1 ´ 8 4 + 0 ´ 8 3 + 0 ´ 8 2 + 2 ´ 8 1 + 0 ´ 8 0 + 0 ´ 8 –1 + 4 ´ 8 –2

= 4096 + 0 + 0 + 16 + 0 + 0 + 0.0625

= 4112.0625

\ (10020.04) 8 = (4112.0625) 10

Example 1.3.18

Solution : i) Decimal to octal conversion

Integer part : Conversion of integer part by successive division method.

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 1-3 Review of Number Systems

Q R

LSD

8 1947 3

8 243 3

8 30 6

8 3 3 MSD

Fig. 1.5

\ (1947) 10 = (3633) 8

ii) Decimal to hexadecimal conversion

Integer part : Conversion of integer part by successive division method.

Q R

LSD

16 1947 11(B)

16 121 9

16 7 7

MSD

0

Fig. 1.6

\ (1947) 10 = (79B) 16

qqq

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Boolean Algebra

2 and Logic Gates

Solutions of Selected Examples for Practice

Example 2.3.4

Solution : F1 = AB + C D + A B C

= AB × (C + C) × (D + D) + (A + A) × (B + B) × C D + A B C(D + D)

= AB × (C D + C D + C D + C D) + (AB + A B + AB + A B) × C D + A B CD + A B CD

= AB C D + AB C D + AB C D + AB C D + AB C D

+ A B C D + AB C D + A B C D + A B C D + A B C D

= A B CD +A B CD +A B CD +A B CD +A B CD

+ ABCD + ABCD + ABCD + ABCD

Example 2.3.5

Solution : f(x, y, z) = (xy + z)(y + xz)

= xy + xyz + yz + xz

= xy × (z + z) + xyz + yz(x + x) + xz × (y + y)

= xyz + xyz + xyz + xyz + xyz + xyz + xyz

= xyz + xyz + xyz + x yz

Example 2.3.12

Solution : f(P, Q, R) = (P + Q)(P + R)

= [(P + Q) + (R × R)][(P + R) + (Q × Q)]

= (P + Q + R) × (P + Q + R) × (P + Q + R) × (P + Q + R)

= (P + Q + R) × (P + Q + R) × (P + Q + R)

(2 - 1)

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-2 Boolean Algebra and Logic Gates

Example 2.5.13

Solution :

CD

AB 00 01 11 10

BC

00 1 X

01 X 1 1 BD

11 X 1 1

10 1 1 1 1 AC

Fig. 2.1

\ F(A, B, C, D) = BC + BD + AC

Example 2.5.14

Solution : i)

BC

A 00 01 11 10

1 1 1 X A

0

1 X 1

Fig. 2.2

\ f(A, B, C) = A + C

ii)

yz

wx 00 01 11 10

00 1 X

xz

01 X 1 wxz

11 1 X

10 1 1 1

wy

Fig. 2.3

\ F(w, x, y, z) = wy + x z + wxz

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-3 Boolean Algebra and Logic Gates

Example 2.6.5

Solution :

yz

x y+z y+z y+z y+z

x 0 y+z

x 0 0

x+z

Fig. 2.4

\ f(x, y, z) = (x + z)(y + z)

Example 2.6.6

Solution :

RS RS

PQ R+S R+S R+S R+S PQ R+S R+S R+S R+S

P+Q+R P+Q+S

P+Q 0 0 0 P+Q 0 0 0

P+Q+R+S

P+Q P+Q+S P+Q

P+Q P+Q

P+Q 0 0 P+Q+R P+Q 0 0 (Q+R)

Fig. 2.5

\ f(P, Q, R, S) = (P + Q+ S) × (Q + R)

Example 2.7.4

Solution :

A=0 A=1

DE DE

00 01 11 10 BC 00 01 11 10

BC

00 1 1 BCD

00 1 1

ABD

01 1 1

01 1

11

11 1

10

10 1

AD E

Fig. 2.6

\ F(A,B,C,D,E) = ABD + ADE + BCD

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-4 Boolean Algebra and Logic Gates

Example 2.11.5

Solution :

Minterms Binary representation Minterms Binary representation

m0 00000 m0 ü 00000

m1 00001 m1 ü 00001

m2 00010 m2 ü 00010

m8 01000 m8 ü 01000

m9 01001 m9 ü 01001

m 15 01111 m 17 ü 10001

m 17 10001 m 24 ü 11000

m 21 10101 m 21 ü 10101

m 24 11000 m 25 ü 11001

m 25 11001 m 15 01111

m 27 11011 m 27 ü 11011

m 31 11111 m 31 11111

Minterms Binary representation

0, 1 ü 0000-

0, 2 000-0

0, 8 ü 0-000

8, 9 0100-

17, 21 10-01

24, 25 ü 1100-

25, 27 110-1

15, 31 -1111

0, 1, 8, 9 0-00-

8, 9, 24, 25 -100-

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-5 Boolean Algebra and Logic Gates

Prime implicants Binary representation

A BC E 0, 2 000-0

A CDE 0, 8 0-000

A B DE 17, 21 10-01

AB CE 25, 27 110-1

BCDE 15, 31 -1111

A CD 0, 1, 8, 9 0-00-

BCD 8, 9, 24, 25 -100-

Prime m0 m1 m2 m8 m9 m15 m17 m21 m24 m25 m27 m31

implicants

ABCE 0, 2

ACDE 0, 8

ABDE 17, 21

ABCE 25, 27

BCDE 15, 31

ACD 0,1,8,9

BCD 8,9,24,25

F = ( 0 0 0 - 0) + (1 0 - 0 1) + (1 1 0 - 1) + ( -1 1 1 1) + ( 0 - 0 0-) + ( -1 0 0-)

F = ABCE + ABDE + ABCE + BCDE + ACD + BCD

Example 2.11.6

Solution : f = Õ M( 0,1, 4,11,13,15) + Õ d(5,7 , 8)

= å m( 2, 3, 6, 9,10,12,14) + d(5,7 , 8)

Minterms Binary representation Minterms Binary representation

m2 0010 m2 ü 0010

m3 0011 dm 8 ü 1000

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-6 Boolean Algebra and Logic Gates

m6 0110 m3 ü 0011

m9 1001 m6 ü 0110

m 10 1010 m9 ü 1001

m 12 1100 m 10 ü 1010

m 14 1110 m 12 ü 1100

dm 5 0101 dm 5 ü 0101

dm 7 0111 m 14 ü 1110

dm 8 1000 dm 7 ü 0111

Minterms Binary representation Minterms Binary representation

2, 3 ü 001- 2, 3, 6, 7 ü 0-1-

2, 6 ü 0-10 2, 6, 10, 14 --10

2, 10 ü -010 8, 10, 12, 14 ü 1--0

8, 9 100-

8, 10 ü 10-0

8, 12 1-00

3, 7 ü 0-11

6, 7 ü 011-

6, 14 ü -110

10, 14 ü 1-10

12, 14 ü 11-0

5, 7 01-1

Prime implicants Binary representation

A BC ü 8, 9 100-

ACD 8, 12 1-00

ABD 5, 7 01-1

ACü 2, 3, 6, 7 0-1-

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-7 Boolean Algebra and Logic Gates

CD 2, 6, 10, 14 --10

ADü 8, 10, 12, 14 1--0

Prime implicants m2 m3 m6 m9 m10 m12 m14 dm5 dm7 dm8

CD

AB 00 01 11 10

ABC 8, 9

00 1 1 AC

ACD 8, 12 01 X X 1

ABD 5,7 11 1 1

10 X 1 1

AC 2,3,6,7

AD

CD 2,6,10,14 ABC

AD 8,10,12,14

F = (1 0 0 -) + ( 0 - 1 -) + (1 - - 0)

\ F = ABC + AC + AD

Example 2.11.7

Solution :

Minterms Binary representation Minterms Binary representation

m0 00000 m0 ü 00000

m1 00001 m1 ü 00001

m4 00100 m4 ü 00100

m5 00101 m 16 ü 10000

m 16 10000 m5 ü 00101

m 17 10001 m 17 ü 10001

m 21 10101 m 21 ü 10101

m 25 11001 m 25 ü 11001

m 29 11101 m 29 ü 11101

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-8 Boolean Algebra and Logic Gates

Minterms Binary representation Minterms Binary representation

0, 1 ü 0000- 0, 1, 4, 5 00-0-

0, 4 ü 00-00 0, 1, 16, 17 -000-

0, 16 ü -0000 1, 5, 17, 21 -0-01

1, 5 ü 00-01 17, 21, 25, 29 1--01

1, 17 ü -0001

4, 5 ü 0010-

16, 17 ü 1000-

5, 21 ü -0101

17, 21 ü 10-01

21, 29 ü 1-101

25, 29 ü 11-01

Prime implicants Binary representation

x1 x2 x4 0, 1, 4, 5 00-0-

x2 x3 x4 0, 1, 16, 17 -000-

x2 x4 x5 1, 5, 17, 21 -0-01

x1 x4 x5 17, 21, 25, 29 1--01

Prime implicants m0 m1 m4 m5 m16 m17 m21 m25 m29

x1x2x4 0, 1, 4, 5

x2x3x4 0, 1, 16, 17

x2x4x5 1, 5, 17, 21

x1x4x5 17, 21, 25, 29

F = (1 - - 0 1) + (- 0 0 0 -) + (0 0 - 0 -)

F = x 1 x 4x 5 + x 2 x3 x 4 + x 1 x 2 x 4

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2-9 Boolean Algebra and Logic Gates

Example 2.11.8

Solution :

Minterms Binary representation Minterms Binary representation

m1 0001 m1 ü 0001

m4 0100 m4 ü 0100

m6 0110 m8 ü 1000

m7 0111 m6 ü 0110

m8 1000 m9 ü 1001

m9 1001 m 10 ü 1010

m 10 1010 m7 ü 0111

m 11 1011 m 11 ü 1011

m 15 1111 m 15 ü 1111

Minterms Binary representation Minterms Binary representation

1, 9 -001 8, 9, 10, 11 10--

4, 6 01-0

8, 9 ü 100-

6, 7 011-

9, 11 10-1

10, 11 ü 101-

7, 15 -111

11, 15 1-11

Prime implicants Binary representation

BCD 1, 9 -001

ABD 4, 6 01-0

ABC 6, 7 011-

A BD 9, 11 10-1

BCD 7, 15 -111

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2 - 10 Boolean Algebra and Logic Gates

ACD 11, 15 1-11

AB 8, 9, 10, 11 10--

Prime m1 m4 m6 m7 m8 m9 m10 m11 m15

implicants

BCD 1,9

ABD 4,6

ABC 6,7

ABD 9,11

BCD 7,15

ACD 11,15

AB 8,9,10,11

\ F = (- 0 0 1) + (0 1 - 0) + (- 1 1 1) + (1 0 - -)

F = B CD+A B D+ B C D+A B

Example 2.11.9

Solution :

Minterms Binary representation Minterms Binary representation

m0 000000 m0 ü 000000

m5 000101 m8 ü 001000

m7 000111 m5 ü 000101

m8 001000 m9 ü 001001

m9 001001 m 12 ü 001100

m 12 001100 m 24 ü 011000

m 13 001101 m 40 ü 101000

m 23 010111 m7 ü 000111

m 24 011000 m 13 ü 001101

m 25 011001 m 25 ü 011001

m 28 011100 m 28 ü 011100

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2 - 11 Boolean Algebra and Logic Gates

m 29 011101 m 37 ü 100101

m 37 100101 m 42 ü 101010

m 40 101000 m 44 ü 101100

m 42 101010 m 56 ü 111000

m 44 101100 m 23 ü 010111

m 46 101110 m 29 ü 011101

m 55 110111 m 46 ü 101110

m 56 111000 m 57 ü 111001

m 57 111001 m 60 ü 111100

m 60 111100 m 55 ü 110111

m 61 111101 m 61 ü 111101

Minterms Binary representation Minterms Binary representation

0, 8 00-000 8, 9, 12, 13 ü 001-0-

8, 9 ü 00100- 8, 9, 24, 25 ü 0-100-

8, 12 ü 001-00 8, 12, 24, 28 ü 0-1-00

8, 24 ü 0-1000 8, 12, 40, 44 ü -01-00

8, 40 ü -01000 8, 24, 40, 56 ü --1000

5, 7 0001-1 9, 13, 25, 29 ü 0-1-01

5, 13 00-101 12, 13, 28, 29 ü 0-110-

5, 37 -00101 24, 25, 28, 29 ü 011-0-

9, 13 ü 001-01 24, 25, 56, 57 ü -1100-

9, 25 ü 0-1001 24, 28, 56, 60 ü -11-00

12, 13 ü 00110- 25, 29, 57, 61 ü -11-01

12, 28 ü 0-1100 28, 29, 60, 61 ü -1110-

12, 44 ü -01100 40, 42, 44, 46 101--0

24, 25 ü 01100- 56, 57, 60, 61 ü 111-0-

24, 28 ü 011-00

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2 - 12 Boolean Algebra and Logic Gates

24, 56 ü -11000

40, 42 ü 1010-0

40, 44 ü 101-00

40, 56 ü 1-1000

7, 23 0-0111

13, 29 ü 0-1101

25, 29 ü 011-01

25, 57 ü -11001

28, 29 ü 01110-

28, 60 ü -11100

42, 46 ü 101-10

44, 46 ü 1011-0

56, 57 ü 11100-

56, 60 ü 111-00

23, 55 -10111

29, 61 ü -11101

57, 61 ü 111-01

60, 61 ü 11110-

Minterms Binary representation

8, 9, 12, 13, 24, 25, 28, 29 0-1-0-

8, 12, 24, 28, 40, 44, 56, 60 --1-00

24, 25, 28, 29, 56, 57, 60, 61 -11-0-

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 2 - 13 Boolean Algebra and Logic Gates

Prime implicants Binary representation

A BDEF ü 0, 8 00-000

A BCDF ü 5, 7 0001-1

A BD EF 5, 13 00-101

B C D EF ü 5, 37 -00101

A CDEF 7, 23 0-0111

B CDEF ü 23, 55 -10111

A BC F ü 40, 42, 44, 46 101--0

ACEü 8, 9, 12, 13, 24, 25, 28, 29 0-1-0-

C EF 8, 12, 24, 28, 40, 44, 56, 60 --1-00

BC Eü 24, 25, 28, 29, 56, 57, 60, 61 -11-0-

Prime implicants m0 m5 m7 m8 m9 m12 m13 m23 m24 m25 m28 m29 m37 m40 m42 m44 m46 m55 m56 m57 m60 m61

ABDEF 0,8

ABCDF 5,7

ABDEF 5,13

BCDEF 5,37

ACDEF 7,23

BCDEF 23,55

ABCF 40,42,44,46

ACE 8,9,12,13,24,25,28,29

CEF 8,12,24,28,40,44,56,60

BCE 24,25,28,29,56,57,60,61

F = (0 0 - 0 0 0) + (0 0 0 1 - 1) + (- 0 0 1 0 1) + (- 1 0 1 1 1)

+ (1 0 1 - - 0) + (0 - 1 - 0 -) + (- 1 1 - 0 -)

F = A B D E F + A B CD F + B CD EF + B CD E F + A B C F + A C E + B C E

qqq

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

3 Combinational Logic

Solutions of Selected Examples for Practice

Example 3.3.6

Solution : Truth table

Input Output K-map simplification

BC

A B C Y A 00 01 11 10

0 1 1 0 1

0 0 0 1

0 0 1 1 1 1 0 0 0

0 1 0 1

Y = BC + AB + AC

0 1 1 0 Fig. 3.1

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 0

Logic diagram

B BC

C

AB

Y

A

AC

Fig. 3.2

(3 - 1)

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 3-2 Combinational Logic

Example 3.7.10

Solution :

Y0

Y1 f1

Y2

A A 3:8 Y3

B B Decoder

Y4

C C Y 5 f2

Y6

Y7 f3

Fig. 3.3

Example 3.9.22

Solution : Implementation table :

D0 D1 D2 D3 D4 D5 D6 D7

A 0 1 2 3 4 5 6 7

A 8 9 10 11 12 13 14 15

1 1 0 A A 0 0 A

Fig. 3.4

Implementation :

A 1

D0

A D1

D2

D3 8:1

MUX Y Y

D4

D5

D6

D7

0 S2 S1 S0

B C D

Fig. 3.5

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 3-3 Combinational Logic

Example 3.9.23

Solution : F(A, B, C, D) = Õ M(0, 3, 5, 8, 9, 10, 12, 14)

= å m(1, 2, 4, 6, 7, 11, 13, 15)

Implementation table :

D0 D1 D2 D3 D4 D5 D6 D7

A 0 1 2 3 4 5 6 7

A 8 9 10 11 12 13 14 15

0 A A A A A A 1

Fig. 3.6

Implementation :

A

0

D0

A

D1

D2

D3 8:1

MUX Y Y

D4

D5

D6

1 D7

S2 S1 S0

B C D

Fig. 3.7

Example 3.9.24

Solution : Implementation table

I0 I1 I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

A

A 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0 A A 0 0 0 0 0 0 A A 0 0 0 A 0

Fig. 3.8

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 3-4 Combinational Logic

Implementation

A

I0

I1

I2

I3

I4

I5

I6

I7 16:1

Y

I8 MUX

I9

I10

I11

I12

I13

I14

I15

S3 S2 S1 S0

B C D E

Fig. 3.9

Example 3.10.6

Solution : Step 1 : Truth table

Inputs Outputs

A B Cin Carry Sum

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 3-5 Combinational Logic

Step 2 : Carry is given by

C = å m(3, 5, 6, 7)

and sum is given by

S = å m(1, 2, 4, 7)

Step 3 : Logic diagram

Y0

Y1

Y2

Y3 S

1:8

Din = 1

DEMUX Y4

Y5 C

Y6

Y7

S0 S1 S2

A B C

Fig. 3.10

Example 3.10.7

Solution :

Y0

Y1

Y2

Y3 f1

1:8

Din = 1 DEMUX Y4

Y5

Y6 f2

Y7

S2 S1 S0

A B C

Fig. 3.11

qqq

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

7 Counters

Solutions of Selected Examples for Practice

Example 7.3.5

Solution :

Step 1 : Number of flip-flops required.

As the counter goes through 0 - 4 states,

Total states = 5

\ N=5

We know that

2n ³ N \ n = 3 i.e. 3 flip-flops are required.

Step 2 : Types of flip-flop to be used : T

Step 3 : Truth table

CLK A B C Output(y)

0 0 0 0 1

1 0 0 1 1

2 0 1 0 1 Valid

states

3 0 1 1 1

4 1 0 0 1

- 1 0 1 0

- Invalid

1 1 0 0

states

- 1 1 1 0

Fig. 7.1

Step 4 : K-map simplification

BC

A 00 01 11 10

0 1 1 1 1 A

\ y = A + BC

1 1 0 0 0

BC

Fig. 7.2

(7 - 1)

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 7-2 Counters

Step 5 : Logic diagram

Logic 1

TA A TB B TC C

CLK A CLK B CLK C

A B C

Reset logic

Fig. 7.3

Example 7.5.19

Solution :

Step 1 : Number of flip-flops required

2n ³ N

Here N = 11 \ n = 4 i.e. four flip-flops are required.

Step 2 : Type of flip-flop to be used : JK

Step 3 : Determine the excitation table for the counter

Qn Q n+1 J K

0 0 0 Ï

0 1 1 Ï

1 0 Ï 0

1 1 Ï 0

Present state Next state Flip-flop inputs

QD QC QB QA Q +D Q +C Q +B +

QA JD KD JC KC JB KB JA KA

0 0 0 0 0 0 0 1 0 Ï 0 Ï 0 Ï 1 Ï

0 0 0 1 0 0 1 0 0 Ï 0 Ï 1 Ï Ï 1

0 0 1 0 0 0 1 1 0 Ï 0 Ï Ï 0 1 Ï

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 7-3 Counters

0 0 1 1 0 1 0 0 0 Ï 1 Ï Ï 1 Ï 1

0 1 0 0 0 1 0 1 0 Ï Ï 0 0 Ï 1 Ï

0 1 0 1 0 1 1 0 0 Ï Ï 0 1 Ï Ï 1

0 1 1 0 0 1 1 1 0 Ï Ï 0 Ï 0 1 Ï

0 1 1 1 1 0 0 0 1 Ï Ï 1 Ï 1 Ï 1

1 0 0 0 1 0 0 1 Ï 0 0 Ï 0 Ï 1 Ï

1 0 0 1 1 0 1 0 Ï 0 0 Ï 1 Ï Ï 1

1 0 1 0 0 0 0 0 Ï 1 0 Ï Ï 1 0 Ï

1 0 1 1 Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï

1 1 0 0 Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï

1 1 0 1 Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï

1 1 1 0 Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï

1 1 1 1 Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï Ï

Step 4 : K-map simplification

For JD For KD

QCQD QCQD

QAQB 00 01 11 10 QAQB 00 01 11 10

00 0 0 0 0 00 X X X X

01 0 0 1 0 01 X X X X

11 X X X X 11 X X X X

10 X X X X 10 0 0 X 1

JD = QBQCQD KD = QC

QCQD For JC QCQD For KC

QAQB 00 01 11 10 QAQB 00 01 11 10

00 0 0 1 0 00 X X X X

01 X X X X 01 0 0 1 0

11 X X X X 11 X X X X

10 0 0 X 0 10 X X X X

JC = QCQD KC = QCQD

Fig. 7.4

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 7-4 Counters

QCQD For JB QCQD For KB

QAQB 00 01 11 10 QAQB 00 01 11 10

00 0 1 X X 00 X X 1 0

01 0 1 X X 01 X X 1 0

11 X X X X 11 X X X X

10 0 1 X X 10 X X X 1

JB = QD KB = QA + QD

QCQD For JA QCQD For KA

QAQB 00 01 11 10 QAQB 00 01 11 10

00 1 X X 1 00 X 1 1 X

01 1 X X 1 01 X 1 1 X

11 X X X X 11 X X X X

10 1 X X 0 10 X 1 X X

JA = QA + QC KA = 1

Fig. 7.4

Step 5 : Logic diagram

QA QC QB

JA QA QD JB QB JC QC QC JD QD

QC QD QD

A B C D

1 QA

KA QA KB QB KC QC QC KD QD

QD

CLK

(LSB)QA QB QC QD(MSB)

Output

Fig. 7.5

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 7-5 Counters

Example 7.5.20

Solution : Excitation table

Present state Next state Flip-flop inputs

A B C A+ B+ C+ DA DB DC

0 0 0 0 0 1 0 0 1

0 0 1 0 1 0 0 1 0

0 1 0 0 1 1 0 1 1

0 1 1 1 0 0 1 0 0

1 0 0 1 0 1 1 0 1

1 0 1 1 1 0 1 1 0

1 1 0 1 1 1 1 1 1

1 1 1 0 0 0 0 0 0

K-map simplification

For DA For DB

BC BC

A 00 01 11 10 A 00 01 11 10

0 0 0 1 0 0 0 1 0 1

1 1 1 0 1 1 0 1 0 1

DA = AB + AC + ABC DB = BC + BC

=BÅC

For DC

BC

A 00 01 11 10

0 1 0 0 1

1 1 0 0 1

DC = C

Fig. 7.6

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 7-6 Counters

Logic diagram

A B A C A BC

B

DA A DB B DC C

C

A B C

A B C

CLK

A (LSB) B C (MSB)

Output

Fig. 7.7

qqq

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Memory and Programmable

10 Logic Devices

Solutions of Selected Examples for Practice

Example 10.7.5

Solution :

Step 1 : K-map simplification

For f1 For f2

bc bc

a 00 01 11 10 a 00 01 11 10

0 1 1 0 1 1

1 1 1 1 1 1

f1 = ab + ab f1 = ab + ac

Fig. 10.1

Step 2 : PAL program table

Product term AND Inputs Outputs

a b c

1. 0 0 - f1 = ab + ab

2. 1 1 -

3. 0 1 - f2 = ab + ac

4. 1 - 1

(10 - 1)

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

Digital Principles and System Design 10 - 2 Memory and Programmable Logic Devices

Step 3 : Logic diagram

a a b b c c

1

f1

f2

Fig. 10.2

qqq

TM

TECHNICAL PUBLICATIONS - An up thrust for knowledge

S-ar putea să vă placă și

- BIT DL 1 1Document20 paginiBIT DL 1 1prajwol neupaneÎncă nu există evaluări

- Chapter 0 - Introduction To ComputingDocument43 paginiChapter 0 - Introduction To ComputingBuket CüvelenkÎncă nu există evaluări

- Digital Logic Design (R17a0461) (1) - 7-130Document124 paginiDigital Logic Design (R17a0461) (1) - 7-130Slim ShadyÎncă nu există evaluări

- Awers Af34125Document1 paginăAwers Af34125kingofpaladinsÎncă nu există evaluări

- Lecture 01 Number ConversionDocument18 paginiLecture 01 Number ConversionSuresh BabuÎncă nu există evaluări

- EOC - Number SystemDocument7 paginiEOC - Number SystemElawarasi NadarajanÎncă nu există evaluări

- Exp-7 PlotDocument4 paginiExp-7 PlotSwaroop MallickÎncă nu există evaluări

- Cse 205: Digital Logic Design: Dr. Tanzima Hashem Assistant Professor Cse, BuetDocument55 paginiCse 205: Digital Logic Design: Dr. Tanzima Hashem Assistant Professor Cse, BuetShakib AhmedÎncă nu există evaluări

- Chapter - 6 Data RepresentationDocument8 paginiChapter - 6 Data RepresentationAshish SharmaÎncă nu există evaluări

- 4 - Machine Level Representation of Data-LatestDocument47 pagini4 - Machine Level Representation of Data-LatestjojoÎncă nu există evaluări

- WK2 3 Conversions of Number System Part1 Whole NumbersDocument15 paginiWK2 3 Conversions of Number System Part1 Whole NumbersJhin KhadaÎncă nu există evaluări

- Logic Design Lec 1Document7 paginiLogic Design Lec 1Ggfgsgege GegsgsÎncă nu există evaluări

- Chapter 2Document64 paginiChapter 2Muhammad NazmiÎncă nu există evaluări

- Chapter 1 - Digital LogicDocument18 paginiChapter 1 - Digital Logicvc78it10Încă nu există evaluări

- Chapter 3: Number System: Summary of Number SystemsDocument9 paginiChapter 3: Number System: Summary of Number SystemsdagneÎncă nu există evaluări

- Octal and Hexadecimal Number Systems: © 2014 Project Lead The Way, Inc. Digital ElectronicsDocument25 paginiOctal and Hexadecimal Number Systems: © 2014 Project Lead The Way, Inc. Digital ElectronicsAJÎncă nu există evaluări

- Lec 1 - Number Systems and Digital LogicDocument38 paginiLec 1 - Number Systems and Digital LogicSAVILASH A/L RAVINDRANÎncă nu există evaluări

- UntitledDocument156 paginiUntitledRameshchandra K ECEÎncă nu există evaluări

- Unit - 1 Number Systems & Boolean Algebra: Introduction About Digital SystemDocument111 paginiUnit - 1 Number Systems & Boolean Algebra: Introduction About Digital SystemRCEE-2020 ONLINE FDPÎncă nu există evaluări

- Digital Number System: Dr. A.K. SinghDocument15 paginiDigital Number System: Dr. A.K. SinghSomya ShuklaÎncă nu există evaluări

- CMPE 011 Reviewer MidtermsDocument5 paginiCMPE 011 Reviewer MidtermsJohn Rave Manuel GonzalesÎncă nu există evaluări

- Number System ConversionDocument8 paginiNumber System Conversiongeddam06108825Încă nu există evaluări

- Chapter 3Document64 paginiChapter 3ZeÎncă nu există evaluări

- LASU CSC 111 Notes ManualDocument14 paginiLASU CSC 111 Notes ManualOluwatoyin TobiÎncă nu există evaluări

- Logic Design Dr. Yosry A. AzzamDocument52 paginiLogic Design Dr. Yosry A. AzzamdvfgdfggdfÎncă nu există evaluări

- Topic To Be Covered Number System Integer Arithmetic Integer Arithmetic Floating Point ArithmeticDocument47 paginiTopic To Be Covered Number System Integer Arithmetic Integer Arithmetic Floating Point ArithmeticAbdulaziz TilahunÎncă nu există evaluări

- Lecture 2Document26 paginiLecture 2علي صالحÎncă nu există evaluări

- Ade Units Iii-VDocument101 paginiAde Units Iii-VanithaÎncă nu există evaluări

- CSC 111 Lecture 4Document61 paginiCSC 111 Lecture 4LawalÎncă nu există evaluări

- Soft PLC Soft PLC CFW CFW - 11 11: Introduction To Numbering Introduction To Numbering Systems SystemsDocument73 paginiSoft PLC Soft PLC CFW CFW - 11 11: Introduction To Numbering Introduction To Numbering Systems SystemsJulia-e Regina-e AlexandreÎncă nu există evaluări

- IIP Midterm SolDocument7 paginiIIP Midterm SolSacky SackÎncă nu există evaluări

- FDMcodeDocument9 paginiFDMcodeViswanath KapavarapuÎncă nu există evaluări

- Prof. A.K. Singh: What Is Number? What Is Number System? Why Number System Is Needed?Document13 paginiProf. A.K. Singh: What Is Number? What Is Number System? Why Number System Is Needed?Somya ShuklaÎncă nu există evaluări

- Weekly Report: Numerical Calculation On Simple Mass-Spring Case Using C++ Code. 1. ProblemDocument6 paginiWeekly Report: Numerical Calculation On Simple Mass-Spring Case Using C++ Code. 1. ProblemYosua Heru IrawanÎncă nu există evaluări

- CC 113 A The Computer Number SystemsDocument11 paginiCC 113 A The Computer Number SystemsRaymark TimothyÎncă nu există evaluări

- An Introduction To JPEG Compression Using Matlab: Arno Swart 28th October 2003Document5 paginiAn Introduction To JPEG Compression Using Matlab: Arno Swart 28th October 2003infiniti47Încă nu există evaluări

- BBBCB 45 FDocument111 paginiBBBCB 45 FMarkos AnagnostouÎncă nu există evaluări

- Unit - I Boolean Algebra and Logic GatesDocument40 paginiUnit - I Boolean Algebra and Logic GatesAbi MoorthyÎncă nu există evaluări

- Lec 2 Number Systems and ConversionsDocument83 paginiLec 2 Number Systems and Conversionsi222048 Sahil KumarÎncă nu există evaluări

- Number SystemDocument22 paginiNumber SystemButter VittoriÎncă nu există evaluări

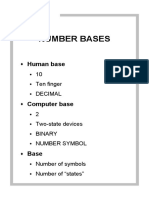

- Number Bases: Human BaseDocument12 paginiNumber Bases: Human BaseJawad CHÎncă nu există evaluări

- 1advanced Encryption StandardNov30Document28 pagini1advanced Encryption StandardNov30JerryGillÎncă nu există evaluări

- 3.number System & ConversionsDocument51 pagini3.number System & ConversionskurdkÎncă nu există evaluări

- Number Systems and CodesDocument59 paginiNumber Systems and CodesSyafnie NinieÎncă nu există evaluări

- Switching Theory and Logic CircuitsDocument159 paginiSwitching Theory and Logic CircuitsnaveenÎncă nu există evaluări

- Chapter 3: Number SystemDocument13 paginiChapter 3: Number SystemDagneWalleÎncă nu există evaluări

- Chapter One HandoutDocument21 paginiChapter One HandoutNatnael TesfayeÎncă nu există evaluări

- 2002 Exam AnswersDocument5 pagini2002 Exam AnswersRanu GamesÎncă nu există evaluări

- ITT270 Task3 RCS1103CDocument5 paginiITT270 Task3 RCS1103CAdib AfhamÎncă nu există evaluări

- Chapter 2 3Document40 paginiChapter 2 322342asÎncă nu există evaluări

- 01 The Number System Part IDocument17 pagini01 The Number System Part IAlain Marvin Alon IlanoÎncă nu există evaluări

- Switching Theory and Logic Circuits 1Document184 paginiSwitching Theory and Logic Circuits 1kujong agacerÎncă nu există evaluări

- 1 1 1 Number RepresentationDocument17 pagini1 1 1 Number Representationrugera wanjaraÎncă nu există evaluări

- Paper 1 Computer Science ASDocument194 paginiPaper 1 Computer Science ASLailaEl-BeheiryÎncă nu există evaluări

- 1.1.1 Number Representation NDocument17 pagini1.1.1 Number Representation NSALEM MAZHINDUÎncă nu există evaluări

- 1.1.1 Number RepresentationDocument17 pagini1.1.1 Number RepresentationHussain SajidÎncă nu există evaluări

- 1.1.1 Number Representation NDocument17 pagini1.1.1 Number Representation NAbhinand TitusÎncă nu există evaluări

- Mechanical Operations (CH31007 and CH21205) Assignment: InstructionsDocument5 paginiMechanical Operations (CH31007 and CH21205) Assignment: InstructionsHarsh GuptaÎncă nu există evaluări

- Basicon 2 Term, SY 2002-2003: Number System Base SymbolsDocument5 paginiBasicon 2 Term, SY 2002-2003: Number System Base SymbolsBidhiidhiÎncă nu există evaluări

- PTS-PAPR Reduction Technique For 5G Advanced Waveforms Using BFO AlgorithmDocument10 paginiPTS-PAPR Reduction Technique For 5G Advanced Waveforms Using BFO AlgorithmVimal RajÎncă nu există evaluări

- Raana Semicondutors PVT LTD: ARM 7-LPC2148 Development BoardDocument107 paginiRaana Semicondutors PVT LTD: ARM 7-LPC2148 Development BoardVimal RajÎncă nu există evaluări

- Introduction To OFDMDocument11 paginiIntroduction To OFDMVimal RajÎncă nu există evaluări

- Power Efficient Cmos Full Adders With Reduced Transistor Count IJERTV3IS031276Document4 paginiPower Efficient Cmos Full Adders With Reduced Transistor Count IJERTV3IS031276Vimal RajÎncă nu există evaluări

- Power Measurement With Cadence EDA: Microelectronics Students Group December 31, 2009Document8 paginiPower Measurement With Cadence EDA: Microelectronics Students Group December 31, 2009Vimal RajÎncă nu există evaluări

- Starting Cadence and Library ManagementDocument7 paginiStarting Cadence and Library ManagementVimal RajÎncă nu există evaluări

- Application Form: User IdDocument7 paginiApplication Form: User IdVimal RajÎncă nu există evaluări

- PressedDocument222 paginiPressedVimal RajÎncă nu există evaluări

- Anna University: Madras Institute of Technology CampusDocument4 paginiAnna University: Madras Institute of Technology CampusVimal RajÎncă nu există evaluări

- Svcet: 1. Addressing ModesDocument14 paginiSvcet: 1. Addressing ModesVimal Raj100% (1)

- Vlsi - Physical DesignDocument27 paginiVlsi - Physical DesignVimal RajÎncă nu există evaluări

- Digital Signal Processing by Ramesh Babu PDFDocument303 paginiDigital Signal Processing by Ramesh Babu PDFVimal RajÎncă nu există evaluări

- A Study On The Different Image Segmentation Technique: ISO 9001:2008 CertifiedDocument6 paginiA Study On The Different Image Segmentation Technique: ISO 9001:2008 CertifiedVimal RajÎncă nu există evaluări

- 833Document5 pagini833Vimal RajÎncă nu există evaluări

- Using Signaltap Ii Embedded Logic Analyzers in Sopc Builder SystemsDocument21 paginiUsing Signaltap Ii Embedded Logic Analyzers in Sopc Builder SystemsVimal RajÎncă nu există evaluări

- Floating Point Numbers: Do You Have Your Laptop Here?Document10 paginiFloating Point Numbers: Do You Have Your Laptop Here?dhandayuthapaniÎncă nu există evaluări

- Rockwell Micro850 Free Tag NamesDocument8 paginiRockwell Micro850 Free Tag NamesTrần Văn ToảnÎncă nu există evaluări

- Arithmetic InstructionsDocument18 paginiArithmetic InstructionsSushil KumarÎncă nu există evaluări

- Two's Complement Adder/Subtractor: Lab L03Document7 paginiTwo's Complement Adder/Subtractor: Lab L03Darrel VeluzÎncă nu există evaluări

- Chapter 4Document45 paginiChapter 4Mohammad Ahmed ChoudhryÎncă nu există evaluări

- COA Question Bank With SolutionDocument145 paginiCOA Question Bank With SolutionSandeep Kumar YadavÎncă nu există evaluări

- Mips Ref PDFDocument1 paginăMips Ref PDFGrant SellersÎncă nu există evaluări

- Decimal To Floating Point: Property of STIDocument3 paginiDecimal To Floating Point: Property of STIjjÎncă nu există evaluări

- Data RepresentationDocument28 paginiData Representationmanishbhardwaj8131Încă nu există evaluări

- Exam2 (Example With Solutions)Document6 paginiExam2 (Example With Solutions)radhakodirekka8732Încă nu există evaluări

- User Man Ita Adv Conf RepeDocument24 paginiUser Man Ita Adv Conf RepeFabio ComunettiÎncă nu există evaluări

- Yr8 BasesDocument33 paginiYr8 Baseshamblack321Încă nu există evaluări

- Computer Organization and Design Final After CorrectionsDocument238 paginiComputer Organization and Design Final After CorrectionsPritha ThangaveluÎncă nu există evaluări

- Cs3351-Digital Principles and Computer Organization-1955364779-Dpsd All UnitDocument270 paginiCs3351-Digital Principles and Computer Organization-1955364779-Dpsd All UnitremaÎncă nu există evaluări

- Digital Fundamentals LAB #5 Binary Adders: ObjectiveDocument3 paginiDigital Fundamentals LAB #5 Binary Adders: ObjectiveAnonymous uPUm1vh4H100% (1)

- Number SystemDocument18 paginiNumber SystemJanarthanan SubramanianÎncă nu există evaluări

- 5 NumberSystemsDocument76 pagini5 NumberSystemsKamran SaifÎncă nu există evaluări

- Ece238 HW 01Document3 paginiEce238 HW 01Dave WorshipÎncă nu există evaluări

- Fall 22-23 COA Lecture-9 Overview of Multiplication and DivisionDocument38 paginiFall 22-23 COA Lecture-9 Overview of Multiplication and DivisionShanjida JimÎncă nu există evaluări

- Onsong BB VL3 MIDI Setup LuisLugoDocument6 paginiOnsong BB VL3 MIDI Setup LuisLugoDavid LynxÎncă nu există evaluări

- Lecture5 INSTRUCTIONS MICROPROCESSOR APLICATIONSDocument58 paginiLecture5 INSTRUCTIONS MICROPROCESSOR APLICATIONSagustin cordobaÎncă nu există evaluări

- Floating Point MAC Implementation Using Residue Number SystemDocument21 paginiFloating Point MAC Implementation Using Residue Number SystemSuresha V SathegalaÎncă nu există evaluări

- OperatorsDocument9 paginiOperatorsnilesh kumarÎncă nu există evaluări

- Indian Institute of Technology, KharagpurDocument2 paginiIndian Institute of Technology, KharagpurKaushal BanthiaÎncă nu există evaluări

- Computer Arithmetic: Unit - IiDocument41 paginiComputer Arithmetic: Unit - IiAakash kumar shahÎncă nu există evaluări

- Decimal Binary Octal Hexadecimal: Calvin Kim Peraman Bet-Ct N2ADocument3 paginiDecimal Binary Octal Hexadecimal: Calvin Kim Peraman Bet-Ct N2AVincent ParcoÎncă nu există evaluări

- CO 18CS34 MOD4 IncompleteDocument11 paginiCO 18CS34 MOD4 IncompleteAashik J KrishnanÎncă nu există evaluări

- DLP TemplateDocument9 paginiDLP TemplateWhite KrampÎncă nu există evaluări

- Java Assignment I: Bitwise Operators Bitwise Shift Operators Garbage Collection Class Buffered ReaderDocument7 paginiJava Assignment I: Bitwise Operators Bitwise Shift Operators Garbage Collection Class Buffered ReaderShehan SerasingheÎncă nu există evaluări

- Laws of IndicesDocument52 paginiLaws of IndicesAnonymous PPYjNttÎncă nu există evaluări