Documente Academic

Documente Profesional

Documente Cultură

Tn0613 Technical Note: ST System-On-Chip (Soc) Debug Interfaces

Încărcat de

cahpmasterTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tn0613 Technical Note: ST System-On-Chip (Soc) Debug Interfaces

Încărcat de

cahpmasterDrepturi de autor:

Formate disponibile

TN0613

Technical note

ST system-on-chip (SoC) debug interfaces

Synopsis

ST has developed an extensive family of debug interfaces that support host-target

connection and facilitate debug functionality.

The purpose of this document is to describe the target board requirements for connecting to

the various interfaces. It is intended to be read by board design engineers.

December 2011 8339250 Rev 3 1/19

www.st.com

Contents ST system-on-chip (SoC) debug interfaces

Contents

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 JTAG interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1 Type A debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2 Type C debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.3 Type H debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4 Type J debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 LVDS interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1 Type F debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2 Type G debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3 Type K debug interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces Overview

1 Overview

Table 1 summarizes the relevant types of debug interface for custom board designs.

Table 1. Debug interfaces

Debug Debug

Features

interface support

– 20-way IDC target connection

Type A – notASEBRK JTAG

– 3V3 JTAG

– 20-way IDC target connection

Type C JTAG

– Automatic I/O voltage sensing

– LVDS connection

Type F JTAG

– notASEBRK

– LVDS connection

Type G – notASEBRK JTAG

– Altera ISP EPLD programming support

– MIPI-34 connection JTAG and

Type H

– Automatic I/O voltage sensing trace signals

– Intelligent software configurable LVDS connector JTAG and

Type I

(defined for use in future ST development boards) trace signals

– 10-way IDC target connection

Type J JTAG

– 3V3 JTAG

JTAG and

Type K – LVDS direct connection

trace signals

Note: 1 If your target board does not support trace, it is still possible to connect to one of the types

that does, for example a Type K, by not wiring in the trace pins.

2 Some connections have optional pins and these are identified in the appropriate pinout

description.

3 In the tables in this document, in the Signal direction column, “From SoC” means a signal

from the SoC on the processor board, and “To SoC” means a signal to the SoC on the

processor board.

8339250 Rev 3 3/19

JTAG interfaces ST system-on-chip (SoC) debug interfaces

2 JTAG interfaces

This chapter describes the various JTAG interfaces in the following sections:

● Section 2.1: Type A debug interface

● Section 2.2: Type C debug interface on page 6

● Section 2.3: Type H debug interface on page 8

● Section 2.4: Type J debug interface on page 11

2.1 Type A debug interface

Type A is a 2 x 10-way IDC connection (Figure 1) providing a standard JTAG debug

interface. The wiring of a Type A debug interface on the processor board is shown in

Figure 2 and Figure 3.

This interface should be used on ST40-based development boards.

Figure 1. JTAG debug 2 x 10-way IDC connector

19 1

20 2

Table 2. Type A pin allocation

Pin Signal name Signal direction Pin Signal name Signal direction

Even

GROUND Not applicable 11 TCK To SoC

pins

1 Reserved Not applicable 13 TDI To SoC

3 TRIGOUT From SoC 15 TDO From SoC

5 TRIGIN To SoC 17 notSYSRESET To SoC

7 notASEBRK Bi-directional 19 notTRST To SoC

9 TMS To SoC

4/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces JTAG interfaces

Figure 2. Type A JTAG interface wiring

Processor board

VREF

SoC

10 K

JTAG interface connector

47R TRIGOUT

TRIGIN

47R notASEBRK1

TMS

TCK

TDI

47R TDO

notSYSRESET

notPOWERONRESET

notTRST

10 K

1. Only connect for SoCs with notASEBRK support.

Figure 3. Type A with TAPMux JTAG interface wiring

Processor board

VREF

SoC

10 K

JTAG interface connector

47R TRIGOUT

TRIGIN

47R notASEBRK1

TMS

TCK

TDI

47R TDO

notSYSRESET

notPOWERONRESET

notTRST

10 K

1. Only connect for SoCs with notASEBRK support.

8339250 Rev 3 5/19

JTAG interfaces ST system-on-chip (SoC) debug interfaces

2.2 Type C debug interface

Type C is a 2 x 10-way IDC connection (Figure 4) providing a standard JTAG debug

interface. The wiring of a Type C debug interface on the processor board is shown in

Figure 5.

This interface should be used on STxP70 and ARM-based (not Cortex-A9) development

boards.

Figure 4. JTAG debug 2 x 10-way IDC connector

19 1

20 2

Table 3. Type C pin allocation

Pin Signal name Signal direction Pin Signal name Signal direction

1 VREF From SoC 2 VSUPPLY From SoC

3 notTRST To SoC 4 GROUND

5 TDI To SoC 6 GROUND

7 TMS To SoC 8 GROUND

9 TCK To SoC 10 GROUND

11 RTCK From SoC 12 GROUND Not applicable

13 TDO From SoC 14 GROUND

15 notSYSRESET Bi-directional 16 GROUND

17 DBGRQ To SoC 18 GROUND

19 DBGACK From SoC 20 GROUND

Note: VREF between 1V8 and 3V3 must be provided from the SoC in order to support

Multi-volt I/O.

6/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces JTAG interfaces

Figure 5. Type C JTAG interface wiring

Processor board

VREF

SoC

10 K

JTAG interface connector

47R DBGACK

DBGRQ

TMS

TCK

TDI

47R TDO

notPOWERONRESET notSYSRESET

notTRST

RTCK1

10 K

1. Only connect for SoCs with RTCK support.

8339250 Rev 3 7/19

JTAG interfaces ST system-on-chip (SoC) debug interfaces

2.3 Type H debug interface

Type H is used to define a MIPI-34 connection (Figure 6) that provides both standard JTAG

signals and trace signals in two voltage domains.

● The voltage of the JTAG signals are defined by VREF_DEBUG.

● The voltage of the trace signals are defined by VREF_TRACE.

The wiring of a Type H debug interface on the processor board is shown in Figure 7.

This interface should be used on ARM Cortex-A9 based development boards.

Further information on the MIPI connectors can be found in the MIPI Alliance

Recommendation for Test & Debug: Debug and Trace Connectors (TDC), version 1.00.00,

MIPI Alliance Inc., 5 June 2007.

Figure 6. MIPI-34 connector

33 1

34 2

Table 4 lists the required pin allocation for the MIPI-34 connector on the target board.

Note: Connection to the trace signals by the target is optional, depending on whether your target

supports trace or not.

Table 4. Type H pin allocation

Pin Signal name Description Signal direction Voltage

JTAG signals

1 VREF_DEBUG Debug port reference voltage.

2 TMS IEEE 1149.1 JTAG signal To SoC VREF_DEBUG

3 GROUND N/A

4 TCK IEEE 1149.1 JTAG signal To SoC VREF_DEBUG

5 GROUND N/A

6 TDO IEEE 1149.1 JTAG signal From SoC VREF_DEBUG

7 KEY Pin removed N/A

8 TDI IEEE 1149.1 JTAG signal To SoC VREF_DEBUG

This pin is GROUND on the target board and

connects to TARGET_PRESENCE_DETECT

9 GROUND From SoC

(+3V3) on the host, using a weak pull-up on

the host interface.

8/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces JTAG interfaces

Table 4. Type H pin allocation (continued)

Pin Signal name Description Signal direction Voltage

Target reset signal. Open drain active low

10 notSYSRESET signal. May be used bi-directional to drive or To SoC VREF_DEBUG

sense the target reset signal.

11 GROUND N/A

Return debug clock (optional). If unused tie to

12 RTCK From SoC VREF_DEBUG

GROUND.

13 GROUND N/A

IEEE 1149.1 JTAG signal with pull-down

14 TRST_PD From SoC VREF_DEBUG

resistor on target

15 GROUND N/A

16 notTRST IEEE 1149.1 JTAG signal To SoC VREF_DEBUG

17 GROUND N/A

18 TRIGIN Target debug halt request To SoC VREF_DEBUG

19 GROUND N/A

20 TRIGOUT Target debug halt acknowledge From SoC VREF_DEBUG

Trace signals

21 GROUND N/A

Trace clock pin. If unused should be

22 TRC_CLK connected to GROUND or driven to a low From SoC VREF_TRACE

logic level.

23 GROUND N/A

24 TRC_DATA0 Trace data pin. If unused tie to GROUND. From SoC VREF_TRACE

25 GROUND N/A

26 TRC_DATA1 Trace data pin. If unused tie to GROUND. From SoC VREF_TRACE

27 GROUND N/A

28 TRC_DATA2 Trace data pin. If unused tie to GROUND. From SoC VREF_TRACE

29 GROUND N/A

30 TRC_DATA3 Trace data pin. If unused tie to GROUND. From SoC VREF_TRACE

31 GROUND N/A

User selectable,

Asynchronous serialized control stream to

32 TRC_EXT To SoC defaults to

configure the trace port on the target.

VREF_DEBUG

33 GROUND N/A

34 VREF_TRACE Trace port reference voltage.

8339250 Rev 3 9/19

JTAG interfaces ST system-on-chip (SoC) debug interfaces

Figure 7. Type H JTAG interface wiring

Processor board

VREF

SoC

10 K

JTAG interface connector

47R TRIGOUT

TRIGIN

TMS

TCK

TDI

47R TDO

notPOWERONRESET notSYSRESET

notTRST

RTCK1

1. Only connect for SoCs with RTCK support, otherwise pulldown.

10/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces JTAG interfaces

2.4 Type J debug interface

Type J is a 2 x 5-way IDC connection (Figure 8) providing a JTAG debug interface. It is used,

for example, on the STi7111-SAT platform for the target debug connection.

The wiring of a Type J debug interface on the processor board is shown in Figure 9.

This interface should be used on ST40-based development boards with a reduced pinout.

Figure 8. JTAG debug 2 x 5-way IDC connector

9 1

10 2

Table 5. Type J pin allocation

Pin Signal name Signal direction Pin Signal name Signal direction

1 TCK To SoC 2 notASEBRK Bi-directional

3 TMS To SoC 4 GROUND

5 TDO From SoC 6 GROUND N/A

7 TDI To SoC 8 GROUND

9 notTRST To SoC 10 notSYSRESET To SoC

Figure 9. Type J JTAG interface wiring

Processor board

VREF

SoC

10 K

JTAG interface connector

47R notASEBRK1

TMS

TCK

TDI

47R TDO

notSYSRESET

notPOWERONRESET

notTRST

10 K

8339250 Rev 3 11/19

LVDS interfaces ST system-on-chip (SoC) debug interfaces

3 LVDS interfaces

This chapter describes the various LVDS interfaces in the following sections:

● Section 3.1: Type F debug interface

● Section 3.2: Type G debug interface

● Section 3.3: Type K debug interface on page 16

An example of an LVDS connector is shown in Figure 10.

Figure 10. LVDS host-target connector

34 1

68 35

Note: All LVDS signals should be buffered using a suitable LVDS buffer.

The pin definitions for the LVDS connectors include four CODE pins. These are read by the

ST Micro Connect to identify the type of connection used. For a Type F connection the code

pins are set as 0101, for a Type G connection the code pins are set as 0110 and for a Type

K connection the code pins are set as 1000.

The wiring of Type F and Type G debug interfaces on the processor board is shown in

Figure 11.

12/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces LVDS interfaces

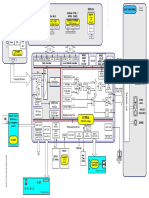

Figure 11. Target board Type F and Type G circuitry

STMC2 Type F circuitry +3V3

notBoardReset

R319

TARGET

10K

IC53

CN32

CODE = 0101 = Type 'F'

MAX9122 PROCESSOR

For 1.6mm PCB 2

CODE = 0110 = Type 'G' LVDS_notTRST+ R364

STMC_LVDSCON 15

notTRST

R360 LVDS_notTRST- 1 0R

68 0R

68 34 34 R361 DNF

R362 DNF LVDS_notRESET+ 3

67 R365

67 33 33 R363 0R 14

LVDS_notRESET- 4 0R

66

66 32 32

LVDS_TDI+ 6

65 R366

11

65 31 31 TDI

LVDS_TDI- 5 0R

64

64 30 30

LVDS_CLKIN+ 7

63 R367

10

63 29 29 TCK

LVDS_CLKIN- 8 0R

62 +3V3_LVDS

62 28 28

LVDS_notTRST- 16

R318

R320

R369

61

10K

10K

10K

61 27 27 LVDS_notTRST+ 9 LVDSBUF_notEN

60 VCC=+3V3_LVDS

60 26 26

59 LVDS_notRESET-

59 25 25 LVDS_notRESET+

58 LVDS_MODE_SEL-

58 24 24 LVDS_MODE_SEL+

IC54

57 LVDS_TDI- MAX9123

57 23 23 LVDS_TDI+

LVDS_USEROUT+ 15

56 2

56 22 22 notASEBRK

LVDS_CLKIN- LVDS_USEROUT- 16

55

55 21 21 LVDS_CLKIN+

LVDS_TRIGOUT+ 14

54 3 R322 47R

54 20 20

+3V3

TrigOut

LVDS_CLKOUT- LVDS_TRIGOUT- 13

53

53 19 19 LVDS_CLKOUT+

LVDS_TDO+ 11

52 +5V_LVDS 6 R321 47R

52 18 18 TDO

R368

10K

LVDS_TDO- 12

51

51 17 17 TP253

R370

10K

LVDS_CLKOUT+ 10

50 7

50 16 16 LVDSBUF_notEN

LVDS_CLKOUT- 9

49 +3V3_LVDS

49 15 15

LVDS_EPLD_SPARE3- 1

48 8

48 14 14 LVDS_EPLD_SPARE3+ LVDSBUF_notEN

47 LVDS_TDO-

VCC=+3V3_LVDS +3V3 +3V3

47 13 13 LVDS_TDO+

46 LVDS_EPLD_SPARE2-

46 12 12 LVDS_EPLD_SPARE2+

LVDS_TRIGOUT-

R373

R371

45

10K

10K

45 11 11 LVDS_TRIGOUT+

IC55

44 LVDS_EPLD_SPARE1- MAX9122

44 10 10 LVDS_EPLD_SPARE1+

LVDS_USEROUT- LVDS_TMS+ 2

43 R372

15

43 9 9 LVDS_USEROUT+ TMS

LVDS_EPLD_TDO- LVDS_TMS- 1 0R IC50-1

42 74LCX07

42 8 8 LVDS_EPLD_TDO+

R323

10K

LVDS_TMS- LVDS_USERIN+ 3

41 14 1 2

41 7 7 LVDS_TMS+

LVDS_EPLD_TCK- LVDS_USERIN- 4

40 VCC=+3V3

40 6 6 LVDS_EPLD_TCK+

LVDS_USERIN- LVDS_TRIGIN+ 6

39 11

39 5 5 LVDS_USERIN+ TrigIn

LVDS_EPLD_TMS- LVDS_TRIGIN- 5

38

38 4 4 LVDS_EPLD_TMS+

LVDS_TRIGIN- LVDS_SPAREIN+ 7 240R

37 10

37 3 3 LVDS_TRIGIN+

R374

10K

LVDS_EPLD_TDI- LVDS_SPAREIN- 8 R382

36 +3V3_LVDS 1

36 2 2 LVDS_EPLD_TDI+ GREEN

LVDS_SPAREIN- 16

35 9 LD9-B

35 1 1 LVDS_SPAREIN+ LVDSBUF_notEN

2

VCC=+3V3_LVDS

SHIELD=CHASSIS

Pins 1-34 = SCSI-5 +VE signals

Pins 35-68 = SCSI-5 -VE signals

STMC2 Type G extra circuitry

NOTE: If remote power on feature used, buffers should be powered from STMC2 +5V_LVDS.

+5V_LVDS IC52

R375

LP3964-3.3 +3V3_LVDS

1K

L42 2 Vin Vout 3

3V3

R317

FBEAD_SMT

10K

800mA notRemotePowerOn

600mA

C482 C481 1 notSD ADJ 4 C484 C491 C483 C488 C487 C489 C485 TR5

GND

20V 50V 20V 50V 50V 50V 50V 50V 50V MMBT2222A e.g. Connect to ATX P_ON signal.

47u 1U 47u 100n 100n 100n 100n 100n 100n

5

IC57

MAX9122

LVDS_MODE_SEL+ 2

R379

15

TargetDebugModeSel

LVDS_MODE_SEL- 1 0R e.g. Connect to processor mode pin to force boot from JTAG.

LVDS_EPLD_TCK+ 3

R380

14

AuxTck

LVDS_EPLD_TCK- 4 0R

LVDS_EPLD_TMS+ 6

R383

11

AuxTms

LVDS_EPLD_TMS- 5 0R

LVDS_EPLD_TDI+ 7

R384

10

AuxTdi

LVDS_EPLD_TDI- 8 0R

+3V3

16 +3V3

9

R359

3 10K

VCC=+3V3_LVDS 2 TARGET EPLD

J26-A 1 LVDSBUF_notEN

IC56

MAX9123

LVDS_EPLD_TDO+ 15

2

AuxTdo

LVDS_EPLD_TDO- 16

LVDS_EPLD_SPARE1+ 14

3

UserFeedback1

LVDS_EPLD_SPARE1- 13

LVDS_EPLD_SPARE2+ 11

6

UserFeedback2

LVDS_EPLD_SPARE2- 12

LVDS_EPLD_SPARE3+ 10

7

notPowerOnReset

LVDS_EPLD_SPARE3- 9

+3V3_LVDS

1

8 LVDSBUF_notEN

VCC=+3V3_LVDS

8339250 Rev 3 13/19

LVDS interfaces ST system-on-chip (SoC) debug interfaces

3.1 Type F debug interface

Type F is used to define a 68-pin LVDS connection (see Figure 10) that provides a JTAG

debug interface. It does not provide an EPLD programming interface.

Note: This interface is not recommended for new designs, Type G should be used instead.

Table 6 lists the target pin allocation.

Table 6. Type F pin allocation

Signal Signal

Pin Signal name Pin Signal name

direction direction

1 LVDS_SPAREIN+ To SoC 35 LVDS_SPAREIN- To SoC

2 NC N/A 36 NC N/A

3 LVDS_TRIGIN+ To SoC 37 LVDS_TRIGIN- To SoC

4 NC N/A 38 NC N/A

5 LVDS_notASEBRKOUT_notSRST+ From SoC 39 LVDS_notASEBRKOUT_notSRST- From SoC

6 NC N/A 40 NC N/A

7 LVDS_TMS+ To SoC 41 LVDS_TMS- To SoC

8 NC N/A 42 NC N/A

9 LVDS_USEROUT+ From SoC 43 LVDS_USEROUT- From SoC

10 NC N/A 44 NC N/A

11 LVDS_TRIGOUT+ From SoC 45 LVDS_TRIGOUT- From SoC

12 NC N/A 46 NC N/A

13 LVDS_TDO+ From SoC 47 LVDS_TDO- From SoC

14 NC N/A 48 NC N/A

15 GROUND N/A 49

GROUND N/A

16 LVDSBUF_notEN To SoC 50

17 51

+5V_LVDS N/A +5V_LVDS N/A

18 52

19 LVDS_CLKOUT+ From SoC 53 LVDS_CLKOUT- From SoC

20 GROUND N/A 54 GROUND N/A

21 LVDS_CLKIN+ To SoC 55 LVDS_CLKIN- To SoC

22 GROUND N/A 56 GROUND N/A

23 LVDS_TDI+ To SoC 57 LVDS_TDI- To SoC

24 NC N/A 58 NC N/A

25 LVDS_notSYSRESET+ To SoC 59 LVDS_notSYSRESET- To SoC

26 NC N/A 60 NC N/A

27 LVDS_notTRST+ To SoC 61 LVDS_notTRST- To SoC

28 NC N/A 62 NC N/A

14/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces LVDS interfaces

Table 6. Type F pin allocation (continued)

Signal Signal

Pin Signal name Pin Signal name

direction direction

29 63

30 64

NC N/A NC N/A

31 65

32 66

33 CODE3 (GROUND) From SoC 67 CODE2 (Do not connect) From SoC

34 CODE1 (GROUND) From SoC 68 CODE0 (Do not connect) From SoC

3.2 Type G debug interface

Type G is used to define a 68-pin LVDS connection (see Figure 10) that provides a JTAG

debug interface and an EPLD programming interface. It is used, for example, on the

HD-GEN-MB peripheral board for the target debug connection.

Table 7 lists the target pin allocation.

Table 7. Type G pin allocation

Signal Signal

Pin Signal name Pin Signal name

direction direction

1 LVDS_SPAREIN+ To SoC 35 LVDS_SPAREIN- To SoC

2 LVDS_EPLD_TDI+ To SoC 36 LVDS_EPLD_TDI- To SoC

3 LVDS_TRIGIN+ To SoC 37 LVDS_TRIGIN- To SoC

4 LVDS_EPLD_TMS+ To SoC 38 LVDS_EPLD_TMS- To SoC

5 LVDS_notASEBRKOUT_notSRST+ From SoC 39 LVDS_notASEBRKOUT_notSRST- From SoC

6 LVDS_EPLD_TCK+ To SoC 40 LVDS_EPLD_TCK- To SoC

7 LVDS_TMS+ To SoC 41 LVDS_TMS- To SoC

8 LVDS_EPLD_TDO+ From SoC 42 LVDS_EPLD_TDO- From SoC

9 LVDS_USEROUT+ From SoC 43 LVDS_USEROUT- From SoC

10 BOOT_FROM_ROM_FEEDBACK1+ From SoC 44 BOOT_FROM_ROM_FEEDBACK1- From SoC

11 LVDS_TRIGOUT+ From SoC 45 LVDS_TRIGOUT- From SoC

12 BOOT_FROM_ROM_FEEDBACK2+ From SoC 46 BOOT_FROM_ROM_FEEDBACK2- From SoC

13 LVDS_TDO+ From SoC 47 LVDS_TDO- From SoC

14 LVDS_notSYSRESET_RTN+ From SoC 48 LVDS_notSYSRESET_RTN- From SoC

15 GROUND N/A 49

GROUND N/A

16 LVDSBUF_notEN To SoC 50

17 51

+5V_LVDS N/A +5V_LVDS N/A

18 52

19 LVDS_CLKOUT+ From SoC 53 LVDS_CLKOUT- From SoC

8339250 Rev 3 15/19

LVDS interfaces ST system-on-chip (SoC) debug interfaces

Table 7. Type G pin allocation (continued)

Signal Signal

Pin Signal name Pin Signal name

direction direction

20 GROUND N/A 54 GROUND N/A

21 LVDS_CLKIN+ To SoC 55 LVDS_CLKIN- To SoC

22 GROUND N/A 56 GROUND N/A

23 LVDS_TDI+ To SoC 57 LVDS_TDI- To SoC

24 LVDS_MODE_SEL+ To SoC 58 LVDS_MODE_SEL- To SoC

25 LVDS_notSYSRESET+ To SoC 59 LVDS_notSYSRESET- To SoC

26 NC N/A 60 NC N/A

27 LVDS_notTRST+ To SoC 61 LVDS_notTRST- To SoC

28 62

29 63

30 NC N/A 64 NC N/A

31 65

32 66

33 CODE3 (GROUND) From SoC 67 CODE2 (Do not connect) From SoC

34 CODE1 (Do not connect) From SoC 68 CODE0 (GROUND) From SoC

3.3 Type K debug interface

Type K is used to define a 68-pin LVDS connection (see Figure 10 on page 12) that provides

a debug and trace signal interface. It is used, for example, on the STiH415-HVK board for

target debug and trace connection.

Table 8 lists the target pin allocation.

Table 8. Type K pin allocation

Signal Signal

Pin Signal name Pin Signal name

direction direction

JTAG signals

1 LVDS_PWRON+ To SoC 35 LVDS_PWRON- To SoC

2 LVDS_EPLD_TDI+ To SoC 36 LVDS_EPLD_TDI- To SoC

3 LVDS_TRIGIN+ To SoC 37 LVDS_TRIGIN- To SoC

4 LVDS_EPLD_TMS+ To SoC 38 LVDS_EPLD_TMS- To SoC

5 LVDS_notASEBRKOUT_notSRST+ From SoC 39 LVDS_notASEBRKOUT_notSRST- From SoC

6 LVDS_EPLD_TCK+ To SoC 40 LVDS_EPLD_TCK- To SoC

7 LVDS_TMS+ To SoC 41 LVDS_TMS- To SoC

8 LVDS_EPLD_TDO+ From SoC 42 LVDS_EPLD_TDO- From SoC

9 NC N/A 43 NC N/A

16/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces LVDS interfaces

Table 8. Type K pin allocation (continued)

Signal Signal

Pin Signal name Pin Signal name

direction direction

10 BOOT_FROM_ROM_FEEDBACK1+ From SoC 44 BOOT_FROM_ROM_FEEDBACK1- From SoC

11 LVDS_TRIGOUT+ From SoC 45 LVDS_TRIGOUT- From SoC

12 BOOT_FROM_ROM_FEEDBACK2+ From SoC 46 BOOT_FROM_ROM_FEEDBACK2- From SoC

13 LVDS_TDO+ From SoC 47 LVDS_TDO- From SoC

14 LVDS_notSYSRESET_RTN+ From SoC 48 LVDS_notSYSRESET_RTN- From SoC

15 GROUND N/A 49

GROUND N/A

16 LVDS_BUF_notEN To SoC 50

17 51

+5V_LVDS N/A +5V_LVDS N/A

18 52

19 LVDS_CLKOUT+ From SoC 53 LVDS_CLKOUT- From SoC

20 GROUND N/A 54 GROUND N/A

Trace signals

21 LVDS_CLKIN+ To SoC 55 LVDS_CLKIN- To SoC

22 GROUND N/A 56 GROUND N/A

23 LVDS_TDI+ To SoC 57 LVDS_TDI- To SoC

24 NC N/A 58 NC N/A

25 LVDS_notSYSRESET+ To SoC 59 LVDS_notSYSRESET- To SoC

26 LVDS_STMRTN+ To SoC 60 LVDS_STMRTN- To SoC

27 LVDS_notTRST+ To SoC 61 LVDS_notTRST- To SoC

28 LVDS_STMDATA0+ From SoC 62 LVDS_STMDATA0- From SoC

29 LVDS_STMDATA1+ From SoC 63 LVDS_STMDATA1- From SoC

30 LVDS_STMDATA2+ From SoC 64 LVDS_STMDATA2- From SoC

31 LVDS_STMDATA3+ From SoC 65 LVDS_STMDATA3- From SoC

32 LVDS_STMCLK+ From SoC 66 LVDS_STMCLK- From SoC

33 CODE3 (Do not connect) From SoC 67 CODE2 (GROUND) From SoC

34 CODE1 (GROUND) From SoC 68 CODE0 (GROUND) From SoC

8339250 Rev 3 17/19

Revision history ST system-on-chip (SoC) debug interfaces

4 Revision history

Table 9. Document revision history

Date Revision Changes

04-Aug-2011 1 Initial release.

Updated Table 1: Debug interfaces on page 3 to include Type F.

Added Figure 3: Type A with TAPMux JTAG interface wiring on

page 5.

Updated Chapter 3: LVDS interfaces on page 12 to include Type F.

17-Nov-2011 2 Added Figure 11 on page 13 and Section 3.1: Type F debug

interface on page 14.

Corrected Type K code pins value in Chapter 3: LVDS interfaces on

page 12.

Corrected Code pin settings in Table 7: Type G pin allocation on

page 15.

Changed name of document to ST system-on-chip (SoC) debug

06-Dec-2011 3

interfaces.

18/19 8339250 Rev 3

ST system-on-chip (SoC) debug interfaces

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

8339250 Rev 3 19/19

S-ar putea să vă placă și

- Exploring Arduino: Tools and Techniques for Engineering WizardryDe la EverandExploring Arduino: Tools and Techniques for Engineering WizardryEvaluare: 4.5 din 5 stele4.5/5 (5)

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDe la EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemÎncă nu există evaluări

- Bascom Avr Demonstration BoardDocument8 paginiBascom Avr Demonstration BoardNitish KumarÎncă nu există evaluări

- Encoder Board MACH3Document12 paginiEncoder Board MACH3Minerva MartinezÎncă nu există evaluări

- Si3226/7 Si3208/9: D P Slic DC-DC CDocument38 paginiSi3226/7 Si3208/9: D P Slic DC-DC CDarwin SipayungÎncă nu există evaluări

- CDocument35 paginiCJagopati Jr.Încă nu există evaluări

- 1220e Datasheet enDocument6 pagini1220e Datasheet enAlexandra GarciaÎncă nu există evaluări

- Data Sheet: Model: Cosmos IiDocument31 paginiData Sheet: Model: Cosmos IichackÎncă nu există evaluări

- BX 2 EN Manual 101112Document50 paginiBX 2 EN Manual 101112Ibrahim ALhaj Gharib100% (2)

- The NEXTSAPIENS Development Board: User ManualDocument33 paginiThe NEXTSAPIENS Development Board: User ManualHarshit MahajanÎncă nu există evaluări

- 1.8inch Module SpecificationDocument3 pagini1.8inch Module SpecificationEdsonÎncă nu există evaluări

- IWC Manual Issue 2Document18 paginiIWC Manual Issue 2woody8112Încă nu există evaluări

- TCS34725 Color Sensor User ManualDocument16 paginiTCS34725 Color Sensor User Manualarijit_ghosh_18Încă nu există evaluări

- Encoder Interface: Sound LogicDocument12 paginiEncoder Interface: Sound Logicالكترونيات يافاÎncă nu există evaluări

- ProgrammingGuideforMatrixGlitcherXilinxCPLDCoolRunner-IIXC2C64AModule1 0Document4 paginiProgrammingGuideforMatrixGlitcherXilinxCPLDCoolRunner-IIXC2C64AModule1 0jj_baluÎncă nu există evaluări

- DJF Iot Reversing Field ManualDocument1 paginăDJF Iot Reversing Field ManualMark TarterÎncă nu există evaluări

- Section 2 - Port Control On SAMD20: TasksDocument18 paginiSection 2 - Port Control On SAMD20: TasksjmsaakÎncă nu există evaluări

- 5 Pin Interface, Version 2.9, 01.02.2010Document10 pagini5 Pin Interface, Version 2.9, 01.02.2010msalem73Încă nu există evaluări

- Electronics Individual DocumentDocument13 paginiElectronics Individual DocumentkennethÎncă nu există evaluări

- Jtag-Hs3 ™ Programming Cable For Xilinx Fpgas: Revised March 13, 2019 This Manual Applies To The JTAG-HS3 Rev. ADocument6 paginiJtag-Hs3 ™ Programming Cable For Xilinx Fpgas: Revised March 13, 2019 This Manual Applies To The JTAG-HS3 Rev. AWilman LealÎncă nu există evaluări

- Microcontroller and Systems Part-5: Anil JBDocument24 paginiMicrocontroller and Systems Part-5: Anil JBUsha RaniÎncă nu există evaluări

- Ecee AVR Mega32 - Users ManualDocument40 paginiEcee AVR Mega32 - Users Manualgoaltech100% (1)

- KV Dsflab Mini Projects 2020 PDFDocument5 paginiKV Dsflab Mini Projects 2020 PDFkundu.banhimitraÎncă nu există evaluări

- Id-Pcm8e - 1.0a Pc3000e+Document28 paginiId-Pcm8e - 1.0a Pc3000e+tavares ximenesÎncă nu există evaluări

- Iot Unit 2 & 3Document22 paginiIot Unit 2 & 3lakshmiÎncă nu există evaluări

- TCC8200 v0.2 20060425Document505 paginiTCC8200 v0.2 20060425Joe LuiÎncă nu există evaluări

- 7.chapter 3Document11 pagini7.chapter 3thethtet87Încă nu există evaluări

- Sel 751Document4 paginiSel 751Suraj GuptaÎncă nu există evaluări

- Embedded Market Io Board DatasheetDocument8 paginiEmbedded Market Io Board DatasheetAnil SuhaÎncă nu există evaluări

- DT-AVR Low Cost Nano System - EngDocument2 paginiDT-AVR Low Cost Nano System - EngajibÎncă nu există evaluări

- Micromis Base V1 - Quick Start GuideDocument17 paginiMicromis Base V1 - Quick Start GuideDominik NuszkiewiczÎncă nu există evaluări

- Infineon-XMC Link Board Users Manual - pdf-UserManual-v01 00-ENDocument12 paginiInfineon-XMC Link Board Users Manual - pdf-UserManual-v01 00-ENNik NameÎncă nu există evaluări

- General Specifications CO-920-01: GS48D20Z01-00E-NDocument4 paginiGeneral Specifications CO-920-01: GS48D20Z01-00E-N赵先生Încă nu există evaluări

- LCD Debug Card Manual MULTIDocument28 paginiLCD Debug Card Manual MULTInishatiwari820% (1)

- Inter Integrated Circuit TrainingDocument26 paginiInter Integrated Circuit Trainingsai saiÎncă nu există evaluări

- App Arm JtagDocument34 paginiApp Arm JtagbalzoniaÎncă nu există evaluări

- I2c PaperDocument14 paginiI2c PaperParvinder SinghÎncă nu există evaluări

- AN93Document307 paginiAN93AhmedÎncă nu există evaluări

- Communication Interface: SD20 Series Digital IndicatorDocument28 paginiCommunication Interface: SD20 Series Digital IndicatorChristianÎncă nu există evaluări

- Co2 Laser Card ManualDocument11 paginiCo2 Laser Card ManualJuan Carlos CosmeÎncă nu există evaluări

- Ad5308 5318 5328 PDFDocument28 paginiAd5308 5318 5328 PDFAndres Fernandez FernandezÎncă nu există evaluări

- VGADocument7 paginiVGACarlosVillavicencioGÎncă nu există evaluări

- Ad 622 DiscriptionDocument20 paginiAd 622 DiscriptionZenache AhlemÎncă nu există evaluări

- CP2102 EkDocument8 paginiCP2102 EkDavid LandaÎncă nu există evaluări

- Combo Debug CardDocument48 paginiCombo Debug Cardlemp9002Încă nu există evaluări

- PmodCMPS Manual HMC5883Document2 paginiPmodCMPS Manual HMC5883soros4Încă nu există evaluări

- Hardware and Software Implementation of Android-Controlled Robotic VehicleDocument21 paginiHardware and Software Implementation of Android-Controlled Robotic VehicleSai Som MeinÎncă nu există evaluări

- Microcontroller Compete Course PDFDocument106 paginiMicrocontroller Compete Course PDFRidaÎncă nu există evaluări

- Fujitsu Lifebook lh531 Inventec Strike ms14 Rev x01 SCHDocument56 paginiFujitsu Lifebook lh531 Inventec Strike ms14 Rev x01 SCHvisa uk 1Încă nu există evaluări

- LM32019DFW C TopwayDocument15 paginiLM32019DFW C TopwayJudá RibeiroÎncă nu există evaluări

- The Arduino: This Presentation Made by Thingerbit's PDFDocument23 paginiThe Arduino: This Presentation Made by Thingerbit's PDFscience for lifeÎncă nu există evaluări

- S32K148 EVB: Quick Start GuideDocument55 paginiS32K148 EVB: Quick Start GuideHtet lin AgÎncă nu există evaluări

- LCD I2C/Serial : User's GuideDocument16 paginiLCD I2C/Serial : User's GuideorenlustÎncă nu există evaluări

- Using TerminalsDocument19 paginiUsing TerminalscointoinÎncă nu există evaluări

- Using DE0-Nano ADC-1Document17 paginiUsing DE0-Nano ADC-1Sylwester MÎncă nu există evaluări

- Bluetooth Low Energy 4.2 Soc General Description: FinalDocument234 paginiBluetooth Low Energy 4.2 Soc General Description: FinalspotÎncă nu există evaluări

- DE2-70 Media Computer PDFDocument46 paginiDE2-70 Media Computer PDFOmidÎncă nu există evaluări

- Connecting To A Target Board With The Avr Jtagice Mkii: MicrocontrollersDocument5 paginiConnecting To A Target Board With The Avr Jtagice Mkii: MicrocontrollersAli BarakatÎncă nu există evaluări

- ST8675 5in1 Mini PCIe Laptop Debug Test Card User GuideDocument4 paginiST8675 5in1 Mini PCIe Laptop Debug Test Card User Guideanacer55Încă nu există evaluări

- Analog Display Digital VFODocument3 paginiAnalog Display Digital VFOtestÎncă nu există evaluări

- Low-Cost HDTV Satellite Set-Top Box Decoder For Microsoft VC-1, H.264 and MPEG-2Document4 paginiLow-Cost HDTV Satellite Set-Top Box Decoder For Microsoft VC-1, H.264 and MPEG-2shhmmmÎncă nu există evaluări

- UM1250 User Manual: ST40 Micro Toolset GDB Command ScriptsDocument87 paginiUM1250 User Manual: ST40 Micro Toolset GDB Command ScriptscahpmasterÎncă nu există evaluări

- cd17379953 st40 Micro Toolset StmicroelectronicsDocument311 paginicd17379953 st40 Micro Toolset StmicroelectronicscahpmasterÎncă nu există evaluări

- St40 Stlinux: Distribution and Development Environment For St40 PlatformsDocument16 paginiSt40 Stlinux: Distribution and Development Environment For St40 PlatformscahpmasterÎncă nu există evaluări

- Stapi SDK: User ManualDocument192 paginiStapi SDK: User ManualcahpmasterÎncă nu există evaluări

- UM1369 User Manual: OS21 For ST40Document23 paginiUM1369 User Manual: OS21 For ST40cahpmasterÎncă nu există evaluări

- En CD17182230Document544 paginiEn CD17182230cahpmasterÎncă nu există evaluări

- Scat April PDFDocument84 paginiScat April PDFcahpmasterÎncă nu există evaluări

- VB Ganesh 19122019Document4 paginiVB Ganesh 19122019cahpmasterÎncă nu există evaluări

- tbs6910 User Guide PDFDocument24 paginitbs6910 User Guide PDFcahpmasterÎncă nu există evaluări

- TBS5520SE User Guide: 1. Connect The TV Signal Cable To The Corresponding Device PortDocument23 paginiTBS5520SE User Guide: 1. Connect The TV Signal Cable To The Corresponding Device PortcahpmasterÎncă nu există evaluări

- TBS5520SE User Guide: 1. Connect The TV Signal Cable To The Corresponding Device PortDocument23 paginiTBS5520SE User Guide: 1. Connect The TV Signal Cable To The Corresponding Device PortcahpmasterÎncă nu există evaluări

- Tbs5580 User GuideDocument20 paginiTbs5580 User GuidecahpmasterÎncă nu există evaluări

- A/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardDocument1 paginăA/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardcahpmasterÎncă nu există evaluări

- BEDocument55 paginiBEcahpmasterÎncă nu există evaluări

- An 11483Document31 paginiAn 11483cahpmasterÎncă nu există evaluări

- Duckworth Lewis Stern Methodology 2017Document8 paginiDuckworth Lewis Stern Methodology 2017cahpmasterÎncă nu există evaluări

- SeentcsyllabusDocument20 paginiSeentcsyllabuscahpmasterÎncă nu există evaluări

- Ieee International Workshop On Factory Communication SystemsDocument9 paginiIeee International Workshop On Factory Communication SystemscahpmasterÎncă nu există evaluări

- SeentcsyllabusDocument20 paginiSeentcsyllabuscahpmasterÎncă nu există evaluări

- BASIC VLSI DESIGN .PptsDocument32 paginiBASIC VLSI DESIGN .PptsNarayana Rao RevallaÎncă nu există evaluări

- Digital Electronics & Computer Fundamentals Theory.Document137 paginiDigital Electronics & Computer Fundamentals Theory.Raju Ali Kawsar50% (2)

- Antipona, Clarence A. - Chapter 5-7, 5-8 SummaryDocument3 paginiAntipona, Clarence A. - Chapter 5-7, 5-8 Summaryclarence antiponaÎncă nu există evaluări

- Experiment 11 Asynchronous CountersDocument10 paginiExperiment 11 Asynchronous CountersMd. Arif Hasan MasumÎncă nu există evaluări

- Challenges in Embedded Memory Design and TestDocument19 paginiChallenges in Embedded Memory Design and TestCHARANÎncă nu există evaluări

- Coa Neptel AnswersDocument69 paginiCoa Neptel AnswersManav KhambhayataÎncă nu există evaluări

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersDocument20 paginiGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuÎncă nu există evaluări

- COP87L84BC 8-Bit CMOS OTP Microcontrollers With 16k Memory, Comparators, and CAN InterfaceDocument54 paginiCOP87L84BC 8-Bit CMOS OTP Microcontrollers With 16k Memory, Comparators, and CAN InterfaceWarr SteelÎncă nu există evaluări

- Cmose mcq-1Document30 paginiCmose mcq-1Prajwal BirwadkarÎncă nu există evaluări

- Area Delay Power Efficient Carry Select AdderDocument5 paginiArea Delay Power Efficient Carry Select AdderAzeem TopÎncă nu există evaluări

- CH.5. Data Converters & PLDsDocument59 paginiCH.5. Data Converters & PLDshidag66550Încă nu există evaluări

- M68 HC 05Document332 paginiM68 HC 05rullitoÎncă nu există evaluări

- Special Function Registers (SFR'S)Document14 paginiSpecial Function Registers (SFR'S)kishaÎncă nu există evaluări

- Resume OldDocument2 paginiResume OldsureshchattuÎncă nu există evaluări

- ARM STM32F107 Development Board ManualDocument66 paginiARM STM32F107 Development Board ManualTiago AveiroÎncă nu există evaluări

- DSY1501 Assignment 1 - S2 - 2023Document3 paginiDSY1501 Assignment 1 - S2 - 2023Tshepiso Qobolo0% (1)

- Lecture 1: Introduction To ARM Based Embedded SystemsDocument24 paginiLecture 1: Introduction To ARM Based Embedded SystemsSaurabh HedaÎncă nu există evaluări

- Fundamentals of Logic Design Enhanced Edition JR Charles H Roth Full ChapterDocument51 paginiFundamentals of Logic Design Enhanced Edition JR Charles H Roth Full Chaptershannon.bush789100% (9)

- RiSC PipelineDocument9 paginiRiSC Pipelinekb_lu232Încă nu există evaluări

- Digital TechniqueDocument33 paginiDigital Techniquekhalique demonÎncă nu există evaluări

- W25X10, W25X20, W25X40, W25X80Document48 paginiW25X10, W25X20, W25X40, W25X80Brahim TelliÎncă nu există evaluări

- QMTECH XC7A35T DDR3 DaughterBoard V02Document1 paginăQMTECH XC7A35T DDR3 DaughterBoard V02Andrew NikonovÎncă nu există evaluări

- 07 Flip Flop and ApplicationDocument20 pagini07 Flip Flop and ApplicationChen ShyanÎncă nu există evaluări

- Application Note 18: The ARM6 Family Bus InterfaceDocument22 paginiApplication Note 18: The ARM6 Family Bus InterfaceVINAY YADAVÎncă nu există evaluări

- PHYSICS (Logic Gates) by Ashwin SajiDocument16 paginiPHYSICS (Logic Gates) by Ashwin SajiAshwin SajiÎncă nu există evaluări

- Computer System Architecture: (Third Edition)Document40 paginiComputer System Architecture: (Third Edition)Saravanan KumarÎncă nu există evaluări

- A Modeling of A Dynamically Reconfigurable Processor Using SystemCDocument6 paginiA Modeling of A Dynamically Reconfigurable Processor Using SystemCRyan CookÎncă nu există evaluări

- Fritzing EGR270Document8 paginiFritzing EGR270Andres Guevara100% (1)

- VLSI Design Lab Project ReportDocument18 paginiVLSI Design Lab Project ReportSimbu YarhaÎncă nu există evaluări

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document5 paginiPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraÎncă nu există evaluări