Documente Academic

Documente Profesional

Documente Cultură

1990-Photocopieuse Corrigé PDF

Încărcat de

ChabehouTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

1990-Photocopieuse Corrigé PDF

Încărcat de

ChabehouDrepturi de autor:

Formate disponibile

BAC STI GENIE ELECTRONIQUE - EPREUVE D’ETUDE D’UN SYSTEME TECHNIQUE 1/2

ETUDE D’UN SYSTEME TECHNIQUE - GROUPEMENT INTERACADEMIQUE II - SESSION 1990

PHOTOCOPIEUSE

CORRIGE

I - ETUDE DE FP1 (ALIMENTATION)

I.1 - ETUDE DE FS1.1 (alimentation continue régulée +5 V)

Données : Vd = 0,85 V, VC1moy = 9 V, I1moy = 1 A, VLCQW54 = 1,8 V, Tjmax = 125 °C, Rthja = 35 °C/W, RThjb = 2 °C/W

VC1

I.1.1 VC1 min = 8V et VC1 max = 8 2 − 2 × Vd = 9,6V

9,6V

I.1.2 Pendant la décharge de C1, VC1 = - I1 × t / C1 + VC1max 8V

⇒ C1 = (I1 × Td) / (VC1max - VC1min) = 1 × 8.10-3 / (9,6 - 8) = 5000µF. 8ms

10ms

I.1.3 a) Td = 8ms. 0

b) La valeur normalisée de C1 est 4700 µF et la tension de service doit être 0 5ms 10ms 15ms 20ms t

supérieure à 9,6V. 35 V est bien une valeur supérieure à 9,6V.

I.1.4 P = (VC1moy - Vcc) × I1moy = (9 - 5) × 1 = 4 W.

I.1.5 Rthjamax = (Tjmax - Ta) / P = (125 - 40) / 4 ≅ 21 °C/W. La résistance thermique jonction/ambiant du boîtier TO3 du LM323 est de 35°C/W.

Il faudra donc un radiateur permettant d’avoir, au plus, une résistance thermique boîtier/ambiant de 19°C/W.

I.1.6 Les caractéristiques des composants électroniques varient en fonction de la température. La température modifie donc la précision

du composant et peut, si elle est trop importante, le détruire (Tj > 125°C).

I.1.7 R1 = (Vcc - VL) / IL = (5 - 1,8) / 13.10-3 = 246 Ω. Je prendrai donc dans la série E12 : R1 = 220 Ω 1/4W ou R1 = 270 Ω 1/4W.

I.1.8 La LED L indique que l’alimentation 5V est en fonction.

I.2 - ETUDE DE FS1.2 (alimentation continue régulée +24 V).

Données : Vd = 0,65 V, VC2moy = 30 V, Imoy = 2 A, Transistor : β = 9, Veb = +0,7 V

I.2.1 Type du transistor T : PNP.

I.2.2 Vb = VC2moy - Veb = 30 - 0,7 = 29,3 V

I.2.3 I3 = Veb / R2 = 0,7 / 68 = 10,3 mA ;

Ie = Imoy - I3 = 2 - 10,3.10-3 = 1,99 A ;

Ib = Ic / β et Ic = Ie - Ib ⇒ Ib = Ie / (β + 1) = 1,99 / 10 = 199 mA ; et Ic = 1,99 - 0,199 = 1,79 A ;

I2 = Ib + I3 = 199.10-3 + 10,3.10-3 = 209,3 mA.

I.2.4 Vce moy = Vs - VC2moy = 24 - 30 = - 6 V. Le transistor T est donc passant.

I.2.5 PT = Ic × Vec + Ib × Veb ≅ Ic × Vec = 1,79 × 6 ≅ 10,7 W .

PCI2 ≅ I2 × (Vb - Vs) = 209,3.10-3 × (29,3 - 24) ≅ 1,11 W.

I.2.6 Le transistor T devra être monté sur un radiateur.

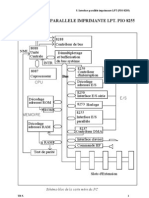

II - ETUDE DE FP2 (UNITE DE TRAlTEMENT MICROPROGRAMMEE).

II.1 - ETUDE DE FS21 (Base de temps):

II.1.1 Freq E = 1MHz ⇒ Période E = 1µs . Il y a donc 1 million de périodes E

par seconde donc 250 000 instructions par seconde (4fois moins). Vcc

0

II.1.2 Représentation du signal F : voir graphe ci-contre. t

Q

II.1.3 Fréq F = 2 MHz. Vcc

0

II.1.4 Fréq F1 = Fréq F / 21 = Fréq F / 2 = 1 MHz. t

Fréq F4 = Fréq F / 24 = Fréq F / 16 = 125 kHz. F

Fréq F8 = Fréq F / 28 = Fréq F / 256 = 7,8125 kHz. Vcc

0

t

LEGT Basse-Terre - T. GOMILA PHOTOCOPIEUSE - 1990 - CORRIGE

BAC STI GENIE ELECTRONIQUE - EPREUVE D’ETUDE D’UN SYSTEME TECHNIQUE 2/2

II.2 - ETUDE DE FS22 (mémoire de programme)

II.2.1 CI6 est une EPROM possédant 13 bits d’adresses et 8 bits de données.

Sa capacité est donc de : 213 octets = 8192 octets = 8 Kilo-octets = 64 Kilo-bits = 65536 bits.

II.2.2 Plan d’adressage de FS22

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 R/W BA BS

1er octet mémoire EPROM1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

dernier octet mémoire EPROM1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0

1er octet mémoire EPROM2 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

dernier octet mémoire EPROM2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0

II.2.3 - L’EPROM1 se situe entre $C000 à $ DFFF.

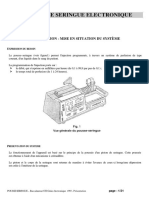

II.3 - ETUDE DE FS23 (circuit de protection et de contrôle du RESET SYSTEME)

II.3.1 Tableau des niveaux logiques des signaux A9, A8, A7, A6, Signal K A9 A8 A7 A6 CGL R/W

CGL et R/W conduisant à K = 1. Niveau logique 1 1 1 1 1 0 0

II.3.2 K = A9. A8. A7. A6. CGL.R / W avec CGL = A15. A14. A13 ⇒ K = A15. A14. A13. A9. A8. A7. A6. R / W

II.3.3 L'adresse minimale correspondante à K = 1 est $A3C0

II.3.4 T1 = R4 C4 = 22ms et T2 = R5 C5 = 10ms

II.3.5 Le bouton poussoir BP sert de réinitialisation manuelle du système (le RESET est actif lors de l’appui sur ce BP).

Réponse à la question II.3.4 Réponse à la question II.3.6

K Vcc

Vcc +5V

0 0

25 50 75 t t

(ms) 0,2 0,4 0,6 0,8 1 1,2 1,4 1,6 (s)

Q1 VC3

Vcc +5V

0

t

22ms 10ms Vcc/2

Q2

Vcc

0

0 t

t 0,693.R3.C3=0,1s

RESET

RESET

+5V

Vcc

0

0 t

t

II.3.7 L’ensemble +Vcc , R3, C3 sert d’initialisation automatique du système lors de la mise sous tension.

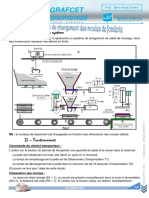

III - ETUDE DE FP3 (COMMANDE ET CONTROLE DE L'EXPOSITION).

ETUDE DE FS31 (commande de l'exposition) :

III.1 R21 sert de résistance de tirage à la masse. Elle fixe un niveau bas sur l’entrée PE en l’absence d’appui sur le bouton poussoir BN.

CI14 est un circuit CMOS le courant d’entrée est négligeable, on peut donc prendre n’importe quelle résistance assez grande, quelques

dizaine de kΩ. Exemple R21 = 47 kΩ Ω

III.2 Q0 = 1 ; Q1 = 0 ; Q2 = 1 ; Q3 = 0.

III.3 Quand BF est actionné (BC étant au repos), U/D reste à 1, CK passe à l’état haut (front montant). CI14 s’incrémente d’un pas.

III.4 Quand BC est actionné (BF étant au repos), U/D passe à 0, CK passe à l’état haut (front montant). CI14 se décrémente d’un pas

III.5 CI16 sert d’anti-rebond pour les boutons poussoirs BC et BF.

III.6 VX = - ( V0 / R10 + V1 / R11 + V2 / R12 + V3 / R13 ) × R14 = - ( V3 + V2 / 2 + V1 / 4 + V0 / 8 )

III.7 Quand Qn = 1 ⇒ Vn = 5 V - VX0 = 0 V

Quand Qn = 0 ⇒ Vn = 0 V - VX5 = - ( V2 / 2 + V0 / 8 ) = - 3,125 V

- VX9 = - ( V3 + V0 / 8 ) = - 5,625 V

Ω et d’un ajustable de 22 kΩ

III.8 R10 sera l’association d’une résistance de 68 kΩ Ω montés en série.

LEGT Basse-Terre - T. GOMILA PHOTOCOPIEUSE - 1990 - CORRIGE

S-ar putea să vă placă și

- Eval1 QCM TSSE1Document5 paginiEval1 QCM TSSE1Doha Bens100% (1)

- Sujet Automatisme Et Informatique Industrielle TcmaDocument14 paginiSujet Automatisme Et Informatique Industrielle TcmaEugene MballaÎncă nu există evaluări

- Distributeur de Billets (Corrigé)Document2 paginiDistributeur de Billets (Corrigé)Rouaissi RidhaÎncă nu există evaluări

- E Diviseur TensionDocument4 paginiE Diviseur TensionYassine M100% (1)

- Étude Des Familles de Circuits LogiquesDocument41 paginiÉtude Des Familles de Circuits LogiquesStanislas Godwin BASSAH100% (1)

- Circuits Electriques EXAMEN THEORIQUE 1Document13 paginiCircuits Electriques EXAMEN THEORIQUE 1Anbari MehdiÎncă nu există evaluări

- Comment Fonctionne Le Circuit de Minuterie NE555Document18 paginiComment Fonctionne Le Circuit de Minuterie NE555Arounan DembeleÎncă nu există evaluări

- Pic 16 F 877Document10 paginiPic 16 F 877Youssef Boughallad100% (1)

- Epreuve D'electronique Pour Electrotechnicien 1Document4 paginiEpreuve D'electronique Pour Electrotechnicien 1Patrick Steve Simo100% (2)

- Cartes ExtensionDocument7 paginiCartes Extensionsouriant1100% (1)

- NE555 Et CD4017Document32 paginiNE555 Et CD4017MARIE VIANNEYÎncă nu există evaluări

- Le Circuit Integre Ne555Document4 paginiLe Circuit Integre Ne555Sami Mahjoubi100% (1)

- Epreuve 2Document4 paginiEpreuve 2ChristianÎncă nu există evaluări

- BTSELECTRO Etude D Equipement Electrique 2016Document8 paginiBTSELECTRO Etude D Equipement Electrique 2016Ayoub EnergieÎncă nu există evaluări

- Structure 68000Document9 paginiStructure 68000Otman Mchachti100% (2)

- Guide Pour La Fabrication de Circuits ImprimesDocument12 paginiGuide Pour La Fabrication de Circuits ImprimesOliver TwisteÎncă nu există evaluări

- 1 Logique Combinatoire PDFDocument35 pagini1 Logique Combinatoire PDFMOUMMOUÎncă nu există evaluări

- Les Transistors PDFDocument36 paginiLes Transistors PDFchayef100% (1)

- Upload - Résumé Du Cours-Microcontroleurs - 2016-2017Document7 paginiUpload - Résumé Du Cours-Microcontroleurs - 2016-2017Habib Ben AmmarÎncă nu există evaluări

- Marquage Oeufs Séquenceur CorrectionDocument4 paginiMarquage Oeufs Séquenceur Correctionsoumeya100% (1)

- Filtres Du Second OrdreDocument4 paginiFiltres Du Second OrdreEmmanuel AkedÎncă nu există evaluări

- Micro ControleurDocument9 paginiMicro ControleurAdel JamilaÎncă nu există evaluări

- Alimentation StabiliséeDocument4 paginiAlimentation StabiliséeMohammed Chnafa50% (2)

- TD - Théorèmes Généraux de L'électricitéDocument7 paginiTD - Théorèmes Généraux de L'électricitéEsperance TchibindaÎncă nu există evaluări

- RAPPORTDocument16 paginiRAPPORTAubin SouopÎncă nu există evaluări

- Exercice CodeurDocument5 paginiExercice CodeurMoncef MhasniÎncă nu există evaluări

- TD AmplificateursdepuissanceDocument3 paginiTD Amplificateursdepuissancemutrace100% (1)

- 604 TD 2016Document66 pagini604 TD 2016minkoominÎncă nu există evaluări

- Section Sciences Techniques Epreuve Technologie: Devoir de Controle N°1Document5 paginiSection Sciences Techniques Epreuve Technologie: Devoir de Controle N°1Lotfi NairiÎncă nu există evaluări

- TD-Alternatif Et PuissanceDocument24 paginiTD-Alternatif Et PuissanceBakr IbrahimiÎncă nu există evaluări

- Circuit IntegresDocument7 paginiCircuit IntegresAbd OUÎncă nu există evaluări

- TP 1, Initiation A La Programmation Du Pic 16F877A Premiere Approche Des Logiciels UtilisesDocument6 paginiTP 1, Initiation A La Programmation Du Pic 16F877A Premiere Approche Des Logiciels UtilisesNaima BajouÎncă nu există evaluări

- Les Circuits IntegresDocument71 paginiLes Circuits IntegresBilel Ben Jamel Souidi100% (1)

- Etude D'un Logiciel de Simulation ProteusDocument30 paginiEtude D'un Logiciel de Simulation ProteusStanley Vianney100% (1)

- Automates Programmables Industriels (A.P.I)Document26 paginiAutomates Programmables Industriels (A.P.I)Hayet BechedliÎncă nu există evaluări

- Alimentation StabiliséeDocument1 paginăAlimentation StabiliséeMouritaniDakhnawi100% (3)

- Elec1 TDDocument12 paginiElec1 TDDDDDÎncă nu există evaluări

- AnalyseCircuitsElectriques (TP 2 3)Document14 paginiAnalyseCircuitsElectriques (TP 2 3)Martin100% (1)

- Exercices PICvers2Document3 paginiExercices PICvers2sanonymeÎncă nu există evaluări

- Corrigé TD4 CNDocument14 paginiCorrigé TD4 CNPapeCheikh SYLLA100% (1)

- Analyse Temporelle GrafcetDocument2 paginiAnalyse Temporelle GrafcetKhaled Ouni100% (1)

- Exam - ARCHITECTURE - Jan - 2021-V3 - CorrigéDocument2 paginiExam - ARCHITECTURE - Jan - 2021-V3 - CorrigéGANG SHOOTÎncă nu există evaluări

- Série de TD N°03Document1 paginăSérie de TD N°03sarah wiwi100% (1)

- Cours Electronique Numerique-3Document141 paginiCours Electronique Numerique-3ibouÎncă nu există evaluări

- Exercice Cor8rigé Sur La Théorème de ThéveninDocument7 paginiExercice Cor8rigé Sur La Théorème de ThéveninTalel Missaoui100% (1)

- Port Parallèle Pia 8255Document11 paginiPort Parallèle Pia 8255alex bbapÎncă nu există evaluări

- Programmation de L'interface ParallèleDocument10 paginiProgrammation de L'interface ParallèleAbdeltif BelquorchiÎncă nu există evaluări

- Exercice 3Document1 paginăExercice 3Adel KmimechÎncă nu există evaluări

- TD2 - Grafcet - Mise en Équations - MatérialisationDocument4 paginiTD2 - Grafcet - Mise en Équations - Matérialisationfakhfakh100% (1)

- Grafcet Synchronisé: I - Description Du SystèmeDocument4 paginiGrafcet Synchronisé: I - Description Du SystèmeNou Ha BenabdallahÎncă nu există evaluări

- TDDocument10 paginiTDredÎncă nu există evaluări

- 04 Microprocesseur 8086Document18 pagini04 Microprocesseur 8086nesrine ninaÎncă nu există evaluări

- Arduino | Pas à pas: Le guide ultime du débutantDe la EverandArduino | Pas à pas: Le guide ultime du débutantÎncă nu există evaluări

- Projets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadDe la EverandProjets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadÎncă nu există evaluări

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesDe la EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesÎncă nu există evaluări

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabDe la EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabÎncă nu există evaluări

- Support TP Electronique S4Document25 paginiSupport TP Electronique S4Jihane AlouiÎncă nu există evaluări

- Devoir ÉlectriqueDocument2 paginiDevoir ÉlectriqueFouad Abatouy0% (1)

- Correction TD Puissance OnduleurDocument5 paginiCorrection TD Puissance OnduleurMourad BelkassemiÎncă nu există evaluări

- HOLOGRAPHIEDocument14 paginiHOLOGRAPHIEChabehouÎncă nu există evaluări

- Maths4 TD 5 Support PDFDocument22 paginiMaths4 TD 5 Support PDFYounes RabehiÎncă nu există evaluări

- Classement-UNEF-des-villes-universitaires-2022Document50 paginiClassement-UNEF-des-villes-universitaires-2022ChabehouÎncă nu există evaluări

- support_de_presentation_conference_benchmark_diversiteDocument49 paginisupport_de_presentation_conference_benchmark_diversiteChabehouÎncă nu există evaluări

- Cours D'algorithmeDocument248 paginiCours D'algorithmeYassine Sinou AlaziziÎncă nu există evaluări

- Arduino Cours 2016Document44 paginiArduino Cours 2016Julio Ratovonkery100% (1)

- Cours Limites Et Asymptotes Maths-TerminaleDocument10 paginiCours Limites Et Asymptotes Maths-TerminaleChabehouÎncă nu există evaluări

- Maths Bepc - Blanc - Up Bingerville 2015Document2 paginiMaths Bepc - Blanc - Up Bingerville 2015ChabehouÎncă nu există evaluări

- Aires Volumes FormuleDocument5 paginiAires Volumes FormuleChabehouÎncă nu există evaluări

- Dclics Parcours RobotiqueDocument108 paginiDclics Parcours RobotiqueadmmehdiÎncă nu există evaluări

- Elec - Arduino - Memo Et CondenseDocument36 paginiElec - Arduino - Memo Et CondenseNadia Sahli100% (1)

- Info GlossaireDocument112 paginiInfo GlossaireWassim Attia100% (1)

- TD Nombre Complexe 3Document9 paginiTD Nombre Complexe 3ChabehouÎncă nu există evaluări

- Premiers Pas en Informatique Embarquee PDFDocument268 paginiPremiers Pas en Informatique Embarquee PDFSaad ThamineÎncă nu există evaluări

- Club Robotique Et ProgrammationDocument5 paginiClub Robotique Et ProgrammationChabehouÎncă nu există evaluări

- Memento Creation Club ScientifiqueDocument52 paginiMemento Creation Club ScientifiqueChabehouÎncă nu există evaluări

- 1993 Pompe PeristaltiqueDocument20 pagini1993 Pompe PeristaltiqueChabehouÎncă nu există evaluări

- C Regulateurs PDFDocument5 paginiC Regulateurs PDFguedri houdaÎncă nu există evaluări

- 1993 Pousse Seringue ElectroniqueDocument21 pagini1993 Pousse Seringue ElectroniqueChabehou100% (1)

- 1993 PortixDocument18 pagini1993 PortixChabehouÎncă nu există evaluări

- Les Lois de La Gestion Du TempsDocument5 paginiLes Lois de La Gestion Du TempsOlivier DufourÎncă nu există evaluări

- Des Hubs Aux VlansDocument47 paginiDes Hubs Aux VlansChabehouÎncă nu există evaluări

- 1993-Pompe Peristaltique CorrigéDocument4 pagini1993-Pompe Peristaltique CorrigéChabehouÎncă nu există evaluări

- 1992 Portes Automatique Stanley Magic Door (Complet)Document17 pagini1992 Portes Automatique Stanley Magic Door (Complet)ChabehouÎncă nu există evaluări

- 1990 Photocopieuse PDFDocument8 pagini1990 Photocopieuse PDFChabehouÎncă nu există evaluări

- TD Systèmes Logiques PDFDocument67 paginiTD Systèmes Logiques PDFRajhiHoussem85% (13)

- PDF ExseqDocument27 paginiPDF ExseqMôhãmêd Bèñ100% (1)

- Algo Carré Magique1Document2 paginiAlgo Carré Magique1ChabehouÎncă nu există evaluări

- Theme de Recherche DTS 1 ElectriciteDocument1 paginăTheme de Recherche DTS 1 ElectriciteChabehouÎncă nu există evaluări

- TEMPLATE - Offre Odoo Pour PartenairesDocument38 paginiTEMPLATE - Offre Odoo Pour Partenairesjoel nugrohoÎncă nu există evaluări

- Licence LPDocument6 paginiLicence LPOualid OualidÎncă nu există evaluări

- Agreg Document Pell FermatDocument2 paginiAgreg Document Pell FermatMetyÎncă nu există evaluări

- Cours CryptanalyseDocument62 paginiCours CryptanalyseGensoft GensoftÎncă nu există evaluări

- Comment Gagner de L'argent Avec LinkedInDocument11 paginiComment Gagner de L'argent Avec LinkedInRahelisonÎncă nu există evaluări

- Fiche de Competences GitDocument2 paginiFiche de Competences GitCassandre213Încă nu există evaluări

- Introduction Big DataDocument24 paginiIntroduction Big Datakarim labidiÎncă nu există evaluări

- Exercice Sphinx PatisserieDocument8 paginiExercice Sphinx Patisserieeric.2021Încă nu există evaluări

- Math C 2 PDFDocument6 paginiMath C 2 PDFKhalil ChhataÎncă nu există evaluări

- Internet - Activité 6 - S'identifier Sur Internet (Partie 2)Document4 paginiInternet - Activité 6 - S'identifier Sur Internet (Partie 2)MonnierÎncă nu există evaluări

- Informatique - Option - Base de Donn+®es - BTSDocument139 paginiInformatique - Option - Base de Donn+®es - BTSzerrouki sarraÎncă nu există evaluări

- 11 RS232Document13 pagini11 RS232ioan jeanÎncă nu există evaluări

- Diagramme Gantt v4.1Document10 paginiDiagramme Gantt v4.1ICTB COTE D'IVOIREÎncă nu există evaluări

- Formation Opale AdvancedDocument50 paginiFormation Opale AdvancedAndo MampianinaÎncă nu există evaluări

- CAMPUS Livro Lista de MateriaisDocument11 paginiCAMPUS Livro Lista de Materiaisgeron1Încă nu există evaluări

- Les Ecrans Parlons en Ecran TotalDocument16 paginiLes Ecrans Parlons en Ecran TotalSophie AichaouiÎncă nu există evaluări

- Etude155222555 PDFDocument77 paginiEtude155222555 PDFOussama SlimaniÎncă nu există evaluări

- Gerer Sa Facturation Avec Access Maj Tutoriel Creer Une Facture Avec AccessDocument20 paginiGerer Sa Facturation Avec Access Maj Tutoriel Creer Une Facture Avec AccessXavier NkongÎncă nu există evaluări

- Etlv STMG Identites Et Echanges Fiche SequenceDocument2 paginiEtlv STMG Identites Et Echanges Fiche Sequencec.sankha93Încă nu există evaluări

- TP AlarmeDocument11 paginiTP AlarmeAbdelhamid SammoudiÎncă nu există evaluări

- Situation Probleme Algo CryptosystemesDocument3 paginiSituation Probleme Algo CryptosystemesnadineÎncă nu există evaluări

- Ligne 4Document16 paginiLigne 4Benoît AgassantÎncă nu există evaluări

- PS 200 Ferroscan Demo GuideDocument32 paginiPS 200 Ferroscan Demo GuidefontaineÎncă nu există evaluări

- Serie D'exercices 1 - Structures de Données - Cond - Iteratives - Algo - PythonDocument2 paginiSerie D'exercices 1 - Structures de Données - Cond - Iteratives - Algo - Pythonnaoufel charfeddineÎncă nu există evaluări

- 1.1.2.4 Lab - Mapping The InternetDocument13 pagini1.1.2.4 Lab - Mapping The InternetGiovanny Lauraine HendersonÎncă nu există evaluări

- Cours Informatique 1. Monsieur SADOUNI SalheddineDocument39 paginiCours Informatique 1. Monsieur SADOUNI SalheddineEmmanuel Brékibia OuattaraÎncă nu există evaluări

- TP NmapDocument6 paginiTP NmapSamy HassineÎncă nu există evaluări

- IA Séance 4Document54 paginiIA Séance 4Abdallahi SidiÎncă nu există evaluări

- Activite 1Document3 paginiActivite 1exgouÎncă nu există evaluări

- Je Dédie Ce Modeste Travail Et Ma Profonde Gratitude A: DedicacesDocument97 paginiJe Dédie Ce Modeste Travail Et Ma Profonde Gratitude A: DedicacesSana BhiraÎncă nu există evaluări