Documente Academic

Documente Profesional

Documente Cultură

TP04

Încărcat de

lange6810 evaluări0% au considerat acest document util (0 voturi)

81 vizualizări2 paginiknkn

Drepturi de autor

© © All Rights Reserved

Formate disponibile

PDF, TXT sau citiți online pe Scribd

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentknkn

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

0 evaluări0% au considerat acest document util (0 voturi)

81 vizualizări2 paginiTP04

Încărcat de

lange681knkn

Drepturi de autor:

© All Rights Reserved

Formate disponibile

Descărcați ca PDF, TXT sau citiți online pe Scribd

Sunteți pe pagina 1din 2

UNIVERSITE DE MOSTAGANEM

FACULTE DES SCIENCES ET DE LA TECHNOLOGIE

Département GENIE ELECTRIQUE

Electronique numérique avancée

TP n°0 : Circuits combinatoires

Partie 1 : Relié les commutateurs SW aux LED.

I. Objectifs

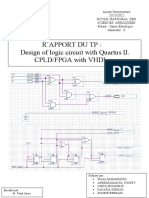

Nous voulons réaliser un circuit logique (Figure 1) avec la programmation VHDL

sous Quartus II et implémentera dans une FPGA de type ALTERA DE2.

Vcc

SW0

Pin_N25 Pin_AE23

LEDR0

Vcc

SW1 Pin_N26 Pin_AF23

LEDR1

EP2C35F672C6

Figure 1 : Circuit FPGA de type ALTERA cyclone II - EP2C35F672C6.

II. Matériels utilisé & Documentation nécessaires

Logiciel Quartus II v13.0

Carte de développement FPGA ALTERA DE2.

Câble USB relie la carte de développement DE2 avec le PC.

Fiche pratique n°1 : Prise en main DE2.

Fiche pratique n°2 : Prise en main VHDL.

III. Travail demandé

1. Créé un répertoire nommé « TP0 », afin de stoker les fichiers de votre projet

Quartus.

2. Crée un projet Quartus nommé « TP0.qpf » et le sauvegardez dans le répertoire

« TP0 ».

3. Développez en VHDL le circuit logique présenté à la figure n°1.

4. Inclure dans votre projet les tâches de goupille (Pin assignement) requise pour

le panneau DE2.

5. Compiler le projet.

Responsable du TP : Larbi beklaouz Hadj

Apres l’étape n°5, Quartus affiche le statut de la compilation. S’il y a des erreurs refaire

les étapes cité précédemment de 1 à 5. Si non, affiche compilation réussie avec le pourcentage

des ressources consommé.

IV. Simulation avec Quartus

6. Visualiser & vérifier le circuit logique développé en VHDL avec « RTL

Viewer ». Pour montrer le design du circuit.

7. Afin de simuler est examinée la fonctionnalité du circuit logique, nous pouvons

utiliser « Simulation WaveForm Editor ». Ainsi de présenter le chronogramme

logique du circuit.

V. Implémentation

8. Brancher la carte de développement DE2 avec le PC à l’aide du cable USB

Blaster.

9. Exécuter « Programmer » et vérifier si le PC reconnaitre la carte de

développement DE2. Si non, refaire l’étape n°8.

10. Le projet développé s’apparaitre dans le Programmer avec le nom « TP0.sof ».

Cliquer sur le bouton Star, pour charger le fichier « .sof » dans la cible FPGA.

VI. Vérification final

11. Examiner la fonctionnalité du circuit logique en basculant les commutateurs

SW et en observant les LEDs qui s’allument selon la logique du circuit

développé.

Responsable du TP : Larbi beklaouz Hadj

S-ar putea să vă placă și

- Rapport A DibDocument21 paginiRapport A DibMehdi El BakkouriÎncă nu există evaluări

- TP5 - Circuits Logiques Programmables CPLDDocument8 paginiTP5 - Circuits Logiques Programmables CPLDeya arfaouiÎncă nu există evaluări

- R'Apport Du TP: Design of Logic Circuit With Quartus II. Cpld/Fpga With VHDLDocument47 paginiR'Apport Du TP: Design of Logic Circuit With Quartus II. Cpld/Fpga With VHDLAbdelouahad FhailÎncă nu există evaluări

- Tppic16f877 Au 2018 2019Document19 paginiTppic16f877 Au 2018 2019MaramÎncă nu există evaluări

- Rapport Finals Er Rue Code eDocument29 paginiRapport Finals Er Rue Code ezineb kadiriÎncă nu există evaluări

- helabenghorbelL2SEM OdtDocument17 paginihelabenghorbelL2SEM OdtHela Ben GhorbelÎncă nu există evaluări

- FPGA - ArduinoDocument8 paginiFPGA - Arduinoali azilaÎncă nu există evaluări

- TP N2 - Circuits CombinatoiresDocument15 paginiTP N2 - Circuits CombinatoiresREDNANIÎncă nu există evaluări

- Tp1: Led Clignotante (Blink) : A. ObjectifDocument7 paginiTp1: Led Clignotante (Blink) : A. ObjectifhoudaÎncă nu există evaluări

- TP SE Licence Sujet OKDocument29 paginiTP SE Licence Sujet OKisaacnoah KouakouÎncă nu există evaluări

- 759 TP Compteur VHDL Virtual Instruments FpgaDocument21 pagini759 TP Compteur VHDL Virtual Instruments FpgaYouness LMÎncă nu există evaluări

- Sequence 1Document7 paginiSequence 1t22366526Încă nu există evaluări

- TP Integration Num FPGA V1.7Document22 paginiTP Integration Num FPGA V1.7Ouma ImaaÎncă nu există evaluări

- Travaux Dirigés FPGA & VHDLDocument28 paginiTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- Travaux Dirigés FPGA & VHDL - 2Document28 paginiTravaux Dirigés FPGA & VHDL - 2simohamed1993Încă nu există evaluări

- TP TER LoRa STM32 Dalancon KissiDocument18 paginiTP TER LoRa STM32 Dalancon KissiPascal BerthouÎncă nu există evaluări

- Compte Rendu TP Electronique NumériqueDocument16 paginiCompte Rendu TP Electronique NumériqueEL YâssirÎncă nu există evaluări

- TP Uc877 SAADAOUI Vide À CompléterDocument8 paginiTP Uc877 SAADAOUI Vide À CompléterBenkilani RimÎncă nu există evaluări

- tp3 VHDLDocument10 paginitp3 VHDLAya BchiniÎncă nu există evaluări

- Tuto VivadoDocument7 paginiTuto Vivadoجميلة جميلةÎncă nu există evaluări

- Compte RenduDocument21 paginiCompte RenduYoussef BTS SEÎncă nu există evaluări

- Compte RenduDocument21 paginiCompte RenduYoussef BTS SEÎncă nu există evaluări

- Compte RenduDocument5 paginiCompte RenduAlaa MessaoudÎncă nu există evaluări

- Objectifs:: Module: Internet of Things and Cloud Computing TP N°1: Introduction de La Plateforme ArduinoDocument4 paginiObjectifs:: Module: Internet of Things and Cloud Computing TP N°1: Introduction de La Plateforme ArduinoMoulay Ayoub ChaabaÎncă nu există evaluări

- Compte Rendu TP1 VHDLDocument8 paginiCompte Rendu TP1 VHDLboussaoud.oualidÎncă nu există evaluări

- rOBOT SUIVEUR DE LIGNE À FPGA AlteraDocument23 paginirOBOT SUIVEUR DE LIGNE À FPGA AlteraH. Seo100% (2)

- 12arduino Intro Et chp1 Et 2Document8 pagini12arduino Intro Et chp1 Et 2Tadjou AdomÎncă nu există evaluări

- VL53L0X Laser Distance Sensor Module - FRDocument21 paginiVL53L0X Laser Distance Sensor Module - FRPI PICOÎncă nu există evaluări

- Prog Registres ArduinoDocument7 paginiProg Registres ArduinoAdil AbouelhassanÎncă nu există evaluări

- TP LCDDocument6 paginiTP LCDchadli saidÎncă nu există evaluări

- TP MicrocontrôleurDocument38 paginiTP MicrocontrôleurNourallah Aouina100% (3)

- Arduino Et Afficheur LCDDocument4 paginiArduino Et Afficheur LCDHichem Hamdi100% (1)

- 8 I2cDocument6 pagini8 I2cbtssnaÎncă nu există evaluări

- MSP 430 MemioDocument20 paginiMSP 430 MemioIgor KAMGUE FOKOÎncă nu există evaluări

- Tp1 Con-Cir Log 2iotDocument9 paginiTp1 Con-Cir Log 2iotferielÎncă nu există evaluări

- TP6: de La Conception Graphique À La Programmation Des CPLD Et FPGA I. ObjectifDocument7 paginiTP6: de La Conception Graphique À La Programmation Des CPLD Et FPGA I. ObjectifLAHOUSSINE ELMAHNIÎncă nu există evaluări

- TP 01Document10 paginiTP 01Ilh BrighÎncă nu există evaluări

- TP1-ΜC - Prise en MainDocument17 paginiTP1-ΜC - Prise en MainNabil EL KassoumiÎncă nu există evaluări

- Travaux Pratique 2 RLIDocument12 paginiTravaux Pratique 2 RLIKader AbdoulÎncă nu există evaluări

- Résumé - Français - ASIC FPGA CPLD Course (Important)Document21 paginiRésumé - Français - ASIC FPGA CPLD Course (Important)hichemÎncă nu există evaluări

- TP ElecII GM2 PDFDocument21 paginiTP ElecII GM2 PDFyoussef MoujanniÎncă nu există evaluări

- E2i3 Tp1 Cod Sopc Builder 2012Document27 paginiE2i3 Tp1 Cod Sopc Builder 2012Elbahaoui Abdel100% (1)

- Allumer Et Éteindre Des LEDs Avec Smartphone Et ArduinoDocument14 paginiAllumer Et Éteindre Des LEDs Avec Smartphone Et ArduinoMahamat Youssouf YassirÎncă nu există evaluări

- Maquette de Développement PIC 16FXXXDocument22 paginiMaquette de Développement PIC 16FXXXNejib JallouliÎncă nu există evaluări

- TR Ordo ArduinoDocument8 paginiTR Ordo ArduinoSmart ClasseÎncă nu există evaluări

- DE1 SoC TP1 v18Document26 paginiDE1 SoC TP1 v18Saamson StephenÎncă nu există evaluări

- CF VHDL 2021Document1 paginăCF VHDL 2021Ayman LamzouriÎncă nu există evaluări

- CorrigeDocument2 paginiCorrigeRod GOMAÎncă nu există evaluări

- TP FpgaDocument22 paginiTP FpgakfawazÎncă nu există evaluări

- Simulation FPGADocument24 paginiSimulation FPGAIlyass2012Încă nu există evaluări

- 19 VHDLDocument15 pagini19 VHDLAmina GhardallouÎncă nu există evaluări

- Mini Projet EclairageDocument3 paginiMini Projet EclairageNeiville AgbrÎncă nu există evaluări

- td1 Arduino Ing2Document6 paginitd1 Arduino Ing2kawtar elbirakiÎncă nu există evaluări

- Cours VHDLDocument62 paginiCours VHDLBrice Albin Fotso GhomdimÎncă nu există evaluări

- Cours 1Document56 paginiCours 1ElMegoÎncă nu există evaluări

- Etude Et Realisation D'une Horloge NumeriqueDocument38 paginiEtude Et Realisation D'une Horloge NumeriqueHon Ey100% (1)

- Projets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadDe la EverandProjets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadÎncă nu există evaluări

- Projets Arduino avec Tinkercad: Concevoir et programmer des projets basés sur Arduino avec TinkercadDe la EverandProjets Arduino avec Tinkercad: Concevoir et programmer des projets basés sur Arduino avec TinkercadEvaluare: 1 din 5 stele1/5 (1)

- Arduino Pas à pas: Le guide ultime du débutant avec les bases du matériel, du logiciel, de la programmation et des projetsDe la EverandArduino Pas à pas: Le guide ultime du débutant avec les bases du matériel, du logiciel, de la programmation et des projetsEvaluare: 4 din 5 stele4/5 (1)

- Tinkercad | Pas à pas: Créer des objets 3D (CAO), schémas électroniques et apprendre à programmerDe la EverandTinkercad | Pas à pas: Créer des objets 3D (CAO), schémas électroniques et apprendre à programmerÎncă nu există evaluări

- Mémoire 1Document7 paginiMémoire 1lange681Încă nu există evaluări

- TP N°1 - Prise en Main de L'environnement APIDocument5 paginiTP N°1 - Prise en Main de L'environnement APIlange681Încă nu există evaluări

- TP N°2 DSPDocument2 paginiTP N°2 DSPlange681Încă nu există evaluări

- Mise en Oeuvre GrafcetDocument12 paginiMise en Oeuvre GrafcetMohammed Amine KenedÎncă nu există evaluări

- TD1 Séquentiel-ConvertiDocument2 paginiTD1 Séquentiel-Convertilange681Încă nu există evaluări

- TP N°2 - Mise en Oueuvre D APIDocument4 paginiTP N°2 - Mise en Oueuvre D APIlange681Încă nu există evaluări

- Mémoire 1Document7 paginiMémoire 1lange681Încă nu există evaluări

- TD 4Document1 paginăTD 4lange681Încă nu există evaluări

- solution-TD N°2Document2 paginisolution-TD N°2lange681Încă nu există evaluări

- TD 2Document1 paginăTD 2lange681Încă nu există evaluări

- TP N°1 DSPDocument1 paginăTP N°1 DSPlange681Încă nu există evaluări

- TD 1Document1 paginăTD 1lange681Încă nu există evaluări

- TD 3Document1 paginăTD 3lange681Încă nu există evaluări

- Solution-TD N°1Document5 paginiSolution-TD N°1lange681Încă nu există evaluări

- Cours Sur Les MEMS de La Conception À La Fabrication Des MEMSDocument5 paginiCours Sur Les MEMS de La Conception À La Fabrication Des MEMSlange681Încă nu există evaluări

- Chapitre 4-1 DSPDocument7 paginiChapitre 4-1 DSPlange681Încă nu există evaluări

- Chapitre 2 DSPDocument3 paginiChapitre 2 DSPlange681Încă nu există evaluări

- Chapitre 3 DSPDocument4 paginiChapitre 3 DSPlange681Încă nu există evaluări

- TP1 PooDocument1 paginăTP1 Poolange681Încă nu există evaluări

- Chapitre 1 DSPDocument7 paginiChapitre 1 DSPlange681Încă nu există evaluări

- CHP II-La Mesure Et Les Capteurs IndustrielsDocument129 paginiCHP II-La Mesure Et Les Capteurs Industrielslange681Încă nu există evaluări

- Les Systèmes À Énergies AutonomesDocument5 paginiLes Systèmes À Énergies Autonomeslange681Încă nu există evaluări

- Proposition de Sujets ExposéDocument1 paginăProposition de Sujets Exposélange681Încă nu există evaluări

- Sea Cours 2 Et 3Document2 paginiSea Cours 2 Et 3lange681Încă nu există evaluări

- Solutions Desexercices duTP03Document12 paginiSolutions Desexercices duTP03lange681Încă nu există evaluări

- Tableaux Et Pointeurs en C++Document10 paginiTableaux Et Pointeurs en C++lange681Încă nu există evaluări

- TP02 Programmation Orientée ObjetDocument1 paginăTP02 Programmation Orientée Objetlange681Încă nu există evaluări

- TP01 Programmation Orientée ObjetDocument1 paginăTP01 Programmation Orientée Objetlange681Încă nu există evaluări

- TP01Document8 paginiTP01lange681Încă nu există evaluări

- M1 Ese Poo TP6Document1 paginăM1 Ese Poo TP6lange681Încă nu există evaluări

- TP1 FpgaDocument6 paginiTP1 Fpgasaid100% (1)

- Mini Projet VHDLDocument29 paginiMini Projet VHDLMouad ES SoubaaiÎncă nu există evaluări

- CoursDocument11 paginiCoursIly'as En-naouiÎncă nu există evaluări

- Etude Et Realisation D'une Horloge NumeriqueDocument38 paginiEtude Et Realisation D'une Horloge NumeriqueHon Ey100% (1)

- Électronique Numérique AvancéeDocument81 paginiÉlectronique Numérique AvancéeBoulbeba Jribi100% (1)

- 387 2 Sin Fpga Schema 2 PDFDocument23 pagini387 2 Sin Fpga Schema 2 PDFGhani LamiÎncă nu există evaluări

- Les Microcontrôleurs PICDocument26 paginiLes Microcontrôleurs PICMøhãmëd BåkKäriÎncă nu există evaluări

- Guide de Laboratoire ELE3311 SYSTÈMES LOGIQUES PROGRAMMABLESDocument79 paginiGuide de Laboratoire ELE3311 SYSTÈMES LOGIQUES PROGRAMMABLESabdelli aliÎncă nu există evaluări

- Flots de Conception Et CodesignDocument40 paginiFlots de Conception Et CodesignHichem GuedriÎncă nu există evaluări

- Layout Avancé-Chapitre2-2Document34 paginiLayout Avancé-Chapitre2-2Hossam El KhiariÎncă nu există evaluări

- ZYNQDocument13 paginiZYNQSmart ClasseÎncă nu există evaluări

- 8 Commande D'un Moteur À CC - V2Document26 pagini8 Commande D'un Moteur À CC - V2Mohamed Hechmi JERIDIÎncă nu există evaluări

- TP 4 Xilinx - FPGADocument9 paginiTP 4 Xilinx - FPGAHàjàr KcimÎncă nu există evaluări

- Pfe VHDL FpgaDocument38 paginiPfe VHDL FpgaBilal LkhloufÎncă nu există evaluări

- Github CoursDocument31 paginiGithub Coursbader haouariÎncă nu există evaluări

- TP 1Document12 paginiTP 1Usb MasÎncă nu există evaluări

- MC Codesign 2015Document20 paginiMC Codesign 2015Mohamed Ali AbdallahÎncă nu există evaluări

- Suite Cours Fpga Ikram MaaouiDocument26 paginiSuite Cours Fpga Ikram MaaouiFeriel GHOUILAÎncă nu există evaluări

- VHDLDocument101 paginiVHDLMariem ZoubirÎncă nu există evaluări

- Electronique Electrotechnique AutomatiqueDocument32 paginiElectronique Electrotechnique AutomatiqueHgkckvÎncă nu există evaluări

- Logique Programmable Mémoires Mortes: PROM, EPROM, EEPROM: Conception Et Implémentation de Systèmes NumériquesDocument16 paginiLogique Programmable Mémoires Mortes: PROM, EPROM, EEPROM: Conception Et Implémentation de Systèmes NumériquesGray AbÎncă nu există evaluări

- Chapitre 1 Classification Des Circuits IntégrésDocument29 paginiChapitre 1 Classification Des Circuits IntégrésHichem GuedriÎncă nu există evaluări

- Conception de PCB.Document93 paginiConception de PCB.Olivier PrusÎncă nu există evaluări

- Cours Fpga PDFDocument63 paginiCours Fpga PDFمحمد الأمير الحازمي100% (1)

- Eln-Electronique Desn Systemes EmbarquesfDocument23 paginiEln-Electronique Desn Systemes EmbarquesfMarquiz DitchiÎncă nu există evaluări

- Cours VHDL 10 Partie1 IntroductionDocument57 paginiCours VHDL 10 Partie1 IntroductionHedi TunÎncă nu există evaluări

- TD N 1 FpgaDocument3 paginiTD N 1 FpgaLE BARON100% (1)

- Electronique Et Loisirs N002Document72 paginiElectronique Et Loisirs N002mechergui100% (3)

- Cours dsp06 07Document68 paginiCours dsp06 07Farouk Zeani100% (2)

- 6 ELN Electronique Des Systèmes Embarqués - 11septDocument77 pagini6 ELN Electronique Des Systèmes Embarqués - 11septDOUNIAÎncă nu există evaluări