Documente Academic

Documente Profesional

Documente Cultură

Memristor

Încărcat de

Nibin PayaniDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Memristor

Încărcat de

Nibin PayaniDrepturi de autor:

Formate disponibile

Memristor based multilevel memory 1

1. INTRODUCTION

1.1 MEMRISTOR

For nearly 150 years, the known fundamental passive circuit elements were limited to the

capacitor (discovered in 1745), the resistor (1827), and the inductor (1831). Then, in a brilliant

but underappreciated 1971 paper, Leon Chua, a professor of electrical engineering at the

University of California, Berkeley, predicted the existence of a fourth fundamental device, which

he called a memristor. He proved that memristor behavior could not be duplicated by any circuit

built using only the other three elements, which is why the memristor is truly fundamental.

Memristor is a contraction of “memory resistor,” because that is exactly its function: to

remember its history. A memristor is a two-terminal device whose resistance depends on the

magnitude and polarity of the voltage applied to it and the length of time that voltage has been

applied. When you turn off the voltage, the memristor remembers it’s most recent resistance until

the next time you turn it on, whether that happens a day later or a year later

Chua discovered a missing link in the pair wise mathematical equations that relate the

four circuit quantities—charge, current, voltage, and magnetic flux—to one another. These can

be related in six ways. Two are connected through the basic physical laws of electricity and

magnetism, and three are related by the known circuit elements: resistors connect voltage and

current, inductors connect flux and current, and capacitors connect voltage and charge. But one

equation is missing from this group: the relationship between charge moving through a circuit

and the magnetic flux surrounded by that circuit

Chua demonstrated mathematically that his hypothetical device would provide a relationship

between flux and charge similar to what a nonlinear resistor provides between voltage and cur-

rent. In practice, that would mean the device’s resistance would vary according to the amount of

charge that passed through it. And it would remember that resistance value even after the current

was turned of

College of engineering chengannur

Memristor based multilevel memory 2

1.2 THEORY

Memristor symbol.

The memristor is formally defined as a two-terminal element in which the magnetic flux Φm

between the terminals is a function of the amount of electric charge q that has passed through the

device. Each memristor is characterized by its memristance function describing the charge-

dependent rate of change of flux with charge.

Noting from Faraday's law of induction that magnetic flux is simply the time integral of voltage,

and charge is the time integral of current, we may write the more convenient form

It can be inferred from this that memristance is simply charge-dependent resistance. If M (q (t))

is a constant, then we obtain Ohm's Law R (t) = V (t)/ I (t). If M (q (t)) is nontrivial, however, the

equation is not equivalent because q (t) and M (q (t)) will vary with time. Solving for voltage as a

function of time we obtain

This equation reveals memristance defines a linear relationship between current and voltage, as

long as M does not vary with charge. Of course, nonzero current implies time varying charge.

College of engineering chengannur

Memristor based multilevel memory 3

Alternating current, however, may reveal the linear dependence in circuit operation by inducing

a measurable voltage without net charge movement as long as the maximum change in q does

not cause much change in M.

Furthermore, the memristor is static if no current is applied. If I (t) = 0, we find V (t) = 0 and

M (t) is constant. This is the essence of the memory effect.

The power consumption characteristic recalls that of a resistor, I2R.

As long as M (q (t)) varies little, such as under alternating current, the memristor will appear as a

resistor. If M (q (t)) increases rapidly, however, current and power consumption will quickly

stop.

2. DETAILED DISCRIPTION

2.1 STRUCTURE OF TITANIUM DIOXIDE MEMRISTOR

College of engineering chengannur

Memristor based multilevel memory 4

IO

Fig 2.1.1

The HP device is composed of a thin (50 nm) titanium dioxide film between two 5 nm thick

electrodes, two platinum wires

Initially, there are two layers to the titanium dioxide film, TiO2 and TiO2-x. The upper layer

has a slight depletion of oxygen atoms. The oxygen vacancies are donors of electrons which

makes the vacancies themselves positively charged. Stoichiometric TiO2 act as an insulator

(It is a semiconductor) but oxygen deficient TiO2-x is a conductor and have lower resistance

than the stoichiometric compound

College of engineering chengannur

Memristor based multilevel memory 5

2.2 WORKING

Fig 2.2.1

If a positive voltage is applied to the top electrode of the device, it will repel the (also positive)

oxygen vacancies in the TiO2-x layer down into the pure TiO2 layer. That turns the TiO2 layer

into TiO2-x and makes it conductive, thus turning the device on. A negative voltage has the

opposite effect: the vacancies are attracted upward and back out of the TiO2, and thus the thick-

ness of the TiO2 layer increases and the device turns off.

The oxygen deficiencies in the TiO2-x manifest as “bubbles” of oxygen vacancies

scattered throughout the upper layer. A positive voltage on the switch repels the (positive)

oxygen deficiencies in the metallic upper TiO2-x layer, sending them into the insulating TiO2

layer below. That causes the boundary between the two materials to move down, increasing the

percentage of conducting TiO2-x and thus the conductivity of the entire switch. The more

positive voltage is applied, the more conductive the cube becomes.

A negative voltage on the switch attracts the positively charged oxygen bubbles, pulling

them out of the TiO2. The amount of insulating, resistive TiO2 increases, thereby making the

switch as a whole resistive. The more negative voltage is applied, the less conductive the cube

becomes.

What makes this switch special—memristive—is that when the voltage is

turned off, positive or negative, the oxygen bubbles do not migrate. They stay where they are,

which means that the boundary between the two titanium dioxide layers is frozen. That is how

the memristor “remembers” how much voltage was last applied.

College of engineering chengannur

Memristor based multilevel memory 6

Resistance also depends on the length of time that voltage has been applied

CROSSBAR ARCHITECTURE: A memristor’s structure, shown here in a scanning tunneling

microscope image, will enable dense, stable computer memories.

Fig 2.2.2

BOW TIES

Leon Chua’s original graph of the hypothetical memristor’s behavior is shown at top right; the

graph of R. Stanley William’s experimental results are shown below. The loops map the

switching behavior of the device: it begins with a high resistance, and as the voltage increases,

the current slowly increases. As charge flows through the device, the resistance drops, and the

current increases more rapidly with increasing voltage until the maximum is reached. Then, as

the voltage decreases, the current decreases but more slowly, because charge is flowing through

the device and the resistance is still dropping. The result is an on-switching loop. When the

voltage turns negative, the resistance of the device increases, resulting in an off-switching loop

College of engineering chengannur

Memristor based multilevel memory 7

Fig 2.2.3

IMPLIMENTATION OF OTHER TYPES OF MEMRISTORS

SPINTRONIC MEMRISTOR

Concept of Spintronic memristor is given as, resistance is caused by the spin of electrons in one

section of the device pointing in a different direction than those in another section, creating a

"domain wall," a boundary between the two states. Electrons flowing into the device have a

certain spin, which alters the magnetization state of the device. Changing the magnetization, in

turn, moves the domain wall and changes the device's resistance.

SPIN TORQUE TRANSFER MAGNETORESISTANCE

College of engineering chengannur

Memristor based multilevel memory 8

Spin Torque Transfer MRAM is a well-known device that exhibits memristive behavior. The

resistance is dependent on the relative spin orientation between two sides of a magnetic tunnel

junction. This in turn can be controlled by the spin torque induced by the current flowing through

the junction. However, the length of time the current flows through the junction determines the

amount of current needed, i.e., the charge flowing through is the key variable.

Additionally, MgO based magnetic tunnel junctions show memristive behavior based on the drift

of oxygen vacancies within the insulating MgO layer (resistive switching). Therefore, the

combination of spin transfer torque and resistive switching leads naturally to a second-order

memristive system with w=(w1,w2) where w1 describes the magnetic state of the magnetic tunnel

junction and w2 denotes the resistive state of the MgO barrier. Note that in this case the change of

w1 is current-controlled (spin torque is due to a high current density) whereas the change of w2 is

voltage-controlled (the drift of oxygen vacancies is due to high electric fields).

POLYMERIC MEMRISTOR

Juri H. Krieger and Stuart M. Spitzer claim to have developed a polymeric memristor before the

titanium dioxide memristor more recently announced.

There work describes the process of dynamic doping of polymer and inorganic dielectric-like

materials in order to improve the switching characteristics and retention required to create

functioning nonvolatile memory cells. Described is the use of a special passive layer between

electrode and active thin films, which enhances the extraction of ions from the electrode. It is

possible to use fast ion conductor as this passive layer, which allows to significantly decreasing

the ionic extraction field

RESONANT TUNNELING DIODE MEMRISTOR

College of engineering chengannur

Memristor based multilevel memory 9

1994, F. A. Buot and A. K. Rajagopal demonstrated that a 'bow-tie' current-voltage (I-V)

characteristics occurs in AlAs/GaAs/AlAs quantum-well diodes containing special doping design

of the spacer layers in the source and drain regions, in agreement with the published

experimental results This 'bow-tie' current-voltage (I-V) characteristic is sine qua non of a

memristor although the term memristor is not explicitly mentioned in their papers. No magnetic

interaction is involved in the analysis of the 'bow-tie' I-V characteristics

3-TERMINAL MEMRISTOR (MEMISTOR)

Although the memristor is defined in terms of a 2-terminal circuit element, there was an

implementation of a 3-terminal device called a memistor developed by Bernard Widrow in 1960.

Memistors formed basic components of a neural network architecture called ADALINE

developed by Widrow and Ted Hoff the memistor was described as follows:

Like the transistor, the memistor is a 3-terminal element. The conductance between two of the

terminals is controlled by the time integral of the current in the third, rather than its instantaneous

value as in the transistor. Reproducible elements have been made which are continuously

variable (thousands of possible analog storage levels), and which typically vary in resistance

from 100 ohms to 1 ohm, and cover this range in about 10 seconds with several mille amperes of

plating current. Adaptation is accomplished by direct current while sensing the neuron logical

structure is accomplished nondestructively by passing alternating currents through the arrays of

memistor cells.

Since the conductance was described as being controlled by the time integral of current as in

Chua's theory of the memristor, the memistor of Widrow may be considered as a form of

memristor having three instead of two terminals. However, one of the main limitations of

Widrow's memistor was that they were made from an electroplating cell rather than as a solid-

state circuit element. Solid-state circuit elements were required to achieve the scalability of the

College of engineering chengannur

Memristor based multilevel memory 10

integrated circuit which was gaining popularity around the same time as the invention of

Widrow's memistor.

2.3 ADVANTAGES

When you turn off the voltage, the memristor remembers its most recent resistance until the

next time you turn it on, whether that happens a day later or a year later

This freezing property suits memristors brilliantly for computer memory. The ability to

indefinitely store resistance values means that a memristor can be used as a nonvolatile memory.

That might not sound like very much, but go ahead and pop the battery out of your laptop, right

now—no saving, no quitting, nothing. You’d lose your work, of course. But if your laptop were

built using a memory based on memristors, when you popped the battery back in, your screen

would return to life with everything exactly as you left it: no lengthy reboot, no half-dozen auto-

recovered files.

There are several advantages of the memristor memory over conventional transistor-based

memories. One is its strikingly small size. Though memristor is still at its early development

stage, its size is at most one tenths of its RAM counterparts. If the fabrication technology for

memristor is improved, the size and advantage could be even more significant. Another feature

of the memristor is its incomparable potential to store analog information which enables the

memristor to keep multiple bits of information in a memory cell. Besides these features, the

memristor is also an ideal device for implementing synaptic weights in artificial neural networks

Williams' solid-state memristors can be combined into devices called crossbar

latches, which could replace transistors in future computers, taking up a much smaller area.

College of engineering chengannur

Memristor based multilevel memory 11

They can also be fashioned into non-volatile solid-state memory, which would allow greater data

density than hard drives with access times potentially similar to DRAM, replacing both

components HP prototyped a crossbar latch memory using the devices that can fit 100 gigabits

in a square centimeter, and has designed a highly scalable 3D design (consisting of up to 1000

layers or 1 petabit in a cubic CM) has reported that its version of the memristor is currently

about one-tenth the speed of DRAM . The devices' resistance would be read with alternating

current so that they do not affect the stored value.

2.4 PROBLEMS

Despite many favorable features, memristors have several weaknesses in practice. One weakness

comes from the nonlinearity in the Ø vs. q curve which makes it difficult to determine the proper

pulse width for achieving a desired resistance value. If the nonlinearity is spatially variant in the

die of a chip which is common in the fabrication process, the difficulty could be very serious.

Another difficulty comes from the property of the memristor which integrates any kind of signals

including noise that appeared at the memristor and results in the memristors being perturbed

from its original pre-set values.

College of engineering chengannur

Memristor based multilevel memory 12

The principle of the memristor is based on the nonlinear property of basic circuit elements. In the

relationships defining basic circuit elements, charge is defined as the time integral of current,

namely,

College of engineering chengannur

Memristor based multilevel memory 13

Thus, the resistance can be interpreted as the slope at an operating point on the Ø- q curve. If the

Ø- q curve is nonlinear, the resistance will vary with the operating point. For instance, if the

Ø - q curve is the nonlinear function

Shown in Fig. 2.4.1, its small-signal resistance can be obtained by re-plotting it as a function of

Øq in the R vs .Ø plane as in Fig. 2.4.2.

Since the flux Ø is obtained by integrating the voltage, the resistance of the memristor can be

Controlled by applying a voltage signal across the memristor, where

Fig 2.4.1

College of engineering chengannur

Memristor based multilevel memory 14

Fig 2.4.2

College of engineering chengannur

Memristor based multilevel memory 15

Fig 2.4.3

The above memristance tuning method assumes an ideal operating condition. In practice, there

are some problems that must be overcome. The first problem is caused by the nonlinearity

between the applied voltage and the corresponding resistance. Suppose the resistance

characteristics of the memristors is different from each other as shown in Fig. 2.4.3, where the

resistance R d is obtained at different values of Ø such as Ø1

Ø2 and Ø3. If the same magnitude of voltage pulses is chosen, then the durations of the pulse

widths for obtaining the same resistance will be different depending on the characteristics of the

memristors.

Another problem comes from the fact that the operating point and its associated memristance

would be changed whenever some voltage is applied across the memristor. The voltage applied

for read-out or even noise voltages would be integrated which causes the flux Ø to be altered.

Again, this causes the programmed resistance to be varied. Chua had suggested applying a

voltage doublet with equal positive and negative read-out pulses to resolve such problem.

However, the problem remains if the positive and the negative pulses are not perfectly identical

due to the non-ideal pulse-generation circuits.

College of engineering chengannur

Memristor based multilevel memory 16

2.5 REFERENCE RESISTANCE ARRAY-BASED MULTILEVEL MEMORY OF

MEMRISTOR

The proposed method has the operating point of the memristor be maintained its desired location

(or resistance value) utilizing a set of pre-determined multiple resistance levels. Fig. 2.5.1 shows

the basic idea of the proposed method, where the resistance array to be referenced and the

memristor to be programmed (tuned) are shown. The goal is to have the memristor keep any of

the resistance level selected from the resistance array. If a predetermined magnitude of the

current pulse Is (t) is applied to the resistance array, different levels of voltages V k will appear at

each node of the resistance array. The same current pulse Is (t ) is also applied to the memristor.

Fig 2.5.1

College of engineering chengannur

Memristor based multilevel memory 17

The programming (tuning) of the memristor is performed by applying additional current pulses

to the memristor with the appropriate directions until the voltage of the memristor equals to that

of the selected node voltage in the resistance array. If the voltage of the memristor reaches that of

the selected node, the resistance value of the memristor becomes the same as the partial sum of

the resistance from the ground to the selected node of the resistance array.

This idea is employed in both the “write-in” and the “read-out/restoration” circuits. Detailed

description of these circuits will be presented in the following sections.

2.6 MEMRISTOR WRITE-IN CIRCUIT

Fig 2.6.1

College of engineering chengannur

Memristor based multilevel memory 18

The memristor write-in circuit is used to bias the memristor at a desired resistance level. The

critical write-in circuit is shown in Fig 2.6.1. The first step is to choose the write-in memristor

and the resistance value to be memorized by turning on one of the switches in switch array S1 of

Fig2.6.1. and the corresponding switch pair in switch array S4 respectively. Then, an initial

current pulse I s(t) is applied at the drain of the transistor Q1 so that its mirrored current pulses

appear at transistors Q2 and Q3. With this current pulse, negative voltages appear at both the

selected reference nodes and at the output terminal V out of the memristors.

Suppose the selected memristance M j is less than the referenced sum of the resistances

Rk sum in Fig2.6.1. In this particular case, Diffk+ is smaller than Diffk- sinceVout (Tp) is less

negative than that of Vk (Tp). These Diffk outputs caused the comparator C1 to generate a

positive pulse. Note that the negative and the positive output terminals of Diffk are linked to the

positive and the negative input terminals of C1 respectively. As a consequence, switch S3 is

turned on. Ø such increased flux Ø, the increment of the memristance can be obtained with a

monotonically increasing function via the R vs. Ø graph in Fig 2.6.1. As a consequence, the

memristor voltage decreases toward the selected reference level.

The processing from the above voltage difference computation repeats until the difference

between Vk (Tp ) and Vout (Tp) becomes zero, thereby completing the “write-in” processing of

the reference resistance Rk sum

On the other hand, when the selected memristance M j is larger than the referenced sum

Rk sum of the resistances, the memristance of the selected memristor is decreased and the

memristor voltage is increased toward the selected reference level through the opposite

procedure mentioned above.

The above comparison between the voltages and the adjustment of the memristance are repeated

until the memristor voltage is equal to its selected reference voltage level.

College of engineering chengannur

Memristor based multilevel memory 19

2.7 MEMRISTOR READ-OUT/RESTORATION CIRCUIT

Fig 2.7.1

The memristor read-out/ restoration circuit is used to read the content of the memristor by

applying an appropriate integrating current or voltage. The critical function of this circuit is to

guarantee the memristor will stay at a set of fixed values without being perturbed when a read-

out voltage or a noise voltage is applied across the memristor. To achieve this goal, a single

compensating pulse is applied to have the memristance changed toward the closest reference

resistance after the initial read-out pulse is applied. The read-out circuit is the same as the write-

in circuit except the negative signal excluding circuit (N_Excld), MIN A and MIN B circuits as

shown in Fig.2.7.1 . The N_Excld is the circuit to choose only the positive signals from Diffk+ or

College of engineering chengannur

Memristor based multilevel memory 20

Diffk- using the negative signal excluding circuit N_Excld by comparing between the DC

voltage and the output of the Diff circuit. The circuits MIN A and MIN B together with the

comparator C1 are used to choose the smallest absolute value among all

Diff k+ and Diffk- signals.

If the output of MIN A is smaller than that of MIN B, the memristor voltage is higher than that

of its closest reference voltage (with M j< Rk sum)

In this case, the memristance M j should be increased. On the other hand, if the output of the

MIN A is larger than that of MIN B, then the memristor voltage is smaller than that of its closest

reference voltage (with M j>Rk sum). In this case, M j should be decreased.

The above adjustment of the memristor is executed only once during each read-out processing.

2.8 SIMULATIONS

The write-in circuit and the read-out/restoration circuit of the proposed method have been

simulated extensively. All circuit components are assumed to be ideal. The simulations aim to

check if the memristors are written accurately with the prescribed resistance levels and if the

memristor contents are adjusted properly when they are altered by noise or read-out voltages.

Also, it focuses on whether the proposed circuits are working well when memristors with slightly

different characteristics are used in practice. All memristors used in this simulation are

mathematical models because physical memristor devices with prescribed .Ø vs Q

Characteristics are not commercially available at the moment.

The first simulation is designed to test the write-in operation of three memristors with slightly

different characteristics. To have this simulation be as close to real experiments as possible,

scientists chose the characteristic curve of the HP memristor and two contrived variations. This

simulation consists of writing a fixed reference resistance of 18 kΩ on the three memristors

which have different Ø-q characteristics. The initial values of the memristors are randomly

selected. Fig. 2.8.1shows the changes in the R- Ø

Values while repeated writing pulses are applied.

The relatively larger movements of the lower points of each characteristic curve are due to the

big difference between the reference resistance and the initial memristance. Note that the

College of engineering chengannur

Memristor based multilevel memory 21

relatively larger movement of the lower points of each compensation pulse width generated by

the pulse width modulator (PWM) is proportional to the difference between the reference

resistance and that of the memristor. Also observe that, depending on its characteristics, different

amounts ΔØ of the flux Ø are required to write and maintain the same resistance level on each

memristor. Despite significant differences in the 3 memristor characteristics, the proposed

method is able to write exactly the same resistance level in all 3 memristors

Fig 2.8.1

College of engineering chengannur

Memristor based multilevel memory 22

Extensive simulations for testing the write-in function for multiple levels have also been made.

The number of levels have chosen to write-in the memristors is 8 and the model of the

memristor used in this simulations is chosen from the HP publication whose resistance ranges

from about 8K Ohm to 25.5 K Ohm. The memristors are allowed to have 8 equally spaced

resistance levels of {8.0, 10.5, 13, 15.5, 18, 20.5, 23, 25.5} K Ohm as in Fig. 2.8.2. Big red dots

are the desired writing levels and the initial resistance values are selected randomly. As shown in

the fig. 2.8.2, all memristor converge successfully to their desired values during repeated

applications of the write-in pulses to 20 memristor models.

Fig 2.8.2

College of engineering chengannur

Memristor based multilevel memory 23

Similar simulations have been made for the read-out/restoration circuit. The goal of this circuit is

to have the memristors to stay at fixed values without being perturbed when a read-out voltage or

any noise voltage is applied across the memristor by applying a single compensating pulse after

the initial read-out pulse. Extensive simulations on 8 memristors with 8 slightly different

characteristics have been made. The memristors are perturbed initially by a maximum of 10%

from their reference resistances. Fig. 2.8.3 shows traces of the resistance on the R-Ø curve of a

typical memristor. The big red dots are the desired levels and the small cross symbols are the

traces of the resistance changes while the read-out/restoration operation is performed. Note that a

single compensation pulse is generated during each read-out processing. Observe that the

resistance values in Fig. 2.8.3 converge to their closest levels with the read-out pulses.

Fig 2.8.3

College of engineering chengannur

Memristor based multilevel memory 24

3. FUTURE SCOPE

Combined with transistors in a hybrid chip, memristors could radically improve the

performance of digital circuits without shrinking transistors. Using transistors more efficiently

could in turn give us another decade, at least, of Moore’s Law performance improvement,

without requiring the costly and increasingly difficult doublings of transistor density on chips. In

the end, memristors might even become the cornerstone of new analog circuits that compute

using an architecture much like that of the brain. Memristor’s potential goes far beyond instant-

on computers to embrace one of the grandest technology challenges: mimicking the functions of

a brain. Within a decade, memristors could let us emulate, instead of merely simulate, networks

of neurons and synapses. Many research groups have been working toward a brain in silico:

IBM’s Blue Brain project, Howard Hughes Medical Institute’s Janelia Farm, and Harvard’s

Center for Brain Science are just three. However, even a mouse brain simulation in real time

involves solving an astronomical number of coupled partial differential equations. A digital com-

puter capable of coping with this staggering workload would need to be the size of a small city,

and powering it would require several dedicated nuclear power plants.

Memristors can be made extremely small, and they function like synapses. Using them, we will

be able to build analog electronic circuits that could fit in a shoebox and function according to

the same physical principles as a brain. Memristors can potentially learn like synapses and be

used to build human brain-like computers

Two CMOS circuits connected by a memristor is analogous to two neurons in the brain

connected by a synapse. It is thought that synaptic connections strengthen as the neurons either

side fire and so brain 'circuits' are established which constitutes the basis of human learning.

Wei Lu, a University of Michigan scientist connected two CMOS circuits by a silver and silicon

Memristor and powered the two CMOS circuits on and off with varying time gaps between them.

College of engineering chengannur

Memristor based multilevel memory 25

The memristor alters its state differently depending on the timing of the powering of the CMOS

circuits.

This is said to be the same behavior as that shown by synapses, called "spike timing plastic

dependency", which is thought to be the possible basis for memory and learning in human and

other mammalian brains.

The synaptic connection between neurons becomes stronger or weaker, as the time gap between

when they are stimulated becomes shorter or longer. In the same way, the shorter the time

interval the lower the resistance of the memristor to electricity flowing across it between the two

CMOS circuits.

A 20 millisecond time interval between the two CMOS circuits caused a resistance level roughly

half that of a 40 millisecond gap. Lu said: "Cells that fire together wire together... The memristor

mimics synaptic action.

"We show that we can use voltage timing to gradually increase or decrease the electrical

conductance in this memristor-based system. In our brains, similar changes in synapse

conductance essentially give rise to long term memory.

A hybrid circuit—containing many connected memristors and transistors—could help us

research actual brain function and disorders. Such a circuit might even lead to machines that can

recognize patterns the way humans can, in those critical ways computers can’t—for example,

picking a particular face out of a crowd even if it has changed significantly since our last

memory of it.

College of engineering chengannur

Memristor based multilevel memory 26

There are several advantages of the memristor memory over conventional transistor-based

memories. One is its strikingly small size. Though memristor is still at its early development

stage, its size is at most one tenths of its RAM counterparts. If the fabrication technology for

memristor is improved, the size and advantage could be even more significant. Another feature

of the memristor is its incomparable potential to store analog information which enables the

memristor to keep multiple bits of information in a memory cell, Besides these features, the

memristor is also an ideal device for implementing synaptic weights in artificial neural networks.

HP already has plans to implement memristors in a new type of non-volatile memory which

could eventually replace flash and other memory systems.

Recently, a simple electronic circuit consisting of an LC network and a memristor was

used to model experiments on adaptive behavior of unicellular organisms. It was shown that the

electronic circuit subjected to a train of periodic pulses learns and anticipates the next pulse to

come, similarly to the behavior of slime molds Physarumpolycephalum subjected to periodic

changes of environment. Such a learning circuit may find applications, e.g., in pattern recognition

4. CONCLUSION

The reference resistance array-based multilevel memristor memory is proposed in this paper. The

idea has been implemented with two circuits namely the write-in and the read-out circuits.

Simulation of the write-in circuit shows that the memristors memorize the desired discrete

resistance levels regardless of their characteristic differences. In read-out simulation, contents of

the memristors move toward their original values from the deviated ones whenever the read-out

processing is performed.

The proposed multilevel idea of the memristor together with its intrinsic feature of small size

would make the memristor to be a powerful memory device. Also, if the number of multilevel of

College of engineering chengannur

Memristor based multilevel memory 27

memory is increased, the memristor could be an ideal element for synaptic weight

implementation since the synaptic multiplication can be performed simply by Ohm’s law V=IR

in the memristor.

Memristor is the fourth fundamental component the arrangement of

few fundamental circuit components form the basis of almost all of the electronic devices we use

in our everyday life. Thus the discovery of a brand new fundamental circuit element is something

not to be taken lightly and has the potential to open the door to a brand new type of electronics.

HP already has plans to implement memristors in a new type of non-volatile memory which

could eventually replace flash and other memory systems

College of engineering chengannur

Memristor based multilevel memory 28

5. REFERENCES

[1] Hyongsuk Kim Sah, M.P. Changju Yang Chua, L.O.”Memristor based multilevel

memory” Cellular Nanoscale Networks and Their Applications (CNNA), 2010 12th

International Workshop, 3-5 Feb. 2010, pp1-6

[2] R. Stanley Williams “How we found the Missing Memristor” Spectrum, IEEE,

Volume: 45, Issue: 12, Dec 2008, pp 28-35

[3] Memristor-From Wikipedia, www.wikipedia.org

College of engineering chengannur

S-ar putea să vă placă și

- Electrical QuestionsDocument32 paginiElectrical Questionselec310Încă nu există evaluări

- Zick AnalysisDocument12 paginiZick AnalysisrksahayÎncă nu există evaluări

- Complete Electronics Self-Teaching Guide with ProjectsDe la EverandComplete Electronics Self-Teaching Guide with ProjectsEvaluare: 3 din 5 stele3/5 (2)

- Circuit Breaker Types & Working PrinciplesDocument42 paginiCircuit Breaker Types & Working PrinciplesVikas GuptaÎncă nu există evaluări

- John Titor TIME MACHINEDocument21 paginiJohn Titor TIME MACHINEKevin Carey100% (1)

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1De la EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Încă nu există evaluări

- MemristorDocument18 paginiMemristorNaveed BashirÎncă nu există evaluări

- Introduction To Automotive NVHDocument80 paginiIntroduction To Automotive NVHAmit PatilÎncă nu există evaluări

- Kinetics of a Particle: Impulse & MomentumDocument40 paginiKinetics of a Particle: Impulse & MomentumZeeshan HaiderÎncă nu există evaluări

- Theory of Static Winding Circuit AnalysisDocument13 paginiTheory of Static Winding Circuit AnalysisHoang Thanh VanÎncă nu există evaluări

- Ohms LawDocument25 paginiOhms LawLui PorrasÎncă nu există evaluări

- Aim of Experiment: Basic Principle of Bourdon Tube Pressure GaugeDocument2 paginiAim of Experiment: Basic Principle of Bourdon Tube Pressure GaugePunit SurinÎncă nu există evaluări

- Isaac NewtonDocument10 paginiIsaac NewtonJustine Lisette PedrajasÎncă nu există evaluări

- Power Transformer Tests Guide - Voltage Ratio, Turns Ratio, Polarity Vector GroupDocument7 paginiPower Transformer Tests Guide - Voltage Ratio, Turns Ratio, Polarity Vector GroupsupermannonÎncă nu există evaluări

- Basic Introduction To Single Electron TransistorDocument5 paginiBasic Introduction To Single Electron TransistorIJRASETPublicationsÎncă nu există evaluări

- Hypersonic Aerothermoelastic Studies For Reusable Launch VehiclesDocument35 paginiHypersonic Aerothermoelastic Studies For Reusable Launch Vehiclesgalaxy_hypeÎncă nu există evaluări

- Memristor DocumentationDocument33 paginiMemristor Documentationsyviswanath100% (8)

- Problem StatementDocument11 paginiProblem StatementprathameshÎncă nu există evaluări

- p240 MemristorDocument5 paginip240 MemristorGopi ChannagiriÎncă nu există evaluări

- Definition:: By: Arjun C MemristorDocument19 paginiDefinition:: By: Arjun C Memristorrakshith_kr_1Încă nu există evaluări

- Design of Memristor: A Paper Presentation OnDocument12 paginiDesign of Memristor: A Paper Presentation Onnightking_1Încă nu există evaluări

- Motor Circuit Analysis Concept and PrincipleDocument13 paginiMotor Circuit Analysis Concept and Principleclide_050793Încă nu există evaluări

- 191ee721 - Unit-1 To 5 QBDocument9 pagini191ee721 - Unit-1 To 5 QBPoorani MahesÎncă nu există evaluări

- The Impact of The Different Voltages and Frequencies On Resistivity of The Tio - Based Memristors With 3D Observation in MatlabDocument5 paginiThe Impact of The Different Voltages and Frequencies On Resistivity of The Tio - Based Memristors With 3D Observation in MatlabJules FossiÎncă nu există evaluări

- MemoristerDocument9 paginiMemoristerkmt340Încă nu există evaluări

- MemristorDocument12 paginiMemristorkrish2601scribdÎncă nu există evaluări

- Single Electron Transistor: Our World Is Without Doubt Built On The Power of The Transistor, A Microscopic ElectronicDocument6 paginiSingle Electron Transistor: Our World Is Without Doubt Built On The Power of The Transistor, A Microscopic ElectronicLily SharmaÎncă nu există evaluări

- A Seminar ReportDocument30 paginiA Seminar ReportSanthanu Surendran100% (1)

- HSpice Model Design for Dual-Doped MemristorDocument6 paginiHSpice Model Design for Dual-Doped MemristorAshish JainÎncă nu există evaluări

- Welding: A. Arslan KAYA, Prof. Dr. Anadolu University and Muğla UniversityDocument58 paginiWelding: A. Arslan KAYA, Prof. Dr. Anadolu University and Muğla UniversityŞafakk CanıberkkÎncă nu există evaluări

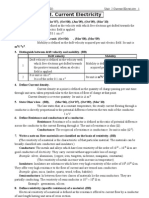

- I DQ DT: Topic 1: Basic Concepts 1.0 CurrentDocument11 paginiI DQ DT: Topic 1: Basic Concepts 1.0 Currentkumares_nfbmÎncă nu există evaluări

- Why Ac DC TransformersDocument21 paginiWhy Ac DC Transformersapi-252130436Încă nu există evaluări

- Transmission LinesDocument51 paginiTransmission LinesBobeth TubigÎncă nu există evaluări

- LC Circuit ExplorationDocument3 paginiLC Circuit ExplorationNorlyn RunesÎncă nu există evaluări

- Current Electricity ConceptsDocument14 paginiCurrent Electricity ConceptsJoseph HenryÎncă nu există evaluări

- 12 Phy em 3mark Unit 2Document7 pagini12 Phy em 3mark Unit 2physicspalanichamyÎncă nu există evaluări

- Circuit BreakersDocument19 paginiCircuit BreakersOsama SalemÎncă nu există evaluări

- Familiarization of The Electrical Machine Laboratory ApparatusDocument5 paginiFamiliarization of The Electrical Machine Laboratory ApparatusRosalinda CondeÎncă nu există evaluări

- Basic Electricity Lesson 02Document17 paginiBasic Electricity Lesson 02Sandra Barnett CrossanÎncă nu există evaluări

- Ee00 PPPDocument203 paginiEe00 PPPlunalight253Încă nu există evaluări

- Single Electron TransistorDocument7 paginiSingle Electron Transistorimcoolsha999Încă nu există evaluări

- XXL, Oct 2011Document5 paginiXXL, Oct 2011emediageÎncă nu există evaluări

- Chapter 26 Current and ResistanceDocument26 paginiChapter 26 Current and ResistanceUnknown PersonÎncă nu există evaluări

- (Q) Discuss in Detail Working Principle of Chemical SensorsDocument9 pagini(Q) Discuss in Detail Working Principle of Chemical SensorsShalan KosékarÎncă nu există evaluări

- Memristor PPT FinalDocument23 paginiMemristor PPT FinalIndraprakas KnÎncă nu există evaluări

- Assignment 5Document14 paginiAssignment 5Arnon PukhrambamÎncă nu există evaluări

- ElectromagnetsDocument51 paginiElectromagnetsRoanne Mae MañalacÎncă nu există evaluări

- Magnetic Flux: ' Between The Terminals Is A Function of The Amount of Electric Charge Q' That Has PassedDocument27 paginiMagnetic Flux: ' Between The Terminals Is A Function of The Amount of Electric Charge Q' That Has PassedravitejapotuÎncă nu există evaluări

- MemristorDocument30 paginiMemristorjoseph458Încă nu există evaluări

- Ese Ed QP Answer KeyDocument40 paginiEse Ed QP Answer Keyசெல்வம் முத்துராமன்Încă nu există evaluări

- Single Electron TransistorDocument11 paginiSingle Electron TransistorHarsha VardhanÎncă nu există evaluări

- MT 2Document77 paginiMT 2safeer ahmadÎncă nu există evaluări

- Basic ElectronicsDocument47 paginiBasic ElectronicsPolyn LopezÎncă nu există evaluări

- L7 Unit 1 Electrical TechnologyDocument4 paginiL7 Unit 1 Electrical TechnologyDr G VijayakumarÎncă nu există evaluări

- Chapter-3 Current ElectricityDocument39 paginiChapter-3 Current ElectricityjeevendraÎncă nu există evaluări

- Midterm AssignmentDocument7 paginiMidterm AssignmentEzekiel BrizuelaÎncă nu există evaluări

- BacksTab 03Document155 paginiBacksTab 03VaishnaviRaviÎncă nu există evaluări

- 2Document83 pagini2Kalyan Reddy AnuguÎncă nu există evaluări

- Mechanical Forces and Magnetic Field Simulation of Transformer With Finite Element MethodDocument4 paginiMechanical Forces and Magnetic Field Simulation of Transformer With Finite Element MethodSarojakanti SahooÎncă nu există evaluări

- Basic ElectricityDocument19 paginiBasic ElectricityTerfaia NadjatÎncă nu există evaluări

- Single Electron Tansistor: Introduction To Nanoscience and Nano Technology ECE1006Document23 paginiSingle Electron Tansistor: Introduction To Nanoscience and Nano Technology ECE1006lahari jagarlamudiÎncă nu există evaluări

- EE 421 Module 2Document42 paginiEE 421 Module 2Eirish Chrystelle EsmasÎncă nu există evaluări

- Single Electron Tunneling and Coulomb BlockadeDocument76 paginiSingle Electron Tunneling and Coulomb BlockadePrashant KumarÎncă nu există evaluări

- E3 Electric Current !: ObjectivesDocument14 paginiE3 Electric Current !: Objectivesostojic007Încă nu există evaluări

- Ch.12 ElectricityDocument19 paginiCh.12 Electricityshraddha2572sharmaÎncă nu există evaluări

- Phy 1206Document5 paginiPhy 1206Sujan ReddyÎncă nu există evaluări

- CFD Simulation of A Co-Current Spray Dryer: February 2010Document7 paginiCFD Simulation of A Co-Current Spray Dryer: February 2010muhammad farisÎncă nu există evaluări

- Properties of Fluids: Sample Problems BDocument4 paginiProperties of Fluids: Sample Problems BFronda Jerome BlasÎncă nu există evaluări

- FBD StaticDocument5 paginiFBD StaticBrianChanÎncă nu există evaluări

- Mechanics of FluidsDocument64 paginiMechanics of FluidsShiva U100% (2)

- التجربة الثانية الانكسارDocument3 paginiالتجربة الثانية الانكسارAymen AbdulrahmanÎncă nu există evaluări

- Study of Lateral Load Carrying Capacities of Piles in Layered Soils Using PLAXIS 3DDocument6 paginiStudy of Lateral Load Carrying Capacities of Piles in Layered Soils Using PLAXIS 3Dneerad mohan100% (1)

- Olympiad MotionDocument11 paginiOlympiad MotionKrishna SharmaÎncă nu există evaluări

- Nuclear and Particle Physics Lectures SumnerDocument41 paginiNuclear and Particle Physics Lectures SumneranticiÎncă nu există evaluări

- Design of Small Antennas Based On DNG MetamaterialsDocument4 paginiDesign of Small Antennas Based On DNG MetamaterialsSumaiya AbedinÎncă nu există evaluări

- Mil STD 464aDocument121 paginiMil STD 464amuriel_reperant5867Încă nu există evaluări

- GEC Elective 1 Environmental Science Study GuideDocument3 paginiGEC Elective 1 Environmental Science Study GuideNorlijun HilutinÎncă nu există evaluări

- Thermodynamics 1 Basic Principles, Concepts and DefinitionDocument8 paginiThermodynamics 1 Basic Principles, Concepts and DefinitionHENRICK IGLEÎncă nu există evaluări

- Pumping MechanismsDocument10 paginiPumping MechanismsfuggaÎncă nu există evaluări

- Eyring Equation ExplainedDocument5 paginiEyring Equation ExplainedBeaaaaÎncă nu există evaluări

- Techno-Economic Analysis of Air Humidification DesalinationDocument5 paginiTechno-Economic Analysis of Air Humidification DesalinationIbrahim Al-MutazÎncă nu există evaluări

- Ucd: Physics 9C - Electricity and Magnetism: Tom WeidemanDocument173 paginiUcd: Physics 9C - Electricity and Magnetism: Tom WeidemanEuler Portilla CarrascoÎncă nu există evaluări

- Effect of Casting Speed On Continuous Casting of Steel Slab: January 2014Document12 paginiEffect of Casting Speed On Continuous Casting of Steel Slab: January 2014Prakash SarangiÎncă nu există evaluări

- Rumus CCI 4737Document5 paginiRumus CCI 4737Eko NbsÎncă nu există evaluări

- Physics XII CH 8 Physics Assertion Reasoning Electromagnetic WavesDocument4 paginiPhysics XII CH 8 Physics Assertion Reasoning Electromagnetic WavesNjan KL16么PorottaÎncă nu există evaluări

- IB Chemistry - SL Topic 2 Questions 1. Species Number of Protons Number of Neutrons Number of ElectronsDocument19 paginiIB Chemistry - SL Topic 2 Questions 1. Species Number of Protons Number of Neutrons Number of Electronsyasmine hooeyÎncă nu există evaluări

- Engg. Physic-I 2076 To 2079 ..Document62 paginiEngg. Physic-I 2076 To 2079 ..upendrapaudel0Încă nu există evaluări