Documente Academic

Documente Profesional

Documente Cultură

802 11

Încărcat de

Leão AmaruDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

802 11

Încărcat de

Leão AmaruDrepturi de autor:

Formate disponibile

Institute of Physics Publishing doi:10.

1088/1742-6596/10/1/088

Journal of Physics: Conference Series 10 (2005) 361364 Second Conference on Microelectronics, Microsystems and Nanotechnology

FPGA implementation cost and performance evaluation of IEEE 802.11 protocol encryption security schemes

N Sklavos, G Selimis and O Koufopavlou Electrical and Computer Engineering Department, University of Patras, Patras, Greece E-mail: nsklavos@ee.upatras.gr

Abstract. The explosive growth of internet and consumer demand for mobility has fuelled the exponential growth of wireless communications and networks. Mobile users want access to services and information, from both internet and personal devices, from a range of locations without the use of a cable medium. IEEE 802.11 is one of the most widely used wireless standards of our days. The amount of access and mobility into wireless networks requires a security infrastructure that protects communication within that network. The security of this protocol is based on the Wired Equivalent Privacy (WEP) scheme. Currently, all the IEEE 802.11 market products support WEP. But recently, the 802.11i working group introduced the Advanced Encryption Standard (AES), as the security scheme for the future IEEE 802.11 applications. In this paper, the hardware integrations of WEP and AES are studied. A Field Programmable Gate Array (FPGA) device has been used as the hardware implementation platform, for a fair comparison between the two security schemes. Measurements for the FPGA implementation cost, operating frequency, power consumption and performance are given.

1. Introduction IEEE 802 standards committee formed the 802.11 Wireless Local Area Networks (WLAN) Standards Working Group in 1990 [1]. IEEE 802.11 standard does not provide technology or implementation, but introduces the specifications for the physical and the Media Access Control (MAC) layers. 802.11 is the wireless protocol for both ad-hoc and client/server networks. The users acceptance of this protocol is high. Although, the security of the transmission channel is a matter of special attention that always has to be considered [2]. The Wired Equivalent Privacy (WEP) scheme has been adopted by IEEE 802.11 standard to ensure security for the transmitted information [1-2]. The basic two components of WEP are: the Pseudorandom Number Generator (PRNG) and the Integrity Algorithm. The PRNG is the most valuable component because it actually is the original encryption core. WEP adopts RC4 cipher as the PRNG unit and Cyclic Redundancy Check (CRC-32) as the Integrity Algorithm. Although WEP is a good security scheme, the offered security in some cases can not satisfy the user demands [3]. In order a higher security level to be ensured [4], 802.11i working group introduced, as protocol's security scheme, the Advanced Encryption Standard (AES) [5]. This paper presents the hardware implementation cost of both WEP and AES schemes. In order to have a fair and detailed comparison between the two schemes, the same implementation platform has been used (i.e.

2005 IOP Publishing Ltd

361

362

the same Field Programmable Gate Array (FPGA) device). For the AES scheme, a compact VLSI architecture is presented. The implementation of this architecture minimizes the allocated area resources. The area-optimized design does not sacrifice the system performance in a restricted way. The throughput of the design is much higher than the required by the IEEE 802.11 standard [6]. Both WEP and AES schemes are compared in terms of implementation performance: allocated area resources, operating frequency, throughput and power consumption. Aspects of the supported security of these encryption schemes are discussed and security level strength comparisons are given. 2. IEEE 802.11 & Wired Equivalent Privacy (WEP) The proposed architecture for the implementation of the Wired Equivalent Privacy (WEP) scheme, is illustrated in Figure 1.

WEP PRNG (RC4) Address Bus (8-bit)

Key Expansion Unit Modulo Adder Control Data Bus (8-bit) Key Generation S-BOX

Control Unit

RAM Blocks

Control Unit Key 128-bit

Control Data Bus (32-bit)

Plaintext 128-bit Transformation Round (128-bit XOR Blocks)

Ciphertext 128-bit

Integrity Algorithm (CRC-32)

In(32) X^32 X^31 In(31) In(4) In(3) X^2 In(2) X^1 In(1) X^0

F/F 32

F/F 31

... ...

X^3

F/F 4

F/F 3

F/F 2

F/F 1

Input Bit

Out(32)

Out(31)

Out(4)

Out(3)

Out(2)

Out(1)

Figure 1. Wired Equivalent Privacy (WEP) Scheme Architecture In order to implement in hardware the Cyclic Redundancy Check (CRC-32), a shift register of 32 Flip-Flops (F/Fs) and a number of XOR gates are used. So, a Linear Feedback Shift Register (LFSR) design is produced by using the F/Fs chain with the XOR gates. The characteristic polynomial of this LFSR is: (X) = X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X+1 The presence/absence of an XOR gate in CRC-32 architecture corresponds to the presence/absence of a term in G(X) polynomial. The required output message is the content of the LFSR after the input message last bit is sampled. RC4 is a variable key-size stream cipher and operates on one plaintext block at a time. RC4 architecture consists of the Key Expansion Unit and the Transformation Round. The Key Expansion Unit is mainly a S-Box component. For the S-BOX implementation a 256-byte RAM memory block is used and another similar memory block is needed for the key array. The Transformation Round is a simple bit-by-bit XOR between the plaintext and the key.

363

3. IEEE 802.111 & Advanced Encryption Standard (AES) AES proposed architecture operates in Counter Mode with Cipher Block ChainingMessage Authentication Code (CCMP) [5]. According to IEEE 802.11i working group, this operation mode is used to ensure, at the same time, integrity and privacy. The proposed AES architecture is shown in Figure 2:

128

Plaintext

128

Initial Key

INITIAL-KEY REGISTER

INITIAL ROUND

32

Input Column

Control Signals

128

Basic Block Transformation Column

S-Box CONTROL UNIT DATA SHIFT MIX COLUMN

KEY EXPANSION UNIT

32

KEY ADDITION

32

Column Key

Transformed Column OUTPUT REGISTER

128

Ciphertext

Figure 2. Encryption (AES) Architecture.

Advanced Standard Scheme

The AES scheme architecture operates each time on a column of 32-bit data. It needs 41 clock cycles to complete the transformation of a 128-bit plaintext block. The column subunit is composed of 4 basic building blocks: S-Box, DataShift, MixColumn and KeyAddition. The RAM based design for the S-BOXes ([256x8]-bit) guarantees high performance. This "column" based architecture, minimizes the area resources compared with "State" based architectures [7, 8]. 4. Implementation Cost and Performance Evaluation In Figure 4, the synthesis results for both WEP and AES implementations are illustrated. For the hardware integration the FPGA device Xilinx Virtex (2V250fg256) has been used. For power consumption estimation, the Xilinx tool provided in [9] was used. Energy optimized methods could be applied to the above described architectures, similar to those used in WTLS security [10] of WAP [11].

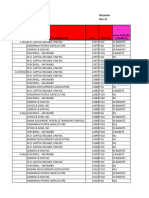

800 700 600 500 400 300 200 100 0 F (MHz) AREA (CLBs) POWER (uW) 40 57 323 325 213 750 WEP AES

Figure 3. Implementations Comparisons

364

Based on the synthesis results regarding the area resources the utilization of both implementations are: AES, 323 CLBs (allocated) + 1213 CLBs (unused) = 1526 CLBs (available in the FPGA device), and for WEP, 750 CLBs (allocated) + 776 CLBs (unused) = 1526 CLBs (available in the FPGA device). The AES implementation performs better compared with WEP implementation. The minimized area resources of AES, do not sacrifice the system performance, which reaches throughput value 177 Mbps. This data rate is much higher compared with the highest specified by IEEE 802.11 [6] throughput of 11 Mbps. On the other hand, RC4 is a more "heavy" design for mobile devices hardware implementation. This is due to the specified S-Boxes and the Key Expansion Unit specifications. RC4 performance is the bottleneck for WEP throughput which reaches the value of 2.22 Mbps. The main RC4 implementation disadvantages, compared with AES are: 1) more required silicon area resources 2) higher power consumption and 3) lower operating frequency. Compared with [7] and [8] proposed AES implementation allocates less area than [7], [8], with higher operation frequency than [8]. The reached throughput values of [7] and [8] are better compared with the proposed implementation. Since the works of [7] and [8] do not present any power consumption results such a comparison with the presented work is not efficient. Concluding and based on the above comparison results, the proposed AES implementation is proposed for applications with special needs in both area resources and operation frequency. Concerning security aspects AES offers, at the same time, privacy and integrity. On the contrary, WEP scheme needs two different algorithms, in order to support bulk encryption and data integrity. In some cases, where AES security is unbreakable, WEP security could be broken. These comparisons give AES advantages and make it an efficient and trustworthy solution for the next years IEEE 802.11 networks. 5. References [1] IEEE Standards Board 2003 802 Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications [2] Sklavos N, and Koufopavlou O 2003 Mobile Communications World: Security Implementations Aspects-A State of the Art CSJM Journal, Institute of Mathematics and Computer Science 11 No 2 [3] Borisov N, Goldberg I and Wagner D 2001 Intercepting Mobile Communications: The Insecurity of 802.11 Proc. of 7th Annual International Conference on Mobile Computing and Networking (July 16-21) [4] Undercoffer J, Perich F, Cedilnik A., Kagal L and Joshi A 2003 A Secure Infrastructure for Service Discovery and Access in Pervasive Computing Journal of Mobile Networks and Applications 8 113-125 Kluwer Academic Publishers [5] Advanced Encryption Standard, (AES) 2003 http://www.nist.gov/aes [6] Xiao Y and Rosdahl J 2002 Throughput and Delay Limits of IEEE 802.11 IEEE Communications Letters 6 No 8 [7] Zhang X and Parhi K 2002 Implementation Approaches for the Advanced Encryption Standard Algorithm IEEE CAS 2 No 4 [8] Sklavos N and Koufopavlou O 2002 Architectures and VLSI Implementations of the AES-Proposal Rijndael", IEEE Transactions on Computers 51 Issue 12 pp 1454-1459 [9] Xilinx Inc., San Jose, California 2003 Virtex, 2.5 V Field Programmable Gate Arrays, & A simple method of estimating power in XC40000X1/EX/E FPGAs Application Brief XBRF 014 v1.0, www.xilinx.com [10] Karri R and Mishra P 2003, Optimizing the Energy Consumed by Secure Wireless Sessions-Wireless Transport Layer Security, Journal of Mobile Networks and Applications 8, 177-185, Kluwer Academic Publishers [11] Hwang G J, Tseng J C R, and Huang Y S 2002 I-WAP: An Intelligent WAP Site Management System, IEEE Transactions On Mobile Computing 1 No 2

S-ar putea să vă placă și

- Fiber Optic System Power Loss Calculator: AssumptionsDocument1 paginăFiber Optic System Power Loss Calculator: AssumptionsLeão AmaruÎncă nu există evaluări

- KHOMAX - CTO-08.16C-LE - FTTX DELTA BOXDocument1 paginăKHOMAX - CTO-08.16C-LE - FTTX DELTA BOXLeão AmaruÎncă nu există evaluări

- Lesson 13Document8 paginiLesson 13Leão AmaruÎncă nu există evaluări

- Models - Woptics.mach Zehnder ModulatorDocument58 paginiModels - Woptics.mach Zehnder ModulatorLeão AmaruÎncă nu există evaluări

- PLC Group PLC Tube Mini Splitter for Telecom, LAN, CATV ApplicationsDocument1 paginăPLC Group PLC Tube Mini Splitter for Telecom, LAN, CATV ApplicationsLeão AmaruÎncă nu există evaluări

- Toney Paper PDFDocument7 paginiToney Paper PDFLeão AmaruÎncă nu există evaluări

- 전자기RF 모델링 교육 v5.0.0 PDFDocument93 pagini전자기RF 모델링 교육 v5.0.0 PDFLeão AmaruÎncă nu există evaluări

- 전자기RF 모델링 교육 v5.0.0 PDFDocument93 pagini전자기RF 모델링 교육 v5.0.0 PDFLeão AmaruÎncă nu există evaluări

- Lesson 13Document8 paginiLesson 13Leão AmaruÎncă nu există evaluări

- Lesson 1 - General Business English - Cambly ContentDocument7 paginiLesson 1 - General Business English - Cambly ContentLeão AmaruÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (119)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Unified Modeling Language Class Diagram ..Uml)Document20 paginiUnified Modeling Language Class Diagram ..Uml)Yasmeen AltuwatiÎncă nu există evaluări

- Answer Any Three of The Following Questions: Madanapalle Institute of Technology & Science MadanapalleDocument1 paginăAnswer Any Three of The Following Questions: Madanapalle Institute of Technology & Science MadanapallePraveen KumarÎncă nu există evaluări

- Matrix Structural Analysis of BeamsDocument28 paginiMatrix Structural Analysis of BeamsKristine May Maturan0% (1)

- Tools - For - Problem - Solving (Appendix B), R.K. Malik's Newton Classes PDFDocument48 paginiTools - For - Problem - Solving (Appendix B), R.K. Malik's Newton Classes PDFMoindavis DavisÎncă nu există evaluări

- AC Assingment 2Document3 paginiAC Assingment 2Levi Deo BatuigasÎncă nu există evaluări

- Preparation of Gases in LaboratoryDocument7 paginiPreparation of Gases in LaboratoryChu Wai Seng50% (2)

- Sling PsychrometerDocument8 paginiSling PsychrometerPavaniÎncă nu există evaluări

- Differential Analysis of Fluid FlowDocument42 paginiDifferential Analysis of Fluid FlowAmr Faisal RaghebÎncă nu există evaluări

- Nov. AbwDocument50 paginiNov. Abwjbyarkpawolo70Încă nu există evaluări

- SteganographyDocument13 paginiSteganographyIgloo JainÎncă nu există evaluări

- A Git Cheat Sheet (Git Command Reference) - A Git Cheat Sheet and Command ReferenceDocument14 paginiA Git Cheat Sheet (Git Command Reference) - A Git Cheat Sheet and Command ReferenceMohd AzahariÎncă nu există evaluări

- Second Mid Term CE 461: Structural Analysis II: Student Name: Student No.: Section: 9 10 11 12Document4 paginiSecond Mid Term CE 461: Structural Analysis II: Student Name: Student No.: Section: 9 10 11 12David Olorato NgwakoÎncă nu există evaluări

- Clone Steps RmanDocument10 paginiClone Steps RmanKishore AdikarÎncă nu există evaluări

- Matrix Inversion Note in Mathematics MagazineDocument2 paginiMatrix Inversion Note in Mathematics Magazinejuan carlos molano toroÎncă nu există evaluări

- 124C1ADocument4 pagini124C1AParthiban DevendiranÎncă nu există evaluări

- OMC 140 Operator Manual v1.08Document38 paginiOMC 140 Operator Manual v1.08Anderson DuarteÎncă nu există evaluări

- Wojciech Gryc - Neural Network Predictions of Stock Price FluctuationsDocument44 paginiWojciech Gryc - Neural Network Predictions of Stock Price FluctuationsjohnsmithxxÎncă nu există evaluări

- Math10 Week3Day4 Polynomial-EqnsDocument44 paginiMath10 Week3Day4 Polynomial-EqnsMark Cañete PunongbayanÎncă nu există evaluări

- Mbs Public School: Topic: Study The Presence of Oxalate Ions in Guava Fruit at Different Stages of RipeningDocument15 paginiMbs Public School: Topic: Study The Presence of Oxalate Ions in Guava Fruit at Different Stages of RipeningSwaraj Patel100% (1)

- Prepare and Interpret Technical DrawingDocument5 paginiPrepare and Interpret Technical DrawingDwin Rosco75% (4)

- IOP Conference Series: Materials Science and EngineeringDocument9 paginiIOP Conference Series: Materials Science and EngineeringMahesh MÎncă nu există evaluări

- QR Code Attendance Monitoring SystemDocument6 paginiQR Code Attendance Monitoring Systemjenny adlaoÎncă nu există evaluări

- Effect of Temperature on Chemical ReactionDocument8 paginiEffect of Temperature on Chemical ReactionnajihahÎncă nu există evaluări

- Welcome: Bahasa Inggris Teknik I Ahmad Nusi, S. PD., M. PDDocument11 paginiWelcome: Bahasa Inggris Teknik I Ahmad Nusi, S. PD., M. PDAsril SalongÎncă nu există evaluări

- Essay For Villa Savoye AbstractDocument1 paginăEssay For Villa Savoye AbstractFrancis PohÎncă nu există evaluări

- Is 4410 9 1982 PDFDocument25 paginiIs 4410 9 1982 PDFSameer Singh PatelÎncă nu există evaluări

- Cics Class 05Document18 paginiCics Class 05HarithaÎncă nu există evaluări

- CFA Level II 3 Topics - High Yield List of QuestionsDocument4 paginiCFA Level II 3 Topics - High Yield List of QuestionsCatalinÎncă nu există evaluări

- It Tigear2Document2 paginiIt Tigear2rrobles011Încă nu există evaluări

- Heat Combustion Laboratory ReportDocument8 paginiHeat Combustion Laboratory ReportSteven Lee100% (1)