Documente Academic

Documente Profesional

Documente Cultură

ch5 Sol

Încărcat de

blue_fire_englandDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

ch5 Sol

Încărcat de

blue_fire_englandDrepturi de autor:

Formate disponibile

Question 5-1) Number of words = 256K words = 28*210 words Number of bits pre each word = 32 bit = 25 bit

Number of registers = 64 bit = 26 Register a) operation code = 7 bits, register code = 6 bits, address part = 18 bits b) the instruction word format is as follows: I Operation Register Address part code part 31 30 24 23 18 17 c) data inputs= 32 bits, address inputs=18 bits

Question 5-2) Direct Address Instruction has its operand address specified directly in the instruction, but the Indirect Address Instruction has the address of the operands address, i.e. not directly the address of the operand. Direct Address Instruction: needs 2 visits to memory. The 1st one is to fetch the instruction, 2nd is to bring the operand. Indirect Address Instruction: needs 3 visits to memory. The 1st one is to fetch the instruction, 2nd is to bring the operand address. And the 3rd is to bring the operand itself.

Question 5-3) Question S2 S1 S0 A B C d 1 1 1 0 1 1 0 0 1 0 0 0

LD of register IR PC DR AC

Memory Adder Read --Write --------Add

Solution IR <-- M[AR] PC <-- TR DR <- AC,M[AR] <-- AC AC <- AC + DR

Question 5-4) Operation AR PC IR M[AR] M[AR] TR AC DR, DR AC (done simultaneously)

S2 0 1 1 1

S1 1 1 1 0

S0 0 1 0 0

LD AR IR ------DR, AC

Memory ------READ WRITE -------

Adder/Logic Unit ------------------Transfer from DR to AC

Question 5-5) a) We cant use the PC as an address to Memory, because Memory takes its address from AR Register. We can write it as: AR PC IR M[AR] b) There is no such access to AC except for INPR, DR and itself, so the correct form would be: DR TR AC AC + DR c) This would change the value of AC to AC + DR. Also the Adder and Logic Unit should save its result in AC not in DR. The correct form would be: AC DR, DR AC AC AC + DR AC DR, DR AC

Question 5-6) Part Binary instructions A B C 0001 0000 0010 0100 1011 0001 0010 0100 0111 0000 0010 0000

Hexa. Operation code 1024 Add memory word that has the address $024 to AC B124 Store the contents of AC in memory word whose address can be found in memory word having the address $124 7020 Increment contents of AC by 1.

Question 5-7) CLE CME

Question 5-9)

Instruction E AC

Given CLA CLE CMA CME CIR CIL INC SPA SNA SZA SZE HLT Question 5-10)

PC AR

X

IR

X

1 A937 021

1 0000 022 800 7800 0 A937 022 400 7400 1 56C8 022 200 7200 0 A937 022 100 7100 1 D49B 022 080 7080 1 526F 022 040 7040 1 A938 022 020 7020 1 A937 022 010 7010 1 A937 023 008 7008 1 A937 022 004 7004 1 A937 022 002 7002 1 A937 022 001 7001

MRI

Initially AND ADD LDA STA BUN BSA ISA Question 5-11)

IR

AR

DR

AC

PC

---- ---- ---- A937 021 0083 083 B8F2 A832 022 1083 083 B8F2 6229 022 2083 083 B8F2 B8F2 022 3083 083 ---- A937 022 4083 083 ---- A937 083 5083 083 ---- A937 083 084 6083 083 B8F3 A9F2 022

Timing signal PC AR DR

Given T0 T1 T2 T3 T4 T5 T6 7FF 7FF 800 800 800 800 800 801 X 7FF 7FF A9F C35 C35 C35 C35 X X X X X FFFF 0000 0000

IR

X X EA9F EA9F EA9F EA9F EA9F EA9F

SC

0 1 2 3 4 5 6 0

Question 5-12) a. Instruction is: 932E b. This instruction is [ADD I 32E ], which will add the contents of memory word whose address is stored in memory location 32E (indirect addressing).So AC will have the value 7EC3 + 8B9F = 0A62. c. PC AR DR AC IR E I SC 3B0 9AC 8B9F 0A62 932E 1 1 0101 0000 Question 5-13) Symbol Opcode Symbolic designation XOR 000 AC <---- AC XOR M[EA] ADM 001 M[EA]<---- M[EA]+ AC SUB XCH SEQ BPA 010 011 100 101 AC <== AC-M[EA] AC<==M[EA], M[EA]<==AC IF(M[EA]==AC) THEN (PC<==PC+1) IF (AC>0) THEN (PC <==EA)

Description XORing Adding Subtraction Skip on equality Branch if AC>0

Assuming: Each instr. Begins by T4 Adder can perform XOR directly Cant do Subtraction

Solution: First Instruction D0T4: R M[AR] AC DR, SC D0T5: AC

Second Instruction: D1T4: DR M[AR] D1T5: DR AC, AC AC + DR D1T6: M[AR] AC, AC DR, SC Third Instruction: D2T4: DR M[AR] D2T5: DR AC, AC DR D2T6: AC (AC D2T7: AC AC+1 D2T8: AC AC + DR, SC

Fourth Instruction (Exchange): D3T4: DR M[AR] D3T5: M[AR] AC, AC DR, SC Fifth Instruction: D4T4: DR M[AR] AC, AC AC DR D4T5: DR D4T6: if (AC= = 0) then (PC

PC + 1), AC PC

DR, SC AR , SC 0

Sixth instruction (branch if AC>0): D5T4: if (AC(15) == 0 && AC <>0) THEN

Question 6-14) We will replace the memory reference instruction ISZ with [ LDC address ], which will load the CTR register with the value specified by the address. In addition to that, we will add a new register reference instruction. ICSZ: increment CTR and skip next instruction if zero. By using this instruction we dont have to load the memory word into DR, then incrementing DR, and then check it whether it is zero or not, and finally at T6 we will load the value of DR into memory or increment PC. However, by using ICSZ we will execute this instruction at only one clock cycle at T4.

Question 6-15) The memory is to be changed to 65,536 * 16 memory ( address of 16 bits) When I=1 (indirect ) theres no change. But when I=0 (direct address) the address is given by the 16 bits in the next word following the instruction. Modify T2, T3, and T4 if necessary to conform to this configuration: Solution: 56,536*16 memory has 16 address lines (which means 216 words) with each word having 16 btis. T0, T1, and T2: No change (fetching and decoding) T3 D7: No change (Register or I/O instructions) Indirect: ID7 T3: AR(12-15) <--- 0 ID7 T4: AR <--M[AR] Direct: ID7 T3: PC <-- PC + 1 ID7 T4: AR <-- PC So memory reference instructions would be executed starting from T5.

Question 5-17) Capacity of memory = 16,384 word (=214) with 40 bits per each word. 6 bits/op-code, 14 bits/address-part, where every two instructions are packed into one memory word. And a 40-bit IR register is available in control unit. Formulate fetching and executing instructions? I will add a flip flop (P) that would do the following:

Question 5-18) a. The instruction @ address 1 must be a branch to address 300, the address written in the book is wrong (4 bits), so I will consider the first 3 bits of it. b. The last two instructions would be: PC PC+1, IEN 1 The last one would be [BUN I 000]: an indirect branch to memory location 0, and then to reset the SC.

Question 5-19) R<--M[AR] Read memory word into R X3 1 X1 2 R<--AC Transfer AC to R X1 3 M[AR]<--R Write R to memory The memory has data inputs, data outputs, and control inputs to read and write. Draw the hardware implementation of R and memory?

Question 5-20) Operations of F flip flop: XT3: F 1 YT1: F 0 ZT2: F F WT5: F G PRESET: J= XT3 + ZT2Q + WT5G CLEAR: K= YT1 + ZT2Q + WT5G

Question 5-21) Control gates associated with PC: We assume those signals A={1:when DR=0 and 0:otherwise} M=AC(15) N=1 if AC=0 INC =RT1 + RT2 + AD6T6 + ID7T3[MB4 + MB3 + NB2 + EB1]+ ID7T3[B9(FGI) + B8(FGO) ] CLR = RT1 LD = D4T4 + D5T5 +

Question 5-22) Control gates for the write input of the memory: WRITE = RT1 + D3T4 + D5T4 + D6T6

Question 5-23) Showing the complete logic of R flip flop in the basic computer using a JK flip flop. (R=1): T0T1T2(IEN)(FGI + FGO) (R=0): RT2

Question 5-24) X2 = RTO + RTO + D5T4 = TO + D5T4

Question 5-25) Deriving the Boolean expression for the gate structure the clears the sequence counter. CLR = D0T5 + D1T5 + D2T5 + D3T4 + D4T4 + D5T5 + D6T6 + D7 IT3 + D7 IT3 + R T2

S-ar putea să vă placă și

- Digital Signal Processing: Instant AccessDe la EverandDigital Signal Processing: Instant AccessEvaluare: 3.5 din 5 stele3.5/5 (2)

- Basic Computer OrganizationDocument19 paginiBasic Computer OrganizationBarikly RobbyÎncă nu există evaluări

- CA SolutionDocument14 paginiCA SolutionSaba InamÎncă nu există evaluări

- Practice AssignmentDocument4 paginiPractice Assignmentshriya2413Încă nu există evaluări

- Exam2 ReviewDocument54 paginiExam2 ReviewSurbhie Kalia ChebaÎncă nu există evaluări

- Basic Computer Organization and DesignDocument35 paginiBasic Computer Organization and DesignVinay KumarÎncă nu există evaluări

- Individual Assignment QuestionsDocument3 paginiIndividual Assignment QuestionsGemechisÎncă nu există evaluări

- Fetch-Execute Cycle: Minggu 1 Arsitektur KomputerDocument12 paginiFetch-Execute Cycle: Minggu 1 Arsitektur KomputerRyan SaputraÎncă nu există evaluări

- Assembly LanguageDocument7 paginiAssembly LanguageDilip JhaÎncă nu există evaluări

- Tutorial Module 4Document9 paginiTutorial Module 4Neupane Er KrishnaÎncă nu există evaluări

- Memory Reference InstructionDocument19 paginiMemory Reference InstructionDeepak SinghÎncă nu există evaluări

- ArchitectureDocument5 paginiArchitectureLove SharmaÎncă nu există evaluări

- 03 Bagian 1 Arsitektur AVRDocument22 pagini03 Bagian 1 Arsitektur AVRTito Adi NugrohoÎncă nu există evaluări

- Lcdf3 Chap 10 p2Document32 paginiLcdf3 Chap 10 p2Ali Ahmad100% (1)

- Unit3 Coa NotesDocument32 paginiUnit3 Coa Notesvivek kumarÎncă nu există evaluări

- Computer Architecture 3rd Edition by Moris Mano CH 05Document35 paginiComputer Architecture 3rd Edition by Moris Mano CH 05Sadaf RasheedÎncă nu există evaluări

- SMIPS ISA and Instruction Decoding: Introduction To Computer OrganizationDocument47 paginiSMIPS ISA and Instruction Decoding: Introduction To Computer OrganizationSai SaurabÎncă nu există evaluări

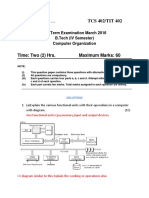

- Roll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Document18 paginiRoll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Obsii ChalaÎncă nu există evaluări

- Exam 1: EE319K Spring 2013 Exam 1 (Practice 1)Document6 paginiExam 1: EE319K Spring 2013 Exam 1 (Practice 1)SRITHA PÎncă nu există evaluări

- Micro Programmed Control Organization.: Next-Address InformationDocument16 paginiMicro Programmed Control Organization.: Next-Address InformationZaheer AsgharÎncă nu există evaluări

- Lecture 6 Practice Problems - Part 1Document3 paginiLecture 6 Practice Problems - Part 1Yasir ButtÎncă nu există evaluări

- Data Transfer and Arithmetic InstructionsDocument6 paginiData Transfer and Arithmetic InstructionsAkshaya ThirumalairajÎncă nu există evaluări

- Basic Computer Organization - Part 05Document5 paginiBasic Computer Organization - Part 05Kamala Rani RoyÎncă nu există evaluări

- Computer Applications and ManagementDocument11 paginiComputer Applications and ManagementParag PaliwalÎncă nu există evaluări

- 03 Chapter 5Document60 pagini03 Chapter 5uabdulgwadÎncă nu există evaluări

- Basic Computer Organization and DesignDocument35 paginiBasic Computer Organization and Designabhisrit2008Încă nu există evaluări

- Lec12 Basic Computer OrganizationDocument75 paginiLec12 Basic Computer OrganizationAya AbdAllah AmmarÎncă nu există evaluări

- The University of Alabama in Huntsville: r2 r1 Not r1, r2Document5 paginiThe University of Alabama in Huntsville: r2 r1 Not r1, r2Kyra LathonÎncă nu există evaluări

- Unit 3 CSADocument25 paginiUnit 3 CSAyugdevÎncă nu există evaluări

- MT Exam Model AnswerDocument13 paginiMT Exam Model AnswerSeif ElmoushyÎncă nu există evaluări

- معمارية 2Document13 paginiمعمارية 2firasvtÎncă nu există evaluări

- Caassgnsem 1Document12 paginiCaassgnsem 1Sunil GawaskerÎncă nu există evaluări

- CO Unit 2-1Document15 paginiCO Unit 2-1Aravinder Reddy SuramÎncă nu există evaluări

- Memory Reference Instructions ExecutionDocument13 paginiMemory Reference Instructions ExecutionAditya Singh100% (1)

- G2B and G3B CANopen FDocument12 paginiG2B and G3B CANopen Fangel silvaÎncă nu există evaluări

- Unit 4Document17 paginiUnit 4pranaykumarghosh41Încă nu există evaluări

- DSP Unit 1 To 5 QBDocument12 paginiDSP Unit 1 To 5 QBSamuel WhiteÎncă nu există evaluări

- CO Unit 2-2Document19 paginiCO Unit 2-2Aravinder Reddy Suram0% (2)

- RGMIIv1 3Document8 paginiRGMIIv1 3lim_mgÎncă nu există evaluări

- Quiz 3 SolutionsDocument3 paginiQuiz 3 SolutionsP o o P o o H e a dÎncă nu există evaluări

- Advanced Micro 2Document18 paginiAdvanced Micro 2Shahabaj DangeÎncă nu există evaluări

- Lab 3mikro P UPDATEDDocument23 paginiLab 3mikro P UPDATEDNaza RenkoÎncă nu există evaluări

- Revision Problems ECE3073/TRC3300 Weeks 7-12Document9 paginiRevision Problems ECE3073/TRC3300 Weeks 7-12kewancamÎncă nu există evaluări

- DatasheetDocument248 paginiDatasheetRajesh MauryaÎncă nu există evaluări

- Instruction Set of C2xx DSP CoreDocument9 paginiInstruction Set of C2xx DSP Coreanju_prajuÎncă nu există evaluări

- Embedded Micro Controller Test SolutionDocument9 paginiEmbedded Micro Controller Test SolutionalikaastridÎncă nu există evaluări

- Lecture 22Document8 paginiLecture 22VINAYÎncă nu există evaluări

- Basic Computer Organization and Design: - Computer Registers - Instruction CycleDocument21 paginiBasic Computer Organization and Design: - Computer Registers - Instruction CycleShashank PandeyÎncă nu există evaluări

- M @-51 Instruction Set: Programmer'SDocument7 paginiM @-51 Instruction Set: Programmer'Swen_galsÎncă nu există evaluări

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofDocument7 paginiLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamÎncă nu există evaluări

- CA Assignment IIDocument9 paginiCA Assignment IISomesh ThakurÎncă nu există evaluări

- DVP - Communication ProtocolDocument15 paginiDVP - Communication ProtocolKashif KhanÎncă nu există evaluări

- Pertemuan 7 Bahasa Rakitan: III: Matakuliah: T0324 / Arsitektur Dan Organisasi Komputer Tahun: 2005 Versi: 1Document30 paginiPertemuan 7 Bahasa Rakitan: III: Matakuliah: T0324 / Arsitektur Dan Organisasi Komputer Tahun: 2005 Versi: 1Ten Dian Novita SariÎncă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysDe la EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysÎncă nu există evaluări

- Exploring Arduino: Tools and Techniques for Engineering WizardryDe la EverandExploring Arduino: Tools and Techniques for Engineering WizardryEvaluare: 4.5 din 5 stele4.5/5 (5)

- Digital Signal Processing Using the ARM Cortex M4De la EverandDigital Signal Processing Using the ARM Cortex M4Evaluare: 1 din 5 stele1/5 (1)

- Erratas For Principles of Signal Detection and Parameter EstimationDocument5 paginiErratas For Principles of Signal Detection and Parameter Estimationblue_fire_englandÎncă nu există evaluări

- Errata For Principles of Signal Detection and Parameter EstimationDocument5 paginiErrata For Principles of Signal Detection and Parameter Estimationblue_fire_englandÎncă nu există evaluări

- Errata Fors Principles of Signal Detection and Parameter EstimationDocument5 paginiErrata Fors Principles of Signal Detection and Parameter Estimationblue_fire_englandÎncă nu există evaluări

- List of Errata For Principles of Signal Detection and Parameter EstimationDocument5 paginiList of Errata For Principles of Signal Detection and Parameter Estimationblue_fire_englandÎncă nu există evaluări

- List of Errata For Principles of Signal Detection and Parameter EstimationDocument5 paginiList of Errata For Principles of Signal Detection and Parameter Estimationblue_fire_englandÎncă nu există evaluări

- Radar HW1Document2 paginiRadar HW1blue_fire_englandÎncă nu există evaluări

- Solution Manual - Error Control Coding 2nd - by Lin Shu and CostelloDocument126 paginiSolution Manual - Error Control Coding 2nd - by Lin Shu and CostelloSerkan Sezer57% (14)

- Introduction To Finite Fields: Yunghsiang S. HanDocument41 paginiIntroduction To Finite Fields: Yunghsiang S. Hanblue_fire_englandÎncă nu există evaluări

- Ocr System ArchitectureDocument15 paginiOcr System ArchitectureNazrul IslamÎncă nu există evaluări

- Preparing Systems For Preparing Systems For SQL Server 2012Document27 paginiPreparing Systems For Preparing Systems For SQL Server 2012Nguyen Khanh Hoa (TGV)Încă nu există evaluări

- VA10800/VA10820 ARM Cortex - M0 Based Processor Programmers GuideDocument151 paginiVA10800/VA10820 ARM Cortex - M0 Based Processor Programmers GuideFlavio FalcãoÎncă nu există evaluări

- Chap 03 Introduction To Assembly Language ProgrammingDocument87 paginiChap 03 Introduction To Assembly Language ProgrammingDann LaurteÎncă nu există evaluări

- Introduction To Computer ApplicationDocument56 paginiIntroduction To Computer ApplicationKrithika K MuralidharanÎncă nu există evaluări

- 1983 Zilog Microprocessor Applications Reference Book Volume 2Document391 pagini1983 Zilog Microprocessor Applications Reference Book Volume 2Vignesh RamakrishnanÎncă nu există evaluări

- Docker Commands Cheat Sheet PDFDocument2 paginiDocker Commands Cheat Sheet PDFprakash_6849Încă nu există evaluări

- Monitoring Hardware ST06 Operating System Overview SM51 Analyzing CPU and Paging ST06Document14 paginiMonitoring Hardware ST06 Operating System Overview SM51 Analyzing CPU and Paging ST06Amit GandhiÎncă nu există evaluări

- SCD5200 CPU OptoNet Power Supply Ethernet (COPE) ModuleDocument8 paginiSCD5200 CPU OptoNet Power Supply Ethernet (COPE) ModuleWisnu HartonoÎncă nu există evaluări

- Intel ChipsetsDocument3 paginiIntel ChipsetsGhefelyn MedinaÎncă nu există evaluări

- Cryptocurrency System Using Body Activity Data 3 of 6Document1 paginăCryptocurrency System Using Body Activity Data 3 of 6Nemo NemoÎncă nu există evaluări

- #Include #Include #Include VoidDocument3 pagini#Include #Include #Include VoidTanya SunishÎncă nu există evaluări

- Cisco Identity Services Engine Installation Guide, Release 2.4Document90 paginiCisco Identity Services Engine Installation Guide, Release 2.4Minh HoàngÎncă nu există evaluări

- Evolution of ProcessorDocument6 paginiEvolution of ProcessorAshley NohayÎncă nu există evaluări

- Mastering stm32 Sample PDFDocument116 paginiMastering stm32 Sample PDFUzair Ahmed Chughtai100% (1)

- AHF and TFA Management - Fernando SimonDocument6 paginiAHF and TFA Management - Fernando SimonAshok ThiyagarajanÎncă nu există evaluări

- Task StructureDocument49 paginiTask StructureAmir HakimÎncă nu există evaluări

- Computer Organization and Architecture Module 3Document34 paginiComputer Organization and Architecture Module 3Assini Hussain100% (1)

- Programmable Logic Controller (PLC) Is A Digital Computer Used For The Automation of VariousDocument23 paginiProgrammable Logic Controller (PLC) Is A Digital Computer Used For The Automation of VariousSunil ChaudhariÎncă nu există evaluări

- Classification of Computer According To CapacityDocument77 paginiClassification of Computer According To CapacityMalou Benoza-Lansangan60% (5)

- MPMC MCQ Unit 1Document7 paginiMPMC MCQ Unit 1Prajwal BirwadkarÎncă nu există evaluări

- Computer Science Paper 1 2 Guide - As 1 mk3xpq3nzjfV04QZDocument29 paginiComputer Science Paper 1 2 Guide - As 1 mk3xpq3nzjfV04QZOmar AamirÎncă nu există evaluări

- M.tech Cse FTDocument33 paginiM.tech Cse FTBalaji SsrÎncă nu există evaluări

- Stepper Motor Interfacing With 8051 Micro ControllerDocument2 paginiStepper Motor Interfacing With 8051 Micro ControllerChandrasekhar Prabhakaran100% (1)

- Public Roadmap Article PDFDocument11 paginiPublic Roadmap Article PDFnew2trackÎncă nu există evaluări

- Cambridge IGCSE: Computer Science 0478/12Document16 paginiCambridge IGCSE: Computer Science 0478/12waihon.pang2011100% (1)

- Computer System ProjectDocument342 paginiComputer System ProjectBryy AnyyÎncă nu există evaluări

- Performance Tuning An HPC Cluster - FINAL 012009Document41 paginiPerformance Tuning An HPC Cluster - FINAL 012009Ezio KurataniÎncă nu există evaluări

- 80x85 FormatDocument17 pagini80x85 Formatnorberto_1Încă nu există evaluări