Documente Academic

Documente Profesional

Documente Cultură

Preliminary Data Sheet TDA21101: Features

Încărcat de

Juan RiosDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Preliminary Data Sheet TDA21101: Features

Încărcat de

Juan RiosDrepturi de autor:

Formate disponibile

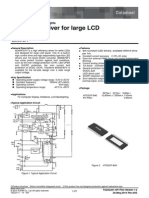

Preliminary Data Sheet High speed Driver with bootstrapping for dual Power MOSFETs

TDA21101

P-DSO-8

Features Fast rise and fall times for frequencies up to 2 MHz Capable of sinking and sourcing of more than 4 A peak current for lowest switching losses Charges High Side (internally clamped to 10 V) and Low Side MOSFETs gates up to 12 V for lowest on-losses Adjustable High Side MOSFET gate drive voltage via high impedance PVCC pin for optimizing ON losses, gate drive losses, and switching losses Integrates the bootstrap diode for reducing the part count Prevents from cross-conducting by adaptive gate drive control Protects the driver against over-temperature Supports shut-down mode for very low quiescent current through three-state input Compatible to standard PWM controller ICs Floating High Side MOSFET drive up to 30 V Operates with V PVCC = 5 to 12 V 10 % requires no separate supply voltage 1:1 compatible to HIP6601A and HIP6601B Ideal for multi-phase Desktop CPU supplies on motherboards and VRMs and Notebook CPU supplies Package P-DSO-8 Marking 21101G Ordering Code Q67042-S4170-A101

Type TDA21101

Pinout

Number Name 1 GATE HS 2 BOOT

Top View

GATEHS 1 BOOT PWM GND 2 3 4 8 7 6 5

PHASE PVCC VCC GATELS

3 4 5 6 7 8

PWM GND GATE LS VCC PVCC PHASE

Description Gate drive output for the N-Channel High side MOSFET Floating bootstrap pin. To be connected to the external bootstrap capacitor to generate the gate drive voltage for the high side N-Channel MOSFET Input for the PWM controller signal Ground Gate drive output for the N-Channel Low Side MOSFET Supply voltage High impedance input to adjust the High Side gate drive This pin connects to the junction of the High Side and the Low Side MOSFET

2002-03-28

Page 1

Preliminary Data Sheet

TDA21101

General Description The dual high speed driver is designed to drive a wide range of N-Channel low side and N-Channel high side MOSFETs with varying gate charges. It has a small propagation delay from input to output, short rise and fall times and the same pin configuration to be compatible to HIP6601. In addition it provides several protection features as well as a shut down mode for efficiency reasons. The high breakdown voltage makes it suitable for mobile applications.

Target application The dual high speed driver is designed to work well in half-bridge type circuits where dual N-Channel MOSFETs are utilized. A circuit designer can fully take advantage of the drivers capabilities in high-efficiency, high-density synchronous DC/DC converters that operate at high switching frequencies, e.g. in multi-phase converters for CPU supplies on motherboards and VRMs but also in motor drive and class-D amplifier type applications. Absolute Maximum Ratings

At Tj = 25 C, unless otherwise specified

Parameter Voltage supplied to VCC pin Voltage supplied to PVCC pin Voltage supplied to PWM pin Voltage supplied to BOOT pin referenced to PHASE (clamped by the TDA21101 to 10 V when PVCC > 10 V) Voltage rating at PHASE pin, DC Junction temperature Storage temperature ESD Rating; Human Body Model IEC climatic category; DIN EN 60068-1 Thermal Characteristic Parameter Thermal resistance, junction-soldering point Thermal resistance, junction-ambient

Symbol VVCC VPVCC VPWM VBOOT VPHASE VPHASE TJ TS

Value Unit Min. Max. -0.3 -0.3 -0.3 -0.3 -15 20 20 6.5 10

30 150 -55 150 4 55/150/56

C kV -

Symbol

Values Unit Min. Typ. Max. 90 K/W 125

Page 2

2002-03-28

Preliminary Data Sheet

TDA21101

Electrical Characteristic

At Tj = 25 C, unless otherwise specified

Parameter Supply Characteristic Bias supply current Quiescent current Power supply current

Symbol

Conditions

Values Unit Min. Typ. Max. 9.0 4.5 -500 500 12 mA mA nA

IVCC IVCCQ IPVCC

Under-voltage lockout 9.0 9.5 10 V Under-voltage lockout 8.15 8.8 9.15 V Input Characteristic Current in PWM pin IPWM_L V_PWM = 0.4 V -120 A Current in PWM pin IPWM_H V_PWM = 4.5 V 180 Shut down window VIN_SHUT t_SHUT > 600 ns 1.8 3.0 V Shut down hold-off t_SHUT 320 450 600 ns 1.8 V V PWM 3.0 V time PWM pin open * VPWM_O 1.8 2.0 2.2 PWM Low level VPWM_L 1.2 2.5 threshold V PWM High level VPWM_H 2.5 3.9 threshold * The driver IC will shut down and the High side MOSFET and the Low side MOSFET will be turnedoff when the PWM input is open (e.g. PWM input disconnected or the PWM IC in a high-Z state) At Tj = 25 C, unless otherwise specified

f = 250 kHz, VPVCC = V VCC = 12 V 1.8 V V PWM 3.0 V 0.1 f 2 MHz, 5 V V PVCC 12 V VVCC rising threshold VVCC falling threshold

Dynamic Characteristic Turn-on propagation td(ON)_HS Delay High Side Turn-off propagation td(OFF)_HS delay High Side Rise time High Side tr_HS Fall time High Side tf_HS Turn-on propagation td(ON)_LS Delay Low Side Turn-off propagation td(OFF)_LS delay Low Side Rise time Low Side tr_LS Fall time Low Side tf_LS Turn-on propagation td(ON)_HS Delay High Side Turn-off propagation td(OFF)_HS delay High Side Rise time High Side tr_HS Fall time High Side tf_HS Turn-on propagation td(ON)_LS Delay Low Side

58 40 PPVCC = V VCC= 12 V CISS = 3000 pF 18 18 40 30 19 17 80 60 PPVCC = V VCC= 12 V CISS = 3000 pF TJ = 125 C 18 21 50

70 50 34 30 60 40 32 25 ns

ns

Page 3

2002-03-28

Preliminary Data Sheet

Turn-off propagation delay Low Side Rise time Low Side Fall time Low Side Operating Conditions

At Tj = 25 C, unless otherwise specified

TDA21101

43 21 20

td(OFF)_LS tr_LS tf_LS

Parameter Voltage supplied to VCC pins Voltage supplied to PVCC pins Input signal transition frequency Power dissipation Thermal shut down Junction temperature Parameter

Symbol VVCC VPVCC f PTOT TOT TJ

Conditions

Values Unit Min. Typ. Max. 10.8 5 0.1 13.2 13.2 2 0.8 150 V V MHz W C C

TA = 25 C, TJ = 125 C (Hysteresis = 50 C)

135 -25

165 125

At Tj = 25 C, unless otherwise specified

Values Unit Min. Typ. Max. Output Characteristic High Side (HS) and Low Side (LS), ensured by design Output HS; Source * PPVCC = V VCC= 12 V 2.15 V Resistance and I_HS_SRC = 2 A Voltage drop HS; Sink VVCC= 12 V, P PVCC = 5 V 1.2 1.9 resp. HS; Sink PPVCC = V VCC= 12 V 0.95 1.5 LS; Source * PPVCC = V VCC= 12 V 2.15 V I_HS_SRC = 2 A LS; Sink PPVCC = V VCC= 12 V 0.7 1.0 HS; Source * PPVCC = V VCC= 12 V 1.65 V I_HS_SRC = 2 A, TJ = 125 C Output HS; Sink VVCC= 12 V, P PVCC = 5 V 1.9 Resistance and TJ = 125 C Voltage drop HS; Sink PPVCC = V VCC= 12 V 1.5 resp. (@ 125 C) TJ = 125 C LS; Source * PPVCC = V VCC= 12 V 1.65 V I_HS_SRC = 2 A, TJ = 125 C LS; Sink PPVCC = V VCC= 12 V 1.1 TJ = 125 C HS; Source * PPVCC = V VCC= 12 V 4 Peak outputD<3% A HS; Sink 4 current t_P / Pulse < 30 ns LS; Source * 4 LS; Sink 4 * The sourcing outputs of the LS and the HS terminals are bipolar and MOS transistors in parallel. The

voltage drop is the voltage drop across the bipolar and MOS transistor combination; the peak output current is the combined output current the driver can deliver.

Conditions

Page 4

2002-03-28

Preliminary Data Sheet

Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 53, D-81541 Mnchen Infineon Technologies AG 1999 All Rights Reserved.

TDA21101

Attention please! The information herein is given to describe certain components and shall not be considered as warranted characteristics. Terms of delivery and rights to technical change reserved. We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list). Warnings Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office. Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Page 5

2002-03-28

S-ar putea să vă placă și

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDe la EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsEvaluare: 3.5 din 5 stele3.5/5 (6)

- Fan 7392NDocument18 paginiFan 7392NKhaleel MohammadÎncă nu există evaluări

- Dual Channel Synchronous-Rectified Buck MOSFET DriverDocument8 paginiDual Channel Synchronous-Rectified Buck MOSFET Driverragav1234Încă nu există evaluări

- APW7165Document20 paginiAPW7165Jorge BulacioÎncă nu există evaluări

- A 2918 SW Data SheetDocument8 paginiA 2918 SW Data SheetGustavo LunaÎncă nu există evaluări

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 paginiNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânÎncă nu există evaluări

- LCD Bias Power Integrated With WLED Backlight Drivers: FeaturesDocument31 paginiLCD Bias Power Integrated With WLED Backlight Drivers: FeaturesJoseph BernardÎncă nu există evaluări

- Uc2854b EpDocument13 paginiUc2854b EpBruno NascimentoÎncă nu există evaluări

- High Efficiency Low-Side N-Channel Controller For Switching RegulatorsDocument33 paginiHigh Efficiency Low-Side N-Channel Controller For Switching Regulatorssoft4gsmÎncă nu există evaluări

- Dual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Document16 paginiDual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Benny RoyÎncă nu există evaluări

- Fan 7382Document14 paginiFan 7382Giovanni Carrillo VillegasÎncă nu există evaluări

- Cost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesDocument13 paginiCost-Effective, 2A Sink/Source Bus Termination Regulator: General Description FeaturesMostapha BenaliÎncă nu există evaluări

- IRAMX16UP60ADocument18 paginiIRAMX16UP60Atheylor1990Încă nu există evaluări

- DRV 8811Document22 paginiDRV 8811nelson_loboÎncă nu există evaluări

- FAN7382 High-And Low-Side Gate Driver: Features DescriptionDocument15 paginiFAN7382 High-And Low-Side Gate Driver: Features DescriptionRiza BaduaÎncă nu există evaluări

- 4623 FDocument24 pagini4623 Fante mitarÎncă nu există evaluări

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDocument17 paginiLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiÎncă nu există evaluări

- CD4047Document9 paginiCD4047Haryadi VjÎncă nu există evaluări

- MC33153 DDocument14 paginiMC33153 DPham LongÎncă nu există evaluări

- NCP 2171Document19 paginiNCP 2171mari_casuÎncă nu există evaluări

- LM2852 Synchronous BuckDocument14 paginiLM2852 Synchronous BuckAndrew CavanaughÎncă nu există evaluări

- Quasi Resonant Controller: The Future of Analog IC TechnologyDocument15 paginiQuasi Resonant Controller: The Future of Analog IC TechnologyJuarez GouveiaÎncă nu există evaluări

- Dap011 DDocument24 paginiDap011 Dsontuyet82Încă nu există evaluări

- DatasheetDocument13 paginiDatasheetkishore kumarÎncă nu există evaluări

- STRW6252Document15 paginiSTRW6252miltoncgÎncă nu există evaluări

- Irs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICDocument29 paginiIrs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICAnonymous R0s4q9X8Încă nu există evaluări

- HV9971Document10 paginiHV9971Jazmin JorgeÎncă nu există evaluări

- DPA001 - ATX-Dedicated PWM Controller DPA001: Customer Specific Device From ON SemiconductorDocument18 paginiDPA001 - ATX-Dedicated PWM Controller DPA001: Customer Specific Device From ON Semiconductorsontuyet82Încă nu există evaluări

- Datasheet PDFDocument15 paginiDatasheet PDFperro sÎncă nu există evaluări

- IC-ON-LINE - CN dm0365r 44840Document20 paginiIC-ON-LINE - CN dm0365r 44840MoscandoÎncă nu există evaluări

- 2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyDocument16 pagini2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyCazbir MariAndradaÎncă nu există evaluări

- Irams 06 Up 60 ADocument18 paginiIrams 06 Up 60 AAndré Roberto EvangelistaÎncă nu există evaluări

- Single Synchronous Buck PWM DC-DC ControllerDocument16 paginiSingle Synchronous Buck PWM DC-DC Controllerbachet56Încă nu există evaluări

- TDA8925Document23 paginiTDA8925Mahmoued YasinÎncă nu există evaluări

- Ic 3843Document4 paginiIc 3843nishatiwari82Încă nu există evaluări

- 275V 40-Channel Row Driver With SCR Outputs: PreliminaryDocument9 pagini275V 40-Channel Row Driver With SCR Outputs: PreliminarySodoma12Încă nu există evaluări

- Datasheet 1Document18 paginiDatasheet 1shashwatthakurÎncă nu există evaluări

- DRV 8834Document30 paginiDRV 8834Anonymous 10cG5eRp8100% (1)

- OB2269Document12 paginiOB2269Juan Ballon100% (1)

- Bd9397efv e PDFDocument30 paginiBd9397efv e PDFshafiuddin7326Încă nu există evaluări

- Mcp1416 Power Mosfet DriverDocument18 paginiMcp1416 Power Mosfet DriverNegru P. PlantatieÎncă nu există evaluări

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 paginiN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxÎncă nu există evaluări

- Tps 92512Document30 paginiTps 92512ppanagosÎncă nu există evaluări

- Tps 40057 PWPDocument33 paginiTps 40057 PWPcatsoithahuong84Încă nu există evaluări

- LT1076 5Document8 paginiLT1076 5Marquis DavidÎncă nu există evaluări

- MC 14053Document12 paginiMC 14053roozbehxoxÎncă nu există evaluări

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocument16 paginiEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84Încă nu există evaluări

- MC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterDocument6 paginiMC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterCh SamirÎncă nu există evaluări

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocument11 paginiNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniÎncă nu există evaluări

- MC14017B Decade Counter: PDIP 16 P Suffix CASE 648Document9 paginiMC14017B Decade Counter: PDIP 16 P Suffix CASE 648JossuarmmÎncă nu există evaluări

- NXP Tja1050Document18 paginiNXP Tja1050Sebastian BryceÎncă nu există evaluări

- VND 7 N 04Document30 paginiVND 7 N 04Juan Guillermo MansillaÎncă nu există evaluări

- HS-2420RH - Fast Sample and HolDocument8 paginiHS-2420RH - Fast Sample and HolDeepa DevarajÎncă nu există evaluări

- NCP 43080Document36 paginiNCP 43080TestronicpartsÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Evaluare: 2.5 din 5 stele2.5/5 (3)

- Pic 150120Document1 paginăPic 150120Juan RiosÎncă nu există evaluări

- LITENING Advanced Targeting Pod - Northrop GrummanDocument8 paginiLITENING Advanced Targeting Pod - Northrop GrummanJuan RiosÎncă nu există evaluări

- RDR 2000 & RDR 2100: Weather Radar For General AviationDocument2 paginiRDR 2000 & RDR 2100: Weather Radar For General AviationJuan RiosÎncă nu există evaluări

- Viavi PSD90 1C Operating ManualDocument44 paginiViavi PSD90 1C Operating ManualJuan RiosÎncă nu există evaluări

- Northrop Grumman's 'OpenPod' Aimed at F-15 Requirement - Defense News - Aviation International NewsDocument1 paginăNorthrop Grumman's 'OpenPod' Aimed at F-15 Requirement - Defense News - Aviation International NewsJuan RiosÎncă nu există evaluări

- Manual OmniDrive USB2 CF V1-21EDocument2 paginiManual OmniDrive USB2 CF V1-21EJuan RiosÎncă nu există evaluări

- Bombardier UpgradeDocument15 paginiBombardier UpgradeJuan RiosÎncă nu există evaluări

- Makito X Encoder Quick Start Guide-V1-20221115 - 040550Document15 paginiMakito X Encoder Quick Start Guide-V1-20221115 - 040550Juan RiosÎncă nu există evaluări

- Manual Informativo Titan ServerDocument6 paginiManual Informativo Titan ServerJuan RiosÎncă nu există evaluări

- Manual AltimetricoDocument14 paginiManual AltimetricoJuan RiosÎncă nu există evaluări

- Información Técnica Radar SARDocument2 paginiInformación Técnica Radar SARJuan RiosÎncă nu există evaluări

- U9 K9gag08u0m 2gb-Final Nand-Not On Some PrototypesDocument51 paginiU9 K9gag08u0m 2gb-Final Nand-Not On Some PrototypesEddy Alexander Bolivar RodriguezÎncă nu există evaluări

- MSIZapDocument1 paginăMSIZapJuan RiosÎncă nu există evaluări

- 5401DM, MGB20N40CL, 09398588Document22 pagini5401DM, MGB20N40CL, 09398588Carlos Luis ColmenaresÎncă nu există evaluări

- Design Methdology For Differential Pair and Operational Transconductance AmplifierDocument18 paginiDesign Methdology For Differential Pair and Operational Transconductance AmplifierjitendraÎncă nu există evaluări

- Syllabus & Scheme For M.Tech. (ECE)Document27 paginiSyllabus & Scheme For M.Tech. (ECE)Siddharth SidÎncă nu există evaluări

- Inverter Analysis and Design: 6.012 - Microelectronic Devices and Circuits - Fall 2009Document7 paginiInverter Analysis and Design: 6.012 - Microelectronic Devices and Circuits - Fall 2009Ravi JainÎncă nu există evaluări

- Features Descriptio: LT4250L/LT4250H Negative 48V Hot Swap ControllerDocument12 paginiFeatures Descriptio: LT4250L/LT4250H Negative 48V Hot Swap ControllergeraldoÎncă nu există evaluări

- Rohini 37095079304Document6 paginiRohini 37095079304zga5v5Încă nu există evaluări

- Pa102fdg Mos PDocument5 paginiPa102fdg Mos PValentinÎncă nu există evaluări

- tpc8107 26791973Document59 paginitpc8107 26791973Richard BaidooÎncă nu există evaluări

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pagini130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucÎncă nu există evaluări

- Build a Tube Mic Pre_ Build Your Own Two Channel Vacuum Tube Mic Preamp! _ Tape Op Magazine _ Longform Candid Interviews With Music Producers and Audio Engineers Covering Mixing, Mastering, Recording and Music ProductionDocument10 paginiBuild a Tube Mic Pre_ Build Your Own Two Channel Vacuum Tube Mic Preamp! _ Tape Op Magazine _ Longform Candid Interviews With Music Producers and Audio Engineers Covering Mixing, Mastering, Recording and Music ProductionRenato Deák100% (1)

- VLSI Report PDFDocument20 paginiVLSI Report PDFNurulAnisAhmadÎncă nu există evaluări

- VIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONDocument8 paginiVIPower: 10W POWER SMPS USING VIPer22A FOR AIR-CONDITIONER APPLICATIONLullaby summerÎncă nu există evaluări

- FETs vs. BJTs: Key DifferencesDocument102 paginiFETs vs. BJTs: Key DifferencesanjanaÎncă nu există evaluări

- KAlam LabManual EEE102 EWU Summer 2012Document18 paginiKAlam LabManual EEE102 EWU Summer 2012Max TanÎncă nu există evaluări

- 2SK3053Document9 pagini2SK3053Иегҵ ГемасснеÎncă nu există evaluări

- BTech ECE Curriculum GuideDocument27 paginiBTech ECE Curriculum GuidePranayKumar AnugurtiÎncă nu există evaluări

- Ecen 3103Document2 paginiEcen 3103gaurav kumarÎncă nu există evaluări

- A Review Paper On CMOS, SOI and FinFET TechnologyDocument12 paginiA Review Paper On CMOS, SOI and FinFET Technologyરાહુલ મેહ્તાÎncă nu există evaluări

- BQ 76952Document86 paginiBQ 76952Đạt Trần DoãnÎncă nu există evaluări

- Dual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Document16 paginiDual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Benny RoyÎncă nu există evaluări

- Ec 1003Document23 paginiEc 1003Salam Surjit SinghÎncă nu există evaluări

- Fan7602-U2 SMDDocument18 paginiFan7602-U2 SMDLefter TironÎncă nu există evaluări

- MOSFET Device Operation and CharacteristicsDocument16 paginiMOSFET Device Operation and CharacteristicsVijay JalneelaÎncă nu există evaluări

- B-Stad Chapter 7Document20 paginiB-Stad Chapter 7ARif HakimÎncă nu există evaluări

- Digital Electronics & MicroprocessorsDocument152 paginiDigital Electronics & MicroprocessorsAnonymous FRJktAGZmÎncă nu există evaluări

- AOZ1031AIDocument15 paginiAOZ1031AIrachnologistÎncă nu există evaluări

- 200701Document88 pagini200701Seunggyu LeeÎncă nu există evaluări

- Thin Film TransistorDocument44 paginiThin Film TransistorSUBHRANSHU KUMAR SINGHÎncă nu există evaluări

- Irg4Pf50Wd: FeaturesDocument11 paginiIrg4Pf50Wd: FeaturesGuillermoÎncă nu există evaluări