Documente Academic

Documente Profesional

Documente Cultură

Regular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI Circuits

Încărcat de

Saranya ChakrabortyDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Regular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI Circuits

Încărcat de

Saranya ChakrabortyDrepturi de autor:

Formate disponibile

540

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 2 4 , NO.

2, APRIL 1989

Regular Correspondence

Compact High-Frequency Output Buffer for Testing of Analog CMOS VLSI Circuits

PETER M. VAN PETEGHEM. MEMBER. IEEE. AND J. F. DUQUE-CARRILLO, MEMBER, IEEE

Ahstrucr -A compact high-frequency CMOS analog buffer for testing purposes is presented. A prototype integrated in a 3-pm CMOS process drives a 15-pF 10-kB load, and shows a bandwidth of more than 30 MH2, a large-signal settling time to 1 percent less than 90 ns, and a dynamic range over 77 d B power consumption is 2.4 mA per cell. Its small size (less than 0.18 m d ) makes it suitable for monitoring low-capacitance internal nodes of analog or mixed-mode VLSI circuits.

related by the following equations:

where gnrl and C,, are the transconductance and gate-source capacitance of the input transistors, respectively, Cloddis the effective load capacitance, and B is a dimensionless transconductance multiplication factor (current mirror ratio). A combination of (1) and (2) yields

Most amplifiers in a CMOS analog integrated circuit only drive a high impedance. Indeed, the capacitive loading of internal nodes is seldom larger than a few picofarad, and the resistive loading is typically larger than 100 kQ. Therefore, unbuffered amplifiers or operational transconductance amplifiers can be used as the gain blocks. Consequently, power consumption and chip area can be minimized, and amplifier design is simplified considerably [l]. Only in the output stages of the circuit are buffered amplifiers, which have the ability to drive large off-chip load capacitances and small off-chip load resistances, included. In this last case, tight specifications on linearity, dynamic range, and stability result in complex amplifier configurations that consume a significant amount of chip area [2]-[4]. Under normal operating conditions, practical integrated analog or mixed-mode systems connect to the surrounding electronics through a limited number of analog nodes. However, many more nodes have to be monitored during testing and evaluation of the chip, and consequently these nodes have to be buffered too. Buffer specifications can be relaxed somewhat, since these internal nodes have to be accessible more to check the global functionality of the chip than to verify system performance. A very good example is a modem front-end IC, where the signal path may contain high-order switched capacitor filters, modulators, A/D converters, and other analog blocks. In case of system malfunctioning, curing the problem starts by gathering information on the signals at internal nodes. The most important specifications that apply to a test buffer for this type of applications are: a compact size, a broad bandwidth, a high dynamic range, and the ability to drive at least the 15-pF 100-k0 load of standard test equipment and probes. The input capacitance should be kept small, but in a high-frequency buffer it cannot be minimized without paying a price in bandwidth or stability, as is shown here. Indeed, the cutoff frequency fT of the input transistors and the buffer bandwidth BW are

Manuscript received January 20, 1988; revised September 29, 1988. This work was supported in part by the NATO Scientific Program. P. M. Van Peteghem is with the Department of Electrical Engineering. Texas A&M University, College Station, TX 77843. J. F. Duque-Carrillo is with the Department of Electrical Engineering, Texas A&M University, College Station, TX 77843 on leave from the Universidad de Extremadura, Badajoz. Spain. IEEE Log Number 8826145.

It is almost impossible to operate a CMOS circuit in a frequency range beyond 10 percent of the fT of the transistors that are active in its high-frequency signal path, and still have an accurate and predictable signal transfer [5]. For high-frequency CMOS circuits, the value of B will typically be around unity to assure stability. Hence, it will be difficult in high-speed buffers to reduce input capacitance, which is dominated by C&,, below 10 percent of Cload. a high-speed buffer implemented in a 3-pm For CMOS technology and a 15-pF capacitive load, minimal input capacitance is between 0.5 and 1 pF. This is sufficiently low to drive such a buffer by an amplifier output node, but it definitely prohibits measuring virtual-ground or other low-capacitance nodes. However, in most applications this is not a major restriction. In this paper, we present a simple 30-MHz CMOS buffer that has been integrated in the MOSIS 3-pm p-well CMOS process. In Fig. l(a) a circuit schematic is shown of the novel buffer amplifier. A microphotograph of the prototype circuit is shown in Fig. l(b). M1 and M2 form a differential pair, followed by the source follower M3. Transistors M4, M5, M 7 and M 8 form a PMOS current mirror; at low frequencies this current mirror enhances the loop gain, and minimizes the systematic mismatch in the differential input stage. Two capacitors are shown in this circuit. At high frequencies the capacitor C, shorts the PMOS current mirror by shorting transistor M4. The pole-zero pair that is introduced in this way is deliberately put lower than the gain-bandwidth product of the loop gain. Therefore the speed performance of the buffer at high frequencies depends only on the three NMOS transistors M1- M3 in this circuit. T h s makes it easier to maximize the bandwidth of this buffer. The compensation capacitor C, is introduced to obtain a stable and maximally flat gain up to high frequencies. It can be seen that C, shorts M1 at high frequencies, which reduces the buffer circuit to a cascade of two NMOS source followers. The simplified highfrequency circuit can, over a broad frequency range, be approximated by a three-pole, three-zero system, as described by (4). Only three capacitors contribute to a large extent to the poles of the circuit: C,,, Cc, and C,. The capacitor C, is the lumped sum of all capacitors that connect between the common-source point of the differential pair and ac ground. A large portion of C , consists of p-well capacitance, since both M1 and M2 are in a

0018-92OO/89/04OO-O540$01 .00 01989 IEEE

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.

24, NO. 2, APRIL 1989

541

VDD

I .... CL.3.16~ - CL= I Op - CL.3

I

1.6~

I

IHI

13

p1/100

PI

Frequency

1O.P I

(a)

CHIP 8 , 1 8

3 t

200 p m

-I0

1. E f 7

2.E+7

3.E+7

4.E+7

FREQUENCY

(Hz1

(b)

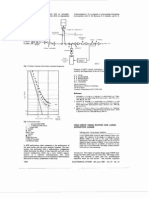

Fig. 2. (a) Calculated buffer gain as a function of frcqucncy, for three values of C,,. Frequency axis: normalized relative to the dominant pole pl. ( b ) Measured buffer gain for the integrated test circuit. as a function of frequency (slowest and fastest buffer in set of six test circuits).

(b) Fig. 1. (a) Circuit schematic of high-frequency CMOS output buffer. (b) Microphotograph of high-frequency buffer, integrated in the MOSIS 3-prn p-well CMOS process (active area: 0.18 m d ) .

Simulation

DC gain

Measurement

-0.2 dB

-0.1 t o -0.5 dB

Two of the poles of this buffer amplifier are defined by a quadratic equation; they are real for low values of the load capacitor C,.. In this case one of these poles cancels roughly with As a result, for low values of C,~,the the zero at s = buffer behaves as a one-pole low-pass filter with a pole p 1:

Ripple Ripple Bandwidth

3 dB Bandwidth

0.6 t o 2 dB

30 t o 38 MHz

2.4 dB 2 2 MHz 25 MHz

g,,,l/c.

Cin Settling to IX (t l V o l t signal) Dynamic Range Offset P o w e r Consumpt.

35 t o 43 MHz < I pF

- (*I

82 nsec

130 t o 150 nsec

> BO dB

< 30 mV

2 . 4 mA

> 77 dB

2 0 mV 2 . 4 mA

This implies that the bandwidth of this buffer can be optimized for small load capacitance by reducing the area of the p-well in which the input differential pair resides. For high values of C, two poles become complex, which can result in excessive overshoot in the step response. In between, there is one value for C, for which all three poles coincide; for the design shown in Fig. l(b) this corresponds to CL. =10 pF. For much larger values of C, the performance degrades. This is also clear in Fig. 2(a) which shows the simulated frequency response of the buffer for three values of C,. The experimental test circuit in Fig. l(b) has been integrated and tested; all measured data and the comparison with the simulation results are shown in Table I. The capacitive load for all measurements is about 15 pF, including the test probe. The measured gain of the test buffer is shown as a function of frequency in Fig. 2(b) for the fastest and slowest buffer in a set of

six samples. The gain is very flat up to about 5 MHz, but shows a 2-dB rise at about 18 MHz. The -3-dB bandwidth is about 25 MHz. The harmonic distortion products for a rf: 1-V sinusoidal output signal are shown in Fig. 3. Above 5 MHz, nonlinearity increases above the 1-percent level. Nevertheless, fast transients still can be monitored. The settling time to 1 percent for a k 1-V square wave is less than 82 ns, as measured with a HP54111D 1-GHz waveform recorder. The measured 10-90-percent transition times are even much faster: 30-ns fall time, 15-ns rise time. This means that sampled-data signals can be measured in a very accurate way, since the baseband signals (iMHz) are pro5 cessed in a linear way, with the low-level high-frequency transients superimposed on it.

542

IEEE JOURNAL OF SOLID-STATE CIRCUITS. VOL.

24, NO. 2, APRIL 1989

-30

- 40

Dist. (dB) -50

-60

-70

-80

100 kHz

I MHz Signal Frequency

10 MHz

Fig 3 Measured second and third harmonic distortion components of buffer as a function of frequency, for a k 1-V peak-to-peak sinusoidal input signal.

REFERENCES

[l] [2]

P. R. Gray and R. G. Meyer, Analvsis and Design of Anulog Integrated

Circuits. New York: Wiley. 1984. D. G. Maeding, A CMOS operational amplifier with low impedance drive capability. I E E E J . Solid-State Circuits. vol. SC-18. pp. 227-229, Apr. 1983. [3] K. E. Brchmer and J. B. Wieser, Large swing CMOS power amplifier, I E E E J . Solid-Stute Circuits, vol. SC-18. no. 6, pp. 624-629, Dec. 1983. [4] J. A. Fisher, A high-performance CMOS power amplifier, I E E E J . Solid-Srute Circuits. vol. SC-20, no. 6, pp. 1200-1205, Dec. 1983. [ 5 ] Y . Tsividis, Operurion arid Modeling of the MOS Trunsistor. New York: McGraw- Hill, 1986.

In typical MOS analog circuits such as switched-capacitor filters [2], [3] or charge-redistribution A/D converters [l],[4], the differential inputs of operational amplifiers or comparators are subject to momentary asymmetrical voltage stresses during their normal operation. In comparators, the magnitude of the stress can be as large as half the full-scale voltage of the A/D converter, while in operational amplifiers, it can be on the order of the supply voltage under slewing conditions. Charge-voltage hysteresis in MOS dielectrics can be caused by the drift of mobile ions [SI,and by dipolar or interfacial polarization [6]. However, the time constants associated with these mechanisms are too long for them to be a serious source of error in typical data converters or switched-capacitor circuits which are reinitialized on time scales of 1-10 ps. The tunneling of channel charge carriers to traps in the oxide, on the other hand, leads to a large dispersion of time constants which can cause hysteresis effects at frequencies of interest in a wide variety of circuit applications. There have been limited studies on MOS threshold-voltage hysteresis in the past. However, voltage, temperature, and time scales were far outside the normal operating range of modem integrated circuits [7]. In the present study, we examine threshold-voltage hysteresis due to oxide traps through its effect on the settling time of a differential amplifier operated at voltage and time scales relevant to typical analog integrated circuit applications. 11. THEORY

Traps located in the oxide close to the silicon-oxide interface can exchange carriers with the channel by tunneling. Electrons can either tunnel directly to oxide traps close to the conduction band or tunneling may occur via a two-step process in which THEODORE L. TEWKSBURY. MEMBER, IEEE, carriers first communicate with fast surface states at the HAE-SEUNG LEE, MEMBER, IEEE. A N D silicon-oxide interface and then tunnel at constant energy into GERALD A. MILLER, MEMBER, IEEE traps in the oxide, or vice versa [8]. Ahstruct -Hysteresis in the threshold voltage of MOSFETs due to When an NMOS transistor is stressed at high positive oxide traps can impose serious limitations on the accuracy and speed of gate-source voltage, the surface electron density increases and analog circuits. The measured magnitude of the input-referred hysteresis traps fill via the tunneling mechanisms. The bending of the oxide ranges from 100 pV to more than 1 mV in NMOS devices stressed with positive gate-source voltages ranging from 1 to 5 V on microsecond-to- bands lowers trap energy levels with respect to the silicon bands so that they may be filled by either of these two tunneling millisecond time scales. This hysteresis is explained by a model in which electrons tunnel to oxide traps close to the interface. mechanisms. When the stress is removed, the band returns to the normal I. INTRODUCTION position, and the traps can empty back into the silicon. However, Hysteresis in the threshold voltage of MOSFETs can limit the the rate at which traps empty is much slower than the rate at accuracy and speed of analog circuits that perform analog-to-dig- which they fill, because of the large difference in electron concenital and digital-to-analog conversion, amplification, filtering, and trations between filling and emptying processes. This asymmetry many other functions. Although the existence of such hysteresis in the rates at which traps fill and empty can cause hysteresis in was indicated in recent high-precision MOS analog circuits [l], the threshold voltage of MOSFETs. Although the hysteresis will no detailed measurement data have been available. In this paper, eventually decay as the traps empty, due to the long decay time we describe extensive measurements of the threshold-voltage (typically more than tens of milliseconds), the settling time of hysteresis in MOSFETs, under various conditions that emulate MOS circuits can be greatly affected. If an NMOS device is subjected to a large positive gate voltage the normal operation of MOS analog circuits. stress (i.e., a few volts), assuming acceptor type traps, the threshold voltage will increase. When the gate voltage returns to its Manuscript rcccived July 1 1988; revised November 4, 19XX. This work was . initial condition, the drain current will not respond immediately, supported by the National Science Foundation under Grant ECS-8505145 and but will show some overshoot which settles to its final value with by the Semiconductor Research Corporation under Grant 86-05-080. a long tail that persists during the time that the traps are T. L. Tewksbury and G. A. Miller are with Analog Devices Inc.. Wilmington. MA 01887. returning to their steady-state occupancy. H.-S. Lee is with the Department of Electrical Engineering, Massachusetts Regardless of whether the tunneling occurs primarily from the Institute of Technology, Cambridge, MA 02139. IEEE Log Number 8826143. conduction band or from fast surface states within the bandgap,

The Effects of Oxide Traps on the Large-Signal Transient Response of Analog MOS Circuits

0018-9200/89/0400-0542$01.00 01989 IEEE

S-ar putea să vă placă și

- Performance Very Low Frequency Filters: Design Considerations For HighDocument4 paginiPerformance Very Low Frequency Filters: Design Considerations For Highmvmuthukumar88Încă nu există evaluări

- 01012833, Technical PaperDocument4 pagini01012833, Technical Paperindresh.vermaÎncă nu există evaluări

- Sampling Theorem Verification: Electronics & Communication EngineeringDocument0 paginiSampling Theorem Verification: Electronics & Communication Engineeringagama1188Încă nu există evaluări

- MV - An E-Band Low-Noise Transformer-Coupled Quadrature VCO in 40 NM CMOSDocument9 paginiMV - An E-Band Low-Noise Transformer-Coupled Quadrature VCO in 40 NM CMOSsm123ts456Încă nu există evaluări

- Op Amp PaperDocument6 paginiOp Amp PaperSrinivasu IrlapatiÎncă nu există evaluări

- Ultra-Low Power Phase-Locked LoopDocument4 paginiUltra-Low Power Phase-Locked Loophawking1122Încă nu există evaluări

- D 119Document35 paginiD 119Mohammad Ayatullah MaktoomÎncă nu există evaluări

- 8 ModulationDocument8 pagini8 ModulationAhmadAkhbariÎncă nu există evaluări

- On-Die Decoupling CapDocument4 paginiOn-Die Decoupling CapBhupesh DasilaÎncă nu există evaluări

- Ultra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueDocument4 paginiUltra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueCamila DamascenoÎncă nu există evaluări

- Analysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionDocument12 paginiAnalysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionPraveen KumarÎncă nu există evaluări

- Paper LC Vco SohiniDocument5 paginiPaper LC Vco SohiniDr-Umakanta NandaÎncă nu există evaluări

- The Impact of Transistor Sizing On Power Efficiency in Submicron CMOS CircuitsDocument4 paginiThe Impact of Transistor Sizing On Power Efficiency in Submicron CMOS Circuitsramu143416305Încă nu există evaluări

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDocument5 paginiA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123Încă nu există evaluări

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocument4 paginiA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghÎncă nu există evaluări

- 40GHz Wide-Locking-Range Regenerative Frequency Divider and Low-Phase-Noise Balanced VCO in 0p18μm CMOSDocument3 pagini40GHz Wide-Locking-Range Regenerative Frequency Divider and Low-Phase-Noise Balanced VCO in 0p18μm CMOSMohamed Mostafa0% (1)

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 paginiA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010Încă nu există evaluări

- Design of Broadband Lumped Element BalunsDocument4 paginiDesign of Broadband Lumped Element BalunsA. Villa100% (1)

- A 2.4GHz Front-End With On-Chip Balun in A 0.13um CMOS TechnologyDocument3 paginiA 2.4GHz Front-End With On-Chip Balun in A 0.13um CMOS TechnologyphithucÎncă nu există evaluări

- A Novel Low-Power CMOS Operational Amplifier With High Slew Rate and High Common-Mode Rejection RatioDocument7 paginiA Novel Low-Power CMOS Operational Amplifier With High Slew Rate and High Common-Mode Rejection RatioJanon MitnickÎncă nu există evaluări

- Ambipolar Electronics: Xy3, mr11, Kmram @rice - EduDocument5 paginiAmbipolar Electronics: Xy3, mr11, Kmram @rice - EduKrishna PrasadÎncă nu există evaluări

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 paginiLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcÎncă nu există evaluări

- Low Swing Signaling Using A Dynamic Diode-Connected DriverDocument4 paginiLow Swing Signaling Using A Dynamic Diode-Connected DriverAkash RaykarÎncă nu există evaluări

- Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BPDocument16 paginiSwitched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BPmohamedÎncă nu există evaluări

- A 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanDocument4 paginiA 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanSunil PandeyÎncă nu există evaluări

- A Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsDocument4 paginiA Low Phase Noise Tri-Band LO Generation For Ku and E Band Radios For Backhauling Point-to-Point ApplicationsrinsonÎncă nu există evaluări

- A Comparative Study of CMOS LNAsDocument4 paginiA Comparative Study of CMOS LNAsMohammad Arif SaberÎncă nu există evaluări

- A Novel Robust Signaling Scheme For High-Speed Low-Power Communication Over Long WiresDocument6 paginiA Novel Robust Signaling Scheme For High-Speed Low-Power Communication Over Long Wiresavishekghosh1985Încă nu există evaluări

- A 2-10 GHZ Digital Cmos Phase Shifter For Ultra-Wideband Phased Array SystemDocument4 paginiA 2-10 GHZ Digital Cmos Phase Shifter For Ultra-Wideband Phased Array SystemHuy LuongÎncă nu există evaluări

- Daniel Proj 1997 Transcond AmpDocument15 paginiDaniel Proj 1997 Transcond AmpIbrahim MuhammedÎncă nu există evaluări

- S A A O N I S C A C: Imulation ND Nalysis F Oise N Witched Apacitor Mplifier IrcuitsDocument4 paginiS A A O N I S C A C: Imulation ND Nalysis F Oise N Witched Apacitor Mplifier IrcuitsSai KrishnaÎncă nu există evaluări

- Design of An Optical Receiver Using Transimpedance Amplifier With Light Detector and Equalization in MOS TechnologiesDocument4 paginiDesign of An Optical Receiver Using Transimpedance Amplifier With Light Detector and Equalization in MOS Technologiessurendiran123Încă nu există evaluări

- CMOS 1.8GHz VCODocument4 paginiCMOS 1.8GHz VCOsanjeevsoni64Încă nu există evaluări

- A 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS TechnologyDocument4 paginiA 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS Technologyfaithfully_fatihÎncă nu există evaluări

- Precision Constant Current Source For Electrical Impedance TomographyDocument4 paginiPrecision Constant Current Source For Electrical Impedance Tomographyjorgeluis.unknownman667Încă nu există evaluări

- Analysis of Ultra Wide Band Four stage Distributed Low Noise Amplifier in TSMC 0.18μm ProcessDocument8 paginiAnalysis of Ultra Wide Band Four stage Distributed Low Noise Amplifier in TSMC 0.18μm Processshowvan001Încă nu există evaluări

- 28.8 A 21dBm-OP1dB 20.3-Efficiency - 131.8dBm Hz-Noise X-Band Cartesian-Error-Feedback Transmitter With Fully Integrated Power Amplifier in 65nm CMOSDocument3 pagini28.8 A 21dBm-OP1dB 20.3-Efficiency - 131.8dBm Hz-Noise X-Band Cartesian-Error-Feedback Transmitter With Fully Integrated Power Amplifier in 65nm CMOSRAJAÎncă nu există evaluări

- Andre Carpenter 02072014 Tracked VersionDocument6 paginiAndre Carpenter 02072014 Tracked VersionnikhatskhanÎncă nu există evaluări

- A High-Speed Continuous-Time Bandpass VHF Filter in TechnologyDocument4 paginiA High-Speed Continuous-Time Bandpass VHF Filter in Technologyعاطف رضاÎncă nu există evaluări

- A 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM CmosDocument4 paginiA 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM Cmossohailasghar_tÎncă nu există evaluări

- Low Phase Noise, Very Wide Band Sige Fully Integrated VcoDocument4 paginiLow Phase Noise, Very Wide Band Sige Fully Integrated VcoSAMÎncă nu există evaluări

- A 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoDocument3 paginiA 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoAhmed ShafeekÎncă nu există evaluări

- A Complete Narrow-Band Power Line Communication Node For AMRDocument6 paginiA Complete Narrow-Band Power Line Communication Node For AMRSudheer KakaniÎncă nu există evaluări

- Active Capacitor Multiplier PDFDocument7 paginiActive Capacitor Multiplier PDFTridentBhattÎncă nu există evaluări

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDocument4 paginiA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyÎncă nu există evaluări

- Dheeraj ReportDocument15 paginiDheeraj ReportGirdhar Gopal GautamÎncă nu există evaluări

- Roychan's Sem 1 ReportDocument13 paginiRoychan's Sem 1 Reportroychan1012Încă nu există evaluări

- Bandwidth Enhacement by Inductor + Current FeedbackDocument14 paginiBandwidth Enhacement by Inductor + Current FeedbackSumant AroraÎncă nu există evaluări

- Conclusion:: To DiagnosticsDocument3 paginiConclusion:: To DiagnosticsDhaval PatelÎncă nu există evaluări

- 2011 IEEE Source Follower Based Track and Hold CircuitDocument4 pagini2011 IEEE Source Follower Based Track and Hold CircuitMuhammad Sohail Asst. ProfessorÎncă nu există evaluări

- A Low Power A - D Converter 05613669Document4 paginiA Low Power A - D Converter 05613669Romualdo Begale PrudêncioÎncă nu există evaluări

- A 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSDocument4 paginiA 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSburakgonenÎncă nu există evaluări

- Frequency DoublerDocument4 paginiFrequency DoublerprakashroutÎncă nu există evaluări

- Digitally Controlled Oscillator ReportDocument18 paginiDigitally Controlled Oscillator ReportVinidhra ShivakumarÎncă nu există evaluări

- Blind Paper SpineDocument5 paginiBlind Paper SpineJoao PauloÎncă nu există evaluări

- A Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterDocument4 paginiA Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterEldhose VargheseÎncă nu există evaluări

- Minimization of Redundant Internal Voltage Swing in Cmos Full-AdderDocument4 paginiMinimization of Redundant Internal Voltage Swing in Cmos Full-AdderAnonymous JnvCyu85Încă nu există evaluări

- Mmwave Submmwave SoC RFIT11Document4 paginiMmwave Submmwave SoC RFIT11workmanjÎncă nu există evaluări

- An 8-20-GHz Wide-Band LNA DesignDocument3 paginiAn 8-20-GHz Wide-Band LNA DesignNguyễn Trần TuấnÎncă nu există evaluări

- Static Earth Leakage Relay: An ISO 9001: 2008 CompanyDocument8 paginiStatic Earth Leakage Relay: An ISO 9001: 2008 CompanypitambervermaÎncă nu există evaluări

- Simetrix ManualDocument474 paginiSimetrix ManualRakesh SandarativjuÎncă nu există evaluări

- DC StarterDocument16 paginiDC StartergokulphdÎncă nu există evaluări

- VSX 808RDS RRV2115Document62 paginiVSX 808RDS RRV2115Milorad Paunovic100% (1)

- Contactor Selection GuideDocument6 paginiContactor Selection GuideJovimarkEncarnacionManzanoÎncă nu există evaluări

- Sharp 14T1 L PDFDocument45 paginiSharp 14T1 L PDFjulio625Încă nu există evaluări

- BPEG Reactors PDFDocument24 paginiBPEG Reactors PDFandre CÎncă nu există evaluări

- Digital Potentiometer Using Optical EncoderDocument3 paginiDigital Potentiometer Using Optical Encoderyu7bx2178100% (1)

- Computer MCQS General KnowledgeDocument2 paginiComputer MCQS General KnowledgeVikaz Nayyar50% (2)

- Wayne's Tinkering: Inexpensively Program Your Arduino Via BluetoothDocument8 paginiWayne's Tinkering: Inexpensively Program Your Arduino Via BluetoothJoey PeliasÎncă nu există evaluări

- Littelfuse Selecting An Appropriate Esd Device Application NoteDocument4 paginiLittelfuse Selecting An Appropriate Esd Device Application NoteluroguitaÎncă nu există evaluări

- Lesson 2 Constructional Features, Operating Principle, Characteristics and Specification of Power Semiconductor DiodeDocument31 paginiLesson 2 Constructional Features, Operating Principle, Characteristics and Specification of Power Semiconductor DiodeChacko MathewÎncă nu există evaluări

- Transistor Radio DX 7500 Bfg235Document7 paginiTransistor Radio DX 7500 Bfg235hurantiaÎncă nu există evaluări

- Noise Bridge Instructions PDFDocument3 paginiNoise Bridge Instructions PDFAnonymous Y4xaavvaÎncă nu există evaluări

- PLL WikipediaDocument8 paginiPLL WikipediaMonika SharmaÎncă nu există evaluări

- Discrete Output Relay Module: Specification SheetDocument2 paginiDiscrete Output Relay Module: Specification SheetdocrafiÎncă nu există evaluări

- Rectifier Probelems and SolutionsDocument11 paginiRectifier Probelems and SolutionsMichael Jerlit J EEEÎncă nu există evaluări

- DIY Metal DetectorDocument3 paginiDIY Metal DetectorsÎncă nu există evaluări

- What Is NanoelectronicsDocument5 paginiWhat Is NanoelectronicsPN VinodÎncă nu există evaluări

- Si 3402Document22 paginiSi 3402dirk13Încă nu există evaluări

- Characterization and Temperature-Dependent Conductivity of PolyanilineDocument7 paginiCharacterization and Temperature-Dependent Conductivity of PolyanilineBianca Beatrice BaștiureaÎncă nu există evaluări

- Low Dropout Linear Regulator: OUT OUTDocument24 paginiLow Dropout Linear Regulator: OUT OUTMr. GreenveeÎncă nu există evaluări

- I9-083G Novar 300Document16 paginiI9-083G Novar 300Rinda_Rayna0% (1)

- Multiphase Rectifier: ME (Industrial Electronics) - Part1Document42 paginiMultiphase Rectifier: ME (Industrial Electronics) - Part1Vrunda ShahÎncă nu există evaluări

- Csce 3303 - Fundamental MicroelectronicsDocument16 paginiCsce 3303 - Fundamental MicroelectronicsSameh SherifÎncă nu există evaluări

- Nexans MV Cables UK Brochure - 1Document48 paginiNexans MV Cables UK Brochure - 1Ra'fat HerzallahÎncă nu există evaluări

- Tda 6508 AddDocument43 paginiTda 6508 AddMukesh ThakkarÎncă nu există evaluări

- Different Types of Integrated CircuitsDocument4 paginiDifferent Types of Integrated Circuitsashvini patilÎncă nu există evaluări

- Practical Design of LCCDocument4 paginiPractical Design of LCCkarthiksmartÎncă nu există evaluări