Documente Academic

Documente Profesional

Documente Cultură

Control Methods and Compensation Characteristics of A Series Active Filter For A Neutral Conductor

Încărcat de

Osama NourDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Control Methods and Compensation Characteristics of A Series Active Filter For A Neutral Conductor

Încărcat de

Osama NourDrepturi de autor:

Formate disponibile

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO.

1, FEBRUARY 2007 433

Control Methods and Compensation Characteristics

of a Series Active Filter for a Neutral Conductor

Shigenori Inoue, Student Member, IEEE, Toshihisa Shimizu, Senior Member, IEEE, and

Keiji Wada, Member, IEEE

AbstractDue to the advance of information technologies, a

large number of electronic products such as personal computers

have been connected to power distribution systems in commer-

cial buildings. Hence, voltage distortion on utility outlets and

excessive neutral current on distribution lines have arisen and

lead to a number of serious problems in the distribution system.

Two control methods and the related compensation characteristics

of a series active lter connected to the neutral conductor are

presented in this paper. The distinct functions of the proposed

active lter are the mitigation of the third-harmonic voltage and

the neutral current in a three-phase four-wire distribution system

in a building. The required power of the proposed active lter is

less than 10% of that of the harmonic-producing loads. A control

method of the dc capacitor voltage on the active lter circuit is also

described. It is claried through experiments that one of the two

functions of the active lter can be realized selectively and the dc

capacitor voltage of the active lter can be regulated to a desired

value.

Index TermsHarmonic voltage distortion, neutral conductor,

series active lter, third harmonic.

I. INTRODUCTION

D

UE TO the advancement of information technologies,

a large number of computer products have been connected

to power distribution systems in commercial buildings. The ac-

to-dc front end of these kinds of electronic products uses diode

rectiers equipped with smoothing dc capacitors, which ow a

large amount of harmonic current into the utility line.

Especially on three-phase four-wire distribution systems,

the third-harmonic currents are increased. The excessive third-

harmonic currents cause overheating of the neutral conductors

[1]. In order to reduce the neutral current, a passive lter

connected in series with the neutral conductor [2], and the

shunt active lters and their control methods [3], [4], have been

proposed. The shunt active lters can mitigate not only third-

harmonic currents but also higher order harmonic currents.

An active lter connected in series with the neutral conductor

in order to mitigate the excessive neutral current has been

presented [5], [6].

Manuscript received July 30, 2004; revised June 22, 2005. Abstract pub-

lished on the Internet September 15, 2006.

S. Inoue and T. Shimizu are with the Department of Electrical Engineer-

ing, Tokyo Metropolitan University, Tokyo 192-0397, Japan (e-mail: shimizu@

eei.metro-u.ac.jp).

K. Wada was with the Department of Electrical Engineering, Tokyo Institute

of Technology, Tokyo 152-8552, Japan. He is now with the Department of

Electrical Engineering, Tokyo Metropolitan University, Tokyo 192-0397, Japan

(e-mail: kj-wada@center.tmu.ac.jp).

Digital Object Identier 10.1109/TIE.2006.885511

Fig. 1. Small-scaled model of a three-phase four-wire distribution system in

a building.

On the other hand, the voltage drop on both the distribution

transformers and the power cables caused by the third-harmonic

current results in the voltage distortion on utility outlets. A

stadium that experienced the problem was reported in [7]. In

this case, lighting equipment cuts out suddenly due to the third-

harmonic voltage in the three-phase four-wire distribution sys-

tem. However, few papers have reported the mitigation methods

of third-harmonic voltages on utility outlets.

The authors have already presented a series active lter in or-

der to mitigate the third-harmonic voltage on utility outlets [8].

The active lter is controlled to operate only for the third-

harmonic frequency, not producing any fundamental voltage.

Therefore, for the fundamental frequency, the active lter can

be regarded as a short circuit. The active lter, which consists

of a single-phase voltage-source inverter, is connected in series

with the neutral conductor. The required power of the active

lter is less than 10% of that of the harmonic-producing loads.

The active lter can mitigate either the third-harmonic voltage

or the neutral current on the three-phase four-wire distribution

system. Thus, there are two operating modes of the proposed

active lter. In this paper, the control methods for the two

operating modes are presented and veried through the ex-

perimental setup. Besides, a control method for regulating the

dc capacitor voltage and its characteristics is presented. Note

that this paper focuses on the three-phase balanced condition,

resulting in no fundamental neutral current owing through the

active lter.

II. SYSTEM CONFIGURATION

Fig. 1 shows the 3-kVA small-scaled model of a three-

phase four-wire distribution system in a building that is used

in theoretical analysis and experiments in this paper. Table I

0278-0046/$25.00 2007 IEEE

434 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 1, FEBRUARY 2007

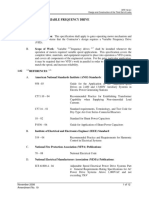

TABLE I

PARAMETERS OF THE CIRCUIT IN FIG. 1

shows the circuit parameters of this model. The model consists

of a Y step-down transformer, three nonlinear loads, and

an active lter. The nonlinear loads, each of which consists

of a diode rectier and a dcdc converter (Densei-Lambda

PH300H280-24), represent a number of computers and are

connected to each phase-to-neutral line. AC front-end circuits

in computers consume the required power regardless of the

ac-side voltage distortion. Then, the dcdc converters in the

model are controlled to consume a constant 2-kW active power.

A 0.86-mH (4.5%) inductor L

N

is added to the experimental

setup in order to simulate the inductance of a neutral conductor

of an actual distribution system in a building.

The active lter is connected in series with the neutral

conductor via a switching-ripple LC lter L

f

and C

f

and a

matching transformer (MT). A 100-F electrolytic capacitor

C

AF

is connected to the dc bus of the active lter. The imple-

mentation on the control circuit is executed by a DSP (Texas

Instruments TMS320VC33150 MHz).

III. METHOD OF THIRD-HARMONIC

VOLTAGE MITIGATION

A. Principle of Neutral Point Voltage and Third-Harmonic

Voltage Mitigation

Under balanced conditions, the third-harmonic component is

classied as a zero-sequence component. In this section, the

mitigation principle of the third-harmonic voltage is introduced

based on Fig. 2, which shows the zero-sequence equivalent

circuits of Fig. 1. In Fig. 2, the neutral current I

N

is assumed

to be an ideal third-harmonic current source because diode

rectiers equipped with dc capacitors behave as harmonic

current sources when the proposed series active lter mitigates

the third-harmonic voltage on the neutral point [8]. The active

lter is represented as an ideally controlled voltage source, and

R

S

and L

S

are the resistance and the leakage inductance of

the Y step-down transformer, respectively. V

N

is a phasor

expression of the neutral point voltage v

N

given by

v

N

=

v

La

+ v

Lb

+ v

Lc

3

(1)

where v

La

, v

Lb

, and v

Lc

are the utility outlet voltages on

each phase. The value of v

N

mainly means the third-harmonic

Fig. 2. Zero-sequence equivalent circuits when the neutral current is assumed

to be a current source. (a) Without an active lter. (b) With an active lter.

Fig. 3. Phasor diagrams explaining the neutral point voltage mitigation.

(a) Without an active lter. (b) With an active lter.

component contained in each phase voltage v

La

, v

Lb

, and v

Lc

.

Hence, the mitigation of v

N

results in the reduction of the third-

harmonic component in the utility outlet voltage.

Fig. 3 shows phasor diagrams of the voltages and currents

in Fig. 2. It should be noted that the angular frequency of those

phasors is the third-harmonic frequency contained in the utility

line voltage. The direction of each real axis in Fig. 3(a) and (b)

is set to the direction of the neutral current I

N

. The phase

difference between V

Z

and I

N

is expressed as

= tan

1

3

L

0

R

0

(2)

where R

0

= R

S

/3, L

0

= L

S

/3 + L

N

, and

3

(= 300[rad/s])

is the third-harmonic angular frequency. Control of the active

lter is performed on a rotating frame synchronized with the

third-harmonic frequency as explained in the next section. Each

value on the complex planes in Fig. 3 corresponds to the one on

the rotating frame, which is implemented in the controller of

the active lter in Fig. 4.

The voltage drop across the zero-sequence impedances V

Z

can be calculated as

V

Z

= (R

0

+ j

3

L

0

)I

N

. (3)

When the active lter is not installed, as shown in Fig. 2(a), the

neutral point voltage V

N

can then be obtained as

V

N

= V

Z

= (R

0

+ j

3

L

0

)I

N

. (4)

INOUE et al.: CONTROL METHODS AND COMPENSATION CHARACTERISTICS OF A SERIES ACTIVE FILTER 435

Fig. 4. Block diagram of the controller for the mitigation of third-harmonic

voltages at the utility outlet.

V

N

can be separated into two components V

Nd

and V

Nq

as

V

N

= V

Nd

+ jV

Nq

(5)

where

V

Nd

= R

0

I

N

V

Nq

=

3

L

0

I

N

. (6)

When the active lter is installed, as shown in Fig. 2(b),

the active lter generates a voltage given by

V

AF

= K

V

jV

Nq

(7)

where K

V

is the control gain of the active lter. The voltages

V

N

, V

Z

, and V

AF

comply with Kirchhoffs voltage law, and the

phasor diagram changes from Fig. 3(a) to Fig. 3(b). As a result,

V

N

is expressed as

V

N

= V

Nd

+ jV

Nq

=

R

0

+ j

3

L

0

1 + K

V

I

N

. (8)

It is clear that the larger the value of K

V

is selected, the higher

the performance of reducing V

N

can be achieved.

The complex power of the active lter P

AF

is calculated as

P

AF

= V

AF

I

N

= j

K

V

1 + K

V

3

L

0

I

2

N

. (9)

As can be seen, P

AF

becomes a pure imaginary number, so the

active lter needs no active power ow for the third-harmonic

voltage mitigation. Note that the active power owing into

or out of the active lter is used to control the dc capacitor

voltage v

C

, as explained in the following sections.

The active lter does not mitigate V

Nd

because mitigation

of V

Nd

requires the active lter to supply an active power of

I

N

V

Nd

= I

2

N

R

0

into the utility line. To avoid the expenses of

adding an external dc power supply to the dc bus on the active

lter inverter, excluding the compensation of V

Nd

is a cost-

effective solution from a production point of view.

B. Controller of the Active Filter for Third-Harmonic

Voltage Mitigation

Fig. 4 shows the controller of the active lter for the third-

harmonic voltage mitigation. The part above the dotted line in

Fig. 4 is the controller for the dc capacitor voltage explained in

the next section. Control of the active lter is performed on a

rotating frame synchronized with the third-harmonic frequency

(150 Hz).

The neutral point voltage v

N

is transformed into orthogonal

quantities v

N

and v

N

by a time-derivative element

v

N

v

N

3

d

dt

v

N

. (10)

The dq components v

Nd

and v

Nq

are transformed from v

N

and v

N

as

v

Nd

v

Nq

cos

3i

sin

3i

sin

3i

cos

3i

v

N

v

N

. (11)

The phase angle

3i

of the dq coordinates is obtained from

the third-harmonic component in the neutral current i

N

, so the

direction of the d-axis is equal to the direction of the neutral

current vector i

N

. The q-axis component of the third-harmonic

voltage v

Nq

is separated through a rst-order low-pass lter

with a cutoff frequency of 0.8 Hz. The q-axis output reference

voltage v

AFq

is calculated by amplifying v

Nq

by K

V

as

v

AFq

= K

V

v

Nq

. (12)

The d-axis output reference voltage v

AFd

is given by the con-

trol signal from the controller for the dc capacitor voltage. The

output reference voltage on the stationary frame v

AF

is obtained

from v

AF

= [v

AFd

, v

AFq

]

T

by using the dq inverse trans-

form. Pulse width modulation (PWM) signals for the active

lter inverter are generated by comparing v

AF

with a 10-kHz

triangular-wave signal.

C. DC Capacitor Voltage Control in the Case of

Third-Harmonic Voltage Mitigation

The voltage across the dc capacitor connected to the dc bus

of the active lter inverter needs to be regulated in order to

ensure proper operation of the active lter. The active lter can

charge the dc capacitor voltage by itself without an external

power supply. The dc capacitor voltage v

C

is obtained as

v

C

=

2

C

AF

p

AF

dt (13)

where p

AF

(= v

AF

i

N

) is the instantaneous power that the

active lter receives from the distribution system. Conventional

feedback control systems for v

C

have nonlinear control charac-

teristics, as shown in (13). Thus, the control system eases to fall

into an unstable operation. A useful solution to this problem is

the use of v

2

C

as a control variable instead of v

C

[9].

Control for the dc capacitor voltage is executed in Fig. 4

above the dotted line. Since the output voltage component to

control the dc capacitor voltage should be in phase with the

neutral current i

N

, then the output reference voltage on the

rotating frame should be the d-axis value v

AFd

expressed as

v

AFd

= K

C

v

2

C

v

2

C

(14)

436 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 1, FEBRUARY 2007

Fig. 5. Block diagram of the dc capacitor voltage control.

Fig. 6. Zero-sequence equivalent circuits when the neutral point voltage V

N

is assumed to be an ideal voltage source. (a) Without an active lter. (b) With

an active lter operated to behave as an inductor.

where K

C

is the proportional gain of the dc capacitor voltage

control.

Fig. 5 shows a block diagram of the feedback control system

of v

2

C

. In Fig. 5, the 300-Hz (= 2 150 Hz) ripple in the single-

phase instantaneous power p

AF

is ignored, and the rms value

of the neutral current I

N

is assumed to be constant despite

the operation of the active lter. Under these assumptions, the

control system becomes a linear rst-order system expressed as

F(s) =

V

2

C

(s)

V

2

C

(s)

=

1

1 +

C

AF

2K

C

I

N

s

. (15)

IV. METHOD OF NEUTRAL CURRENT REDUCTION

A. Principle of Neutral Current Reduction

Fig. 6 shows the zero-sequence equivalent circuits of Fig. 1

when the active lter reduces the neutral current. In Fig. 6,

the neutral point voltage V

N

is assumed to be an ideal third-

harmonic voltage source because the diode rectiers equipped

with dc capacitors behave as harmonic voltage sources when

the proposed series active lter operates in a way that increases

the impedance of the neutral conductor [10].

Fig. 7 shows the phasor diagrams of the voltages and currents

in Fig. 6. The direction of each real axis in Fig. 7(a) and (b) is

set to the direction of the neutral point voltage V

N

. Control of

the active lter is performed on a rotating frame synchronized

with the third-harmonic frequency as explained in the next

section. Each value on the complex planes in Fig. 7 corresponds

to the one on the rotating frame, which is implemented in the

controller of the active lter in Fig. 8.

When the active lter is not installed as shown in Fig. 6(a),

the neutral current I

N

is calculated as

I

N

=

V

N

R

0

+ j

3

L

0

=

R

0

j

3

L

N

R

2

0

+

2

3

L

2

0

V

N

. (16)

Fig. 7. Phasor diagrams explaining neutral current reduction. (a) Without an

active lter. (b) With an active lter.

Fig. 8. Block diagram of the controller for reduction of neutral current.

I

N

can be separated into two components, as shown in

Fig. 7(a), as

I

N

= I

Nd

+ jI

Nq

(17)

where

I

Nd

=

R

0

R

2

0

+

2

3

L

2

0

V

N

I

Nq

=

3

L

N

R

2

0

+

2

3

L

2

0

V

N

. (18)

In order to reduce the neutral current, the impedance of the

neutral conductor needs to be increased. Therefore, the active

lter has to operate as either a resistor or an inductor.

A mitigation method of the neutral current has been pro-

posed, in which a series active lter operates as a resistor for

the third-harmonic frequency [5]. However, this method may

result in excessive dc capacitor voltage because the active lter

receives an active power from the distribution system. Hence,

a method in which the active lter is operated as an inductor is

proposed, as shown in Fig. 7(b), in order to prevent the active

power ow.

To realize such inductive operation of the active lter, the

neutral current I

N

is measured, and the active lter generates

an output voltage of

V

AF

= jK

I

I

N

= K

I

(I

Nq

+ jI

Nd

). (19)

As the active lter has an effective inductive reactance of

[K

I

], the phasor diagram changes from Fig. 7(a) to Fig. 7(b),

INOUE et al.: CONTROL METHODS AND COMPENSATION CHARACTERISTICS OF A SERIES ACTIVE FILTER 437

and the neutral current I

N

is then given by

I

N

=

V

N

R

0

+ j(

3

L

0

+ K

I

)

. (20)

It is clear that the larger the value of K

I

is selected, the higher

the performance of reducing I

N

can be achieved.

The complex power of the active lter P

AF

is calculated as

P

AF

=V

AF

I

N

=jK

I

I

N

I

N

=j

K

I

R

2

0

+ (

3

L

0

+ K

I

)

2

V

2

N

. (21)

As can be seen, P

AF

becomes a pure imaginary number like

that in (9), so the active lter needs no active power ow for the

neutral current reduction. Note that the active power owing

into or out of the active lter is used to control the dc capacitor

voltage v

C

as explained in the following sections.

B. Controller of the Active Filter for Neutral Current

Reduction

Fig. 8 shows a controller of the active lter for the neutral

current reduction. The part above the dotted line in Fig. 8 is

a controller for the dc capacitor voltage explained in the next

section.

The neutral current i

N

is transformed into a dq vector

based on a time-derivative element and a dq transform. The

phase angle

3v

of the dq coordinates is obtained from the

neutral point voltage v

N

. The third-harmonic components in

the neutral current vector

i

N

= [

i

Nd

,

i

Nq

]

T

are separated by

two rst-order low-pass lters. The output reference voltage

for the neutral current reduction on the rotating frame v

AFI

=

[v

AFId

, v

AFIq

]

T

is given as

AFId

v

AFIq

= K

I

cos

2

sin

2

sin

2

cos

2

i

Nd

i

Nq

= K

I

i

Nq

i

Nd

.

(22)

C. DC Capacitor Voltage Control in the Case of Neutral

Current Reduction

Voltage control on C

AF

can be performed by generating

a voltage component in phase with i

N

. In order to achieve

control, the phase angle of i

N

, in other words, the direction of

the vector i

N

on the rotating frame, has to be calculated. The

output reference voltage for the dc capacitor voltage control on

the rotating frame v

AFC

= [v

AFCd

, v

AFCq

]

T

is given from the

control signal K

C

(v

2

C

v

2

C

) and the vector

i

N

as

AFCd

v

AFCq

= K

C

v

2

C

v

2

C

1

|

i

N

|

i

Nd

i

Nq

(23)

where

|

i

N

| =

i

2

Nd

+

i

2

Nq

. (24)

Note that the transfer function V

2

C

/V

2

C

is the same as (15).

Fig. 9. Experimental waveforms when the active lter is not activated.

The total output reference voltage on the rotating frame v

AF

is obtained by adding (23) to (22) as

v

AF

= v

AFI

+ v

AFC

. (25)

V. EXPERIMENTAL RESULTS

A. Third-Harmonic Voltage Mitigation

Fig. 9 shows experimental waveforms when the active lter

is not activated, and Fig. 10 shows the waveforms when the

active lter is operated to mitigate the third-harmonic voltage

at a gain of K

V

= 5. Note that dc capacitor voltage control

is performed with a reference of v

C

= 150 V and a gain

of K

C

= 1.0 10

3

V

1

in both Figs. 9 and 10. The load

rectiers consume a constant 2-kW active power, regardless of

the operating mode of the active lter.

In Fig. 10, the total harmonic distortion (THD) of the utility

outlet voltage v

La

is reduced from 13.3% to 5.3% by the third-

harmonic voltage mitigation. The phase current i

Sa

and the

neutral current i

N

are not changed, and the dc capacitor voltage

v

C

is regulated to around 150 V. The required power of the

active lter P

AF

is calculated from Fig. 10 as

P

AF

= V

AF

I

N

= 11 V 17.5 A = 192 VA. (26)

This value agrees well with the calculation result in (9) (which

is 220 VA) and is less than 7% of the load power (which is

3 kVA). This calculation was carried out by substituting I

N

=

17.5 A and the circuit parameters in Table I to (9).

Fig. 11 shows the relationship among the neutral point

voltage V

N

, the neutral current I

N

, and the gain K

V

. When

K

V

increases from 0 to 6, V

N

is reduced from 13.4 to 5.0 V.

However, setting K

V

to a value larger than 4 does not contribute

438 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 1, FEBRUARY 2007

Fig. 10. Experimental waveforms for an active lter at a gain of K

V

= 5

operating to mitigate the third-harmonic voltage.

Fig. 11. Relationship among V

N

, I

N

, and gain K

V

.

to the further mitigation of V

N

because the active lter can

mitigate only the q-axis component V

Nq

, and V

Nd

remains.

It is also noted that the neutral current I

N

remains nearly

constant at 17.5 A regardless of K

V

. This conrms the validity

of the assumption that neutral current is a current source, as

mentioned in Section III-A.

The optimal value of K

V

depends on the line impedance

and system stability. An excessively large value of K

V

does

not contribute to the third-harmonic voltage mitigation and may

cause unstable operation of the active lter.

B. Neutral Current Reduction

Fig. 12 shows experimental waveforms when the active lter

is operated to reduce the neutral current at a gain of K

I

= 6 ,

which is equal to the unit impedance (100%) of the system.

The dc capacitor voltage control is performed under the same

conditions as Figs. 9 and 10. In Fig. 12, the neutral current is

mitigated from 16.9 to 3.2 A by the active lter. Unfortunately,

the THD of the utility outlet voltage v

La

increases to 20.3%

Fig. 12. Experimental waveforms for an active lter at a gain of K

I

= 6

operating to reduce the neutral current.

Fig. 13. Relationship among V

N

, I

N

, and gain K

I

.

as the gain K

I

increases. In an actual distribution system, if

the voltage distortion becomes excessive, it may result in lower

dc voltages in diode rectiers or deterioration of control perfor-

mance of PWM or power-factor correction (PFC) rectiers. The

dc capacitor voltage v

C

is regulated to around 125 V despite the

rms value of the neutral current being suppressed. The required

power of the active lter P

AF

is calculated from Fig. 12 as

P

AF

= V

AF

I

N

= 19 V 3.2 A = 61 VA. (27)

This value agrees well with the calculation result in (21) (which

is 62 VA) and is almost 2% of the load power (which is 3 kVA).

The calculation was carried out by substituting V

N

= 22 V and

the circuit parameters in Table I to (21).

Fig. 13 shows the relationship among V

N

, I

N

, and K

I

. When

K

I

increases from 0 to 6 , I

N

is reduced from 16.9 to 3.2 A.

The neutral point voltage V

N

increases to 22 V at K

I

0.8

and is nearly constant when K

I

> 1 . This conrms the

validity of the assumption that the neutral point voltage is an

ideal voltage source, as mentioned in Section IV-A.

INOUE et al.: CONTROL METHODS AND COMPENSATION CHARACTERISTICS OF A SERIES ACTIVE FILTER 439

Fig. 14. Experimental waveforms when the two operating modes are alter-

nated smoothly.

The value of K

I

in this experiment was chosen to reduce

the neutral current as less as possible without making the

active lter unstable, and 6 (100% in per unit expression)

is sufcient to do so [11]. Practically, the value of K

I

should be

chosen to limit the neutral current within a regulation without

causing serious problems due to voltage distortion.

C. Smooth Transition Between the Two Operating Modes

Fig. 14 shows an example of experimental waveforms when

the two operating modes of the active lter are transited

smoothly from the third-harmonic voltage mitigation to the

neutral current reduction. This experiment is conducted under

a supposed situation where the state of the distribution system

changes and the operating mode of the active lter has to be

alternated. The dc capacitor of the active lter inverter C

AF

is

now 3600 F in this experiment.

First, both the gains K

V

and K

I

are set to zero. When K

V

increases from 0 to 6, and K

I

remains 0 , the active lter

begins to mitigate the neutral point voltage v

N

. Then, K

V

decreases from 6 to 0, and K

I

increases from 0 to 6 . At this

time, the operating mode of the active lter is changed, and

the active lter begins to reduce the neutral current i

N

. Finally,

the gain K

I

decreases to 0 , and the active lter stops the

harmonic compensation.

Neither surge voltage nor current occurred in the systemin all

the periods in Fig. 14, and it is claried that the active lter can

change its operating modes smoothly. Note that dc capacitor

voltage control is performed, and v

C

is maintained between 145

and 155 V in all the periods described above.

VI. CONCLUSION

Two operating modes of a series active lter connected in

series with the neutral conductors were presented. Operation

principles for the third-harmonic voltage mitigation and the

neutral current reduction were presented and evaluated through

the 3-kVA experimental setup.

In addition, an effective method of controlling the dc ca-

pacitor voltage of the active lter inverter was presented. The

proposed control system, in which the squared value of the

dc capacitor voltage is used instead of the voltage itself, was

conrmed to operate stably to regulate successfully.

REFERENCES

[1] T. M. Gruz, A survey of neutral currents in three-phase computer power

systems, IEEE Trans. Ind. Appl., vol. 26, no. 4, pp. 719725, Jul./Aug.

1990.

[2] T. Key and J. S. Lai, Analysis of harmonic mitigation methods for build-

ing wiring systems, IEEE Trans. Power Syst., vol. 13, no. 3, pp. 890897,

Aug. 1998.

[3] M. Aredes, J. Hfner, and K. Heumann, Three-phase four-wire shunt

active lter control strategies, IEEE Trans. Power Electron., vol. 12,

no. 2, pp. 311318, Mar. 1997.

[4] M. Ishihara, S. Mori, G. Nakagawa, and M. Nishitoba, Development

of active lter for three-phase four-wire system, presented at the IEEJ

Technical Meeting Semiconductor Power Converter, Kobe, Japan, 1996,

Paper SPC-96-128. (in Japanese).

[5] P.-T. Cheng, Y.-F. Huang, and C.-C. Hou, Design of neutral har-

monic mitigator for three-phase four-wire distribution systems, in Proc.

IEEE/IAS Annu. Meeting, 2001, vol. 1, pp. 164171.

[6] P.-T. Cheng, C.-C. Hou, and Y.-F. Huang, Overload prevention, IEEE

Ind. Appl. Mag., vol. 10, no. 6, pp. 2634, Nov./Dec. 2004.

[7] K. Sakai, K. Furuya, K. Mimura, and K. Mizuno, Development of third-

harmonic active lter for three phases four line, in Proc. IEIE Nat. Conf.,

2001, pp. 203204. (in Japanese).

[8] K. Wada and T. Shimizu, Mitigation method of third-harmonic voltage

for a three-phase four-wire distribution system based on a series active

lter for the neutral conductor, in Proc. IEEE/IAS Annu. Meeting, 2002,

vol. 1, pp. 6469.

[9] M. Saitou and T. Shimizu, A single-phase PWM rectier with dc power

active lter for fast dc output voltage control, presented at the IEEJ

Technical Meeting Semiconductor Power Converter, Kobe, Japan, 2001,

Paper SPC-01-106. (in Japanese).

[10] F. Z. Peng, Harmonic sources and ltering approaches, IEEE Ind. Appl.

Mag., vol. 7, no. 4, pp. 1825, Jul./Aug. 2001.

[11] H. Fujita and H. Akagi, An approach to harmonic current-free ac/dc

power conversion for large industrial loads: The integration of a series

active lter with a double-series diode rectier, IEEE Trans. Ind. Appl.,

vol. 33, no. 5, pp. 12331240, Sep./Oct. 1997.

Shigenori Inoue (S02) was born in Saitama, Japan,

in 1979. He received the B.S. and M.S. degrees

from Tokyo Metropolitan University, Tokyo, Japan,

in 2002 and 2004, respectively, both in electrical en-

gineering. He is currently working toward the Ph.D.

degree at the Tokyo Institute of Technology, Tokyo.

His research interests include medium-voltage

power conversion systems and next-generation pow-

er switching devices based on SiC and/or GaN.

440 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 1, FEBRUARY 2007

Toshihisa Shimizu (M93SM02) was born in

Tokyo, Japan, in 1955. He received the B.E., M.E.,

and Dr.Eng. degrees from Tokyo Metropolitan Uni-

versity, Tokyo, Japan, in 1978, 1980, and 1991,

respectively, all in electrical engineering.

In 1998, he was a Visiting Professor with the

Virginia Polytechnic Institute and State University

(Virginia Tech), Blacksburg. In 1980, he was with

Fuji Electric Corporate Research and Development,

Ltd. He joined the Department of Electrical Engi-

neering, Tokyo Metropolitan University, as an Asso-

ciate Professor in 1993 and has been a Professor since 2005. He has published

more than 40 journal papers, 60 international conference proceedings, and four

technical books. He holds ve patents and has more than ten patents pend-

ing. His research interests include power converters, high-frequency inverters,

photovoltaic power generations, UPSs, EMI problems, etc.

Dr. Shimizu is a member of the Institute of Electrical Engineers of Japan

(IEEJ) and the Japan Society of Power Electronics. He is also an At-Large

Member of the Administrative Committee of the IEEE Power Electronics

Society. He received the Transactions Paper Award from the Institute of

Electrical Engineers of Japan in 1999.

Keiji Wada (S98A00M02) was born in

Hokkaido, Japan, in 1973. He received the B.S. and

M.S. degrees from Polytechnic University, Kana-

gawa, Japan, in 1995 and 1997, respectively, and the

Ph.D. degree from Okayama University, Okayama,

Japan, in 2000, all in electrical engineering.

From 2000 to 2006, he was a Research Asso-

ciate with Tokyo Metropolitan University, Tokyo,

Japan, and Tokyo Institute of Technology, Tokyo.

Since 2006, he has been an Associate Professor

with Tokyo Metropolitan University. His research

interests include active power lters.

S-ar putea să vă placă și

- Ybus Matrix With Regulating Transformer - Self Study TopicDocument21 paginiYbus Matrix With Regulating Transformer - Self Study TopicSankar MuthuswamyÎncă nu există evaluări

- Zapi ControllerDocument86 paginiZapi Controllerlm100% (1)

- 26 29 23 - Variable Frequency DriveDocument12 pagini26 29 23 - Variable Frequency Drivejose aparicioÎncă nu există evaluări

- A Method To Reduce Neutral Current in Three Phase Four Wire Electric Distribution Systems by Using Active Power FilterDocument4 paginiA Method To Reduce Neutral Current in Three Phase Four Wire Electric Distribution Systems by Using Active Power FilterStedroy RoacheÎncă nu există evaluări

- Ripple Current Analysis of Three-Level Inverter Based On SVPWM and Design of LCL FilterDocument7 paginiRipple Current Analysis of Three-Level Inverter Based On SVPWM and Design of LCL FilterAnonymous eCmTYonQ84Încă nu există evaluări

- Carga Linear e Não Linear em Sistemas MonofásicosDocument5 paginiCarga Linear e Não Linear em Sistemas MonofásicosAlex PastickÎncă nu există evaluări

- Art CapaciteCompensationDocument5 paginiArt CapaciteCompensationserban_elÎncă nu există evaluări

- Multi Level Statcom For Harmonic ReductionDocument8 paginiMulti Level Statcom For Harmonic ReductionInternational Journal of Application or Innovation in Engineering & ManagementÎncă nu există evaluări

- Simulation of Grid Connected THIPWM-Three-Phase Inverter Using SimulinkDocument5 paginiSimulation of Grid Connected THIPWM-Three-Phase Inverter Using SimulinkAhmed JanadÎncă nu există evaluări

- 01413552Document8 pagini01413552Nalin Lochan GuptaÎncă nu există evaluări

- Yamada 2014Document11 paginiYamada 2014Bhargav ReddyÎncă nu există evaluări

- A Carrier-Based PWM Techniques Applied To A Three-Level Four-Leg Inverter For Use As A Shunt Active Power FilterDocument6 paginiA Carrier-Based PWM Techniques Applied To A Three-Level Four-Leg Inverter For Use As A Shunt Active Power FilterZellagui EnergyÎncă nu există evaluări

- Wcecs2009 - pp545-549 Computer LoadsDocument5 paginiWcecs2009 - pp545-549 Computer LoadsYogesh MsdÎncă nu există evaluări

- Transient Analysis of A Z-Source Inverter With An Asymmetrical Impedance NetworkDocument5 paginiTransient Analysis of A Z-Source Inverter With An Asymmetrical Impedance NetworkRudanekÎncă nu există evaluări

- Power System AnalysisDocument40 paginiPower System AnalysisAkhtarÎncă nu există evaluări

- 3 Phase Full Wave Bridge ConverterDocument4 pagini3 Phase Full Wave Bridge Convertersubhasishpodder100% (1)

- Model Predictive Current Control For High-Power Grid-Connected Converters With Output LCL FilterDocument6 paginiModel Predictive Current Control For High-Power Grid-Connected Converters With Output LCL FilterAndreeaÎncă nu există evaluări

- Dynamic Improvement of Induction Generators Connected To Distribution Systems Using A DstatcomDocument5 paginiDynamic Improvement of Induction Generators Connected To Distribution Systems Using A DstatcomVinod Kumar VudathaÎncă nu există evaluări

- A New Passive 28-Step Current Shaper For Three-Phase RectificationDocument8 paginiA New Passive 28-Step Current Shaper For Three-Phase Rectificationkishor reddyÎncă nu există evaluări

- Control Strategy For Three Phase PWM Rectifier Using SVM ModulationDocument7 paginiControl Strategy For Three Phase PWM Rectifier Using SVM Modulationeditor_ijtelÎncă nu există evaluări

- LCI Firing AngleDocument6 paginiLCI Firing AngleMuthamil KumaranÎncă nu există evaluări

- Lab2 Eeb 451Document6 paginiLab2 Eeb 451tetojogoldenboyÎncă nu există evaluări

- A Novel Three-Phase Three-Port UPS Employing A Single High-Frequency Isolation TransformerDocument7 paginiA Novel Three-Phase Three-Port UPS Employing A Single High-Frequency Isolation TransformerDaniel Oscar GarridoÎncă nu există evaluări

- Voltaje Source InverterDocument9 paginiVoltaje Source Invertercarra80Încă nu există evaluări

- Investigation of Harmonic Current Source Effects On Distribution and Transmission Lines Capacity and Losses: Case StudyDocument5 paginiInvestigation of Harmonic Current Source Effects On Distribution and Transmission Lines Capacity and Losses: Case Studyawan_krÎncă nu există evaluări

- PWM 2 Level and 3 LevelDocument7 paginiPWM 2 Level and 3 LevelnewrajasinghÎncă nu există evaluări

- Design Implementation of Power Filter: Hybrid ActiveDocument5 paginiDesign Implementation of Power Filter: Hybrid ActiveSpecial2424Încă nu există evaluări

- 20 The Essence of ThreePhase INTELEC2011Document28 pagini20 The Essence of ThreePhase INTELEC2011noreuÎncă nu există evaluări

- (C12) PDFDocument6 pagini(C12) PDFSuhendra Dwi ParanaÎncă nu există evaluări

- Ijert: Power Quality Improvement Using Instantaneous Power Theory Based Hybrid FilterDocument7 paginiIjert: Power Quality Improvement Using Instantaneous Power Theory Based Hybrid FilterJulio FerreiraÎncă nu există evaluări

- Active Filters With Control Based On The P-Q TheoryDocument8 paginiActive Filters With Control Based On The P-Q TheoryradhathotaÎncă nu există evaluări

- Modeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorDocument6 paginiModeling and Simulation of Frequency Converter Used in Speed Control of Asynchronous MotorLelosPinelos123Încă nu există evaluări

- Chen 1995Document6 paginiChen 1995أمين توات الجزائريÎncă nu există evaluări

- Virtual Instrument Based Fault Classification in Power Transformers Using Artificial Neural NetworksDocument5 paginiVirtual Instrument Based Fault Classification in Power Transformers Using Artificial Neural NetworksNituÎncă nu există evaluări

- IJIRAE:: Parallel Active Filter Modelling and Control Strategy For Harmonic EliminationDocument7 paginiIJIRAE:: Parallel Active Filter Modelling and Control Strategy For Harmonic EliminationIJIRAE- International Journal of Innovative Research in Advanced EngineeringÎncă nu există evaluări

- Department of Electronics & Communication: Aharaja Institute of Technology MysoreDocument8 paginiDepartment of Electronics & Communication: Aharaja Institute of Technology MysoreVinayaka KadampurÎncă nu există evaluări

- Measurement of Three-Phase Transformer Derating and Reactive Power Demand Under Nonlinear Loading ConditionsDocument8 paginiMeasurement of Three-Phase Transformer Derating and Reactive Power Demand Under Nonlinear Loading ConditionsSaurav KafleÎncă nu există evaluări

- Man Dache 2006Document5 paginiMan Dache 2006Radouan RadwanÎncă nu există evaluări

- Wilson Choo Chin Tze PHD ThesisDocument6 paginiWilson Choo Chin Tze PHD Thesis임광식Încă nu există evaluări

- Neutral Point BalancingDocument9 paginiNeutral Point BalancingLekha SejpalÎncă nu există evaluări

- Modeling and Simulation of A Three-Phase Inverter With Rectifier-Type Nonlinear LoadsDocument10 paginiModeling and Simulation of A Three-Phase Inverter With Rectifier-Type Nonlinear LoadsTuấn DũngÎncă nu există evaluări

- Inverter - Fault Current Contribution PDFDocument6 paginiInverter - Fault Current Contribution PDFbalaeee123Încă nu există evaluări

- Harmonic Reduction of Arc Furnaces Using D-Statcom: S.Pushpavalli, A. CordeliasumathyDocument8 paginiHarmonic Reduction of Arc Furnaces Using D-Statcom: S.Pushpavalli, A. CordeliasumathyIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalÎncă nu există evaluări

- Two Wattmeter MethodDocument11 paginiTwo Wattmeter MethodSARITHA SÎncă nu există evaluări

- Power Quality Improvement by UPQC Using ANN Controller: Saleha Tabassum, B.Mouli ChandraDocument6 paginiPower Quality Improvement by UPQC Using ANN Controller: Saleha Tabassum, B.Mouli ChandraKrishna Vasishta KavuturuÎncă nu există evaluări

- Pulse-Width Modulation For Electronic Power ConversionDocument18 paginiPulse-Width Modulation For Electronic Power ConversionPhạm Văn TưởngÎncă nu există evaluări

- Sample Paper - ICPCES 2010Document5 paginiSample Paper - ICPCES 2010ShwetaGautamÎncă nu există evaluări

- Chapter 2 DC Circuit TheoryDocument37 paginiChapter 2 DC Circuit TheoryTynoh MusukuÎncă nu există evaluări

- Influenta Regimurilor Deformante Asupra Incalzirii ConductoarelorDocument14 paginiInfluenta Regimurilor Deformante Asupra Incalzirii Conductoarelordimitriu47Încă nu există evaluări

- EG 232 Assignment 2 PDFDocument4 paginiEG 232 Assignment 2 PDFNalucha MukumbutaÎncă nu există evaluări

- University of Tripoli Faculty of Engineering Electrical and Electronics Engineering DepartmentDocument8 paginiUniversity of Tripoli Faculty of Engineering Electrical and Electronics Engineering DepartmentShehab RamadanÎncă nu există evaluări

- A Norton Model of A Distribution Network For Harmonic EvaluationDocument7 paginiA Norton Model of A Distribution Network For Harmonic Evaluationbubo28Încă nu există evaluări

- Detrimental Effects of Capacitors in Distribution Networks in The Presence of Harmonic PollutionDocument5 paginiDetrimental Effects of Capacitors in Distribution Networks in The Presence of Harmonic PollutionLuis CifuentesÎncă nu există evaluări

- PN2 06Document4 paginiPN2 06twinvbooksÎncă nu există evaluări

- Analog Electronic WattmetrDocument2 paginiAnalog Electronic WattmetrKaran AnejaÎncă nu există evaluări

- 87Document5 pagini87vinay kumarÎncă nu există evaluări

- Propogation of Unbalance in Electrical Power SystemsDocument5 paginiPropogation of Unbalance in Electrical Power SystemsNeethu EappanÎncă nu există evaluări

- Inductance Measurements For Synchronous MachinesDocument2 paginiInductance Measurements For Synchronous MachinesYusuf YaşaÎncă nu există evaluări

- Static Synchronous Series Compensator Using ADocument4 paginiStatic Synchronous Series Compensator Using ASai Bhargav VeerabathiniÎncă nu există evaluări

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesDe la EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesÎncă nu există evaluări

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlDe la EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlEvaluare: 5 din 5 stele5/5 (1)

- IGBT Overcurrent and Short Circuit Protection in Industrial Motor Drives PDFDocument6 paginiIGBT Overcurrent and Short Circuit Protection in Industrial Motor Drives PDFprathap394Încă nu există evaluări

- RC 1978 06Document46 paginiRC 1978 06Jan PranÎncă nu există evaluări

- 09b DesignDevConstructionofaLowCostAutomatic2KVAInvSyst PDFDocument13 pagini09b DesignDevConstructionofaLowCostAutomatic2KVAInvSyst PDFChela MaceasÎncă nu există evaluări

- Ib0600516engt FR Configurator2 INSTRUCTION MANUALDocument204 paginiIb0600516engt FR Configurator2 INSTRUCTION MANUALiuctmeÎncă nu există evaluări

- KM Standalone Solar PV GuidelinesDocument24 paginiKM Standalone Solar PV GuidelinesIrf NavaneethÎncă nu există evaluări

- Deck All MachineryDocument72 paginiDeck All Machineryrajishrrr100% (1)

- T Box Wind Power Generation: Vrushali Thok, Minal Kapgate, Prajkta Gawali, Shraddha Kolhe, Ankita SinghDocument6 paginiT Box Wind Power Generation: Vrushali Thok, Minal Kapgate, Prajkta Gawali, Shraddha Kolhe, Ankita Singhrahul.yerrawarÎncă nu există evaluări

- PWM Motor ControllerDocument44 paginiPWM Motor ControllerTrương Tuấn VũÎncă nu există evaluări

- Operating Instruction ZETADYN 3BFDocument194 paginiOperating Instruction ZETADYN 3BFReaper68Încă nu există evaluări

- 1 Comparison - of - Traditional - Inverters - and - Z - Source - Inverter - For - Fuel - Cell - VehiclesDocument11 pagini1 Comparison - of - Traditional - Inverters - and - Z - Source - Inverter - For - Fuel - Cell - Vehiclesramoha2514Încă nu există evaluări

- Edp 70Document163 paginiEdp 70iaward05Încă nu există evaluări

- Handbook UPS PDFDocument52 paginiHandbook UPS PDFJoni EfwanÎncă nu există evaluări

- LVDC Distribution SystemDocument52 paginiLVDC Distribution SystemAhmad TouqirÎncă nu există evaluări

- Motor Bearing Current PhenomenonDocument13 paginiMotor Bearing Current PhenomenonJose PradoÎncă nu există evaluări

- T.E. Electrical EngineeringDocument26 paginiT.E. Electrical EngineeringAshutoshBhattÎncă nu există evaluări

- Complete Seminar Report (11EEL19016 - DIMPAL SONI) PDFDocument45 paginiComplete Seminar Report (11EEL19016 - DIMPAL SONI) PDFDeepakSoni80% (5)

- Installation Standard For SPPDocument4 paginiInstallation Standard For SPPSagar ChandaranaÎncă nu există evaluări

- Harmonic Measurement and Analysis of Variable Frequency Drive (VFD) in IndustryDocument7 paginiHarmonic Measurement and Analysis of Variable Frequency Drive (VFD) in IndustrySPOOKY WARRIORSÎncă nu există evaluări

- Modeling of Switching and Conduction Losses in Three - Phase SPWM VSC Using Switching Function Concept-1Document6 paginiModeling of Switching and Conduction Losses in Three - Phase SPWM VSC Using Switching Function Concept-1oghaleudoluÎncă nu există evaluări

- Pe Lab ExperimentsDocument6 paginiPe Lab Experimentsramesh tÎncă nu există evaluări

- Current Source Inverter Fed Induction Motor Drives: A SurveyDocument14 paginiCurrent Source Inverter Fed Induction Motor Drives: A SurveyefrensaoÎncă nu există evaluări

- Silicon Controlled Rectifier: 600 VoltsDocument6 paginiSilicon Controlled Rectifier: 600 VoltsBruno GomesÎncă nu există evaluări

- Springer (IJ 6)Document11 paginiSpringer (IJ 6)Sherif M. DabourÎncă nu există evaluări

- By Reading and Using The Thesis, The Reader Understands and Agrees To The Following TermsDocument189 paginiBy Reading and Using The Thesis, The Reader Understands and Agrees To The Following TermsAlbert vallejos ariasÎncă nu există evaluări

- DIY Solar Projects - Eric SmithDocument161 paginiDIY Solar Projects - Eric SmithsezaitanyoluÎncă nu există evaluări

- Modeling of ABB Solar Inverters in Power System Simulations: Digital and AnalyticsDocument6 paginiModeling of ABB Solar Inverters in Power System Simulations: Digital and AnalyticsAlejandro Solis GomezÎncă nu există evaluări

- PE - Final TestDocument5 paginiPE - Final Testกรพัฒน์ เก่งพานิชÎncă nu există evaluări

- 4★★★★모듈레이터의 종류 - Fukuda - RF Sourced and Modulator (mainly for linac)Document79 pagini4★★★★모듈레이터의 종류 - Fukuda - RF Sourced and Modulator (mainly for linac)고석호Încă nu există evaluări