Documente Academic

Documente Profesional

Documente Cultură

Tema 1 - 4

Încărcat de

Elniño RoenTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Tema 1 - 4

Încărcat de

Elniño RoenDrepturi de autor:

Formate disponibile

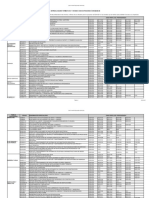

DESARROLLO E IMPLEMENTACION DE UN CIRCUITO INTEGRADOR, DIFERENCIAL E INVERSOR,CON AMPLIFICADOR OPERACIONAL LF356.

Dadas las condiciones tericas relacionadas, con las configuraciones bsicas con Op Amp tanto lineales como no lineales, se contina con el estudio del Op Amp. con la implementacin de circuitos con las configuraciones mas comunes referentes al trabajo del amplificador operacional .

Laboratorio de Electrnica III. Universidad Distrital Fco. Jos de Caldas. Bogot, 2002

El amplificador operacional deriva su nombre de una serie de fenmenos tcnicos que se hicieron evidentes tiempo despus de iniciados algunos desarrollos con este componente por la poca posterior a su invencin: los desarrolladores del integrado se percataron de las distintas funciones que poda desempear este amplificador con la conexin apropiada, por ejemplo, de algunos elementos pasivos tales como capacitores y resistores; entre esas funciones se encontraban algunas aplicaciones lineales como la suma y la resta, as como algunas no lineales, entre las que citamos la comparacin, la integracin y la diferenciacin. Algunas de estas configuraciones bsicas del Op Amp han sido tema de estudio, ante lo cual se proponen como objetivos de esta prctica . implementacion le los arreglos bsicos de los circuitos amplificadores, como son a saber, el integrador, diferenciador y sumador. Calcular y simular los efectos en la salida bajo la excitacin del circuito con las seales de la figura 1, a frecuencia de operacin 10KHz y Vpp = 1V, y comparar estos clculos con los resultados de la experiencia. Inicialmente se comienza este anlisis con la inclinacin a utilizar el Op Amp LF 356 ante el uA741c, ya que, si se tiene en cuenta que los circuitos que usaremos no estn bien compensados ante los errores del operacional, el primer amplificador tiene unos parmetros mas aceptables que los del segundo. Bajo estas premisas, continuamos con el estudio del Op Amp. con el anlisis de la funcin de transferencia propuesta, en lo referente a los circuitos bsicos que hacen parte del circuito final que implementa tal relacin y el clculo de las ganancias propuestas. CIRCUITO SUMADOR INVERSOR. Tal parece que el circuito a disear responde a una sola entrada, Vi ( t ) y que en cierto punto de bifurcacin, la seal atraviesa tres caminos distintos, ante los cuales sufre tres diversas transformaciones, cada una de las cuales corresponde a un sumando en la funcin de transferencia y que dadas estas transformaciones, las tres seales entran a un punto suma para as conformar la seal 1

Vo( t ). Es claro, por las condiciones que presenta la funcin que la excitacin Vi ( t ) se bifurca en tres caminos, en donde la seal de entrada es modificada; y estas tres modificaciones convergen a un punto suma final Un factor decisivo en la estabilidad de los pesos es la impedancia de salida Zo de los bloques en cada una de las ramas del sumador inversor, las cuales eventualmente se sumaran a la magnitud de las resistencias en cada rama, desviando las magnitudes calculadas para las ganancias. Por esta razn, una buena opcin sera colocar en cada rama un buffer a LF356. En buena medida, esto garantiza unas condiciones de acople que independicen a los pesos de Zo en la salida de cada bloque correspondiente. CIRCUITO INTEGRADOR. El tercer trmino de la funcin de transferencia es, como sigue: K3 " Vi( t ). El circuito integrador parece ser el indicado para generar modificacin de Vi( t ), circuito cuyo diagrama esquemtico y funcin se describen a continuacin: Vo ( t ) = 1/ RC [ " Vi( t ) dt ]+ K. K corresponde Vc en t = 0 . La conmutacin de JFET libra de carga al capacitor antes de iniciado el proceso de integracin. Cualquier potencial ms negativo que Vp y pondrn a conmutar a dicho transistor. Respecto a la ganancia que es igual a dos, remtase un momento a la ecuacin del integrador. Supngase que la entrada es un tren de pulsos de Vpp =1V a Fop= 10k. Por tanto el periodo de la seal es T=100Seg. Este es el esquema de la seal de entrada. La integracin de esta seal a lo largo de un periodo es: Vo( t ) = 1/ RC * " ( 0.5v )dt + 0V; se supone descargado el condensador. Vo( t ) = 1/ RC * 50 s * 0.5V. Necesariamente, y como es del comn, t = RC tiene unidades de tiempo, y 1/ RC * 50 s = 2. Entonces RC =25 s. R = 25K y C= 1nF. Con fines de compensacin, R+ se hace igual a R4. CIRCUITO AMPLIFICADOR INVERSOR. Con un amplificador inversor queda resuelta la cuestin con RF " 2.2K y R1 " 1K (digo " por aquello de las tolerancias), con lo que A " 2.2. Para compensar las entradas, Rp = RF || R1 " 680. CIRCUITO DIFERENCIADOR La ganancia directamente se obtiene de la magnitud del producto RC. Con los valores comerciales, se calcula R " 1.5K, C"100nF. Con lo anterior, se calcula una ganancia aproximada de 3. En la siguiente figura se ilustra el esquemtico del circuito, junto a la Rp de compensacin, y una resistencia en serie de c, que se calcula en un dcimo de R, y evita las oscilaciones causadas por el Slew Rate y limita la ganancia en baja frecuencia a " 10. +15V Switch

JFET nch. +15V 2.5K 25K 50s 100s 50s 0s 680 +15V +15V 1K 2.2K 1.5k! 100nF 150! 1.5k! 15V 15V

S-ar putea să vă placă și

- ESCALETADocument1 paginăESCALETAElniño Roen100% (1)

- Escribir Canciones PDFDocument18 paginiEscribir Canciones PDFfernar75Încă nu există evaluări

- Programa Energias RenovablesDocument109 paginiPrograma Energias RenovablesNilko CodalloÎncă nu există evaluări

- CATÁLOGO ELEMENTOS CONST-CAT-EC-v06.3 - Marzo - 10Document141 paginiCATÁLOGO ELEMENTOS CONST-CAT-EC-v06.3 - Marzo - 10Pau MargalloÎncă nu există evaluări

- Escribir Canciones PDFDocument18 paginiEscribir Canciones PDFfernar75Încă nu există evaluări

- Norma de IluminacionDocument10 paginiNorma de IluminacionElniño RoenÎncă nu există evaluări

- Capitulo XiiDocument8 paginiCapitulo XiiElniño RoenÎncă nu există evaluări

- Modelado robot móvilDocument10 paginiModelado robot móvilDiana ArciniegasÎncă nu există evaluări

- Mantenimiento ViDocument20 paginiMantenimiento ViMiguel Angel Galan CaballeroÎncă nu există evaluări

- Guia Rodamientos SKFDocument23 paginiGuia Rodamientos SKFCirilo Hernandez Ayala100% (1)

- Guia Rodamientos SKFDocument23 paginiGuia Rodamientos SKFCirilo Hernandez Ayala100% (1)

- Convert Id OresDocument4 paginiConvert Id OresElniño RoenÎncă nu există evaluări

- AmplificadoresDocument4 paginiAmplificadoresElniño RoenÎncă nu există evaluări

- Curso - Metod Transm SDHDocument210 paginiCurso - Metod Transm SDHArturo Geraldo100% (1)

- Guía 2. Párrafos de Desarrollo (Agosto)Document4 paginiGuía 2. Párrafos de Desarrollo (Agosto)Christian NovoaÎncă nu există evaluări

- Gestion para Establecimientos de Alimentos y BebidasDocument59 paginiGestion para Establecimientos de Alimentos y Bebidaslicetpatricia83% (6)

- Manual Motero de Mejoras: Gilera Yl 275 Gilera Yl 275 Gilera Yl 275 Gilera Yl 275Document31 paginiManual Motero de Mejoras: Gilera Yl 275 Gilera Yl 275 Gilera Yl 275 Gilera Yl 275patricia100% (2)

- Examen Nivel 1 Leccion 4Document7 paginiExamen Nivel 1 Leccion 4Juan Arturo Beltràn Sànchez42% (24)

- Actividad#10 HRRDSDocument3 paginiActividad#10 HRRDSHéctor De santiagoÎncă nu există evaluări

- Implementación de un SCADA con instrumentación virtualDocument15 paginiImplementación de un SCADA con instrumentación virtualRodrigoÎncă nu există evaluări

- Modelo de Acta de Entrega de CargoDocument2 paginiModelo de Acta de Entrega de CargoJean Carlos Vigo FiestasÎncă nu există evaluări

- Animatronics TabajoDocument3 paginiAnimatronics TabajoJose VillalobosÎncă nu există evaluări

- Unidad 4 InnovaciónDocument24 paginiUnidad 4 InnovaciónAbar MoncadaÎncă nu există evaluări

- CNOs Perfil Profesorado 2020-2021Document6 paginiCNOs Perfil Profesorado 2020-20211147forÎncă nu există evaluări

- GEA-24 - Resellers PRICE LIST JANUARY 2023.en - EsDocument1 paginăGEA-24 - Resellers PRICE LIST JANUARY 2023.en - EsRichard Enrriquez KanchiÎncă nu există evaluări

- 5 - Sistemas Digitales y RedesDocument2 pagini5 - Sistemas Digitales y RedesRodolfo LaimeÎncă nu există evaluări

- 56-Article Text-539-1-10-20191028Document16 pagini56-Article Text-539-1-10-20191028Darcy Huamán GonzalesÎncă nu există evaluări

- Guia 5 1 7 - ScrumdDocument9 paginiGuia 5 1 7 - ScrumdRodrigoÎncă nu există evaluări

- IO-Link Master EtherNet IP 8 PortsDocument4 paginiIO-Link Master EtherNet IP 8 PortscelectricÎncă nu există evaluări

- Phcopone XXXDocument2 paginiPhcopone XXXJulian muñozÎncă nu există evaluări

- Mapa conceptual sobre software y servicios de internetDocument3 paginiMapa conceptual sobre software y servicios de internetPatricia MBÎncă nu există evaluări

- Cuadro Comparativo de Los Métodos para Calcular La Raíz de Una EcuaciónDocument7 paginiCuadro Comparativo de Los Métodos para Calcular La Raíz de Una EcuaciónFernandoCifuentes100% (1)

- Loor Cabrera Leonor - Proyecto de GradoDocument26 paginiLoor Cabrera Leonor - Proyecto de GradoDaniela Dennysse Vega BenavidesÎncă nu există evaluări

- Conceptos de ProyectoDocument7 paginiConceptos de Proyectodcorcho1100% (2)

- Plantilla de Evidencias Modulo A Parte 1Document8 paginiPlantilla de Evidencias Modulo A Parte 1luisdepedroÎncă nu există evaluări

- ISO45001-PHVADocument5 paginiISO45001-PHVAFlavio Cesar Mamani SelgueronÎncă nu există evaluări

- Programacion Lineal EnteraDocument43 paginiProgramacion Lineal Enteraedwin fernando joya duarteÎncă nu există evaluări

- Práctica No 5-ELE1Document12 paginiPráctica No 5-ELE1Juan CarlosÎncă nu există evaluări

- Formato Sobredemanda 2019Document1 paginăFormato Sobredemanda 2019Román García0% (1)

- Investigacion 2 de Comercio AdministrativoDocument5 paginiInvestigacion 2 de Comercio AdministrativomariaÎncă nu există evaluări

- Examen Computación III - Tienda Mascotas OnlineDocument2 paginiExamen Computación III - Tienda Mascotas OnlineHERLIN HAMED LUDEÑA MORENOÎncă nu există evaluări

- KEMO Planeacion Didactica U1 2019 2 B1Document7 paginiKEMO Planeacion Didactica U1 2019 2 B1qwewd 123sdÎncă nu există evaluări

- 3 PrólogoDocument1 pagină3 PrólogoTiare Espinoza RiverosÎncă nu există evaluări