Documente Academic

Documente Profesional

Documente Cultură

RPT Instruction Plan

Încărcat de

Vishal KumarDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

RPT Instruction Plan

Încărcat de

Vishal KumarDrepturi de autor:

Formate disponibile

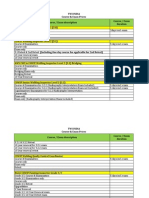

Lovely Professional University,Punjab

Format For Instruction Plan [for Courses with Lectures and Labs

Course No CSE211

Cours Title COMPUTER ORGANIZATION AND ARCHITECTURE

Course Planner 11471 :: Deepika Sukhija

Lectures Tutorial Practical Credits 4 0 0 4

Text Book:

Morris Mano,Title: Computer System Architecture,Publishers: Prentice Hall

Other Specific Book:

2 David A Patterson, Computer Architecture A Quantitative Approach, Pearson Education Asia. 3 4 5 P. Pal Choudhuri, Computer Organisation and Design, PHI, New Delhi Ali leigh, System Architecture, South Wester Publishing Co., New Delhi. Parallel Computers by Rajaram & Murthy, EEE

Other Reading Sr No Jouranls atricles as compulsary readings (specific articles, Complete reference)

Relevant Websites Sr. No. (Web adress) (only if relevant to the courses) 6 http://www.wisegeek.com/what-is-clock-speed.htm 7 http://computerconfiguration.org/ 8 http://www.diffen.com/difference/Mac_vs_PC 9 http://www.pcmag.com/article2/0,2817,2356818,00.asp 10 http://www.scribd.com/doc/52641020/15/ADDRESSINGMODES-EXAMPLES Salient Features This matter is required in lecture 45 This matter is required in lecture 45 A comparision of MAC vs PC Different features for laptop Material for chapter Central Processing Unit

11 http://search.proquest.com/pqcentral/docview/274376249/fullt Client-Server Computer Architecture Saves Costs and Eliminates Bottlenecks extPDF/130B6EF8A38E96990D/9?accountid=80692 1 Approved for Autumn Session 2011-12

12 http://search.proquest.com/pqcentral/docview/233974398/130 Competitive Advantage: Hardware selection: RISC vs CISC B6F85621271F312D/8?accountid=80692 13 http://search.proquest.com/pqcentral/docview/195582863/130 A transformation approach to derive efficient parallel implementations B6F85621271F312D/12?accountid=80692 14 http://web.ebscohost.com/ehost/viewarticle? Look-Ahead processors data=dGJyMPPp44rp2%2fdV0%2bnjisfk5Ie45PFKr6iuS7Kk63 nn5Kx94Km%2bT62osEewpq9Jnqy4TbawsUiet8s %2b8ujfhvHX4Yzn5eyB4rOvTLSst0muqK9JpOLfhuWz44ak2u BV36%2fmPvLX5VW%2fxKR57LOvSq%2brsk20qKR %2b7ejrefKz5I3q4vJ99uoA&hid=21 15 http://web.ebscohost.com/ehost/viewarticle? Cache Independent Algorithms data=dGJyMPPp44rp2%2fdV0%2bnjisfk5Ie45PFKr6iuS7Kk63 nn5Kx94Km%2bT62osEewpq9Jnqy4Tbews0%2bet8s %2b8ujfhvHX4Yzn5eyB4rOvTLSst0muqK9JpOLfhuWz44ak2u BV36%2fmPvLX5VW%2fxKR57LOyULCutEu2rqR %2b7ejrefKz5I3q4vJ99uoA&hid=14 16 http://web.ebscohost.com/ehost/viewarticle? A multi cluster architecture: Reducing processor cycle time through partitiong data=dGJyMPPp44rp2%2fdV0%2bnjisfk5Ie45PFKr6iuS7Kk63 nn5Kx94Km%2bT62osEewpq9Jnq24SLSwr1Get8s %2b8ujfhvHX4Yzn5eyB4rOvTLSst0muqK9JpOLfhuWz44ak2u BV4OvmPvLX5VW%2fxKR57LOwTK %2btsVGvnOSH8OPfjLvc84Tq6uOQ8gAA&hid=123

Detailed Plan For Lectures

Week Number Lecture Number Lecture Topic Chapters/Sections of Pedagogical tool Textbook/other Demonstration/case reference study/images/anmatio n ctc. planned

Part 1

Week 1 Lecture 1 Lecture 2 Review of Basics of Digital Electronics: Codes, logic gates Flip flops ->Reference :1, section 1.2(page 5 to7) ->Reference :1, section http://en.wikipedia.org/wi 1.6(page 24 to26) ki/Flip-flop_ %28electronics%29 ->Reference :1, section http://nptel.iitm.ac.in/cou 1.6(page 26 to29) rses/Webcoursecontents/IITKANPUR/esc102/node3 2.html

Lecture 3

Flip flops

Approved for Autumn Session 2011-12

Week 1 Week 2

Lecture 4 Lecture 5 Lecture 6 Lecture 7

Registers Counters Multiplexer, Demultiplexer Decoder and encoder

->Reference :1, section 2.4(page 50 to55) ->Reference :1, section http://en.wikipedia.org/wi 2.6(page 55 to59) ki/Counter ->Reference :1, section http://en.wikipedia.org/wi 2.3(page 47 to 50) ki/Multiplexer ->Reference :1, section http://www.ugrad.cs.ubc. 2.2(page 43 to 47) ca/~cs218/slides/2184.pdf ->Reference :1, section 3.2(page 74 to 77) ->Reference :1, section 3.3(page 77 to 82) ->Reference :1, section 1. 3.4(page 83 to 84) http://steve.hollasch.net/ cgindex/coding/ieeefloat .html 2. http://fourier.eng.hmc.ed u/e85 /lectures/arithmetic_html /node11.html

Lecture 8 Week 3 Lecture 9 Lecture 10

Signed Magnitude,1s,2s,rs complement Real numbers ( Fixed point ) Floating Point representation, IEEE754 representation)

Lecture 11

Register Transfer and Microoperations: Register transfer language, Register transfer, Bus & memory transfer Logic micro operation Shift micro operation

->Reference :1, section 4.1(page 93 to 102) ->Reference :1, section 4.5(page 108 to 113) ->Reference :1, section 4.6(page 114 to 116)

Lecture 12 Week 4 Lecture 13

Part 2

Week 4 Lecture 14 Lecture 15 Arithmetic Logic Shift Unit Basic Computer Organization: Instruction codes, computer instructions ->Reference :1, section 4.7(page 116 to 118) ->Reference :1, section http://web.cecs.pdx.edu/ 5.1(page 125 to 129) ~mperkows/CLASS_573 section 5.3(pg 134/573_2007/xx.pdf 137) ->Reference :1, section 5.4(page 137 to 141) ->Reference :1, section 5.5(page 141 to 146) Approved for Autumn Session 2011-12

Lecture 16 Week 5 3 Lecture 17

Timing and control Instruction cycles

Week 5

Lecture 18

Memory reference instruction

->Reference :1, section 5.6(page 147 to 152) ->Reference :1, section 5.7(page 152 to 159) ->Reference :1, http://spike.scu.edu.au/~ section 5.9(page 159 to barry/dp234/dp234166) t1.html ->Reference :1, section 7.1(page 215 to 218) ->Reference :1, section 7.1(page 215 to 218) ->Reference :1, section 7.2(page 218 to 222) ->Reference :1,section www.mediafire.com/? 7.2(page 218 to 222) jcl3olaxowc71w4 ->Reference :1,Section 8.2(pg 244-249) ->Reference :1,Section 8.3(pg 249-257) ->Reference :1,Section 8.4(pg 257-262) ->Reference :1,Section http://www.scribd.com/d 8.5(pg 262-267) oc/52641020/15/ADDRE SSING-MODESEXAMPLES

Lecture 19

Input/output & interrupts

Lecture 20

Design of basic computer

Week 6

Lecture 21

Control Unit: Hardwired vs. micro programmed control unit Control Memory Address Sequencing Microprogram Sequencer Central Processing Unit: General register organization Stack organization Instruction format Addressing Modes

Lecture 22 Lecture 23 Lecture 24 Week 7 Lecture 25 Lecture 26 Lecture 27 Lecture 28

MID-TERM Part 3

Week 8 Lecture 29 Lecture 30 Lecture 31 Central Processing Unit: Data transfer & manipulation Program control RISC, CISC ->Reference :1, section 8.6(pg 268-274) ->Reference :1, section 8.7(pg 275-284) ->Reference :1, section http://www.heyrick.co.uk 8.8(pg 284-290) /assembler/riscvcisc.htm l ->Reference :1, section 10.2(pg 336-342) ->Reference :1, section 10.3(pg 342-350) Approved for Autumn Session 2011-12

Lecture 32 Week 9 4 Lecture 33

Computer Arithmetic: Addition & Subtraction algorithm Multiplication algorithm

Week 9

Lecture 34 Lecture 35 Lecture 36

Division Algorithm Decimal arithmetic units Decimal Artithmetic Operations (addition, subtraction) Peripheral Devices, I/O interface

->Reference :1, section 10.4(pg 350-356) ->Reference :1, section 10.6(pg 365-371) ->Reference :1, Section 10.7 (page 371 -373) ->Reference :1, Section 11.1 11.2 (page 383-393)

Week 10

Lecture 37

Part 4

Week 10 Lecture 38 Data Transfer Schemes (Asynchronous) ->Reference :1, http://www.indiastudych Section 11.3 (page 393 annel.com/resources/10 -404) 1531-Data-TransferScheme-InMicroprocessor.aspx ->Reference :1, Section 11.4 (page 404 -409) ->Reference :1, Section 11.5 (page 409 -417 ->Reference :1, Section 11.6 11.7 (page 417-425) ->Reference :1, Section 12.4 (page 458 -464) ->Reference :1, Section 12.5 (page 464 -471) ->Reference :1, Section 12.6 (page 471 -478) Open House Discussion in class http://www.altera.com/pr oducts/ip/iup/memory/meur-dma-cont.html

Lecture 39

Program Control

Lecture 40

Interrupt

Week 11

Lecture 41

DMA, IOP

Lecture 42

Content Addressable Memory

Lecture 43

Cache Memory

Lecture 44

Virtual Memory

Week 12

Lecture 45

Units to measure computer speed; clock cycle; Factors effecting speed of computer; Configuration of computers available in market (desktop/laptop)

Approved for Autumn Session 2011-12

Week 12

Lecture 46

Pipelining, Flynns classification

->Reference :1, Section 9.1 9.2 (page 301-309

http://www-csfaculty.stanford.edu/~er oberts/courses/soco/proj ects/200001/risc/pipelining/index.h tml 1. http://smu.covertbay.co m/bt0068-5 2. http://www.scribd.com/d oc/22839152 /InterconnectionStructures

Lecture 47

Characteristics of multiprocessors, Various types of ->Reference :1, MIMD processors and Overview of interconnection Section 13.1 13.2 structures (page 491-502)

Lecture 48

Interprocesasor arbitration; Inter-processor communication & synchronization

->Reference :1, Section 13.3 13.4 (page 502-511)

Spill Over

Week 13 Lecture 49 Overview of Distributed Systems 1. http://www.computing.dc u.ie/~kpodesta/distribute d/ 2 .http://www.mithral.com/ projects/cosm/ch-02 .html Lecture 50 Massively Parallel Processors

Details of homework and case studies

Homework No. Objective Topic of the Homework Nature of homework (group/individuals/field work Individual Individual Evaluation Mode Allottment / submission Week 6/6 10 / 10

Test 1 Test 2

Student Evalutaion Test based on topics covered from Week 1 to Week 5 Student Evaluation Test based on topics covered from Week 6 to Week 9

Questions set in test paper questions set in test paper

Approved for Autumn Session 2011-12

Term Paper 1

To asses technical Topic as per Term Paper allotment list understanding of student about the subject

Individual

Written Report and Viva/Presentation

3/9

Scheme for CA:out of 100*

Component Test,Term Paper Frequency 2 Total :Out Of 3 Each Marks Total Marks 10 10 20 20

* In ENG courses wherever the total exceeds 100, consider x best out of y components of CA, as explained in teacher's guide available on the UMS List of suggested topics for term paper[at least 15] (Student to spend about 15 hrs on any one specified term paper) Sr. No. Topic 1 Analysis of Cache Memory Oraganization Schemes 2 Comparative Performance evaluation of i3, i5 and i7 processors 3 Comparisions of Different memories like ROM, PROM, EPROM, EAROM, RAM etc 4 Comparision of RISC and CISC 5 Analysis and synthesis of synchronous circuits 6 Asynchronous vs. Synchronous circuits 7 Memory Hierarchy 8 Case Study of Cray, X-MP multiprocessor 9 Parallel processing applications 10 Piplined processing units 11 Case study of MPP 12 Simulation of page replacement algorithms 13 Comparision of Intel and AMD processors 14 Processors with Parallel Architecture 15 Virtual Memory management in Windows/Linux

Approved for Autumn Session 2011-12

Approved for Autumn Session 2011-12

S-ar putea să vă placă și

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Project Planning Putting It All TogetherDocument25 paginiProject Planning Putting It All TogetherPedro Carranza Matamoros100% (1)

- Course 463 Aircraft Structural Repair For Engineers-Part IDocument2 paginiCourse 463 Aircraft Structural Repair For Engineers-Part IAE0% (2)

- Hausa Literature 1Document10 paginiHausa Literature 1Mubarak BichiÎncă nu există evaluări

- Student Needs AssessmentDocument4 paginiStudent Needs Assessmentapi-285240070Încă nu există evaluări

- Chapter 6 Assessment in Affective Domain FinalDocument37 paginiChapter 6 Assessment in Affective Domain FinalNoriel Aranza100% (2)

- (Sinica Leidensia) Doris Croissant, Catherine Vance Yeh, Joshua S. Mostow-Performing - Nation - Gender Politics in Literature, Theater, and The Visual Arts of China and Japan, 1880-1940-Brill AcademicDocument465 pagini(Sinica Leidensia) Doris Croissant, Catherine Vance Yeh, Joshua S. Mostow-Performing - Nation - Gender Politics in Literature, Theater, and The Visual Arts of China and Japan, 1880-1940-Brill AcademiclucuzzuÎncă nu există evaluări

- Korean SourcesDocument6 paginiKorean Sourcesgodoydelarosa2244Încă nu există evaluări

- Social Intelligence TheoryDocument5 paginiSocial Intelligence Theorymineasaroeun100% (1)

- Resume Elizabeth PretzerDocument3 paginiResume Elizabeth Pretzerapi-532076550Încă nu există evaluări

- Mechanical ForemanDocument7 paginiMechanical Foremanbook1616Încă nu există evaluări

- September 26 2023 1Document4 paginiSeptember 26 2023 1Aubrey DacerÎncă nu există evaluări

- Group3 Abm FinalDocument43 paginiGroup3 Abm Finalkiethjustol070Încă nu există evaluări

- India Course Exam PricesDocument6 paginiIndia Course Exam PricesElankumaran PeriakaruppanÎncă nu există evaluări

- Self-Diagnosis Table: Behavior Yes No X X X X X X X X X XDocument2 paginiSelf-Diagnosis Table: Behavior Yes No X X X X X X X X X XCarmen Maria CordovaÎncă nu există evaluări

- Why Adults LearnDocument49 paginiWhy Adults LearnOussama MFZÎncă nu există evaluări

- Untitled DocumentDocument8 paginiUntitled DocumentAkshat PagareÎncă nu există evaluări

- The Relationship Between Theoretical Concepts and ArchitectureDocument17 paginiThe Relationship Between Theoretical Concepts and ArchitectureHasanain KarbolÎncă nu există evaluări

- AFE8 Ad 01Document2 paginiAFE8 Ad 01UmarÎncă nu există evaluări

- Oral Communication in ContextDocument26 paginiOral Communication in ContextRoxanne LomandasÎncă nu există evaluări

- Designing Your Life - Stanford Life Design LabDocument7 paginiDesigning Your Life - Stanford Life Design LabnicÎncă nu există evaluări

- Call For Admission 2020 Per Il WebDocument4 paginiCall For Admission 2020 Per Il WebVic KeyÎncă nu există evaluări

- PURPOSIVE!!Document6 paginiPURPOSIVE!!junita ramirez50% (2)

- UJ FEBE Postgrad Yearbook 2016 FINAL PDFDocument51 paginiUJ FEBE Postgrad Yearbook 2016 FINAL PDFluke123456Încă nu există evaluări

- Lesson Planning and Classroom ManagementDocument4 paginiLesson Planning and Classroom ManagementMIFTAKHUL JANNAHÎncă nu există evaluări

- Personal Data SheetDocument4 paginiPersonal Data SheetPinoy Ziraniko VlogzÎncă nu există evaluări

- Evaluation-Form-LSCES Teambuilding Cum National Teachers DayDocument1 paginăEvaluation-Form-LSCES Teambuilding Cum National Teachers DayKRISTINE CALIXTONÎncă nu există evaluări

- AchievementsDocument4 paginiAchievementsapi-200331452Încă nu există evaluări

- How To Become An ICAEW Chartered AccountantDocument20 paginiHow To Become An ICAEW Chartered AccountantEdarabia.com100% (1)

- West Bengal State University: 1.answer Any Two Questions: 5x2 10Document3 paginiWest Bengal State University: 1.answer Any Two Questions: 5x2 10Cracked English with Diganta RoyÎncă nu există evaluări

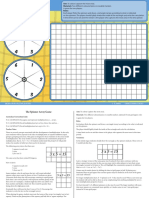

- Arrays GameDocument2 paginiArrays Gameapi-311154509Încă nu există evaluări