Documente Academic

Documente Profesional

Documente Cultură

12 Ti Miftakhutdinov Ibm Symposium 2011 Handouts

Încărcat de

coldwattDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

12 Ti Miftakhutdinov Ibm Symposium 2011 Handouts

Încărcat de

coldwattDrepturi de autor:

Formate disponibile

1

1

Post-PFC DC-DC Converter Design

Considerations to Meet Wide Load

Current Efficiency Goals

Rais Miftakhutdinov

Texas Instruments, High Performance Isolated Power,

South-East Design Center, Cary, North Carolina

r-miftakhutdinov1@ti.com

2011 IBM Power Technology Symposium

2

Outline

Energy Saving and Power Supply Efficiency related Standards

Benchmark Design Goals: Efficiency, Power Density, Cost

Phase-Shifted Full-Bridge Post-PFC Converter

Optimal Design Procedure and Power Saving Algorithm

Analog and Digital Controllers to meet Power Saving Goals

MathCAD and SIMPLIS based Design Tools

Prototype Example and Measured Performance

Summary

2

3

Strive for Efficiency and Power Saving

Telecommunication industry consumes 1% of electrical energy

worldwide that equals to 160 Billions kWh [1]

International Telecommunication Union (ITU) estimates that

Information and Communication Technology contributes 2.5% into

the worldwide greenhouse gas emission:

http://www.itu.int/themes/climate/events/cop16/sg.html

Worldwide movement for energy saving and Green power

generation and distribution, have resulted in number of voluntary

initiatives and mandatory regulations by international and

government organizations for increased efficiency of electronic

equipment including data and telecommunication power systems.

Examples of such organizations and initiatives are United States

ENERGY STAR program, German Blue Angel, Japan Environment

Association, European Code of Conduct and others [2].

USA Energy Star

German

Blue Angel

Japan

Environment

Association

European

Code of

Conduct

China Energy

Conservation

Project

Korea Energy

Management

Corp

CA Energy

Commission

4

Energy Star

for Server Power Supplies, ver. 1, May 15, 2009

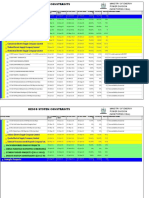

88% 92% 88% 80% > 1000 W

85% 89% 85% 75% > 500 1000 W

85% 89% 82% 70% 500 W

Single-Output (AC-

DC & DC-DC)

82% 85% 82% N/A

All Output

Levels

Multi-Output (AC-

DC & DC-DC)

100%

Load

50%

Load

20%

Load

10%

Load

Rated Output

Power

Power Supply Type

Energy Star

minimum efficiency requirements for

12-V output server power supplies at 10%, 20%,

50%, 100% load and 230 V AC line [7].

3

5

0.95 @

50% load

0.9 @

50% load

0.9 @

50% load

0.9 @

50% load

PF

91% 88% 85% 81% 100% load

94% 92% 89% 85% 50% load

90% 88% 85% 81% 20% load

80 PLUS and Climate Savers Computing

Climate Savers Computing initiative requires servers to

meet Energy Star

specification and the power supply to

be certified in accordance to 80 PLUS requirements.

[8] http://www.plugloadsolutions.com/80PlusPowerSupplies.aspx

[9] http://www.climatesaverscomputing.org/

6

Design Goals for Front-End Power Supply

Efficiency:

96.5% at half and 95.4% at full load for telecom rectifier

94% at half and 92% at full load for server power supply

Power Factor: 0.95 at half-load and full load

Power Density: >40 W/cub.inch

Cost per Watt: <10 cents/W

Design Cycle from Spec to Volume Production: < 8 Months

Facility

208V AC

AC/DC

(PFC)

DC/DC

12V DC (server)

-48V DC (rectifier)

PSMA Power Technology Road Map 2009: http://www.psma.com/

4

7

80+ Platinum Server Power Supply Efficiency Breakdown

0.95 0.95 0.90 0.80

Power

Factor

97.6

96.9

94

50%

97.7 96.4 95.3 PFC

94.4 95.8 92 DC-DC

92 91 85.7 AC-DC

100% 20% 10% Pout

Efficiency and Power Factor goals for Platinum Power Supply

Platinum 80+ requirements for server power

supply are most challenging. Below is efficiency

breakdown between PFC and DC/DC parts of Front-

End AC/DC server power supply

8

Post-PFC DC/DC Converter Topologies Comparison

Duty cycle range is limited

Difficult to maintain ZVS at

wide input voltage range

Mature ZVS topology for

one channel

Simple control and

minimum number of

components

Easy interleaving of any

number of channels

Scalable and efficient over

wide load current range

Interleaved Assymm. Half-

Bridge

Difficult for interleaving and

synchronization

Frequency control

Large ripple current through

capacitors

Non-trivial for optimal design

Short circuit issue

At wide input voltage range

the efficiency degrades

because of circulating

current during the

freewheeling stage

-

ZVS and ZCS of major

switches

Lower rated voltage Sync

FETs

Highest efficiency at

maximum Vin, which is good

for post-PFC converter

Low EMI

Mature ZVS topology

Interleaving capability

Improved modifications

available using the same

control

Fixed frequency PWM

Can be designed to

operate in different power

saving modes

+

LLC Converters Phase-Shift Full Bridge

5

9

Phase Shifted Full Bridge Converter

Soft switching (ZVS)

No snubbers on primary side

High frequency

Highest efficiency

Low EMI while ZVS is maintained

Complex control

10

Considerations for Highest Efficiency over Whole Load Range

- Vout +

12V

Vin

330V to 380V

(420V peak)

+

_

Q1

Q11

Q22

Q2

Q3

Q4

Llk=10H

L=736H

Rpr=37.8m

24T

1T 1T

Tr

Co = 8,000F

Q1, Q2, Q11, Q22: IPB50R250CP, Rdson=0.22 typ.

Q3, Q4: 3 in parallel

each,

IRF7749L2TRPbF

Rdson =1.1m

A B

Coss

Coss

Coss

Coss

Optimal ratio between conduction and

switching losses while FETs selection

Primary FETs with low Coss

Transformer with optimal turns ratio,

Ls and L to achieve ZVS

Synchronous rectification on

secondary side

Adaptive optimal switching timing for

all primary and secondary FETs

Optimal output inductor to set

boundary between CCM and DCM mode

Optimal light load management

algorithm

[3][6]

6

11

Optimal Design Procedure

Select ZVS allowing topology and number of channels based on

efficiency design goals and output power level

Optimize maximum efficiency point location where switching and

conduction losses ratio are equal and select power switches and

magnetics accordingly

Find optimal Ls and L to maintain ZVS over entire load current range

Identify optimal DCM, Diode rectification and Burst mode regions, and

phase shedding boundaries if multi-channel topology is selected

Estimate optimal switching timing for all FETs as function of operating

conditions

Design cycle might take few iterations, so the use of design support

software is very helpful

12

Optimal Pcond/Psw Selection with MathCAD

Dots show efficiency design goals

Pcond low, Psw high

Pcond & Psw optimal

Pcond high, Psw low

Optimal light load

management in

this region

7

13

Optimal Light Load Management

Moving into DCM mode, sync. FETs in diode emulation mode, D significantly

depends on load

0 1 2 3 4 5 6 7 8 9 10

0

0.2

0.4

0.6

0.8

Vsmin

Vsmax

Load Current, A

D

u

t

y

C

y

c

l

e

Setting Dmin=15.6%

Burst Mode Area

The region below DCM is identified where the diode emulation is maintained

Diode rectification region is where synchronous MOSFETs drive losses become burden

At very light current it is beneficiary to operate in burst mode to reduce power losses

even further. Simplest way to operate in burst mode is by limiting minimum duty cycle

Diode rectification

mode

14

Power Saving Control Algorithm vs Load Current

Nominal Operation at Io from 20 to 100%

Transition Mode at Io from 10 to 20% by

gradually reducing synchronous FETs

conduction time

Diode rectification with DCM at Io <10%

Burst Mode at no-Load or very light load

8

15

Suggested Optimal Power Management Algorithm

16

UCC28950 Phase-Shifted Controller Utilizing Power Saving Algorithm

Accurate, adaptive ZVS

timing over wide operating

range as function of current

sensing signal

MOSFET Rectifier Outputs

synchronized with primary

switching as function of

current sensing signal

Light Load Power

Management Block

Vin

+

_

Vout

+

_

Enable

UCC28950

Vdd

Vdd

Vdd

Vdd

CT

Vdd

SYNC

QA

QB

QC

QD

QE QF

18

19

OUTE

4

RSUM

6

3

7

20

1

2

21

5

22

23

24

COMP

SS/EN

SYNC

VREF

TMIN

VDD

OUTA

OUTC

OUTD

OUTB

GND

EA+

DELCD

9

8

15

16

17 DELEF

EA-

CS

ADEL

ADELEF

OUTF

DELAB

DCM

10

11

12 13

14

RT

A

A

B

C

D

E

F

B

C

D

E F

Vsense

Vsense

VREF

VREF

[12]

9

17

UCC28950 Block Diagram Employing Green Features

- 20% Accurate Adaptive ZVS Dead Band Over

Wide Operating Range

- Adaptive Timing MOSFET Rectifier Outputs

- Programmable SR ON/OFF Control

- Programmable Burst Mode at Very Light

or No Load

- Programmable Slope Compensation

- Peak Current or Voltage Mode Control

- 20-mA, 1.5% Accurate VREF Regulator

- Closed Loop Soft Start with Enable

- 8% Accurate Switching Frequency Setting

- Bi-directional Synchronization

- 3% Accurate Cycle-by-Cycle Current Limit

- V

DD

Under Voltage Lockout

- Thermal Shutdown

- 150 A Start Up Current

- Standard TSSOP-24 Package

- Wide Temperature Range: -40 to 125 C

8

10

4

13

2

1

12

GND

VREF

VDD

5V LDO

EN

UVLO

Comp.

7.3V rise

6.7V fall

VDD

VDD

RT

Cycle-by-

Cycle Ilim

SS/EN

Thermal

Shutdown

Is

OUTB

OUTA

Logic

Block

CLK

COMP

EA-

RSUM

4

8

10

OUTD

OUTC

VDD

Reference

Generator

8

DELAB

8

DELCD

Programmable

Delay CD

Programmable

Delay AB

PWM COMP

RAMP

4 EA+

4

CS

Ramp

Summing

4

Oscillator

8

10

OUTF

OUTE

8

DELEF

Programmable

Delay EF

8

ADELEF

10

ADEL

SYNC

4

2 V

Light Load

Efficiency

Block

DCM TMIN

Soft Start & Enable

with 0.55 V Thershold

Synchronization

Block

ON/OFF

CS

CS

CS

CS

CS

0.8V

2.8V

Lower + Input is

Dominant

[12]

18

Digital Controller UCD3K PSFB + Sync-Rec Configuration

10

19

Digital Controller C2000 PSFB + Sync-Rec Configuration

Secondary Side

Controller

Piccolo-A

Comp

ADC

P

W

M

Q11

Q1

Q2

Q8

Q7

Q13

Q14-Q15

Secondary Side

Controller

Piccolo-A

Comp

ADC

P

W

M

Secondary Side

Controller

Piccolo-A

Comp

ADC

P

W

M

Q11

Q1

Q2

Q8

Q7

Q13

Q14-Q15

20

MathCAD Program to Design Phase-Shifted Converter

Designer enters key spec requirements: Input/Output, Efficiency etc.

Program defines optimal ratio between switching and conduction losses

Program sets Rdson limits for primary and secondary FETs

Defines ZVS boundaries and suggests Ls and L values to achieve ZVS

Calculates efficiency and power losses to compare with design goals

Provides power losses budget for further optimization if needed

Generates basic waveforms for voltages and currents through power

stage components

What it does:

11

21

MathCAD Includes non-linear Coss Model to predict ZVS

Coss 63pF = Voss 100V =

E Vds ( )

Coss

2.9

Voss

2

ln

Vds 5 V +

V

|

\

|

|

.

43 pF Vds

2

2

+ := - analytical equation for Coss energy of IPB50R250CP

Analytical plot versus DS

0 50 100 150 200 250 300 350 400 450 500

0

1

2

3

4

5

6

7

E Vds ( )

J

Vds

Left plot shows that analytical equation based curve used in

MathCAD follows the data sheet plot based on experimental data

22

SIMPLIS Model of Phase-Shifted Converter

Allows top level simulations of phase shifted full-bridge Dc-Dc

converter

Provides behavioral model for most functions and features of

UCC28950 controller

Simulates transitions between different operating modes:

CCM, DCM, Burst Mode

Simulation time is relatively short: For example full soft start

simulation takes 6 min to 10 min depending on power stage

configuration

Provides small signal frequency response Bode plots

What it does:

12

23

SIMPLIS Model for Power Stage

Node A

OUTC

U8

RTN

VDD

U7

RTN

VDD

U6

RTN

VDD

U5

RTN

VDD

VDD

U4

RTN

OUTF

OUTE

DCM

DCM

S1

11.5

V2

OUTF

VQ3

C4

6.8n IC=0

R13

18.2k

Q7

FDP047AN08A0

Q8

FDP047AN08A0

Q2 Q1

12

V1

Vref

20p IC=0

C5

R37

10k

R38

40k

R35

50k

R24

360k

Vref

IQ4

IQ1

R

4

2

3

0

u

IIN

E2

208m

R47

2.2

R40

2.2

R36

2.2

C21

100p IC=0

R70

1K

R67

910

R64

39

C19

10n IC=0

R61

2k

R60

68k

C17

470p IC=0

C16

4.7n IC=0

R54

7.5k

R57

18.2k

Q6

STP20NM60FP

Q5

STP20NM60FP

Q4

STP20NM60FP

R9

4.7

C7

1u IC=0

C3

1u IC=0

R5

4.7

Vprimary

TX3

R10

10k

R16

R19 12

R2

12

R12

R14

10k

R11

10k

OUTC

OUTA

R1

120

Vout

X1

1:50 F1

20m

L1

8.7u IC=0

R6

5m

R8

6m

4.15mIC=0

C1

L2

4.8u IC=0

380

V4

R3

2m

R17 12

R23

R26

R25

12

OUTC

OUTD OUTB

R7

10k

TX2

ILS

Q3

STP20NM60FP

C10

6.8n IC=0

Vref

R55

4.3k

C18

10n IC=0

R63

2k

D1n4148

D1

R65

10k

C20

470p IC=0

D1n4148

D2

R71

5.11k

R44

2.2

ILo

ILu

P1 S1

S2

TX4 800u

L4

R

1

5

3

7

.8

m

R

1

8

2

2

0

u

IQ2

IQ3

VDD

R22

144k

R21

144k

R20

1.44

R27

1k

R30

10Meg

R34

10k

R33

1

R31

10Meg

U13-VIN

R29

1

1u IC=0

C2

VDD

300n IC=0

C6

CS

U1 OUTA

OUTB

DELAB

OUTC

DELCD

OUTD

DELEF

OUTE

OUTF

VDD

GND

VREF

SYNC

RT

ADEL

DCM

CS

TMIN

RSUM

ADELEF

SSEN

EAP

EAN

COMP

VQ4

OUTE

U2

DCM

U3

RTN

VDD

OUTA OUTB

OUTD

Node B

[12]

24

Phase-Shifted Converter Design Example

Input voltage: 300V to 400V

Output voltage: 12V

Output current: 55A

Efficiency: up to 95.5%

Includes bias supply and fan

Size of DC/DC converter portion only: 10 x 2 x 1

Power Density 36W/cub. Inch

Overall size: 15 x 2 x 1.6

[3]

13

25

Phase-Shifted Converter Picture

Bias Supply

Fan

Power Stage

Control Card

DC/DC Converter Portion Size: 10 x 2 x 1

26

Power Stage Schematic

14

27

Control Card Schematic

28

Measured Efficiency of 660W Phase-Shifted Converter Using UCC28950

0 5 10 15 20 25 30 35 40 45 50 55

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Vin = 400Vwit h Lres

Vin = 350Vwit h Lres

Vin = 300Vwit h Lres

Load current, A

E

f

f

ic

ie

n

c

y

,

%

Small difference between efficiencies at different input voltages indicate

minimum switching losses of this design

Efficiency curve is flat over wide load current range because of light load

power management technique

15

29

Summary

Power Saving and Efficiency Design Goals for Post-PFC

Converter have been set based on Standards and Regulations

PSFB Converter efficiency enhancing technique over entire

load current range has been discussed

Analog and Digital controllers capable to utilize optimal power

saving algorithm have been listed

MathCAD and SIMPLIS based design tools have been

introduced and test results of prototype have been presented

30

Thanks and Any Questions?

16

31

References

REFERENCES

1. Fasullo, G.; Kania, M. & Pitts, A. (2008). The Green revolution in DC power systems, Proceedings of 30th International

Telecommunications Energy Conference, INTELEC2008, pp. 1-7, ISBN: 978-1-4244-2056-8, San Diego, CA, USA,

September 2008, IEEE

2. Mammano, R. (2006). Improving power supply efficiency - The global perspective, Texas Instruments Power Supply

Design Seminar, Topic 1, SEM-1700, 2006

3. Rais Miftakhutdinov, Power Saving Control Strategies and Their Implementation in DC/DC Converter for Data and

Telecommunications Power Supply, Proc. of IEEE Applied Power Electronics Conf., 2010, pp. 1897-1903.

4. Rais Miftakhutdinov, Zhenyu Yu, New Controller Addresses Energy Saving in Server Power System, Power Systems

Design North America, January/February Issue, 2010, pp. 51-52.

5. Rais Miftakhutdinov, Power Saving Solutions in DC/DC Converter for Data and Telecommunications Power System, Proc.

of PEDS-2009, Taipei, November 2009.

6. Rais Miftakhutdinov, Energy Saving Drives New Approaches to Telecommunications Power System, Chapter in the book

Telecommunications, Intech, 2010

7. ENERGY STAR program requirements for computer servers, version 1.0:

http://www.energystar.gov/index.cfm?c=ent_servers.enterprise_servers

8. 80 PLUS Power Supplies Requirements: http://www.plugloadsolutions.com/80PlusPowerSupplies.aspx

9. Climate Savers Computing Initiative: http://www.climatesaverscomputing.org/

10. Texas Instruments, Datasheet: TMS320F28023 PiccoloTM microcontroller,

http://focus.ti.com/docs/prod/folders/print/tms320f28023.html

11. Texas Instruments, Datasheet: UCD3020 Digital Power Controller, http://focus.ti.com/docs/prod/folders/print/ucd3020.html

12. Texas Instruments, Datasheet: Green Phase-Shifted Full-Bridge controller with synchronous rectification, UCC28950,

http://focus.ti.com/docs/prod/folders/print/ucc28070.html

S-ar putea să vă placă și

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- F3 9000 EngDocument7 paginiF3 9000 Engjohn_kyrÎncă nu există evaluări

- Corporate Exposure RKO 2018 - PRAJAB PLN GROUP 20180914Document76 paginiCorporate Exposure RKO 2018 - PRAJAB PLN GROUP 20180914Adam ArmandoÎncă nu există evaluări

- CN101A Timer Manual: Set Current TimeDocument2 paginiCN101A Timer Manual: Set Current Timemakshdv nsksjdvÎncă nu există evaluări

- Physics Investigatory Project On FULL WAVE RECTIFIERDocument15 paginiPhysics Investigatory Project On FULL WAVE RECTIFIERAnshTripathiÎncă nu există evaluări

- A New LCL - Resonant Push-Pull DC-DC Converter For Inverter AppDocument4 paginiA New LCL - Resonant Push-Pull DC-DC Converter For Inverter AppoleksandrokhapkinÎncă nu există evaluări

- 21-DHANBAD-Sub Station Wise DetailsDocument24 pagini21-DHANBAD-Sub Station Wise DetailsVinamr01Încă nu există evaluări

- Cag 14 & Cag 34Document6 paginiCag 14 & Cag 34Arun KumarÎncă nu există evaluări

- LSis Price ListDocument48 paginiLSis Price ListECATOnline57% (7)

- Tebechop Se: Excellent Technology, Efficiency and QualityDocument8 paginiTebechop Se: Excellent Technology, Efficiency and QualityLương SángÎncă nu există evaluări

- Automotive Charging System Purpose: - Convert Mechanical Energy To Electrical EnergyDocument2 paginiAutomotive Charging System Purpose: - Convert Mechanical Energy To Electrical EnergyDimson B. CabacangÎncă nu există evaluări

- Axpert V Off-Grid Inverter Selection GuideDocument1 paginăAxpert V Off-Grid Inverter Selection GuideOnur Can GençÎncă nu există evaluări

- Exercise 3Document1 paginăExercise 3Ahmed MohamedÎncă nu există evaluări

- Presentation Subhrajyoti EVsDocument31 paginiPresentation Subhrajyoti EVsSubhraJyotiBorah100% (1)

- Imp - A Survey On Neutral-Point-Clamped InvertersDocument12 paginiImp - A Survey On Neutral-Point-Clamped InvertersVenkataramdas BonamÎncă nu există evaluări

- 013 PCRDocument49 pagini013 PCRhow loÎncă nu există evaluări

- Dry Type Transformer: Single-Phase, Three-Single, Three-Two and Three-Phase Transformers 1.1 KV To 7.2 KV ClassesDocument8 paginiDry Type Transformer: Single-Phase, Three-Single, Three-Two and Three-Phase Transformers 1.1 KV To 7.2 KV ClassesJeison Osmar Altamirano SoriaÎncă nu există evaluări

- Kemppi Minarc-Evo-180 en US PDFDocument2 paginiKemppi Minarc-Evo-180 en US PDFIonel ȘearpeÎncă nu există evaluări

- Interview Questions MS WordDocument20 paginiInterview Questions MS Wordhassan iftikhar100% (1)

- NC3 - Automatic Gen.-Set Controller For AMF And: Mains Parallel OperationDocument5 paginiNC3 - Automatic Gen.-Set Controller For AMF And: Mains Parallel Operationطربوش التميميÎncă nu există evaluări

- Coms Part 1Document11 paginiComs Part 1Marinjal TomadhyayÎncă nu există evaluări

- HESCODocument2 paginiHESCOAli Assad MirÎncă nu există evaluări

- STR-S6707 STR-S6709: Discontinued ProductDocument8 paginiSTR-S6707 STR-S6709: Discontinued ProductPetrMulačÎncă nu există evaluări

- Electrical Thumb Rules (Part 1)Document3 paginiElectrical Thumb Rules (Part 1)Manish Tiwari100% (2)

- Chapter 2 PDFDocument24 paginiChapter 2 PDFNathanael Aklilu EjersaÎncă nu există evaluări

- Siemens Energy Company Presentation en 2022 PDF Original FileDocument29 paginiSiemens Energy Company Presentation en 2022 PDF Original FileSunil DashoraÎncă nu există evaluări

- 2022 01 12 Port Development Considerations For Offshore WindDocument45 pagini2022 01 12 Port Development Considerations For Offshore WindPhilip AMCÎncă nu există evaluări

- Product Overview VEM Windpower PDFDocument8 paginiProduct Overview VEM Windpower PDFeghbali2255Încă nu există evaluări

- Answer Tutorial 2Document4 paginiAnswer Tutorial 2Syarina Maat100% (1)

- As NZS 61558.2.16-2010 (IEC TEXT) Safety of Power Transformers Power Supplies Reactors and Similar Products FDocument11 paginiAs NZS 61558.2.16-2010 (IEC TEXT) Safety of Power Transformers Power Supplies Reactors and Similar Products FSAI Global - APAC0% (2)

- Cisco Power Calculator ASR9010Document2 paginiCisco Power Calculator ASR9010Carlos Hoyos RosembluthÎncă nu există evaluări