Documente Academic

Documente Profesional

Documente Cultură

CMOS Inverter Design

Încărcat de

Ahmad KamilDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

CMOS Inverter Design

Încărcat de

Ahmad KamilDrepturi de autor:

Formate disponibile

CMOS inverter design Answer Q1: CMOS referred to as complementary metaloxidesemiconductor that form by NMOS and PMOS transistor.

The technology used in microprocessors, microcontrollers, static RAM, and other digital logic circuits and also for several analog circuits. Answer Q2: The basic operation of the CMOS is full rail-to-rail swing, symmetrical VTC, propagation delay function of load capacitance and resistance of transistors, no static power dissipation and direct path current during switching Answer Q3: 3 basic region operation are:

Cut-Off Region In this region the gate voltage is less than the pinch-off voltage Vp and therefore very little current flows. Triode Region In this mode the device is operating below pinch-off and is effectively a variable resistor. ROUT is ~ linear but only over a small range of VDS. Saturation Region This is the main operating region for the device. The drain voltage has to be greater than the gate voltage less the pinch-off voltage this sets the minimum supply voltage. The curves in the saturation region can be extrapolated to a point 1/, where is known as the Channel length modulation parameter, (units V-1), - this is analogous to the BJT Early voltage.

Answer Q4: The advantages of the CMOS are: High operating speeds and efficient usage of energy. They have very low static power supply drain most of the time. Only when the transistors are switching between the two states (on and off) do you find a significant level of power drain. High degree of noise immunity. Reliable Design, Reliable Performance, Best Price. Cost Optimized Design. Efficient Manufacturing Process. Microwave Performance from Advanced CMOS. Efficient Design. Answer Q5:In PMOS the carriers are holes whose mobility is less than the electrons, the carriers in NMOS. That means PMOS is slower than an NMOS. In CMOS technology, nmos helps in pulling down the output to ground ann PMOS helps in pulling up the output to Vdd. If the sizes of PMOS and NMOS are the same, then PMOS takes long time to charge up the output node. If we have a larger PMOS than there will be more carriers to charge the node quickly and overcome the slow nature of PMOS . Basically we do all this to get equal rise and fall times for the output node. In Transmission Gate, PMOS and NMOS aid each other rather competing with each other. That's the reason why we need not size them like in CMOS. In CMOS design we have NMOS and PMOS competing which is the reason we try to size them proportional to their mobility. Equation of mobility is:

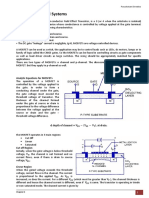

Answer Q6:The voltage transfer characteristic (VTC) gives the response of the inverter circuit,Vout , to specific input voltages,Vin. It is a figure of merit for the static behavior of the inverter. So the gate-source voltage Vgs of the n-chanel MOSFET is equal to Vin. While the gate-source voltage of the p-channel MOSFET calculates as and the drain so voltage of the pMOSFET can be expressed as

Figure above showing output characteristics of both transistors up to Vdd = Vin = 5V. The resulting drain currents in the inverter circuit must be equal for each Vin.

From the figure above extraction of the voltage transfer characteristics of a CMOS inverter. The drain currents of both transistors must be equal. Therefore, the intersection of the output characteristics of both transistors for each input voltage Vin give the output voltage Vout . The circles mark five points of the voltage transfer characteristics.

Answer Q7:

S-ar putea să vă placă și

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Arithmetic Logic UnitDocument63 paginiArithmetic Logic UnitLean MiñonÎncă nu există evaluări

- Digital Buffer and The Tri-State Buffer TutorialDocument10 paginiDigital Buffer and The Tri-State Buffer Tutorialmarcoms75Încă nu există evaluări

- Cmos Vlsi Design: A Systems & Circuits PerspectiveDocument44 paginiCmos Vlsi Design: A Systems & Circuits PerspectiveNoman RathoreÎncă nu există evaluări

- Lab 1 ELEC-4708: Advanced Digital Electronics: CMOS Logic Schematic and LayoutDocument2 paginiLab 1 ELEC-4708: Advanced Digital Electronics: CMOS Logic Schematic and LayoutSiam HasanÎncă nu există evaluări

- VLSI Lab Manual V Sem July16Document65 paginiVLSI Lab Manual V Sem July16Aditya RanjanÎncă nu există evaluări

- Experiment 1Document3 paginiExperiment 1Abdullah ZubairÎncă nu există evaluări

- Chapter 6 Control SystemsDocument7 paginiChapter 6 Control SystemspurushresthaÎncă nu există evaluări

- Universality of Logic GatesDocument6 paginiUniversality of Logic GatesJholieh ToinkzÎncă nu există evaluări

- Introduction To Cmos Vlsi Design: Combinational CircuitsDocument37 paginiIntroduction To Cmos Vlsi Design: Combinational CircuitsNguyễn Khắc ThanhÎncă nu există evaluări

- Boolean and Logic GatesDocument56 paginiBoolean and Logic Gatesmitparikh1046Încă nu există evaluări

- Invertor SIPF150Document3 paginiInvertor SIPF150fallenangel006Încă nu există evaluări

- Universal NorDocument15 paginiUniversal NormÎncă nu există evaluări

- Chapter 6 The NMOS Family of Logic CircuitDocument54 paginiChapter 6 The NMOS Family of Logic Circuitutsav ashishÎncă nu există evaluări

- Chapter 2Document20 paginiChapter 2khatrisudip520Încă nu există evaluări

- Logic Gates-Digital ElectronicsDocument10 paginiLogic Gates-Digital ElectronicsChrissie Jean E. TorresÎncă nu există evaluări

- Logic Gates 1Document3 paginiLogic Gates 1Via Marie MesaÎncă nu există evaluări

- WIX1003 Lab Report 12Document17 paginiWIX1003 Lab Report 12shu minÎncă nu există evaluări

- DLD Lab AssignmentDocument11 paginiDLD Lab Assignmentmir zohaibÎncă nu există evaluări

- Lab CollectionDocument116 paginiLab CollectionMansoor AslamÎncă nu există evaluări

- Simplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MDocument6 paginiSimplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN Mabhishekmath123Încă nu există evaluări

- MCQ Ex-403/deldDocument11 paginiMCQ Ex-403/deldBasic ScienceÎncă nu există evaluări

- Logic Gates: Capacitance and Uses of Capacitors Logic Ics 4000 Series 74 SeriesDocument10 paginiLogic Gates: Capacitance and Uses of Capacitors Logic Ics 4000 Series 74 SeriesCONSTANTINOSÎncă nu există evaluări

- LABORATORY EXPERIMENT 05 NAND ImplementationDocument7 paginiLABORATORY EXPERIMENT 05 NAND ImplementationMatt GacostaÎncă nu există evaluări

- Vlsi-Chip Input and Output CircuitsDocument27 paginiVlsi-Chip Input and Output CircuitsSrilatha KolliÎncă nu există evaluări

- 74AHC04 74AHCT04: 1. General DescriptionDocument17 pagini74AHC04 74AHCT04: 1. General DescriptionalexÎncă nu există evaluări

- Digital Electronics Laboratory Manual (ECE211) : Dr. Pradyut Kumar SankiDocument55 paginiDigital Electronics Laboratory Manual (ECE211) : Dr. Pradyut Kumar Sanki8885684828Încă nu există evaluări

- Assignment 1Document2 paginiAssignment 1mid_cycloneÎncă nu există evaluări

- A Structured Visual Approach To GALS Modelling and Verification of Communication CircuitsDocument15 paginiA Structured Visual Approach To GALS Modelling and Verification of Communication CircuitsElearning 95Încă nu există evaluări

- Assignment 1 (CSA)Document2 paginiAssignment 1 (CSA)Navjot Kaur MahiÎncă nu există evaluări

- Lab 10Document9 paginiLab 10Riffat GulÎncă nu există evaluări