Documente Academic

Documente Profesional

Documente Cultură

Verilog BASYS Example62-TrafficLights

Încărcat de

ਸ. ਇੰਦਰਦੀਪ ਸਿੰਘDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Verilog BASYS Example62-TrafficLights

Încărcat de

ਸ. ਇੰਦਰਦੀਪ ਸਿੰਘDrepturi de autor:

Formate disponibile

Traffic Lights

Example 62: Traffic Lights

It is often useful to be able to sequence through an arbitrary number of states, staying in each state an arbitrary amount of time. For example, consider the set of traffic lights shown in Figure 8.13. The lights are assumed to be at a four-way intersection with one street going north-south and the other road going east-west.

Red

Red

Yellow

Yellow

Green

Green

North - South

East - West

Figure 8.13 Six colored LEDs can represent a set of traffic lights

To simulate these traffic lights we will use the red, yellow, and green LEDs connected to ld[7:2] on the BASYS board and cycle through the six states shown in Table 8.2. A state diagram for controlling these traffic lights is shown in Fig. 8.14. If we use a 3 Hz clock to drive this state diagram then a delay of 1 second is achieved by staying in a state for three clock cycles. Similarly, a delay of 5 second is achieved by staying in a state for fifteen clock cycles. The count variable in Fig. 8.14 will be reset to zero when moving to the next state after a timeout. Listing 8.6 is a Verilog program that implements the state diagram in Fig. 8.14 and its simulation is shown in Fig. 8.15. Because we need a counter for the delay count it is more convenient in this case to combine the state register and combinational modules C1 in the Moore machine in Fig. 8.3 into a single sequential always block as shown in Listing 8.6. Note in this case we use only a single state variable. To generate the 3 Hz signal we will use the version of clkdiv shown in Listing 8.7. The top-level Verilog program is given in Listing 8.8.

Table 8.2 Traffic Light States North - South East - West Green Red Yellow Red Red Red Red Green Red Yellow Red Red

State 0 1 2 3 4 5

Delay (sec.) 5 1 1 5 1 1

Example 62

count < 15

S0

count < 3

S5 S1

count < 3

S4

S2

count < 3

S3

count < 3

count < 15

Figure 8.14 State diagram for controlling traffic lights

Figure 8.15 Simulation of the Verilog program in Listing 8.4

Traffic Lights

Listing 8.6 traffic.v // Example 62a: traffic lights module traffic ( input wire clk , input wire clr , output reg [5:0] lights ); reg[2:0] state; reg[3:0] count; parameter parameter S0 = 3'b000, S1 =3'b001, S2 = 3'b010, // states S3 = 3'b011, S4 = 3'b100, S5 = 3'b101; SEC5 = 4'b1111, SEC1 = 4'b0011; // delays

always @(posedge clk or posedge clr) begin if (clr == 1) begin state <= S0; count <= 0; end else case(state) S0: if(count < SEC5) begin state <= S0; count <= count + 1; end else begin state <= S1; count <= 0; end S1: if(count < SEC1) begin state <= S1; count <= count + 1; end else begin state <= S2; count <= 0; end S2: if(count < SEC1) begin state <= S2; count <= count + 1; end else begin state <= S3; count <= 0; end

Example 62

Listing 8.6 (cont.) traffic.v S3: if(count < SEC5) begin state <= S3; count <= count + 1; end else begin state <= S4; count <= 0; end S4: if(count < SEC1) begin state <= S4; count <= count + 1; end else begin state <= S5; count <= 0; end S5: if(count < SEC1) begin state <= S5; count <= count + 1; end else begin state <= S0; count <= 0; end default state <= S0; endcase end always @(*) begin case(state) S0: lights = 6'b100001; S1: lights = 6'b100010; S2: lights = 6'b100100; S3: lights = 6'b001100; S4: lights = 6'b010100; S5: lights = 6'b100100; default lights = 6'b100001; endcase end endmodule

Traffic Lights

Listing 8.7 clkdiv.v // Example 62b: clock divider module clkdiv ( input wire clk , input wire clr , output wire clk3 ); reg [24:0] q; // 25-bit counter always @(posedge clk or posedge clr) begin if(clr == 1) q <= 0; else q <= q + 1; end assign clk3 = q[24]; endmodule // 3 Hz

Listing 8.8 traffic_lights_top.v // Example 62: traffic_lights_top module traffic_lights_top ( input wire clk , input wire [3:3] btn , output wire [7:2] ld ); wire clk3; wire clr; assign clr = btn[3]; clkdiv U1 (.clk(clk), .clr(clr), .clk3(clk3) ); traffic U2 (.clk(clk3), .clr(clr), .lights(ld) ); endmodule

S-ar putea să vă placă și

- VHDL BASYS Example62-TrafficLightsDocument6 paginiVHDL BASYS Example62-TrafficLightspregresaÎncă nu există evaluări

- An Integer Square Root Algorithm: Example 24Document10 paginiAn Integer Square Root Algorithm: Example 24psomasalÎncă nu există evaluări

- New Text DocumentDocument8 paginiNew Text DocumentMuneeb AhmadÎncă nu există evaluări

- In Class - Finite State Machine ExamplesDocument30 paginiIn Class - Finite State Machine ExamplesAnonymous pcanQ3Încă nu există evaluări

- State Diagram Traffic Light 4 Junction Verilog CodingDocument22 paginiState Diagram Traffic Light 4 Junction Verilog CodingMierul AsrapÎncă nu există evaluări

- Practical Exam - RonquilloDominicDocument9 paginiPractical Exam - RonquilloDominicCYCLONE 1020Încă nu există evaluări

- H-Bridge Motor ControlDocument9 paginiH-Bridge Motor ControlSamSharmaÎncă nu există evaluări

- SVPWM & VbyfDocument11 paginiSVPWM & VbyfPravin NagraleÎncă nu există evaluări

- Problemas ResueltosDocument13 paginiProblemas ResueltosLiz Navarro MonteroÎncă nu există evaluări

- GSM Based Home AutomationDocument80 paginiGSM Based Home AutomationShashi Kant SainiÎncă nu există evaluări

- Atmel 8311 AVR1607 Brushless DC Motor Control in Sensor Mode Using ATxmega128A1 and ATAVRMC323 Application NoteDocument18 paginiAtmel 8311 AVR1607 Brushless DC Motor Control in Sensor Mode Using ATxmega128A1 and ATAVRMC323 Application NoteRoberto CasperÎncă nu există evaluări

- Rdbms Lab - q5Document5 paginiRdbms Lab - q5Jothi KumarÎncă nu există evaluări

- Accurate Position Estimation in Switched Reluctance Motor With Prompt StartingDocument10 paginiAccurate Position Estimation in Switched Reluctance Motor With Prompt Startingmounicapaluru_351524Încă nu există evaluări

- Overview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia TechDocument7 paginiOverview of The Inter-Integrated Circuit (I C) Bus: 2 ECPE 4536 Microprocessor System Design II Virginia Techdineshvhaval100% (1)

- DSP-Based Speed Adaptive Flux Observer of Induction MotorDocument5 paginiDSP-Based Speed Adaptive Flux Observer of Induction MotorthavaselvanÎncă nu există evaluări

- Final Project FinalReport VikasYADAVDocument12 paginiFinal Project FinalReport VikasYADAVviya123Încă nu există evaluări

- CHAPTER4 - Current Source InverterDocument46 paginiCHAPTER4 - Current Source InverterJandfor Tansfg Errott100% (1)

- AVR492: Brushless DC Motor Control Using AT90PWM3: Application NoteDocument26 paginiAVR492: Brushless DC Motor Control Using AT90PWM3: Application NotenicoletabytaxÎncă nu există evaluări

- Amity School of Engineering & Technology Digital Circuits & System - Ii Tutorial No. - 1Document10 paginiAmity School of Engineering & Technology Digital Circuits & System - Ii Tutorial No. - 1Vishal PathakÎncă nu există evaluări

- Modeling and Simulation of A PWM Rectifier Inverter Induction Motor Drive System Implementing Speed Sensor Less Direct Vector ControlDocument6 paginiModeling and Simulation of A PWM Rectifier Inverter Induction Motor Drive System Implementing Speed Sensor Less Direct Vector ControlFarhan SarwarÎncă nu există evaluări

- Verilog HDL: ModuleDocument9 paginiVerilog HDL: ModuleAvinash ReddyÎncă nu există evaluări

- (Matsui) Sensorless PM Brushless DC Motor DrivesDocument9 pagini(Matsui) Sensorless PM Brushless DC Motor DrivesPhạm Văn TưởngÎncă nu există evaluări

- 3axis TB6560 Stepper Motor Driver Board Users Instruction: Key FeaturesDocument9 pagini3axis TB6560 Stepper Motor Driver Board Users Instruction: Key FeaturesDaniela HungÎncă nu există evaluări

- LogicDesign CHPT 10Document31 paginiLogicDesign CHPT 10john juanÎncă nu există evaluări

- Position and Timing Control With DC Motor Using 555 Timer Li TianDocument9 paginiPosition and Timing Control With DC Motor Using 555 Timer Li TianMuhammad NaeemÎncă nu există evaluări

- Tutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Document12 paginiTutorial For Running A Stepper-Motor Using Krypton Board (Wel - Lab, Iit Bombay)Chiquita WhiteÎncă nu există evaluări

- Quadrature EncoderDocument5 paginiQuadrature EncoderJaime Santiago Sanchez ReinosoÎncă nu există evaluări

- Modulo-N Counters: Module M10.4 Section 7.2Document27 paginiModulo-N Counters: Module M10.4 Section 7.2Jeffry MarzellieÎncă nu există evaluări

- Fig. 12.1 - Movement of Rotor For Current in Different WindingsDocument6 paginiFig. 12.1 - Movement of Rotor For Current in Different WindingsBala SubramanianÎncă nu există evaluări

- Lab Manual 10Document8 paginiLab Manual 10ThoughtsÎncă nu există evaluări

- AtoD Converter System S12 NewDocument9 paginiAtoD Converter System S12 NewMina HannaÎncă nu există evaluări

- StopWatch ReportDocument11 paginiStopWatch ReportGeoffrey ChuaÎncă nu există evaluări

- An 101Document6 paginiAn 101Phy DeswitaÎncă nu există evaluări

- Chapter 6 - Introduction To Sequential DevicesDocument62 paginiChapter 6 - Introduction To Sequential DevicesSarath Chandra SÎncă nu există evaluări

- Chapter 7 Ver3Document20 paginiChapter 7 Ver3Divya AhujaÎncă nu există evaluări

- Quadrature Encoder Receiver Module: An Implementation On FPGADocument12 paginiQuadrature Encoder Receiver Module: An Implementation On FPGAสหายดิว ลูกพระอาทิตย์Încă nu există evaluări

- Interpolation Technique For Encoder Resolution Improvement in Permanent Magnet Synchronous Motor Drives PDFDocument6 paginiInterpolation Technique For Encoder Resolution Improvement in Permanent Magnet Synchronous Motor Drives PDFarenasjaÎncă nu există evaluări

- Traffic Light ControlDocument5 paginiTraffic Light ControlRohit KadlagÎncă nu există evaluări

- Lab 13Document11 paginiLab 13ubaidÎncă nu există evaluări

- Driver Motor BrushlesDocument48 paginiDriver Motor BrushlesGONAJ2008Încă nu există evaluări

- Unit8-RK 3Document27 paginiUnit8-RK 3sbaÎncă nu există evaluări

- (212142518) Stepper Motor Control Using MicrocontrollerDocument4 pagini(212142518) Stepper Motor Control Using MicrocontrollerraghavthakurjiÎncă nu există evaluări

- Welcome To International Journal of Engineering Research and Development (IJERD)Document8 paginiWelcome To International Journal of Engineering Research and Development (IJERD)IJERDÎncă nu există evaluări

- Slow-Scale Bifurcation Behavior of Parallel-Connected Boost Converters Via Averaged ModelsDocument18 paginiSlow-Scale Bifurcation Behavior of Parallel-Connected Boost Converters Via Averaged ModelselsaordunaÎncă nu există evaluări

- Verilog 2022 ASSN2 SolutionDocument5 paginiVerilog 2022 ASSN2 SolutionSai HarshithaÎncă nu există evaluări

- The I C-Bus Specification: 6 Bit TransferDocument54 paginiThe I C-Bus Specification: 6 Bit Transferprasanth_vedanthamÎncă nu există evaluări

- Synthesis of A Traffic Light Sequence CircuitDocument19 paginiSynthesis of A Traffic Light Sequence CircuitDino LigutanÎncă nu există evaluări

- Controlling Stepper Motors With A PIC MicrocontrollerDocument16 paginiControlling Stepper Motors With A PIC Microcontrollervasudeva yasasÎncă nu există evaluări

- VHDL FSM UNIT 5 ET&T 7th SemDocument22 paginiVHDL FSM UNIT 5 ET&T 7th SemDEEPA KUNWARÎncă nu există evaluări

- Lecture 10: A Design Example - Traffic Lights: The ProblemDocument6 paginiLecture 10: A Design Example - Traffic Lights: The ProblemKapil_Kaushik_8847Încă nu există evaluări

- Decoupling Control of D and Q CurrentDocument11 paginiDecoupling Control of D and Q CurrentnandarathanaÎncă nu există evaluări

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkDe la EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkÎncă nu există evaluări

- Variable Speed AC Drives with Inverter Output FiltersDe la EverandVariable Speed AC Drives with Inverter Output FiltersÎncă nu există evaluări

- Control of DC Motor Using Different Control StrategiesDe la EverandControl of DC Motor Using Different Control StrategiesÎncă nu există evaluări

- Power Systems-On-Chip: Practical Aspects of DesignDe la EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardÎncă nu există evaluări

- Advanced Multilevel Converters and Applications in Grid IntegrationDe la EverandAdvanced Multilevel Converters and Applications in Grid IntegrationAli Iftekhar MaswoodÎncă nu există evaluări

- Present Ac I OnesDocument235 paginiPresent Ac I OnesjoukornÎncă nu există evaluări

- Periodograms and Blackman-Tukey Spectral Estimation: - ObjectivesDocument11 paginiPeriodograms and Blackman-Tukey Spectral Estimation: - ObjectivesrakeshÎncă nu există evaluări

- NAS and Data Protection: ZFS Storage Appliance Racked System UpdateDocument34 paginiNAS and Data Protection: ZFS Storage Appliance Racked System UpdateThuan Tran NgocÎncă nu există evaluări

- SAP ABAP Training: Hamad AhmadDocument12 paginiSAP ABAP Training: Hamad Ahmadtheict mentorÎncă nu există evaluări

- Multi Format Broadcast LCD Monitor: Operation Manual - v1.0Document36 paginiMulti Format Broadcast LCD Monitor: Operation Manual - v1.0Sergio MorenoÎncă nu există evaluări

- Interview QuestionsDocument9 paginiInterview QuestionskasimÎncă nu există evaluări

- Wimax and VLANDocument13 paginiWimax and VLANramizzzÎncă nu există evaluări

- Lab 1a RASPlib Installation Instructions R5 2016b-2017aDocument10 paginiLab 1a RASPlib Installation Instructions R5 2016b-2017aaleÎncă nu există evaluări

- FC Tranceiver 69Y2876-C - Datasheets - ENDocument6 paginiFC Tranceiver 69Y2876-C - Datasheets - ENY.FÎncă nu există evaluări

- Java LiteralsDocument4 paginiJava LiteralsRavinderRaviÎncă nu există evaluări

- Development of Arduino-Based Panic Alarm With GPS and GSM ModulesDocument11 paginiDevelopment of Arduino-Based Panic Alarm With GPS and GSM ModulesInternational Journal of Innovative Science and Research TechnologyÎncă nu există evaluări

- C Programs (Notes)Document77 paginiC Programs (Notes)Dark KnightÎncă nu există evaluări

- Venkatesh - Java - Backend - Develpoer - 4.5 Years - 168508546Document3 paginiVenkatesh - Java - Backend - Develpoer - 4.5 Years - 168508546venkey reddyÎncă nu există evaluări

- 3.2.8.26 OTU-2/OTU2e/OTU2f/10G LAN/FC10/FC8 XFP/SFP+ Optical TransceiversDocument1 pagină3.2.8.26 OTU-2/OTU2e/OTU2f/10G LAN/FC10/FC8 XFP/SFP+ Optical TransceiversJose JaramilloÎncă nu există evaluări

- Conference PaperDocument3 paginiConference PaperAngelica SutharÎncă nu există evaluări

- System Administration and IT Infrastructure Services 05Document15 paginiSystem Administration and IT Infrastructure Services 05Emey HabulinÎncă nu există evaluări

- 15 ZXHN H168N UserMan 4132358Document12 pagini15 ZXHN H168N UserMan 4132358qaisarhayat68Încă nu există evaluări

- Fundamentals of Cloud Security - BeaconDocument3 paginiFundamentals of Cloud Security - BeaconKesavaÎncă nu există evaluări

- C Standard LibraryDocument17 paginiC Standard LibraryKondamahesh100% (1)

- Vmware ClusterDocument68 paginiVmware ClusterredmiÎncă nu există evaluări

- Perl Scripts For Eda ToolsDocument6 paginiPerl Scripts For Eda ToolsSharan Kumar GoudÎncă nu există evaluări

- OPM Batch APIDocument22 paginiOPM Batch APIKarthikeya Bandaru100% (2)

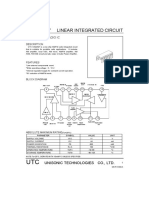

- UTC KA22427 DatasheetDocument3 paginiUTC KA22427 DatasheetSergio Daniel BarretoÎncă nu există evaluări

- High-End Portable Fault Location System: DescriptionDocument5 paginiHigh-End Portable Fault Location System: DescriptionTri Ari WibowoÎncă nu există evaluări

- C C++Document93 paginiC C++KRISHNAVINOD100% (1)

- Vacon NXP Linesynch II Apfiff44v117 Manual Dpd01977a v001Document203 paginiVacon NXP Linesynch II Apfiff44v117 Manual Dpd01977a v001Jelenna JennaÎncă nu există evaluări

- Sottoriva DividerDocument57 paginiSottoriva Divideratya ragabÎncă nu există evaluări

- Ipm41-D3 (9-15-09)Document6 paginiIpm41-D3 (9-15-09)Luis Marin100% (1)

- Configuring OTLDocument136 paginiConfiguring OTLHirenDesai100% (1)

- HowTo Setup ProxySG3 SW License KeyDocument12 paginiHowTo Setup ProxySG3 SW License Keykillo33Încă nu există evaluări