Documente Academic

Documente Profesional

Documente Cultură

Inal Roject: Digital System Design With VHDL Final Project Notes

Încărcat de

Anas XahidDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Inal Roject: Digital System Design With VHDL Final Project Notes

Încărcat de

Anas XahidDrepturi de autor:

Formate disponibile

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 23

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

THE PROBLEM A two-dimensional video image is transferred between processing modules by passing one pixel at a time qualied by horizontal and vertical blank pulses. Example

(shown for 4x4 image) X-> Y-> 0 4 8 12 1 5 9 13 2 6 10 14 3 7 11 15

HB

VB

Clk Pixel HB VB

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 24

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

THE PROBLEM (CONTINUED) The task is to write a VHDL module that accepts the incoming video stream, stores it in a RAM, calculates a histogram from the input data, and locates the 50th percentile of the histogram. A functional block diagram and processing timeline are as follows: CPU Source Video Source Clock Source

Address, Data, Write Enable, Data Strobe

Project Module histogram

video HB VB

Input Decoder

control

Histogram Calc

control

Readout Control

data

clk clk2x A D WE CS A D WE CS

Video RAM

video frame video readin clear hist RAM calculate histogram

Histogram RAM

percentile readout hist readout video readin clear hist RAM

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 25

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

WHAT WE NEED TO DO.... Implement the following functions Input Decoder / Video RAM Controller Accepts video stream, horizontal and vertical blanks, and generates RAM address, data, write enable, and chip select (data strobe) signals to store the incoming video into a RAM At the beginning of the video stream, clears the histogram accumulation RAM After the video stream has been stored in the video RAM, generates RAM address, data, write enable, and chip select (data strobe) signals to read the video into a RAM Sequences out the histogram data, calculates the 50-percentile point, and presents the percentile point to output 50-percentile point is dened as the point (value) in the histogram at which 50% or more of the pixel intensities fall at or below it

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED. Slide 26

Histogram Calculation / Histogram RAM controller -

Readout Controller / Percentile Determination -

February 12, 1998

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

ILLUSTRATION

255 VIDEO PIXEL DATA STREAM = 0 0 0 1 2 4 6 5 7 4 2 0 0 0

255 HISTOGRAM RAM BIN COUNTS

7 INTENSITY PIXEL COUNTS (Histogram Data) 6 5 4 3 2 1 0 0 1 2 3 4 5 6 7 8 9 10 11 12 13

7 6 5 4 3 2 1 0 0 50-percentile 1 2 3 4 5 6 7 8 PIXEL INTENSITY (Histogram Address) 9 255

TIME (IN PIXEL INTERVALS)

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 27

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

INTERFACE SPECIFICATIONS

All external interfaces shall be std_logic or std_logic_vector The Module shall contain an external active-low reset (resetLowIn), and two external clocks, 10 MHz and 20MHz (clkIn and clk2xIn respectively) The Module shall contain a CPU programming interface consisting of: a 24-bit address bus (cpuAddrIn) a bidirectional 16-bit data bus (cpuDataBi) a 1-bit active-low Write Enable (cpuWriteEnLowIn) a 1-bit active-low Data Strobe (cpuDataStrobeLowIn) an 8-bit address bus (vidAddrOut) an 8-bit bidirectional data bus (vidDataBi) a 1-bit active-low Write Enable (vidWriteEnLowOut) a 1-bit active-low Chip Select (vidChipSelLowOut)

The Module shall contain a Video RAM interface consisting of: -

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 28

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

INTERFACE SPECIFICATIONS - CONTINUED

The Module shall contain a Histogram RAM interface consisting of: an 8-bit address bus (histAddrOut) an 8-bit bidirectional data bus (histDataBi) a 1-bit active-low Write Enable (histWriteEnLowOut) a 1-bit active-low Chip Select (histChipSelLowOut)

The Module shall contain an 8-bit data output (statDataOut) and a data valid gate (statDataValidOut) which shall be asserted during the output sequencing The Module shall accept 8-bit video data (pixelDataIn), an active-high horizontal blank (horizBlankIn), and an active-high vertical blank (vertBlankIn)

596B Students only:

The Module shall contain an active-low End-Of-Frame interrupt to the CPU (eofIntLowOut)

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 29

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

FUNCTIONAL SPECIFICATIONS : ALL STUDENTS

Input image size shall be a maximum of 16 x 16 pixels The Module shall contain a CPU programmable threshold value. Every incoming pixel whose value exceeds the threshold value shall be replaced by the threshold value in the histogram determination. The Histogram RAM shall be cleared at the beginning of each video frame, prior to accumulation of the histogram.

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 30

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

ADDITIONAL SPECIFICATIONS : 596 STUDENTS ONLY

The Module shall contain a CPU programmable Pause ag Module function shall be suspended during each video frame in which the Pause ag is set at the beginning of the frame Assertion of the Pause ag shall not interrupt processing of the current video frame The Video RAM and the Histogram shall be accessible for Read and Write to the CPU during any frame in which the Pause ag is set The Module shall supply an End-Of-Frame interrupt to the CPU The interrupt shall be asserted when the last statistics value has been read out and shall remain asserted until an Interrupt Acknowledge is received. An Interrupt Acknowledge shall consist of a Write of 0 to the Interrupt Acknowledge address, followed by a Write of 1 to the same address

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 31

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

SAMPLE TIMING

clkIn statDataOut statDataValidOut eofIntLowOut clkIn cpuAddrIn vidAddrOut histAddrOut cpuDataBi vidDataBi histDataBi cpuWriteEnLowIn vidWriteEnLowOut histWriteEnLowOut cpuDataStrobeLowIn vidChipSelLowOut histChipSelLowOut

V ALID V ALID bin 0 bin 1 bin 2 bin 255 50 %

V ALID

V ALID

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 32

Digital System Design with VHDL Final Project Notes

ProjectNotes_97.doc

FINAL PROJECT

CPU MEMORY MAP

ADDRESS 00,0000 - 7F,FFFFh 80,0000h 80,0001h 80,0002h 80,0003 - 9F,FFFFh A0,0000 - A0,00FFh A0,0100 - BF,FFFFh C0,0000 - C0,00FFh C0,0100 - FF,FFFFh

MEMORY FUNCTION

reserved for internal CPU use

VIDEO THRESHOLD REGISTER PAUSE FLAG END-OF-FRAME INTERRUPT ACKNOWLEDGE REGISTER

reserved

VIDEO RAM

reserved

HISTOGRAM RAM

reserved

February 12, 1998

DAVID M. CLARK REVISION 001 COPYRIGHT 1996 DAVID MICHAEL CLARK. ALL RIGHTS RESERVED.

Slide 33

S-ar putea să vă placă și

- Quiz - 03 - Self Review Quiz - Acad - Sle201v15 Courseware - SUSE AcademyDocument3 paginiQuiz - 03 - Self Review Quiz - Acad - Sle201v15 Courseware - SUSE AcademyMuhammad Salman KhanÎncă nu există evaluări

- Introduction To MicrocontrollersDocument52 paginiIntroduction To MicrocontrollersSanjayaRangaLSenavirathnaÎncă nu există evaluări

- The Single Cycle CPU ProjectDocument16 paginiThe Single Cycle CPU ProjectErik MachorroÎncă nu există evaluări

- Interfacing Nokia ScreenDocument4 paginiInterfacing Nokia ScreenDavid Sanderson100% (2)

- Design of A RISC Microcontroller Core in 48 HoursDocument11 paginiDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediÎncă nu există evaluări

- 05 Systemc TutorialDocument32 pagini05 Systemc TutorialjasonturfÎncă nu există evaluări

- Sata Specs 3.0 PDFDocument663 paginiSata Specs 3.0 PDFdinokid08Încă nu există evaluări

- Catalogo 8 Bits MicrochipDocument12 paginiCatalogo 8 Bits MicrochipManuel Gonzálvez García100% (1)

- Ajax CNC Installation ManualDocument27 paginiAjax CNC Installation ManualsunhuynhÎncă nu există evaluări

- Coin Cell Powered Embedded DesignDocument155 paginiCoin Cell Powered Embedded DesignFeroz Khan100% (1)

- I2c PaperDocument14 paginiI2c PaperParvinder SinghÎncă nu există evaluări

- Microcontroller Lab ManualDocument127 paginiMicrocontroller Lab Manualsiri.pogula100% (2)

- HIL Configuration Using MatlabDocument13 paginiHIL Configuration Using MatlabVimal RauÎncă nu există evaluări

- T89C51 Training Board - V5Document44 paginiT89C51 Training Board - V5davidegrimaÎncă nu există evaluări

- DsPIC DSC Motor Control WorkshopDocument177 paginiDsPIC DSC Motor Control Workshopgzdprlk100% (3)

- Lab UCSPE 2017 PDFDocument68 paginiLab UCSPE 2017 PDFWahyu AriantoÎncă nu există evaluări

- Delhi Technological University: Ec-306 Embedded Systems Lab FileDocument7 paginiDelhi Technological University: Ec-306 Embedded Systems Lab File2K19/EC/192 SWASTIK SHARMAÎncă nu există evaluări

- At89s52 GLCD Stk1 UgDocument7 paginiAt89s52 GLCD Stk1 UgAlberto SequeiraÎncă nu există evaluări

- Write A Program For Interfacing The 16x2 LCD MODULES AimDocument7 paginiWrite A Program For Interfacing The 16x2 LCD MODULES AimLeelasrikanth TubatiÎncă nu există evaluări

- Presentation On Summer Training IN Embedded System: Taken AT "Infinity Technologies"Document20 paginiPresentation On Summer Training IN Embedded System: Taken AT "Infinity Technologies"Gajendra RajoriaÎncă nu există evaluări

- WWW Engineersgarage Com Serial Data Received From PC Using 8Document14 paginiWWW Engineersgarage Com Serial Data Received From PC Using 8Javier ParedesÎncă nu există evaluări

- 24lc21 KullanimiDocument8 pagini24lc21 KullanimiskiziltoprakÎncă nu există evaluări

- Manual For Cycle 1Document193 paginiManual For Cycle 1Seth GreeneÎncă nu există evaluări

- Ch.0 Introduction To VHDLDocument34 paginiCh.0 Introduction To VHDLherrickkongÎncă nu există evaluări

- 8x8 RGB LED Matrix Display v1Document6 pagini8x8 RGB LED Matrix Display v1SamJhonnesÎncă nu există evaluări

- Pico Blaze IntroDocument71 paginiPico Blaze IntroAlexÎncă nu există evaluări

- Openadc High Speed Analog: C Sample Code For Pic Micros and Hi Tech CDocument11 paginiOpenadc High Speed Analog: C Sample Code For Pic Micros and Hi Tech CMuhammedSabriSalimÎncă nu există evaluări

- Direct Drive LCDDocument13 paginiDirect Drive LCDTrijeth DatlaÎncă nu există evaluări

- Delhi Technological University: Ec-306 Embedded Systems Lab FileDocument6 paginiDelhi Technological University: Ec-306 Embedded Systems Lab File2K19/EC/192 SWASTIK SHARMAÎncă nu există evaluări

- Delhi Technological University: Ec-306 Embedded Systems Lab FileDocument5 paginiDelhi Technological University: Ec-306 Embedded Systems Lab File2K19/EC/192 SWASTIK SHARMAÎncă nu există evaluări

- Delhi Technological University: Ec-306 Embedded Systems Lab FileDocument6 paginiDelhi Technological University: Ec-306 Embedded Systems Lab File2K19/EC/192 SWASTIK SHARMAÎncă nu există evaluări

- Ddr3 QuestionsDocument3 paginiDdr3 Questionsthennavan_balu5976Încă nu există evaluări

- Pes1ug20ec217 Isa03 2022 23 Ue20ec324Document11 paginiPes1ug20ec217 Isa03 2022 23 Ue20ec324Vaishnavi B VÎncă nu există evaluări

- 8051 Robot ManualDocument20 pagini8051 Robot ManualAmit B KolekarÎncă nu există evaluări

- Multi Level Security Based Access Control SystemDocument3 paginiMulti Level Security Based Access Control Systemprashant goreÎncă nu există evaluări

- HCS12Document42 paginiHCS12IWillTechnoSolutionsÎncă nu există evaluări

- User's Guide: Developed As Learning Material For Training of Students Under TEQIPDocument21 paginiUser's Guide: Developed As Learning Material For Training of Students Under TEQIPyogeshmgaidhaneÎncă nu există evaluări

- Unity 7.0Document20 paginiUnity 7.0Jonathan Paucar Tenorio100% (1)

- Creating IPCore Loi 11may2013Document20 paginiCreating IPCore Loi 11may2013LinkyÎncă nu există evaluări

- Dw02 Mult 6 StageDocument4 paginiDw02 Mult 6 StageroseootyÎncă nu există evaluări

- Ddcmis LectureDocument58 paginiDdcmis LectureSamÎncă nu există evaluări

- What Is New in UnityV8Document21 paginiWhat Is New in UnityV8kleyvadiÎncă nu există evaluări

- Del-8051 Universal Development Platform Nvis 5001ADocument2 paginiDel-8051 Universal Development Platform Nvis 5001AArkan ahmed husseinÎncă nu există evaluări

- ™ InternetEthernet Demonstration BoardDocument2 pagini™ InternetEthernet Demonstration BoardEuro FuenmayorÎncă nu există evaluări

- Interfacing LCD With Atmega32 Microcontroller Using Atmel StudioDocument5 paginiInterfacing LCD With Atmega32 Microcontroller Using Atmel StudioAbdulÎncă nu există evaluări

- HW Assignment 2Document11 paginiHW Assignment 2Akshat JhaÎncă nu există evaluări

- Objective and AimDocument6 paginiObjective and AimSaadat ZaidiÎncă nu există evaluări

- Microcontroller and Embedded System Designs (EE-328-F) : Lab Manual Vi SemesterDocument43 paginiMicrocontroller and Embedded System Designs (EE-328-F) : Lab Manual Vi SemesterabÎncă nu există evaluări

- Code Composer Studio and The Dsks Dsk6711, Dsk6713 and Dsk6416Document50 paginiCode Composer Studio and The Dsks Dsk6711, Dsk6713 and Dsk6416davidrojasvÎncă nu există evaluări

- USER MANUAL Mab - 51Document93 paginiUSER MANUAL Mab - 51Pushpinder Singh KhalsaÎncă nu există evaluări

- Implementation of Sign Board DOT Matrix Display With 8051Document25 paginiImplementation of Sign Board DOT Matrix Display With 8051Aminu BugajeÎncă nu există evaluări

- DT 3155Document4 paginiDT 3155Gempur SandRisÎncă nu există evaluări

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDocument5 paginiXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackÎncă nu există evaluări

- Decode Mpeg-2 Video With Virtex FpgasDocument3 paginiDecode Mpeg-2 Video With Virtex FpgasBlesson GeorgeÎncă nu există evaluări

- PIC Microprocessor Circuit DesignDocument308 paginiPIC Microprocessor Circuit Designcybhunter007Încă nu există evaluări

- 25L8005m2c PDFDocument44 pagini25L8005m2c PDFjoscar7Încă nu există evaluări

- MX25L4005APC - Macronix International BIOSDocument44 paginiMX25L4005APC - Macronix International BIOSRyosuke RaijiÎncă nu există evaluări

- K L With Advanced Encryption Standard (AES) Receiver/DecoderDocument8 paginiK L With Advanced Encryption Standard (AES) Receiver/DecoderbilarodrigoÎncă nu există evaluări

- Operator Interface Products 48-1: March 2009Document38 paginiOperator Interface Products 48-1: March 2009Herick509Încă nu există evaluări

- Xilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyDocument4 paginiXilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyjackÎncă nu există evaluări

- Simple 8 Bit 16x2 LCD Interfacing With PIC 16F: Jobs Electrician UsaDocument6 paginiSimple 8 Bit 16x2 LCD Interfacing With PIC 16F: Jobs Electrician UsaMuhammad Majid AltafÎncă nu există evaluări

- Dspic33F/Pic24H Flash Programming SpecificationDocument84 paginiDspic33F/Pic24H Flash Programming SpecificationSobhi MahÎncă nu există evaluări

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.De la EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Încă nu există evaluări

- MediaTek Linux SDK Release NotesDocument34 paginiMediaTek Linux SDK Release NotesAnonymous 5aGiTunÎncă nu există evaluări

- Why Block Space Reclamation' Needed?Document23 paginiWhy Block Space Reclamation' Needed?NavneetMishraÎncă nu există evaluări

- CSS 10 Q1 - Las W1 PDFDocument6 paginiCSS 10 Q1 - Las W1 PDFJohndion A. RulomaÎncă nu există evaluări

- AN4378Document15 paginiAN4378ebrahimÎncă nu există evaluări

- Performing Mensuration and Calculation PMCDocument109 paginiPerforming Mensuration and Calculation PMCLawrence RolluquiÎncă nu există evaluări

- Practical Task 3 - VPNDocument6 paginiPractical Task 3 - VPNsyahmiafnanÎncă nu există evaluări

- 2 Digital Subscriber Signalling System No.1 (DSS1) : 2.1 ISDN Network IntroductionDocument7 pagini2 Digital Subscriber Signalling System No.1 (DSS1) : 2.1 ISDN Network IntroductionPaul SigeiÎncă nu există evaluări

- Hyperledger Indy Public Blockchain: Presented by Alexander ShcherbakovDocument42 paginiHyperledger Indy Public Blockchain: Presented by Alexander ShcherbakovYang LinÎncă nu există evaluări

- Vocabulary Workshop #2 PDFDocument5 paginiVocabulary Workshop #2 PDFdassÎncă nu există evaluări

- SESSION: 2018 - 2019 (Spring) B. Tech. 3 Year Subject Code: EE 342 Subject Name: No. of Pages: 1 (Both Side) Full Marks: 30 Duration: 2 HoursDocument2 paginiSESSION: 2018 - 2019 (Spring) B. Tech. 3 Year Subject Code: EE 342 Subject Name: No. of Pages: 1 (Both Side) Full Marks: 30 Duration: 2 HourshiÎncă nu există evaluări

- FNIS FNIS Readme 7.4.5Document17 paginiFNIS FNIS Readme 7.4.5macaquinho.Încă nu există evaluări

- Python EnvironmentDocument3 paginiPython EnvironmentSeshasaiÎncă nu există evaluări

- 7 Steps To Upgrade IOS Image On Cisco Catalyst Switch or RouterDocument7 pagini7 Steps To Upgrade IOS Image On Cisco Catalyst Switch or RouterasimalampÎncă nu există evaluări

- Computer 100 McqsDocument9 paginiComputer 100 McqsSaugat timilsinaÎncă nu există evaluări

- Lab 6 Worksheet: Working With DisksDocument12 paginiLab 6 Worksheet: Working With DisksBj BlackÎncă nu există evaluări

- TraceDocument11 paginiTraceYogeshwarÎncă nu există evaluări

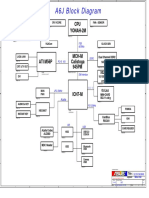

- A6j MB 1122 PDFDocument63 paginiA6j MB 1122 PDFOman SomantriÎncă nu există evaluări

- An Efficient Resource Utilization Technique For Scheduling Scientific Workload in Cloud Computing EnvironmentDocument12 paginiAn Efficient Resource Utilization Technique For Scheduling Scientific Workload in Cloud Computing EnvironmentIAES IJAIÎncă nu există evaluări

- Zenoss Service Dynamics Extended Monitoring 27-032014-4.2-V13Document258 paginiZenoss Service Dynamics Extended Monitoring 27-032014-4.2-V13Cicero SouzaÎncă nu există evaluări

- Optimal RAID Configurations For Video Surveillance: White PaperDocument7 paginiOptimal RAID Configurations For Video Surveillance: White PaperHanny WibisonoÎncă nu există evaluări

- Cloud Computing Course ContentDocument3 paginiCloud Computing Course ContentbugzbinnyÎncă nu există evaluări

- E S R M F: Adsl Usb ModemDocument12 paginiE S R M F: Adsl Usb ModemSaif Eddine AliaÎncă nu există evaluări

- OSY-Microproject V VDocument20 paginiOSY-Microproject V VComputer ActivityÎncă nu există evaluări

- The Essential Software Guide For FreshmoresDocument4 paginiThe Essential Software Guide For FreshmoresKang Raye NgÎncă nu există evaluări

- Verilog HDL: Top.v Cpu.v Ram.v Io.vDocument126 paginiVerilog HDL: Top.v Cpu.v Ram.v Io.vNisreen AlhamriÎncă nu există evaluări

- Flynn's TaxonomyDocument6 paginiFlynn's Taxonomyvenmathimsc482Încă nu există evaluări

- LAB 15 B - Poison Ivy RootkitDocument9 paginiLAB 15 B - Poison Ivy Rootkit1.Huỳnh Ngọc Thiên AnÎncă nu există evaluări