Documente Academic

Documente Profesional

Documente Cultură

Design, Implementation and Characterization of Xor Phase Detector For DPLL in 45 NM Cmos Technology

Încărcat de

Anonymous IlrQK9HuTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Design, Implementation and Characterization of Xor Phase Detector For DPLL in 45 NM Cmos Technology

Încărcat de

Anonymous IlrQK9HuDrepturi de autor:

Formate disponibile

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.

6, November 2011

DESIGN, IMPLEMENTATION AND CHARACTERIZATION OF XOR PHASE DETECTOR FOR DPLL IN 45 NM CMOS TECHNOLOGY

Delvadiya Harikrushna I1, Prof. Mukesh Tiwari2, Prof. Jay Karan Singh3 Dr. Anubhuti Khare4

1

Department of Electronics &Communication, Sri Satya Sai Institute of Science & Technology

hkpatel13@gmail.com

2,3

Professor, Department of Electronics &Communication Sri Satya Sai Institute of Science & Technology Sehore, Bhopal, Madhya Pradesh, India

Jksingh81@yahoo.co.in

UIT, Rajiv Gandhi Proudhyugiki Vishwavidhyalaya University Bhopal, MP, India.

ABSTRACT

In this paper the implementation of XOR phase detector in 45 nm submicron CMOS technology and its CMOS design layout using Microwind 3.1 for Digital Phase Locked Loop in sub-nanometres CMOS Technology is presented. The input-output transfer characteristic of XOR phase detector is presented. The CMOS XOR phase detector produces error pulses on both rising and falling edges while the CMOS phase frequency detector will respond only to positive or negative transitions. XOR phase detector will try to lock on both rising as well as falling edge while the PFD (phase frequency detector) will lock on either rising edge or falling edge of reference signal and feedback signal.

KEYWORDS

PLL, XOR Phase Detector, Phase Frequency Detector, CMOS layout design.

1. INTRODUCTION

A function of digital phase-locked loop is to lock to the phase of an input reference signal with the feedback signal produce by VCO and passes through divider circuitry. A basic form of a PLL consists of three fundamental blocks, namely, Phase detector (PD). Loop filter. Voltage controlled oscillator (VCO) The phase detector compares the phase of input signal or reference signal with the phase of signal produced by the VCO. Phase detector compares the phase difference between two input signal and produce Output signal in form of difference voltage proportional to phase difference. The difference voltage signal is filtered by the loop filter and applied to the input to VCO(Vcontrol). The control voltage on the VCO produce the frequency such that reduces the phase difference between the input signal and the local oscillator. When the loop is locked, than

DOI : 10.5121/acij.2011.2605 45

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

both signals phase are equal. This period of frequency acquisition, is referred as pull-in time, this can be very long or very short, depending on the bandwidth of the PLL.

2. PHASE DETECTOR

Generally two broad categories of phase detectors can be distinguished: multiplier circuits and sequential circuits. Multipliers generate the useful DC error output as the average product of the input-signal waveform times the local oscillator waveform. A properly designed multiplier is capable of operation on an input signal buried deeply in noise. A sequential phase detector generates an output voltage that is a function of the lime interval between a zero crossing on the signal and a zero crossing on the VCO waveform. Sequential phase detectors are capable of detecting both the phase and frequency differences [4]. There are two main digital phase detectors: XOR phase detector. Phase/frequency detector.

3. XOR PHASE DETECTOR

The XOR phase detector is simply exclusive OR gate. We know the simple operation of exclusive OR gate, it compare phase difference between both signal and produce output pulses basis on the input varies. It provide dc level proportional to the phase difference between the inputs. While the XOR circuit produces error pulses on both rising and falling edges. The operation of phase detectors is similar to that of differential amplifiers in that both sense the difference between the inputs, generating a proportional output. It doesnt contain any phase difference information. The phase difference between the dclock and data is given by

= data dclock =

t Tdclock

2 (radians )

..(1)

or, in terms of output clock frequency

= f clock

t 2 2Tclock ..(2) 1 2 = = 2 f dclock = Tclock Tclock ..(3)

When the loop is locked, the clock rising edge is centered on the data; the time difference, t, between the dclock rising edge and the beginning of the data is simply conditions, may be written as

Tclock / 2 or

Tdclock / 4 (Figure 1c). Therefore, the phase difference between dclock and the data, under locked

2 ..(4)

} = K PD

input

The average voltage out of the phase detector may be expressed by

..(5) where the gain of the PD may be written as

VPDout = VDD

46

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

K PD =

VDD

(V / radians)

..(6)

To understand how the phase detector works, see diagrams shown in fig 1. If the data signal and clock signal edges start and stop at same time, (figure 1a), phase difference is zero hence the XOR output,

VPDout

, is 0V. As shown in figure 1b & 1c, the phase difference is 3 / 4 and / 2 .

Figure 1. XOR PD output for various inputs As shown in figure 1 the implementation of XOR Phase Detector in sub- nanometer CMOS technology which is used in PLL to lock the phase of the feedback signals with reference clock signal. The figure 2,3,4,5,6,7,8,9,10,11,12,13,14,15,16 shows the implementation, simulation results, characterization and detailed analysis of the XOR PD when the reference and feedback signals are out of phase by zero, /2, , 3/2, 2 respectively. Here we consider feedback signal dclock signal is leading with respect to data signal and vice-versa, we get the final characteristic as plotted in figure 17.

Figure 2. Implementation of CMOS XOR Phase Detector

47

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 3. XOR Phase Detector with Phase Difference = 0

Figure 4. Characterization of XOR Phase Detector with Phase Difference = 0

48

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 5. XOR Phase Detector with Phase Difference = /2 (when dclock leads data by /2)

Figure 6. XOR Phase Detector with Phase Difference = /2 (when data leads dclock by /2)

49

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 7. Characterization of XOR Phase Detector with Phase Difference = /2

Figure 8. XOR Phase Detector with Phase Difference = (when dclock leads data by )

50

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 9. XOR Phase Detector with Phase Difference = (when data leads dclock by )

Figure 10. Characterization of XOR Phase Detector with Phase Difference =

51

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 11. XOR Phase Detector with Phase Difference = 3/2 (when dclock leads data by 3/2)

Figure 12. XOR Phase Detector with Phase Difference = 3/2 (when data leads dclock by 3/2)

52

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 13. Characterization of XOR Phase Detector with Phase Difference = 3/2

Figure 14. XOR Phase Detector with Phase Difference = 2 (when dclock leads data by 2)

53

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 15. XOR Phase Detector with Phase Difference = 2 (when data leads dclock by 2)

Figure 16. Characterization of XOR Phase Detector with Phase Difference = 2 The XORPD input/output transfer characteristic graph is a plot of average output voltage avg versus the phase difference . The XOR PD characteristic plot is shown in figure 17. As

54

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

shown in figure 17, when the reference clock signal is delayed with respect to feedback signal, the phase difference becomes negative and we get same average voltage avg that we have got when the feedback signal was delayed by zero, /2, , 3/2, 2 with respect to the reference clock signal.

Figure 17. Input/output transfer characteristic of CMOS XOR Phase Detector 4. CMOS LAYOUT DESIGN We have observed the implementation of XOR phase detector now see below figure 18 & 19 shows the CMOS layout design for the XOR phase detector simply verified truth table of the XOR gate or we can say it detect when there is any change in its input phase.

Figure 18. CMOS design layout of XOR phase detector

55

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

Figure 19. Output result of XOR phase detector

5. CONCLUSION

The major disadvantage of XOR Phase Detector is that it can lock onto harmonics of the reference clock signal and most importantly it cannot detect a difference in frequency. To take care of these disadvantages, we have implemented the Phase Frequency Detector, which can detect a difference in phase and frequency between the reference clock signal and feedback signals.

ACKNOWLEDGEMENTS

I would like to hartley thank full to Prof. Jay Karan Singh who guided and promoted me for such a work. Than I would like to give sincere thank to Mr. Bharat Nagpara who helped me whenever required.

REFERENCES

[1] Low Power 1 GHz Charge Pump Phase-Locked Loop in 0.18 m CMOS Process 17th International Conference "Mixed Design of Integrated Circuits and Systems", June 24-26, 2010, Poland. [2] A Low Noise CMOS Phase Locked Loop, 978-1-4244-7161-4/10/$26.00 2010 IEEE. [3] The Design and Simulation of a VCO in CMOS Digital PLL 2011 Fourth International Conference on Intelligent Computation Technology and Automation. [4] A CMOS VCO for lV, lGHz PLL Applications, 2004 IEEE Asia-Pacific Conference on Advanced System Integrated Circuits(AF'-ASIC2004)/ Aug. 4-5,2004.

56

Advanced Computing: An International Journal ( ACIJ ), Vol.2, No.6, November 2011

H. I. Delvadiya. A PG Student form Shree SatyaSai Institute Of Science & Technology, Sehore, Bhopal, MP. He is Completed BE in Electronics & Communication (EC) from V.V.P. Engg. College Rajkot, Gujarat in 2008, DE (EC) from A.V.P.T.I. Rajkot, Gujarat in 2005. His area of interest is VLSI Technology and Embedded System & Wireless Communication. Prof. Mukesh Tiwari. He had completed M.Tech from RGPV university, Bhopal, MP, India. He is working as Director of institute & professor at department of Electronics and Communication at Shree Satya Sai Institute of Science and Technology, Sehore, Bhopal, MP. His area of interest is Wireless Communication, VLSI Design. Prof. Jay Karan Singh. He is Research scholar Electronics and Communication in RGPV University, Bhopal. He had completed M.Tech in Microelectronics and VLSI design in 2009 from RGPV university, Bhopal. He is working as Professor and Head of department of Electronics and Communication at Shree Satya Sai Institute of Science and Technology, Sehore, Bhopal, MP. His area of interest is Wireless Communication, Microelectronics, VLSI Design.

57

S-ar putea să vă placă și

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Advanced Computing: An International Journal (ACIJ)Document1 paginăAdvanced Computing: An International Journal (ACIJ)Anonymous IlrQK9HuÎncă nu există evaluări

- Advanced Computing: An International Journal (ACIJ)Document2 paginiAdvanced Computing: An International Journal (ACIJ)Anonymous IlrQK9HuÎncă nu există evaluări

- Advanced Computing: An International Journal (ACIJ)Document2 paginiAdvanced Computing: An International Journal (ACIJ)Anonymous IlrQK9HuÎncă nu există evaluări

- Advanced Computing: An International Journal (ACIJ)Document1 paginăAdvanced Computing: An International Journal (ACIJ)Anonymous IlrQK9HuÎncă nu există evaluări

- Advanced Computing An International Journal ACIJDocument1 paginăAdvanced Computing An International Journal ACIJAnonymous IlrQK9HuÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- TQM BisleriDocument27 paginiTQM BisleriDishank ShahÎncă nu există evaluări

- Delta PresentationDocument36 paginiDelta Presentationarch_ianÎncă nu există evaluări

- Safety Data Sheet: Fumaric AcidDocument9 paginiSafety Data Sheet: Fumaric AcidStephen StantonÎncă nu există evaluări

- Floor Paln ModelDocument15 paginiFloor Paln ModelSaurav RanjanÎncă nu există evaluări

- Canopy CountersuitDocument12 paginiCanopy CountersuitJohn ArchibaldÎncă nu există evaluări

- Class 11 Accountancy NCERT Textbook Chapter 4 Recording of Transactions-IIDocument66 paginiClass 11 Accountancy NCERT Textbook Chapter 4 Recording of Transactions-IIPathan KausarÎncă nu există evaluări

- Huawei Core Roadmap TRM10 Dec 14 2011 FinalDocument70 paginiHuawei Core Roadmap TRM10 Dec 14 2011 Finalfirasibraheem100% (1)

- Health, Safety & Environment: Refer NumberDocument2 paginiHealth, Safety & Environment: Refer NumbergilÎncă nu există evaluări

- V Series: Three Wheel, Counterbalanced Lift TruckDocument126 paginiV Series: Three Wheel, Counterbalanced Lift TruckВиктор МушкинÎncă nu există evaluări

- Hierarchy of The Inchoate Crimes: Conspiracy Substantive CrimeDocument18 paginiHierarchy of The Inchoate Crimes: Conspiracy Substantive CrimeEmely AlmonteÎncă nu există evaluări

- AkDocument7 paginiAkDavid BakcyumÎncă nu există evaluări

- IP Based Fingerprint Access Control & Time Attendance: FeatureDocument2 paginiIP Based Fingerprint Access Control & Time Attendance: FeaturenammarisÎncă nu există evaluări

- Syed Hamid Kazmi - CVDocument2 paginiSyed Hamid Kazmi - CVHamid KazmiÎncă nu există evaluări

- Majalah Remaja Islam Drise #09 by Majalah Drise - Issuu PDFDocument1 paginăMajalah Remaja Islam Drise #09 by Majalah Drise - Issuu PDFBalqis Ar-Rubayyi' Binti HasanÎncă nu există evaluări

- Sangeetahealingtemples Com Tarot Card Reading Course in UsaDocument3 paginiSangeetahealingtemples Com Tarot Card Reading Course in UsaSangeetahealing templesÎncă nu există evaluări

- MEMORANDUMDocument8 paginiMEMORANDUMAdee JocsonÎncă nu există evaluări

- Quantum Hopfield NetworksDocument83 paginiQuantum Hopfield NetworksSiddharth SharmaÎncă nu există evaluări

- Hitt PPT 12e ch08-SMDocument32 paginiHitt PPT 12e ch08-SMHananie NanieÎncă nu există evaluări

- Sales Manager Latin AmericaDocument3 paginiSales Manager Latin Americaapi-76934736Încă nu există evaluări

- Drill String DesignDocument118 paginiDrill String DesignMohamed Ahmed AlyÎncă nu există evaluări

- Exercise 23 - Sulfur OintmentDocument4 paginiExercise 23 - Sulfur OintmentmaimaiÎncă nu există evaluări

- Windsor Machines LimitedDocument12 paginiWindsor Machines LimitedAlaina LongÎncă nu există evaluări

- Estimation and Detection Theory by Don H. JohnsonDocument214 paginiEstimation and Detection Theory by Don H. JohnsonPraveen Chandran C RÎncă nu există evaluări

- Notice For AsssingmentDocument21 paginiNotice For AsssingmentViraj HibareÎncă nu există evaluări

- ReviewerDocument2 paginiReviewerAra Mae Pandez HugoÎncă nu există evaluări

- Terms and Conditions 27 06 PDFDocument4 paginiTerms and Conditions 27 06 PDFShreyash NaikwadiÎncă nu există evaluări

- Braga - 2016 - On Standing's A Precariat Charter - Confronting The Precaritisation of Labour in Brazil and PortugalDocument12 paginiBraga - 2016 - On Standing's A Precariat Charter - Confronting The Precaritisation of Labour in Brazil and PortugalLiam MurciaÎncă nu există evaluări

- August 2015Document96 paginiAugust 2015Cleaner MagazineÎncă nu există evaluări

- Political Positions of Pete ButtigiegDocument12 paginiPolitical Positions of Pete ButtigiegFuzz FuzzÎncă nu există evaluări

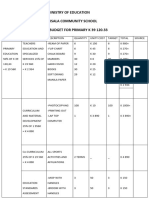

- Ministry of Education Musala SCHDocument5 paginiMinistry of Education Musala SCHlaonimosesÎncă nu există evaluări