Documente Academic

Documente Profesional

Documente Cultură

(IJ) A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter Byeong-Cheol Hyeon Bo-Hyung Cho

Încărcat de

efremofeDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

(IJ) A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter Byeong-Cheol Hyeon Bo-Hyung Cho

Încărcat de

efremofeDrepturi de autor:

Formate disponibile

14

Journal of Power Electronics, Vol. 10, No. 1, January 2010

JPE 10-1-3

A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter

Byeong-Cheol Hyeon and Bo-Hyung Cho

Dept.

of Electrical and Electronics Eng., Seoul National University, Seoul, Korea

Abstract In this paper, a tightly regulated triple output asymmetrical half bridge yback (ASHF) converter is proposed. In order to regulate all output voltages, pulse frequency modulation (PFM), pulse width modulation (PWM) and phase delay (PD) are used simultaneously. In comparison with the conventional PWM-PD method, the interactions among the control variables are minimized and the operating range is increased. By the utilization of a multi winding transformer, the auxiliary transformer and the blocking capacitor are eliminated and the size and cost of the proposed converter is reduced. The operation principle of the converter is explained and the modes of operation are investigated. Based on the results, the steady state characteristics of the converter are explored. A 24V/10A, 12V/5A, 5V/10A hardware prototype is built and tested to verify the analysis results and the voltage regulation of the triple outputs of the proposed converter. Key Words: Asymmetrical half bridge yback, PFM-PWM-PD method, Triple outputs

I. I NTRODUCTION Multiple output DC/DC converters are widely used in switched-mode power supplies (SMPS) due to their competitive cost and size. In order to achieve a tightly regulated output voltage, various post regulation schemes have been proposed. Representative realizations include synchronous switch post regulation (SSPR) which utilizes an auxiliary switch, PWMPD and PWM-PFM control, mag-amp approaches. Among them, a multiple output converter using several control variables is advantageous in cost saving and size reduction because it operates without additional switches. A forward-yback converter using the PWM-PFM method has been proposed [1], [2]. However, the voltage ratio between the two outputs is prexed and the load range is highly limited. An asymmetrical half bridge converter with PWM-PD control has been studied [3]. Although the output voltages are well regulated, the input voltage range is narrow and auxiliary circuitries are required for the third output. In this paper, a tightly regulated triple output asymmetrical half bridge yback converter (ASHF) is proposed. The converter is controlled by the proposed PFM-PWM-PD method and the interactions among the controllers are minimized. As a result, the input voltage and load range can be increased. In addition, the auxiliary transformer for the third output voltage in a conventional power stage is eliminated through the utilization of the multi windings from the existing transformers.

Manuscript received Aug. 17, 2009; revised Nov. 17, 2009 Corresponding Author: novasa@naver.com Tel: +82-880-1785, Fax: +82-878-1452, Seoul National University Dept. of Electrical Eng., Seoul National University, Korea

This paper is organized as follows. The circuit conguration and operation principle of the proposed converter are explained in Section 2. In Section 3, the modes of operation of the proposed converter are examined. Then the steady state characteristics such as the dc voltage gains and the interactions among the three output voltages are investigated. A 320V-400V input range, 24V/10A, 5V/10A and 12V/5A hardware prototype is built to demonstrate the performance of the proposed converter. The experimental results are illustrated in Section 4. The conclusions are summarized in Section 5. II. O PERATING PRINCIPLE OF THE PROPOSED PFM-PWM-PD METHOD A circuit diagram of the ASHF with the PWM-PD method referred to in [3] is shown in Fig. 1(a). The auxiliary transformer, T3 and the blocking capacitor, Cb3 , are required for vo3 . The ASHF PWM converter, which is a main topology of the proposed method, has been widely used as a front end dc/dc converter due to the following advantages: 1) clamped switch voltage to the input voltage; 2) ZVS of MOSFETs and ZCS of the rectier diode; 3) xed switching frequency. The operating principle of a conventional PWM-PD is shown in Fig. 2(a). The rst and second output voltage, vo1 and vo2 , are regulated using duty ratios of S1 (DS1 ) and S3 (DS3 ) respectively. The third output voltage, vo3 , is controlled by the phase delay ratio (Dp ) between the gate driving signals for S1 and S3 . Since Dp is generated by the difference between DS1 and DS3 , the maximum range of Dp is dependent on the actions of vo1 and vo2 . This means the interactions among the converters are strong and the input voltage and the load range

A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter

15

(a) The conventional ASHF converter with PWM-PD Fig. 1.

(b) The proposed ASHF converter with PFM-PWM-PD

The circuit diagram of the conventional and proposed converter.

III. S TEADY STATE CHARACTERISTICS OF THE PROPOSED

CONVERTER

A. Mode analysis of the proposed converter The modes of operation of the ASHF converter with PWM control have been explained in previous studies [5][9]. In this paper, the operations of the proposed converter which includes a dual ASHF and a multi winding transformer are investigated. The key operating waveforms of the proposed converter are shown in Fig. 3. To simplify the analysis, the current of Lo is assumed to be constant. M1(t0 t1 ): S3 is turned on. The input voltage, vg , increases the current of the magnetizing inductance, Lm1 . Due to the dot convention in the T1 , rectier diode, DrH , is turned off. S2 is turned on and the stored energy in Cb2 is released to Ro2 through Lm2 and Llk2 . The equations are written as (1) and (2). The energy is transferred from vg to vo3 through the multi winding of T1 and T2 . This mode ends when S2 is turned off. vg vCb1 (t0 ) sin(o t) Zo N1p vo3 + + iLm1 (t0 ) cos(o t) N1t Ro3 vCb1 (t) = vCb1 (t0 ) cos(o t) + vg (1 cos(o t)) N1p vo3 + iLm1 (t0 ) Zo sin(o t) + N1t Ro3 iLlk1 (t) = where, o = 1 , Zo = Llk1 + Lm1 Cb1

(a) PWM-PD control scheme

(b) Proposed PFM-PWM-PD control scheme Fig. 2. Operating principle of the proposed converter.

(1)

are limited. These problems result in an increase in the input capacitance to satisfy the hold-up requirement [4]. In the proposed ASHF converter with the PFM-PWMPD method from Fig. 1(b), the transformer T3 and the DC blocking capacitor Cb3 in Fig. 1(a) are eliminated by utilizing the multi windings of the transformers, T1 and T2 . Due to the connection of the multi windings, the voltages across the windings are similar to the conventional converter. The operating principle of the proposed converter is shown in Fig. 2(b). The PFM method is applied for the regulation of vo1 and its duty ratio, DS3 , is xed to 50%. Thus, the maximum range for Dp is equal to DS3 and it is independent of the load current. To reduce the interaction, vo2 is controlled by the PWM method which uses DS1 as a control variable in this paper.

(2)

(Llk1 + Lm1 )Cb1 M2(t1 t2 ): The body diode of S1 is turned on by the negative current of Llk2 . To achieve ZVS, S1 is turned on during this period. Since the polarities of the voltage across Llk2 and Lm2 are opposite, iLlk2 is increased and iLm2 is decreased. Thus, the current becomes zero due to the relation of (3) and then DrL is turned off softly. iDrL (t) = N2p (iLlk2 (t) iLm2 (t)) N2s (3)

16

Journal of Power Electronics, Vol. 10, No. 1, January 2010

voltage equations in this mode are dened in (5) and (6). vCb1 (t) = vCb1 (t3 ) cos(1 t) + iLlk1 (t3 )Z1 sin(1 t) N1p (5) + vo1 (1 cos(1 t)) N1s iLlk1 (t) = iLm1 (t3 ) cos(1 t) N1p (6) vo1 vCb1 (t3 ) + N1s sin(1 t) Z1 Llk1 1 , Z1 = . Cb1 Llk1 Cb1 To achieve the monotonic slope in voltage gain for vo3 with respect to Dp , the turns ratios of T1 and T2 should be designed so that the voltage summation of vT 1 and vT 2 becomes almost zero during this period. Current commutation occurs in the rectiers for vo3 due to a low vR3 . Thus, the current of the tertiary winding in T1 is reected to the secondary winding and it is added to the reected current from the primary winding. The increased iDrH during this mode is marked in Fig. 3. M5(t4 t5 ): The body diode of S2 is turned on by the positive current of Llk2 and Lm2 . The stored energy in Cb2 is released to Ro2 and iLlk2 is linearly decreased because vCb2 is constant. DrL conducts and Lm2 is reset by the reected vo2 . Thus, iLm2 is also decreased linearly. The current difference between iLlk2 and iLm2 ows to the load. The current equation of this mode is given by: where, 1 = iLlk2 (t) = iLm2 (t4 ) VCb2 t Lm2 + Llk2 (7)

Due to the dot convention, the current relation in T2 is expressed as (8). Thus, the reected dc current of ILo is subtracted from the reected current of the primary winding of T2 . iDrL =

Fig. 3. The steady state waveforms of the proposed converter.

1 (N2p (iLlk2 iLm2 ) N2s ILo ) N2t

(8)

M3(t2 t3 ): iLm2 is increased linearly by vg and Cb2 is charged through the current. The energy is transferred from vg to vo3 through T1 and T2 . The current equation of this mode is expressed in (4).

M6(t5 t6 ): S4 is turned off and the body diode of S3 conducts. Due to the positive voltage across Llk1 , the current is increased while the current of Lm1 is decreased by the reected vo2 . When the two currents meet, DrH is turned off softly due to the similar relation of (3).

B. Voltage gains of the proposed converter vg VCb2 N2p iLlk2 (t) = iLm2 (t2 ) + t+ ILo Lm2 + Llk2 N2t (4) The voltage gain of vo1 according to the switching frequency can be found from the modes of operation. To simplify the explanation, the transition modes, M2 and M6, are neglected because the time duration of these modes is much shorter than the switching period. Derivation of the voltage gain is similar to the LLC resonant converter case except that the resonant elements of the proposed converter only store the energy from the input voltage during DS1 Ts . The resonant frequency of this period which is dened in (1) and (2) is used. The usage of the half wave rectier is also considered.

where, VCb2 and ILo are the averaged values of Cb1 and Lo . They are equal to DS3 vg and the load current of vo3 respectively. M4(t3 t4 ): S3 is turned off at t3 . The stored energy in Cb1 is released to Ro1 through Llk1 . Thus, resonance between Llk1 and Cb1 starts. DrH becomes conductive and the voltage across Lm1 is clamped to the reected vo1 . The current and

A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter

17

(a) M1

(b) M2

(c) M3

(d) M4

(e) M5 Fig. 4. The modes of operation of the proposed converter.

(f) M6

The voltage gain for vo1 is expressed as (9). vo1 M1 = = vg Np1 Q= 2Ns1 sin DS3 2

2

k1 + 1 1 + Q2 k1 n 2

1 n n

(9)

Z2 4Ro1 Np1 2 Llk1 s , Rac = , k1 = , n = 2N 2 Rac Lm1 2 s1 Lm1 1 Llk2 Z2 = , 2 = , k2 = Cb1 Lm2 Lm1 Cb1

The voltage gain for vo2 was found in previous studies [5] [9] because it is controlled by the PWM method. Due to the inductive output lter in Fig. 1(b), the averaged value of the rectied voltage, vR3 , is the same as vo3 . To nd out the relation between vo3 and Dp , the waveforms in Fig. 3 are used. For the steady state voltage gain, the average value of vCb1 is used to obtain a simple design equation. vCb1 DS3 vg = (11)

(10)

where, 2 is the modied resonant frequency, Z2 is the modied characteristics impedance, n is the normalized switching frequency, Q is the quality factor, Rac is the reected load resistance to the primary side of T1 while k1 and k2 are the inductance ratios between the magnetizing and resonant inductance. The obtained voltage gain for vo1 is compared with the results of the circuit simulation. The PLECS toolbox in MATLAB with a practical switching circuit model is utilized. It shows that the simplied analytical voltage gain function is good enough to obtain the initial design strategies for all load conditions.

The winding voltages of the primary side in T1 and T2 through the multi windings are summarized in Table 1. Applying (11), the gains for the other output voltages in xed switching frequency can be approximated. Vo2 N2s Vo1 N1s DS3 , DS1 = = vg N1p vg N2p (12)

The compensation factor, , should be multiplied because the voltage gain for vo1 is affected by the switching frequency and is obtained from the gain curve in Fig. 5. vo3 is calculated by the averaged value listed in Table 1. The approximated voltage gain is shown in Fig. 6. The slope of the voltage gain becomes zero when Dp is less than (DS3 DS1 ). This means

18

Journal of Power Electronics, Vol. 10, No. 1, January 2010

TABLE I R ECTIFIED WINDING VOLTAGE (vR3 ) AND OPERATING MODE DS3 DS1 + Dp vR3 N1t N2t vo1 vo2 N1s N2s N1t (1 DS3 )vg N2t vo2 N1p (1 + k1 ) N2s N1t (1 DS3 )vg N2t (1 DS1 )vg + N1p (1 + k1 ) N2p (1 + k2 ) N1t N2t (1 DS1 )vg vo1 + N1s N2p (1 + k2 ) DS3 > DS1 + Dp vR3 N1t N2t vo1 vo2 N1s N2s N1t (1 DS3 )vg N2t vo2 N1p (1 + k1 ) N2s N1t (1 DS3 )vg N2t (1 DS1 )vg + N1p (1 + k1 ) N2p (1 + k2 ) N1t (1 DS3 )vg N2t vo2 N1p (1 + k1 ) N2s

mode M5 M1 M3 M4

time duration mode (1 DS3 ) M5 (DS1 + Dp DS3 ) Dp DS3 Dp DS1 + Dp DS3 M1 M3 M4

time duration (1 DS3 ) Dp DS1 DS3 (DS1 + Dp )

(a) Voltage gain @ Ro1 = 2.4 Fig. 6. Approximated gain curve for vo3 according to DS1 and Dp .

(b) Voltage gain @ Ro1 = 24 Fig. 5. Gain comparison between the model in (9) and Switching circuit simulation. Fig. 7. Simulated gain curve for vo3 according to DS1 and Dp .

that the effect of a phase delay occurs within the overlapped area between DS3 and DS1 . Also, the operating range of Dp is limited by DS3 . Thus, the minimum for DS1 is required to prevent abnormal operation. To verify the analytical gain function, the voltage gain for vo3 is obtained through the switching circuit simulation as shown in Fig. 7. The gain difference between the analytical and simulated result is small when DS1 is low, but as DS1 increases, the error becomes large. However, the approximated gain curve can be used in the initial design process. The interactions between the three output controls are

investigated. The effects of DS1 and Dp in vo1 (M1 ) are illustrated in Fig. 8. When fs =120kHz and fs = 150kHz, almost no variations are observed (at planes). This means the variations according to DS1 and Dp variances are negligible during operation. Although a small variation is observed in the low switching frequency (85kHz), it is less than 0.01. The effects of Dp and fs in vo2 (M2 ) are shown in Fig. 9. It is observed that M2 is not affected by the variation of Dp and fs when DS1 = 0 and 0.2. In the case of DS1 = 0.4, the

A Tightly Regulated Triple Output Asymmetrical Half Bridge Flyback Converter

TABLE II T HE PARAMETERS OF THE PROPOSED CONVERTER Device Value Device Value co1 6mF N1p : N1s : N1t 17:2:1 co2 13.2mF N2p : N2s : N2t 42:3:3 co3 1.5mF Lm1 /Llk1 135uH/45uH T1 EER4950s Lm2 /Llk2 300uH/50uH T2 EER3542s Lo 3.3uH MOSFET FQA18N60 Core forLlk2 EI20 Diode KCH30A10 Cb1 33nF fs (kHz) 80 140 Cb2 1uF Core forLo Bar core ( = 6]mm, l = 35mm)

19

Fig. 8.

The interactions of DS1 and Dp to M1 .

Fig. 10.

The steady state waveforms under @vg = 380V, full load.

Fig. 9.

The interactions of fs and Dp to M2 .

variation is less than 0.005. From the results, the interactions among the control variables are small in the PFM-PWM-PD method. Therefore the input and load range can be widened. IV. E XPERIMENTAL VERIFICATION In this section, a hardware prototype is built and tested to verify the analysis results and to demonstrate the voltage regulation of the three output voltages in the proposed converter. The designed circuit parameters are listed in Table 2. T1 is manufactured using the sectional winding technique in [10]. The leakage inductance of T1 is utilized as a series resonant inductor. A small size output lter inductor using a bar type ferrite core is applied to Lo . To verify the output voltage regulation of the proposed converter three feedback loops with a dsPIC33FJ16GS502 are implemented. The steady state waveforms under 380V of input voltage are shown in Fig. 10. The waveforms and phase delay are similar to the analysis results in Fig. 3. The experimental dc voltage gain for vo3 is measured and shown in Fig. 12. The curves show good agreement with the result in Fig. 7.

The results of the output voltage regulation are illustrated in Fig. 11. The load current is changed from 10% to 100%. For the step load change of io1 , the voltage variation (in Fig. 11(a)) of vo1 is less than 2V (8.3%) in the transient period using a PFM control loop. Almost no voltage variations are observed in vo2 and vo3 . In the case of an experiment where io2 is changed, vo2 is also well regulated by PWM control and a small variation is shown in Fig. 11(b). In the case of a change in io3 , vo3 is regulated less than 2V in the transient period. The other output voltages are regulated within 0.5V. In the steady state, all output voltage variations according to the load current are almost zero as shown in Fig. 11. V. C ONCLUSIONS This paper proposes a tightly regulated triple output ASHF converter with PFM-PWM-PD control. The auxiliary circuitries in the conventional approach such as a transformer and a blocking capacitor are eliminated by the utilization of the multi windings of the proposed converter. The modes of operation were explained and the steady state characteristics were investigated. From the analysis result, the minimum interactions among the control variables were veried. The proposed converter and control scheme were implemented with a 24V/10A, 5V/10A and 12V/5A hardware prototype using a 16bit digital controller. The measured voltage gain and operating waveforms veried the analysis results and tight output voltage regulation in the steady state for different loads was conrmed.

20

Journal of Power Electronics, Vol. 10, No. 1, January 2010

(a) io1 : 1A 10A Fig. 11.

(b) io2 : 1A 10A

(c) io3 : 0.5A 5A

The regulation performances of the output voltages respect to the load change.

[7] J. H. Jung and J. G. Kwon, Soft switching and optimal resonance conditions of APWM HB yback converter for high efciency under high output current, in Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, pp. 2994-3000, 2008. [8] T. M. Chen and C. L. Chen, Small-Signal Modeling of Asymmetrical Half Bridge Flyback Converter, in Power Electronics and Motion Control Conference, 2006. IPEMC 2006. CES/IEEE 5th International, pp. 1-5, 2006. [9] J. H. Jung, J. M. Choi and J. G. Kwon, Design Methodology for Transformers Including Integrated and Center-tapped Structures for LLC Resonant Converters, Journal of Power Electronics, Vol. 9, pp. 215-223, 2009. [10] H. S. Choi, Design Consideration of Half-Bridge LLC Resonant Converter, Journal of Power Electronics, Vol. 7, pp. 13-20, 2007. Byeong-Cheol Hyeon received a B.S. degree in electrical engineering from KyungPook National University (KNU), Daegu, Korea, in 2004 and a M.S. degree from Seoul National University (SNU), Seoul, Korea, in 2006 where he is currently pursuing his Ph.D. His interests include resonant converters, multiple output converters, power factor correction circuits and contactless energy transmission. Mr. Hyeon is a Student Member of the IEEE and the Korean Institute of Power Electronics (KIPE). Bo-Hyung Cho received his B.S. and M.E. degrees in Electrical Engineering from the California Institute of Technology, Pasadena. He received his Ph.D. also in Electrical Engineering, from Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, Virginia. Prior to his research at Virginia Tech, he worked for two years as a technical staff member in the Power Conversion Electronics Department at the TRW Defense and Space System Group. From 1982 to 1995, he was a professor in the Department of Electrical Engineering at Virginia Tech. He joined the school of Electrical Engineering at Seoul National University, Seoul, Korea in 1995 and he is presently a Professor. His main research interests include power electronics, modeling, analysis and control of spacecraft power processing equipment, power systems for space stations and space platforms, and distributed power systems. Prof. Cho received the 1989 Presidential Young Investigator Award from the National Science Foundation. He is a member of Tau Beta Pi.

Fig. 12.

The measured voltage gain (M3 ) according to DS1 and Dp .

R EFERENCES

[1] J. Sebastian and J. Uceda, The Double Converter: A Fully Regulated Two-Output DC-DC Converter, Power Electronics, IEEE Transactions on, Vol. PE-2, pp. 239-246, 1987. [2] H. E. Tacca, Single-switch two-output yback-forward converter operation, Power Electronics, IEEE Transactions on, Vol. 13, pp. 903-911, 1998. [3] Yanjun Zhang and Dehong Xu, Design and Implementation of an Accurately Regulated Multiple Output ZVS DC-DC Converter, Power Electronics, IEEE Transactions on, Vol. 22, pp. 1731-1742, 2007. [4] Y. T. Jang, M. M. Jovanovic, and D. L. Dillman, Hold-up time extension circuit with integrated magnetics, in Applied Power Electronics Conference and Exposition, 2005. APEC 2005. Twentieth Annual IEEE, Vol. 1, pp. 219-225, 2005. [5] D. H. Seo, O. J. Lee, S. H. Lim, and J. S. Park, Asymmetrical PWM yback converter, in Power Electronics Specialists Conference, 2000. PESC 00. 2000 IEEE 31st Annual, Vol. 2, pp. 848-852, 2000. [6] Han Li, W. Zhou, S. Zhou and Xiao. Yi, Analysis and design of high frequency asymmetrical half bridge yback converter, in Electrical Machines and Systems, 2008. ICEMS 2008. International Conference on, pp. 1902-1904, 2008.

S-ar putea să vă placă și

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsDe la EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsÎncă nu există evaluări

- 3@1s PFC ConverterDocument5 pagini3@1s PFC Converterranjith120198Încă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- A New Single Switch Buck-Boost Type DC-DC ConverterDocument4 paginiA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrÎncă nu există evaluări

- PWMDocument7 paginiPWMsiddhartha_anirban100% (1)

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDocument6 paginiImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupÎncă nu există evaluări

- A Unity Power Factor Converter Using HalfDocument14 paginiA Unity Power Factor Converter Using HalfLivia Faria PeresÎncă nu există evaluări

- Maswood 01035144Document9 paginiMaswood 01035144rahulanlÎncă nu există evaluări

- Power Factor Correction in Zeta Converter Fed PMBLDCM Drive For An Air ConditionerDocument6 paginiPower Factor Correction in Zeta Converter Fed PMBLDCM Drive For An Air ConditionertheijesÎncă nu există evaluări

- A Transformerless Grid Connected Photovoltaic Inverter With Switched CapacitorsDocument5 paginiA Transformerless Grid Connected Photovoltaic Inverter With Switched CapacitorsRaye PushpalathaÎncă nu există evaluări

- Using Activ BufferDocument7 paginiUsing Activ Bufferranjith120198Încă nu există evaluări

- Bidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsDocument5 paginiBidirectional DC-DC Converter With Full-Bridge / Push-Pull Circuit For Automobile Electric Power SystemsPaulo UchihaÎncă nu există evaluări

- Three-Phase Fly-Back AC/DC Converter With Novel Resonant Snubber CircuitDocument5 paginiThree-Phase Fly-Back AC/DC Converter With Novel Resonant Snubber CircuitKarthik KumarÎncă nu există evaluări

- Resonant DC Link in PWM AC ChopperDocument5 paginiResonant DC Link in PWM AC ChopperMukesh SharmaÎncă nu există evaluări

- Harmonic Reduction in Three-Phase ParallelDocument6 paginiHarmonic Reduction in Three-Phase ParallelAhmed JanadÎncă nu există evaluări

- 6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFDocument12 pagini6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFmajidÎncă nu există evaluări

- High-Frequency Soft-Switching DC-DC Converters For Voltage and Current DC Power SourcesDocument18 paginiHigh-Frequency Soft-Switching DC-DC Converters For Voltage and Current DC Power SourcesFaraz AhmadÎncă nu există evaluări

- CYCLOCONVERTERDocument17 paginiCYCLOCONVERTERRachmat Guntur Dwi Putra100% (1)

- DesignFeatures 3-1110Document10 paginiDesignFeatures 3-1110khaled1512Încă nu există evaluări

- PWM-Switch Modeling DC-DC Converters: HermanDocument7 paginiPWM-Switch Modeling DC-DC Converters: HermanChristopher RosaÎncă nu există evaluări

- Resonant Converter Power Supply For Arc Welding ApplicationDocument5 paginiResonant Converter Power Supply For Arc Welding Applicationshado2010Încă nu există evaluări

- LCI Firing AngleDocument6 paginiLCI Firing AngleMuthamil KumaranÎncă nu există evaluări

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingDocument13 paginiDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luÎncă nu există evaluări

- Shiwani Ref3Document6 paginiShiwani Ref3PRACHI KATAREÎncă nu există evaluări

- Novel Sngle Phase ZCSDocument7 paginiNovel Sngle Phase ZCSAntonio Hadade NetoÎncă nu există evaluări

- AC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveDocument9 paginiAC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveIJERDÎncă nu există evaluări

- Study of Impulse Voltage Distribution in Transformer WindingsDocument5 paginiStudy of Impulse Voltage Distribution in Transformer WindingsBhuvanes Waran100% (1)

- Statespace Model FWD ConverterDocument4 paginiStatespace Model FWD ConverterrogerozÎncă nu există evaluări

- Lin 2013Document12 paginiLin 2013Pavan Singh TomarÎncă nu există evaluări

- VX Ring Suppression: Current Sensor ADocument2 paginiVX Ring Suppression: Current Sensor AVijyashree IyerÎncă nu există evaluări

- Parallel Reasonance ConverterDocument43 paginiParallel Reasonance Converterchong151190Încă nu există evaluări

- VFTO in 550 KV GIS PDFDocument9 paginiVFTO in 550 KV GIS PDFCarlos Lino Rojas AgüeroÎncă nu există evaluări

- Design Considerations For Asymmetric Half Bridge ConvertersDocument16 paginiDesign Considerations For Asymmetric Half Bridge ConvertersGuilhermeFerreiraÎncă nu există evaluări

- Switching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Document17 paginiSwitching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Burlacu AndreiÎncă nu există evaluări

- 60W Flyback TIDocument16 pagini60W Flyback TIe_magazin3821Încă nu există evaluări

- Ieee Current ModeDocument7 paginiIeee Current ModepqqpÎncă nu există evaluări

- A New Passive 28-Step Current Shaper For Three-Phase RectificationDocument8 paginiA New Passive 28-Step Current Shaper For Three-Phase Rectificationkishor reddyÎncă nu există evaluări

- Novel Three-Phase PWM Voltage-Fed Rectifier With An Auxiliary Resonant Commutated Pole LinkDocument9 paginiNovel Three-Phase PWM Voltage-Fed Rectifier With An Auxiliary Resonant Commutated Pole LinkGabriel MejiaÎncă nu există evaluări

- Analysis and Design of SEPIC Converter in Boundary Conduction Mode For Universal-Line Power Factor Correction ApplicationsDocument6 paginiAnalysis and Design of SEPIC Converter in Boundary Conduction Mode For Universal-Line Power Factor Correction ApplicationsxynthianÎncă nu există evaluări

- (C12) PDFDocument6 pagini(C12) PDFSuhendra Dwi ParanaÎncă nu există evaluări

- 00878876Document6 pagini00878876jazzdeepakÎncă nu există evaluări

- Effect of BLDC Motor Commutation Schemes On Inverter Capacitor Size SelectionDocument5 paginiEffect of BLDC Motor Commutation Schemes On Inverter Capacitor Size SelectionXristos LianÎncă nu există evaluări

- Capacitor Balance in Anpc PDFDocument10 paginiCapacitor Balance in Anpc PDFSulthan Basha ShaikÎncă nu există evaluări

- Single Stage PFCconverterDocument10 paginiSingle Stage PFCconvertersquall8712Încă nu există evaluări

- International Conference Paper 2Document6 paginiInternational Conference Paper 2Vishal VnÎncă nu există evaluări

- Proposal of A Soft-Switching Single-PhaseDocument7 paginiProposal of A Soft-Switching Single-Phaseayie55Încă nu există evaluări

- Modified Z-Source Single-Phase Inverter For Single-Phase PM Synchronous Motor DrivesDocument6 paginiModified Z-Source Single-Phase Inverter For Single-Phase PM Synchronous Motor DrivesPRACHI KATAREÎncă nu există evaluări

- Analysis and Design of The Resonant Converter For Low Output Current RippleDocument9 paginiAnalysis and Design of The Resonant Converter For Low Output Current Rippleroughdraft2020Încă nu există evaluări

- Equivalent Circuits For Averaged Description of DC-DC Switch-Mode Power Converters Based On Separation of Variables ApproachDocument13 paginiEquivalent Circuits For Averaged Description of DC-DC Switch-Mode Power Converters Based On Separation of Variables Approach20021103 Vũ Đức DũngÎncă nu există evaluări

- DC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierDocument11 paginiDC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierRajni YadavÎncă nu există evaluări

- A Single-Phase Controlled Rectifier Using Single-Phase Matrix Topology IncorporatingDocument6 paginiA Single-Phase Controlled Rectifier Using Single-Phase Matrix Topology IncorporatingNwokolo Eric Onyekachi BrendanÎncă nu există evaluări

- Input Impedance Analysis of Single-Phase PFC ConvertersDocument7 paginiInput Impedance Analysis of Single-Phase PFC ConvertersCem CanerenÎncă nu există evaluări

- Asymmetrical Full-Bridge ConverterDocument9 paginiAsymmetrical Full-Bridge ConverterAthiesh KumarÎncă nu există evaluări

- Xi International PHD Workshop: Owd 2009, 17-20 October 2009Document6 paginiXi International PHD Workshop: Owd 2009, 17-20 October 2009vendasmbiÎncă nu există evaluări

- Ic Ldo CasfvfDocument10 paginiIc Ldo CasfvfLuis MuñozÎncă nu există evaluări

- High Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterDocument6 paginiHigh Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterKarthik KumarÎncă nu există evaluări

- Current Mode Versus Voltage ModeDocument14 paginiCurrent Mode Versus Voltage ModeqwertypointÎncă nu există evaluări

- Conv DC-DC Paper ENglishDocument5 paginiConv DC-DC Paper ENglishpepe890305Încă nu există evaluări

- ANN Switched Z-Source Inverter Based PV Generation System: AbstractDocument9 paginiANN Switched Z-Source Inverter Based PV Generation System: AbstractsathishÎncă nu există evaluări

- Three-Phase PWM Rectifier With Constant Switching Frequency: Abstract - in This Paper, A Novel AdaptiveDocument6 paginiThree-Phase PWM Rectifier With Constant Switching Frequency: Abstract - in This Paper, A Novel AdaptiveKuntal SatpathiÎncă nu există evaluări

- And8028 DDocument4 paginiAnd8028 DefremofeÎncă nu există evaluări

- Slva666 - Flyback TL494Document25 paginiSlva666 - Flyback TL494betodias30Încă nu există evaluări

- Input Filter Design For SMPSDocument21 paginiInput Filter Design For SMPSsenkum812002Încă nu există evaluări

- sc120 PDFDocument116 paginisc120 PDFefremofeÎncă nu există evaluări

- Designing With LDO RegulatorsDocument109 paginiDesigning With LDO RegulatorsEliza KottikaÎncă nu există evaluări

- Slva666 - Flyback TL494Document25 paginiSlva666 - Flyback TL494betodias30Încă nu există evaluări

- Us 5790354Document6 paginiUs 5790354efremofeÎncă nu există evaluări

- HP Pdp124pDocument1 paginăHP Pdp124pefremofe100% (2)

- External PNP Transistor CircuitDocument5 paginiExternal PNP Transistor Circuitefremofe100% (1)

- TL77xxA SeriesDocument32 paginiTL77xxA SeriesefremofeÎncă nu există evaluări

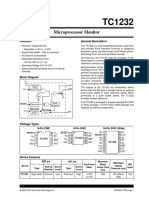

- TC1232Document24 paginiTC1232efremofeÎncă nu există evaluări

- IC Power OPAMPs Versatile and Efficient (An)Document6 paginiIC Power OPAMPs Versatile and Efficient (An)efremofeÎncă nu există evaluări

- Mic 29752Document40 paginiMic 29752efremofeÎncă nu există evaluări

- BSS101Document7 paginiBSS101efremofeÎncă nu există evaluări

- New Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFDocument4 paginiNew Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFefremofeÎncă nu există evaluări

- TRIAC Relay Contact Protection PDFDocument1 paginăTRIAC Relay Contact Protection PDFefremofeÎncă nu există evaluări

- TRIAC Relay Contact Protection PDFDocument1 paginăTRIAC Relay Contact Protection PDFefremofeÎncă nu există evaluări

- New Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFDocument4 paginiNew Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFefremofeÎncă nu există evaluări

- New Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFDocument4 paginiNew Low Cost Lead Resistance Compensation Technique For Resistive Sensors PDFefremofeÎncă nu există evaluări

- 11ak30 Service ModeDocument25 pagini11ak30 Service Moderom2002Încă nu există evaluări

- Implementation of High Step-Up Solar Power Optimizer For DC Micro Grid Application PDFDocument5 paginiImplementation of High Step-Up Solar Power Optimizer For DC Micro Grid Application PDFefremofeÎncă nu există evaluări

- High-Efficiency Diode-Clamped Linear AmplifierDocument10 paginiHigh-Efficiency Diode-Clamped Linear AmplifierefremofeÎncă nu există evaluări

- United States Patent: + T VCC CB (15 (16 H0 JVY/I - J:RDocument16 paginiUnited States Patent: + T VCC CB (15 (16 H0 JVY/I - J:RefremofeÎncă nu există evaluări

- LLC Converters Application - Note - Resonant LLC Converter Operation and Design - Infineon PDFDocument19 paginiLLC Converters Application - Note - Resonant LLC Converter Operation and Design - Infineon PDFFabio Pedroso de MoraisÎncă nu există evaluări

- Coping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFDocument6 paginiCoping W Poor Dynamic Performance of Super-Junction MOSFET Body Diodes PDFefremofeÎncă nu există evaluări

- Ep 24889895Document7 paginiEp 24889895efremofeÎncă nu există evaluări

- Ep 24889895Document7 paginiEp 24889895efremofeÎncă nu există evaluări

- Ep 24889895Document7 paginiEp 24889895efremofeÎncă nu există evaluări

- Ep 24889895Document7 paginiEp 24889895efremofeÎncă nu există evaluări

- Ep 24889895Document7 paginiEp 24889895efremofeÎncă nu există evaluări

- FactSet London OfficeDocument1 paginăFactSet London OfficeDaniyar KaliyevÎncă nu există evaluări

- G-3 L-17 Internal QuestionsDocument4 paginiG-3 L-17 Internal QuestionsActivity MLZS BarhÎncă nu există evaluări

- Pusheen With Donut: Light Grey, Dark Grey, Brown, RoséDocument13 paginiPusheen With Donut: Light Grey, Dark Grey, Brown, RosémafaldasÎncă nu există evaluări

- Las Tech Drafting 3Q WKDocument13 paginiLas Tech Drafting 3Q WKClemenda TuscanoÎncă nu există evaluări

- MA 106: Linear Algebra Tutorial 1: Prof. B.V. Limaye IIT DharwadDocument4 paginiMA 106: Linear Algebra Tutorial 1: Prof. B.V. Limaye IIT Dharwadamar BaroniaÎncă nu există evaluări

- Chapter 7 Dopant Diffusion - IDocument32 paginiChapter 7 Dopant Diffusion - I강준호Încă nu există evaluări

- Bravo MRI II Operation ManualDocument45 paginiBravo MRI II Operation ManualLuis100% (1)

- Diagnosis of TrypanosomiasisDocument82 paginiDiagnosis of TrypanosomiasisDrVijayata Choudhary100% (1)

- Blue Modern Company Profile PresentationDocument15 paginiBlue Modern Company Profile PresentationjaneÎncă nu există evaluări

- ACR39U-U1: (USB Type A) Smart Card ReaderDocument8 paginiACR39U-U1: (USB Type A) Smart Card Readersuraj18in4uÎncă nu există evaluări

- Coffee Quality Manual by Abra Rand Nig Use IDocument25 paginiCoffee Quality Manual by Abra Rand Nig Use IIpungÎncă nu există evaluări

- Mega StructuresDocument2 paginiMega StructuresSanthosh KumarÎncă nu există evaluări

- 3397 - Ciat LDC 300VDocument71 pagini3397 - Ciat LDC 300VPeradÎncă nu există evaluări

- Times Square C2C Cardigan: Finished Measurements NotionsDocument8 paginiTimes Square C2C Cardigan: Finished Measurements Notionsdiana.alyÎncă nu există evaluări

- Indoor Air Quality Standard Procedures - 2014 RevDocument12 paginiIndoor Air Quality Standard Procedures - 2014 RevFioriAmeliaHathawayÎncă nu există evaluări

- 5 Contracting Activity and Technical Staff RequirementsDocument2 pagini5 Contracting Activity and Technical Staff RequirementsDaniyar KussainovÎncă nu există evaluări

- ff2023 Web 0 0Document2 paginiff2023 Web 0 0khaing khantÎncă nu există evaluări

- Phrasal Verbs Related To HealthDocument2 paginiPhrasal Verbs Related To HealthKnuckles El Naco Narco LechugueroÎncă nu există evaluări

- Patel 2013Document116 paginiPatel 2013hnphuocÎncă nu există evaluări

- TheBasicsofBrainWaves - RS PDFDocument4 paginiTheBasicsofBrainWaves - RS PDFOnutu Adriana-LilianaÎncă nu există evaluări

- Test09 Eoc Algebra2 ReducedDocument33 paginiTest09 Eoc Algebra2 ReducedkristymadimikeÎncă nu există evaluări

- Atomic St. Package PDFDocument28 paginiAtomic St. Package PDFSatvik RaoÎncă nu există evaluări

- Colour FastnessDocument37 paginiColour FastnessSivakumar K100% (1)

- Hevi-Bar II and Safe-Lec 2Document68 paginiHevi-Bar II and Safe-Lec 2elkabongscribdÎncă nu există evaluări

- Earth Science Essential Learning Competencies 2020Document5 paginiEarth Science Essential Learning Competencies 2020Charry CervantesÎncă nu există evaluări

- Asaali - Project Estimation - Ce155p-2 - A73Document7 paginiAsaali - Project Estimation - Ce155p-2 - A73Kandhalvi AsaaliÎncă nu există evaluări

- Anderson, Poul - Flandry 02 - A Circus of HellsDocument110 paginiAnderson, Poul - Flandry 02 - A Circus of Hellsgosai83Încă nu există evaluări

- SMC VM Eu PDFDocument66 paginiSMC VM Eu PDFjoguvÎncă nu există evaluări

- Automatic Train OperationDocument6 paginiAutomatic Train OperationAnupam KhandelwalÎncă nu există evaluări

- Clocks (New) PDFDocument5 paginiClocks (New) PDFAbhay DabhadeÎncă nu există evaluări

- Fire on the Horizon: The Untold Story of the Gulf Oil DisasterDe la EverandFire on the Horizon: The Untold Story of the Gulf Oil DisasterÎncă nu există evaluări

- Shorting the Grid: The Hidden Fragility of Our Electric GridDe la EverandShorting the Grid: The Hidden Fragility of Our Electric GridEvaluare: 4.5 din 5 stele4.5/5 (2)

- Introduction to Power System ProtectionDe la EverandIntroduction to Power System ProtectionEvaluare: 5 din 5 stele5/5 (1)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyDe la EverandChip War: The Quest to Dominate the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (227)

- Offshore Wind Energy Generation: Control, Protection, and Integration to Electrical SystemsDe la EverandOffshore Wind Energy Generation: Control, Protection, and Integration to Electrical SystemsÎncă nu există evaluări

- Chip War: The Fight for the World's Most Critical TechnologyDe la EverandChip War: The Fight for the World's Most Critical TechnologyEvaluare: 4.5 din 5 stele4.5/5 (82)

- Power of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesDe la EverandPower of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesEvaluare: 4.5 din 5 stele4.5/5 (21)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)De la EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Evaluare: 5 din 5 stele5/5 (1)

- Practical Reservoir Engineering and CharacterizationDe la EverandPractical Reservoir Engineering and CharacterizationEvaluare: 4.5 din 5 stele4.5/5 (3)

- RV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!De la EverandRV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!Încă nu există evaluări

- iPhone 15 Pro User Guide for Beginners and SeniorsDe la EverandiPhone 15 Pro User Guide for Beginners and SeniorsÎncă nu există evaluări

- Renewable Energy: A Very Short IntroductionDe la EverandRenewable Energy: A Very Short IntroductionEvaluare: 4.5 din 5 stele4.5/5 (12)

- The Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceDe la EverandThe Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceÎncă nu există evaluări

- Nuclear Energy in the 21st Century: World Nuclear University PressDe la EverandNuclear Energy in the 21st Century: World Nuclear University PressEvaluare: 4.5 din 5 stele4.5/5 (3)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsDe la EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsÎncă nu există evaluări

- Solar Power Demystified: The Beginners Guide To Solar Power, Energy Independence And Lower BillsDe la EverandSolar Power Demystified: The Beginners Guide To Solar Power, Energy Independence And Lower BillsEvaluare: 4.5 din 5 stele4.5/5 (2)

- Computer Science: A Concise IntroductionDe la EverandComputer Science: A Concise IntroductionEvaluare: 4.5 din 5 stele4.5/5 (14)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102De la EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Evaluare: 5 din 5 stele5/5 (2)

- Global Landscape of Renewable Energy FinanceDe la EverandGlobal Landscape of Renewable Energy FinanceÎncă nu există evaluări

- A Pathway to Decarbonise the Shipping Sector by 2050De la EverandA Pathway to Decarbonise the Shipping Sector by 2050Încă nu există evaluări

- Heat Transfer Engineering: Fundamentals and TechniquesDe la EverandHeat Transfer Engineering: Fundamentals and TechniquesEvaluare: 4 din 5 stele4/5 (1)

- Formulas and Calculations for Drilling, Production, and Workover: All the Formulas You Need to Solve Drilling and Production ProblemsDe la EverandFormulas and Calculations for Drilling, Production, and Workover: All the Formulas You Need to Solve Drilling and Production ProblemsÎncă nu există evaluări

- Live Off Grid: Escape The City, Learn How To Travel Intelligently Using Solar PowerDe la EverandLive Off Grid: Escape The City, Learn How To Travel Intelligently Using Solar PowerÎncă nu există evaluări

- The New 3D Layout for Oil & Gas Offshore Projects: How to ensure successDe la EverandThe New 3D Layout for Oil & Gas Offshore Projects: How to ensure successEvaluare: 4.5 din 5 stele4.5/5 (3)

- Fundamentals of Hydrogen Production and Utilization in Fuel Cell SystemsDe la EverandFundamentals of Hydrogen Production and Utilization in Fuel Cell SystemsÎncă nu există evaluări