Documente Academic

Documente Profesional

Documente Cultură

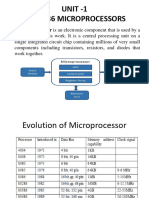

8086 Microprocessor Architecture

Încărcat de

Haribabu VeludandiDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

8086 Microprocessor Architecture

Încărcat de

Haribabu VeludandiDrepturi de autor:

Formate disponibile

8086 microprocessor architecture

Memory Program, data and stack memories occupy the same memory space. The total addressable memory size is 1MB KB. As the most of the processor instructions use 16-bit pointers the processor can effectively address only 64 KB of memory. To access memory outside of 64 KB the CPU uses special segment registers to specify where the code, stack and data 64 KB segments are positioned within 1 MB of memory (see the Registers section below). 16-bit pointers and data are stored as: address: low-order byte address+1: high-order byte 32-bit addresses are stored in segment: offset format as: address: low-order byte of segment address+1: high-order byte of segment address+2: low-order byte of offset address+3: high-order byte of offset Physical memory address pointed by segment: offset pair is calculated as: Address = (<segment> * 16) + <offset> Program memory program can be located anywhere in memory. Jump and call instructions can be used for short jumps within currently selected 64 KB code segment, as well as for far jumps anywhere within 1 MB of memory. All conditional jump instructions can be used to jump within approximately +127 -127 bytes from current instruction. Data memory the processor can access data in any one out of 4 available segments, which limits the size of accessible memory to 256 KB (if all four segments point to different 64 KB blocks). Accessing data from the Data, Code, Stack or Extra segments can be usually done by prefixing instructions with the DS:, CS:, SS: or ES: (some registers and instructions by default may use the ES or SS segments instead of DS segment). Word data can be located at odd or even byte boundaries. The processor uses two memory accesses to read 16-bit word located at odd byte boundaries. Reading word data from even byte boundaries requires only one memory access. Stack memory can be placed anywhere in memory. The stack can be located at odd memory addresses, but it is not recommended for performance reasons (see Data Memory above). Reserved locations: 0000h 03FFh are reserved for interrupt vectors. Each interrupt vector is a 32-bit pointer in format segment: offset. FFFF0h FFFFFh after RESET the processor always starts program execution at the FFFF0h address. Interrupts The processor has the following interrupts: INTR is a maskable hardware interrupt. The interrupt can be enabled/disabled using STI/CLI instructions or using more complicated method of updating the FLAGS register with the help

of the POPF instruction. When an interrupt occurs, the processor stores FLAGS register into stack, disables further interrupts, fetches from the bus one byte representing interrupt type, and jumps to interrupt processing routine address of which is stored in location 4 * <interrupt type>. Interrupt processing routine should return with the IRET instruction. NMI is a non-maskable interrupt. Interrupt is processed in the same way as the INTR interrupt. Interrupt type of the NMI is 2, i.e. the address of the NMI processing routine is stored in location 0008h. This interrupt has higher priority then the maskable interrupt. Software interrupts can be caused by: INT instruction breakpoint interrupt. This is a type 3 interrupt. INT <interrupt number> instruction any one interrupt from available 256 interrupts. INTO instruction interrupt on overflow Single-step interrupt generated if the TF flag is set. This is a type 1 interrupt. When the CPU processes this interrupt it clears TF flag before calling the interrupt processing routine. Processor exceptions: divide error (type 0), unused opcode (type 6) and escape opcode (type 7). Software interrupt processing is the same as for the hardware interrupts. I/O ports 65536 8-bit I/O ports: These ports can be also addressed as 32768 16-bit I/O ports. Registers Most of the registers contain data/instruction offsets within 64 KB memory segment. There are four different 64 KB segments for instructions, stack, data and extra data. To specify where in 1 MB of processor memory these 4 segments are located the processor uses four segment registers: Code segment (CS) is a 16-bit register containing address of 64 KB segment with processor instructions. The processor uses CS segment for all accesses to instructions referenced by instruction pointer (IP) register. CS register cannot be changed directly. The CS register is automatically updated during far jump, far call and far return instructions. Stack segment (SS) is a 16-bit register containing address of 64KB segment with program stack. By default, the processor assumes that all data referenced by the stack pointer (SP) and base pointer (BP) registers is located in the stack segment. SS register can be changed directly using POP instruction. Data segment (DS) is a 16-bit register containing address of 64KB segment with program data. By default, the processor assumes that all data referenced by general registers (AX, BX, CX, DX) and index register (SI, DI) is located in the data segment. DS register can be changed directly using POP and LDS instructions. Extra segment (ES) is a 16-bit register containing address of 64KB segment, usually with program data. By default, the processor assumes that the DI register references the ES segment in string manipulation instructions. ES register can be changed directly using POP and LES instructions. It is possible to change default segments used by general and index registers by prefixing instructions with a CS, SS, DS or ES prefix.

All general registers of the 8086 microprocessor can be used for arithmetic and logic operations. The general registers are: Accumulator register consists of 2 8-bit registers AL and AH, which can be combined together and used as a 16-bit register AX. AL in this case contains the low-order byte of the word, and AH contains the high-order byte. Accumulator can be used for I/O operations and string manipulation. Base register consists of 2 8-bit registers BL and BH, which can be combined together and used as a 16-bit register BX. BL in this case contains the low-order byte of the word, and BH contains the high-order byte. BX register usually contains a data pointer used for based, based indexed or register indirect addressing. Count register consists of 2 8-bit registers CL and CH, which can be combined together and used as a 16-bit register CX. When combined, CL register contains the low-order byte of the word, and CH contains the high-order byte. Count register can be used as a counter in string manipulation and shift/rotate instructions. Data register consists of 2 8-bit registers DL and DH, which can be combined together and used as a 16-bit register DX. When combined, DL register contains the low-order byte of the word, and DH contains the high-order byte. Data register can be used as a port number in I/O operations. In integer 32-bit multiply and divide instruction the DX register contains highorder word of the initial or resulting number. The following registers are both general and index registers: Stack Pointer (SP) is a 16-bit register pointing to program stack. Base Pointer (BP) is a 16-bit register pointing to data in stack segment. BP register is usually used for based, based indexed or register indirect addressing. Source Index (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data address in string manipulation instructions. Destination Index (DI) is a 16-bit register. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data address in string manipulation instructions. Other registers: Instruction Pointer (IP) is a 16-bit register. A flag is a 16-bit register containing 9 1-bit flags: Overflow Flag (OF) set if the result is too large positive number, or is too small negative number to fit into destination operand. Direction Flag (DF) if set then string manipulation instructions will auto-decrement index registers. If cleared then the index registers will be auto-incremented. Interrupt-enable Flag (IF) setting this bit enables maskable interrupts. Single-step Flag (TF) if set then single-step interrupt will occur after the next instruction. Sign Flag (SF) set if the most significant bit of the result is set. Zero Flag (ZF) set if the result is zero. Auxiliary carry Flag (AF) set if there was a carry from or borrow to bits 0-3 in the AL register. Parity Flag (PF) set if parity (the number of 1 bits) in the low-order byte of the result is even.

Carry Flag (CF) set if there was a carry from or borrow to the most significant bit during last result calculation. Instruction Set 8086 instruction set consists of the following instructions: Data moving instructions. Arithmetic add, subtract, increment, decrement, convert byte/word and compare. Logic AND, OR, exclusive OR, shift/rotate and test. String manipulation load, store, move, compare and scan for byte/word. Control transfer conditional, unconditional, call subroutine and return from subroutine. Input/Output instructions. Other setting/clearing flag bits, stack operations, software interrupts, etc. Addressing modes Implied the data value/data address is implicitly associated with the instruction. Register references the data in a register or in a register pair. Immediate the data is provided in the instruction. Direct the instruction operand specifies the memory address where data is located. Register indirect instruction specifies a register containing an address, where data is located. This addressing mode works with SI, DI, BX and BP registers. Based 8-bit or 16-bit instruction operand is added to the contents of a base register (BX or BP), the resulting value is a pointer to location where data resides. Indexed 8-bit or 16-bit instruction operand is added to the contents of an index register (SI or DI), the resulting value is a pointer to location where data resides. Based Indexed the contents of a base register (BX or BP) is added to the contents of an index register (SI or DI), the resulting value is a pointer to location where data resides. Based Indexed with displacement 8-bit or 16-bit instruction operand is added to the contents of a base register (BX or BP) and index register (SI or DI), the resulting value is a pointer to location where data resides.

Read more: http://www.indianshout.com/ap-transco-material-8086-microprocessorarchitecture/1394#ixzz1kcy7a300

ELECTRIC CIRCUITS/NETWORK ANALYSIS-STUDY MATERIAL & MODEL QUESTIONS

Q.1 To calculate Thevenins equivalent value in a circuit (A) all independent voltage sources are opened and all independent current sources are short circuited. (B) both voltage and current sources are open circuited (C) all voltage and current sources are shorted. (D) all voltage sources are shorted while current sources are opened.

Ans: D To calculate Thevenins equivalent impedance value in a circuit, all independent voltage sources are shorted while all independent current sources are opened. Q.2 A 26 dBm output in watts equals to (A) 2.4W. (B) 0.26W. (C) 0.156W. (D) 0.4W. Ans: A A 26dBm output in watts equals to 0.4 W because 10*log10(400MW/1MW) = 26DB Q.3 The Characteristic Impedance of a low pass filter in attenuation Band is (A) Purely imaginary. (B) Zero. (C) Complex quantity. (D) Real value. Ans: A The characteristic impedance of a low pass filter in attenuation band is purely imaginary. Q.4 The real part of the propagation constant shows: (A) Variation of voltage and current on basic unit. (B) Variation of phase shift/position of voltage. (C) Reduction in voltage, current values of signal amplitude. (D) Reduction of only voltage amplitude. Ans: C The real part of the propagation constant shows reduction in voltage, current values of signal amplitude. Q.5 The purpose of an Attenuator is to: (A) increase signal strength. (B) provide impedance matching. (C) decrease reflections. (D) decrease value of signal strength. Ans: D The purpose of an Attenuator is to decrease value of signal strength.

Q.7 In a transmission line terminated by characteristic impedance, ZO (A) There is no reflection of the incident wave. (B) The reflection is maximum due to termination. (C) There are a large number of maximum and minimum on the line. (D) The incident current is zero for any applied signal. Ans: A In a transmission line terminated by characteristic impedance, Zo there is no reflection of the incident wave. Q.8 For a coil with inductance L and resistance R in series with a capacitor C has (A) Resonance impedance as zero.

(B) Resonance impedance R. (C) Resonance impedance L/CR. (D) Resonance impedance as infinity. Ans: B For a coil with inductance L and resistance R in series with a capacitor C has a resonance impedance R. Q.9 Laplace transform of a unit Impulse function is (A)s. (B) 0. (C) e-S (D) 1. Ans: D Laplace transform of a unit Impulse function is 1 Q.10 Millmans theorem is applicable during determination of (A) Load current in a network of generators and impedances with two output terminals. (B) Load conditions for maximum power transfer. (C) Dual of a network. (D) Load current in a network with more than one voltage source. Ans: D Millmans theorem is applicable during determination of Load current in a network with more than one voltage source.

Q.12 An attenuator is a (A) Rs network. (B) RL network. (C) RC network. Ans: A An attenuator is a Rs network.

(D) LC network.

Q.13 A pure resistance, RL when connected at the load end of a loss-less 100 line produces a VSWR of 2. Then R is (A) 50 only. (B) 200 only. (C) 50 or 200 . (D) 400 . Ans: C A pure resistance, RL when connected at the load end of a loss-less 100 line produces a VSWR of 2. Then RL is 50 or 200 , as follows: Q.14 All pass filter (A) passes whole of the audio band. (B) passes whole of the radio band. (C) passes all frequencies with very low attenuation. (D) passes all frequencies without attenuation but phase is changed. Ans: D All pass filters, passes all frequencies without attenuation but phase change. Q.16 A series resonant circuit is inductive at f = 1000 Hz. The circuit will be capacitive some where at

(A) f > 1000 Hz. (B) f < 1000 Hz. (C) f equal to 1000 Hz and by adding a resistance in series. (D) f = 1000+ fO ( resonance frequency) Ans: B A series resonant circuit is inductive at f = 1000 Hz. The circuit will be capacitive some where at f < 1000 Hz. Q.17 Compensation theorem is applicable to (A) non-linear networks. (B) linear networks. (C) linear and non-linear networks. (D) None of the above. Ans: C Compensation theorem is applicable to linear and non-linear networks.

Q.19 A network function is said to have simple pole or simple zero if (A) the poles and zeroes are on the real axis. (B) the poles and zeroes are repetitive. (C) the poles and zeroes are complex conjugate to each other. (D) the poles and zeroes are not repeated. Ans: D A network function is said to have simple pole or simple zero if the poles and zeroes are not repeated. Q.20 A delta connection contains three impedances of 60 each. The impedances of equivalent star connection will be (A) 15 each. (B) 20 each. (C) 30 each. (D) 40 each. Ans: B A delta connection contains three impedances of 60 each. The impedances of equivalent star connection will be 20 each. Q.21 Millman theorem yields (A) equivalent resistance of the circuit. (B) equivalent voltage source. (C) equivalent voltage OR current source. (D value of current in milli amperes input to a circuit from a voltage source. Ans: C Millmans theorem yields equivalent voltage or current source. Q.22 The z-parameters of the shown T-network at Fig.1 are given by (A) 5, 8, 12, 0 (B) 13, 8, 8, 20 (C) 8, 20, 13, 12 (D) 5, 8, 8, 12

Q.23 The Superposition theorem is essentially based on the concept of (A) duality. (B) linearity. (C) reciprocity. (D) non-linearity. Ans: B Q.24 The power factor of a purely resistive circuit is (A) zero. (B) unity. (C) lagging. (D) leading. Ans: B Q.25

Read more: http://www.indianshout.com/aptransco-ae-electrical-telecom-studymaterialmodel-questions/8142#ixzz1kczEYzjj

S-ar putea să vă placă și

- 6th Central Pay Commission Salary CalculatorDocument15 pagini6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Employee Confidentiality and Non-Disclosure AgreementDocument5 paginiEmployee Confidentiality and Non-Disclosure AgreementshamoojeeÎncă nu există evaluări

- U2 All That You Can't Leave BehindDocument82 paginiU2 All That You Can't Leave BehindFranck UrsiniÎncă nu există evaluări

- Navistar O & M ManualDocument56 paginiNavistar O & M ManualMushtaq Hasan95% (20)

- HVAC Master Validation PlanDocument51 paginiHVAC Master Validation Plannavas197293% (30)

- 8086 Microprocessor: Ram Murat SinghDocument27 pagini8086 Microprocessor: Ram Murat SinghAnik100% (1)

- NABARD road inspection report formatDocument24 paginiNABARD road inspection report formatSrinivas PÎncă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960De la EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Încă nu există evaluări

- AA ActivitiesDocument4 paginiAA ActivitiesSalim Amazir100% (1)

- Template WFP-Expenditure Form 2024Document22 paginiTemplate WFP-Expenditure Form 2024Joey Simba Jr.Încă nu există evaluări

- Cot 2Document3 paginiCot 2Kathjoy ParochaÎncă nu există evaluări

- 8086 MicroprocessorDocument7 pagini8086 MicroprocessorVikram ChauhanÎncă nu există evaluări

- Intel 8086 Microprocessor ArchitectureDocument15 paginiIntel 8086 Microprocessor ArchitectureShashank SoodÎncă nu există evaluări

- Intel 8086 Microprocessor ArchitectureDocument16 paginiIntel 8086 Microprocessor Architecturelu4rohitÎncă nu există evaluări

- SegmentationDocument6 paginiSegmentationRavi Kiran BÎncă nu există evaluări

- MTE-605 Assingment2 ProcessorDocument6 paginiMTE-605 Assingment2 ProcessorAeronautical EngineerÎncă nu există evaluări

- Archi 8086Document3 paginiArchi 8086Shashin KaswateÎncă nu există evaluări

- MP Sec.B.1Document33 paginiMP Sec.B.1Girish AroraÎncă nu există evaluări

- Architecture of 8086Document4 paginiArchitecture of 8086sree ramyaÎncă nu există evaluări

- MPMC - Notes T ApparaoDocument105 paginiMPMC - Notes T ApparaoMurthyÎncă nu există evaluări

- Significance of QueueDocument6 paginiSignificance of QueueJun Alfred Alba100% (1)

- 8086 Architecture:: 8. Single Bit Serial I/O PortsDocument67 pagini8086 Architecture:: 8. Single Bit Serial I/O PortsSri ShandilyaÎncă nu există evaluări

- 8086 Microprocessor ArchitectureDocument60 pagini8086 Microprocessor ArchitectureManikandanÎncă nu există evaluări

- Unit-Vi Lecture Notes: - 8086 MICROPROCESSOR: 8086 ArchitectureDocument29 paginiUnit-Vi Lecture Notes: - 8086 MICROPROCESSOR: 8086 Architectureramarao pagadalaÎncă nu există evaluări

- 8086 Register Organization (IMPDocument6 pagini8086 Register Organization (IMPSukanti PalÎncă nu există evaluări

- Unit - Ii: Programmers Model For Intel 8086Document51 paginiUnit - Ii: Programmers Model For Intel 8086franklin4uÎncă nu există evaluări

- Ec8691 Microprocessors and Microcontroller 366672282 MPMC 5unitDocument229 paginiEc8691 Microprocessors and Microcontroller 366672282 MPMC 5unitjeniferÎncă nu există evaluări

- Inside the 8086 CPU: General Purpose and Special RegistersDocument11 paginiInside the 8086 CPU: General Purpose and Special RegistersHashimIdreesÎncă nu există evaluări

- Mpmc All PptDocument479 paginiMpmc All Pptbalakasriram123Încă nu există evaluări

- Micro 8086Document119 paginiMicro 8086Md Fairuz SiddiqueeÎncă nu există evaluări

- CS602 Microprocessor and Microcontroller - 8086Document20 paginiCS602 Microprocessor and Microcontroller - 8086Rehan NightÎncă nu există evaluări

- 01 Introduction To The Microprocessor and Computer The Microprocessor and Its ArchitectureDocument15 pagini01 Introduction To The Microprocessor and Computer The Microprocessor and Its ArchitectureRam AnandÎncă nu există evaluări

- 16-bit Microprocessors TransitionDocument145 pagini16-bit Microprocessors TransitionAASTHA KIETÎncă nu există evaluări

- Ec8691 MPMCDocument480 paginiEc8691 MPMCwww.r2dk2Încă nu există evaluări

- Ec8691 MPMCDocument480 paginiEc8691 MPMCsatishcoimbato12Încă nu există evaluări

- Chapter 2Document25 paginiChapter 2tariku fkaduÎncă nu există evaluări

- Intel 8086 Microprocessor Architecture GuideDocument9 paginiIntel 8086 Microprocessor Architecture Guidedz15dzÎncă nu există evaluări

- Chapter 3 Programming With 8086 Microprocessor PDFDocument34 paginiChapter 3 Programming With 8086 Microprocessor PDFLalit ChaudharyÎncă nu există evaluări

- Unit 1&3Document18 paginiUnit 1&3Sreekanth PagadapalliÎncă nu există evaluări

- Serial CommunicationDocument28 paginiSerial CommunicationSanduni100% (1)

- Execution Unit and BIUDocument29 paginiExecution Unit and BIUMohammad ZakirÎncă nu există evaluări

- 8086 Microprocessor: Lec. 3: 8086 Intel Microprocessor Omar ZyadDocument21 pagini8086 Microprocessor: Lec. 3: 8086 Intel Microprocessor Omar Zyadالزهور لخدمات الانترنيتÎncă nu există evaluări

- Introduction To 8086 MicroprocessorDocument7 paginiIntroduction To 8086 MicroprocessorRameen ChÎncă nu există evaluări

- Lecture 3 Register OrganizationDocument5 paginiLecture 3 Register OrganizationMuhammad ShehrzadÎncă nu există evaluări

- Assignment-1: Software TechnologyDocument4 paginiAssignment-1: Software TechnologySwarnim ShuklaÎncă nu există evaluări

- Microprocesser AssignmentDocument15 paginiMicroprocesser AssignmentMukul RanaÎncă nu există evaluări

- MP&MC 1 ST ChapterDocument29 paginiMP&MC 1 ST Chapteretikelavaishnavi09Încă nu există evaluări

- 8086 Bus Interface Unit and Execution Unit ElementsDocument5 pagini8086 Bus Interface Unit and Execution Unit ElementsAndreas Pitziolis100% (1)

- 8086 Microprocessor IntroductionDocument31 pagini8086 Microprocessor IntroductionVELU KÎncă nu există evaluări

- Chapter 03 8086Document70 paginiChapter 03 8086hari kcÎncă nu există evaluări

- Introduction to 8086 Microprocessor ArchitectureDocument49 paginiIntroduction to 8086 Microprocessor ArchitectureSai Sreenath100% (1)

- Intel 8086 ArchitectureDocument29 paginiIntel 8086 ArchitectureJKÎncă nu există evaluări

- Intel 8086 Microprocessor: Architecture, Registers & Pin DetailsDocument235 paginiIntel 8086 Microprocessor: Architecture, Registers & Pin DetailsPraveen YadavÎncă nu există evaluări

- 8086 Microprocessor Architecture 2Document30 pagini8086 Microprocessor Architecture 2Rajkumar ArumairajÎncă nu există evaluări

- 8086 Notes NITW2020Document76 pagini8086 Notes NITW2020ka21ecb0f27Încă nu există evaluări

- Organization of Intel 8086Document10 paginiOrganization of Intel 8086Ashok ChakriÎncă nu există evaluări

- Internal Block Diagram of 8086Document33 paginiInternal Block Diagram of 8086Salitha100% (1)

- Registri TriDocument4 paginiRegistri TriNenad FemicÎncă nu există evaluări

- 8086 Microprocessor ArchitectureDocument31 pagini8086 Microprocessor ArchitectureLeeza AnandÎncă nu există evaluări

- Microprocessors 8086 (Notes)Document29 paginiMicroprocessors 8086 (Notes)Aravindha BhatÎncă nu există evaluări

- EC 8691-MICROPROCESSORS AND MICROCONTROLLERSDocument39 paginiEC 8691-MICROPROCESSORS AND MICROCONTROLLERSbeaulajenishÎncă nu există evaluări

- Mic ProjectDocument15 paginiMic Projectsudarshan sonawaneÎncă nu există evaluări

- 8086 MicroprocessorDocument32 pagini8086 MicroprocessorMohamedÎncă nu există evaluări

- Introduction To 8086 Microprocessor: Prof. Niraj Kumar, Assistant Professor, Vellore Institute of Technology, ChennaiDocument50 paginiIntroduction To 8086 Microprocessor: Prof. Niraj Kumar, Assistant Professor, Vellore Institute of Technology, ChennaiAyyeeeeÎncă nu există evaluări

- MP Viva Questions With AnswersDocument13 paginiMP Viva Questions With AnswersDeepti ChandrasekharanÎncă nu există evaluări

- Unit 6 Introduction of Advanced MicrtoprocessorDocument9 paginiUnit 6 Introduction of Advanced MicrtoprocessorMann MehtaÎncă nu există evaluări

- Intel Microprocessor: Srinivas - PeralaDocument31 paginiIntel Microprocessor: Srinivas - PeralaJamie SchultzÎncă nu există evaluări

- Lec 2 - Org of MicroprocessorsDocument31 paginiLec 2 - Org of Microprocessorsapi-237335979Încă nu există evaluări

- EM Mod 3 PDFDocument34 paginiEM Mod 3 PDFHaribabu VeludandiÎncă nu există evaluări

- EM Mod 2 PDFDocument37 paginiEM Mod 2 PDFHaribabu VeludandiÎncă nu există evaluări

- Double Edge Latch PDFDocument6 paginiDouble Edge Latch PDFHaribabu VeludandiÎncă nu există evaluări

- Computer NetworksDocument6 paginiComputer NetworksHaribabu VeludandiÎncă nu există evaluări

- EM Mod 1 PDFDocument26 paginiEM Mod 1 PDFHaribabu VeludandiÎncă nu există evaluări

- PDFDocument10 paginiPDFHaribabu VeludandiÎncă nu există evaluări

- EM Mod 5 PDFDocument14 paginiEM Mod 5 PDFHaribabu VeludandiÎncă nu există evaluări

- Emtl by Bakshi PDFDocument156 paginiEmtl by Bakshi PDFHaribabu Veludandi0% (1)

- Assignment 2Document5 paginiAssignment 2Haribabu VeludandiÎncă nu există evaluări

- PDFDocument6 paginiPDFHaribabu VeludandiÎncă nu există evaluări

- Ijsetr389 07Document4 paginiIjsetr389 07Haribabu VeludandiÎncă nu există evaluări

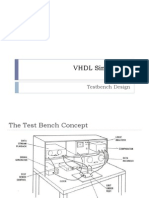

- VHDL 6 TestbenchDocument19 paginiVHDL 6 TestbenchHaribabu VeludandiÎncă nu există evaluări

- IeeeDocument5 paginiIeeeHaribabu VeludandiÎncă nu există evaluări

- An Analysis of Full Adder Cells For Low-Power Data Oriented Adders DesignDocument6 paginiAn Analysis of Full Adder Cells For Low-Power Data Oriented Adders DesignHaribabu VeludandiÎncă nu există evaluări

- Lect 13Document38 paginiLect 13Pham VietÎncă nu există evaluări

- VHDL Lab ManualDocument52 paginiVHDL Lab ManualParag Parandkar100% (1)

- Intelligence Bureau Previous Question PapersDocument23 paginiIntelligence Bureau Previous Question PapersKottinti Karthik100% (1)

- ComparisonDocument6 paginiComparisonHaribabu VeludandiÎncă nu există evaluări

- France Winckler Final Rev 1Document14 paginiFrance Winckler Final Rev 1Luciano Junior100% (1)

- Paper 4 (A) (I) IGCSE Biology (Time - 30 Mins)Document12 paginiPaper 4 (A) (I) IGCSE Biology (Time - 30 Mins)Hisham AlEnaiziÎncă nu există evaluări

- Oxygen Cost and Energy Expenditure of RunningDocument7 paginiOxygen Cost and Energy Expenditure of Runningnb22714Încă nu există evaluări

- Unit 14 Ergonomics Design: AND ProductDocument24 paginiUnit 14 Ergonomics Design: AND ProductRämêşh KątúřiÎncă nu există evaluări

- 7 Aleksandar VladimirovDocument6 pagini7 Aleksandar VladimirovDante FilhoÎncă nu există evaluări

- Crystallizers: Chapter 16 Cost Accounting and Capital Cost EstimationDocument1 paginăCrystallizers: Chapter 16 Cost Accounting and Capital Cost EstimationDeiver Enrique SampayoÎncă nu există evaluări

- Damcos Mas2600 Installation UsermanualDocument26 paginiDamcos Mas2600 Installation Usermanualair1111Încă nu există evaluări

- Key Fact Sheet (HBL FreedomAccount) - July 2019 PDFDocument1 paginăKey Fact Sheet (HBL FreedomAccount) - July 2019 PDFBaD cHaUhDrYÎncă nu există evaluări

- N4 Electrotechnics August 2021 MemorandumDocument8 paginiN4 Electrotechnics August 2021 MemorandumPetro Susan BarnardÎncă nu există evaluări

- Maharashtra Auto Permit Winner ListDocument148 paginiMaharashtra Auto Permit Winner ListSadik Shaikh50% (2)

- Guia de Usuario GPS Spectra SP80 PDFDocument118 paginiGuia de Usuario GPS Spectra SP80 PDFAlbrichs BennettÎncă nu există evaluări

- JM Guide To ATE Flier (c2020)Document2 paginiJM Guide To ATE Flier (c2020)Maged HegabÎncă nu există evaluări

- (123doc) - Chapter-24Document6 pagini(123doc) - Chapter-24Pháp NguyễnÎncă nu există evaluări

- STS Prelim ExamDocument2 paginiSTS Prelim ExamMychie Lynne MayugaÎncă nu există evaluări

- Final Year Project (Product Recommendation)Document33 paginiFinal Year Project (Product Recommendation)Anurag ChakrabortyÎncă nu există evaluări

- eHMI tool download and install guideDocument19 paginieHMI tool download and install guideNam Vũ0% (1)

- Propoxur PMRADocument2 paginiPropoxur PMRAuncleadolphÎncă nu există evaluări

- SiloDocument7 paginiSiloMayr - GeroldingerÎncă nu există evaluări

- GS16 Gas Valve: With On-Board DriverDocument4 paginiGS16 Gas Valve: With On-Board DriverProcurement PardisanÎncă nu există evaluări

- Galaxy Owners Manual Dx98vhpDocument10 paginiGalaxy Owners Manual Dx98vhpbellscbÎncă nu există evaluări

- What's Wrong With American Taiwan Policy: Andrew J. NathanDocument14 paginiWhat's Wrong With American Taiwan Policy: Andrew J. NathanWu GuifengÎncă nu există evaluări

- Inborn Errors of Metabolism in Infancy: A Guide To DiagnosisDocument11 paginiInborn Errors of Metabolism in Infancy: A Guide To DiagnosisEdu Diaperlover São PauloÎncă nu există evaluări