Documente Academic

Documente Profesional

Documente Cultură

74HC112 (Flip Flop J-K)

Încărcat de

Oscar Zabaleta LaverdeDescriere originală:

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

74HC112 (Flip Flop J-K)

Încărcat de

Oscar Zabaleta LaverdeDrepturi de autor:

Formate disponibile

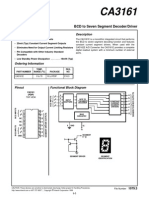

74VHC112 Dual J-K Flip-Flops with Preset and Clear

May 2007

74VHC112 tm

Dual J-K Flip-Flops with Preset and Clear

Features General Description

■ High speed: fMAX = 200MHz (Typ.) at VCC = 5.0V The VHC112 is an advanced high speed CMOS device

■ Low power dissipation: ICC = 2µA (Max.) at TA = 25°C fabricated with silicon gate CMOS technology. It

■ High noise immunity: VNIH = VNIL = 28% VCC (Min.)

achieves the high-speed operation similar to equivalent

Bipolar Schottky TTL while maintaining the CMOS low

■ Power down protection is provided on all inputs

power dissipation.

■ Pin and function compatible with 74HC112

The VHC112 contains two independent, high-speed JK

flip-flops with Direct Set and Clear inputs. Synchronous

state changes are initiated by the falling edge of the

clock. Triggering occurs at a voltage level of the clock

and is not directly related to transition time. The J and K

inputs can change when the clock is in either state with-

out affecting the flip-flop, provided that they are in the

desired state during the recommended setup and hold

times relative to the falling edge of the clock. The LOW

signal on PR or CLR prevents clocking and forces Q and

Q HIGH, respectively. Simultaneous LOW signals on PR

and CLR force both Q and Q HIGH.

An input protection circuit ensures that 0V to 7V can be

applied to the input pins without regard to the supply

voltage. This device can be used to interface 5V to 3V

systems and two supply systems such as battery

backup. This circuit prevents device destruction due to

mismatched supply and input voltages.

Ordering Information

Package

Order Number Number Package Description

74VHC112M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

74VHC112SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74VHC112MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm

Wide

Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the

ordering number.

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2

74VHC112 Dual J-K Flip-Flops with Preset and Clear

Connection Diagram Truth Table

Inputs Outputs

PR CLR CP J K Q Q

L H X X X H L

H L X X X L H

L L X X X H H

H H h h Q0 Q0

H H l h L H

H H h l H L

H H l l Q0 Q0

H (h) = HIGH Voltage Level

L (l) = LOW Voltage Level

X = Immaterial

= HIGH-to-LOW Clock Transition

Q0 (Q0) = Before HIGH-to-LOW Transition of Clock

Lower case letters indicate the state of the referenced

Pin Description input or output one setup time prior to the HIGH-to-LOW

clock transition.

Pin Names Description

J1, J2, K1, K2 Data Inputs

CLK1, CLK2 Clock Pulse Inputs (Active Falling

Edge)

CLR1, CLR2 Direct Clear Inputs (Active LOW)

PR1, PR2 Direct Preset Inputs (Active LOW)

Q1, Q2, Q1, Q2 Outputs

Logic Diagram

(One Half Shown)

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 2

74VHC112 Dual J-K Flip-Flops with Preset and Clear

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability.

The absolute maximum ratings are stress ratings only.

Symbol Parameter Rating

VCC Supply Voltage –0.5V to +7.0V

VIN DC Input Voltage –0.5V to +7.0V

VOUT DC Output Voltage –0.5V to VCC + 0.5V

IIK Input Diode Current –20mA

IOK Output Diode Current ±20mA

IOUT DC Output Current ±25mA

ICC DC VCC / GND Current ±50mA

TSTG Storage Temperature –65°C to +150°C

TL Lead Temperature (Soldering, 10 seconds) 260°C

Recommended Operating Conditions(1)

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to absolute maximum ratings.

Symbol Parameter Rating

VCC Supply Voltage 2.0V to +5.5V

VIN Input Voltage 0V to +5.5V

VOUT Output Voltage 0V to VCC

TOPR Operating Temperature –40°C to +85°C

tr , tf Input Rise and Fall Time,

VCC = 3.3V ± 0.3V 0ns/V ∼ 100ns/V

VCC = 5.0V ± 0.5V 0ns/V ∼ 20ns/V

Note:

1. Unused inputs must be held HIGH or LOW. They may not float.

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 3

74VHC112 Dual J-K Flip-Flops with Preset and Clear

DC Electrical Characteristics

TA = –40°C to

TA = 25°C +85°C

Symbol Parameter VCC (V) Conditions Min. Typ. Max. Min. Max. Units

VIH HIGH Level Input 2.0 1.50 1.50 V

Voltage 3.0–5.5 0.7 x VCC 0.7 x VCC

VIL LOW Level Input 2.0 0.50 0.50 V

Voltage 3.0–5.5 0.3 x VCC 0.3 x VCC

VOH HIGH Level 2.0 VIN = VIH IOH = –50µA 1.9 2.0 1.9 V

Output Voltage or VIL

3.0 2.9 3.0 2.9

4.5 4.4 4.5 4.4

3.0 IOH = –4mA 2.58 2.48

4.5 IOH = –8mA 3.94 3.80

VOL LOW Level 2.0 VIN = VIH IOL = 50µA 0.0 0.1 0.1 V

Output Voltage or VIL

3.0 0.0 0.1 0.1

4.5 0.0 0.1 0.1

3.0 IOL = 4mA 0.36 0.44

4.5 IOL = 8mA 0.36 0.44

IIN Input Leakage 0–5.5 VIN = 5.5V or GND ±0.1 ±1.0 µA

Current

ICC Quiescent 5.5 VIN = VCC or GND 2.0 20.0 µA

Supply Current

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 4

74VHC112 Dual J-K Flip-Flops with Preset and Clear

AC Electrical Characteristics

TA = –40°C

TA = 25°C to +85°C

Symbol Parameter VCC (V) Conditions Min. Typ. Max. Min. Max. Units

fMAX Maximum Clock 3.3 ± 0.3 CL = 15pF 110 150 100 MHz

Frequency CL = 50pF 90 120 80

5.0 ± 0.5 CL = 15pF 150 200 135 MHz

CL = 50pF 120 185 110

tPLH, tPHL Propagation Delay Time 3.3 ± 0.3 CL = 15pF 8.5 11.0 1.0 13.4 ns

(CP to Qn or Qn) CL = 50pF 10.0 15.0 1.0 16.5

5.0 ± 0.5 CL = 15pF 5.1 7.3 1.0 8.8 ns

CL = 50pF 6.3 10.5 1.0 12.0

tPLH, tPHL Propagation Delay Time 3.3 ± 0.3 CL = 15pF 6.7 10.2 1.0 11.7 ns

(PR or CLR to Qn or Qn) CL = 50pF 9.7 13.5 1.0 15.0

5.0 ± 0.5 CL = 15pF 4.6 6.7 1.0 8.0 ns

CL = 50pF 6.4 9.5 1.0 11.0

CIN Input Capacitance VCC = Open 4 10 10 pF

CPD Power Dissipation (2) 18 pF

Capacitance

Note:

2. CPD is defined as the value of the internal equivalent capacitance which is calculated from the operating

current consumption without load. Average operating current can be obtained from the equation:

ICC (opr.) = CPD • VCC • fIN + ICC / 4 (per F/F), and the total CPD when n pcs of the Flip-Flop operate can be calculated

by the following equation: CPD (total) = 30 + 14 • n

AC Operating Requirements

TA = 25°C TA = –40°C to +85°C

Symbol Parameter VCC (V)(3) Typ. Guaranteed Minimum Units

tW Minimum Pulse Width 3.3 5.0 5.0 ns

(CP or CLR or PR) 5.0 5.0 5.0

tS Minimum Setup Time 3.3 5.0 5.0 ns

(Jn or Kn to CPn) 5.0 4.0 4.0

tH Minimum Hold Time 3.3 1.0 1.0 ns

(Jn or Kn to CPn) 5.0 1.0 1.0

tREC Minimum Recovery Time 3.3 6.0 6.0 ns

(CLR or PR to CP) 5.0 5.0 5.0

Note:

3. VCC is 3.3 ± 0.3V or 5.0 ± 0.5V.

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 5

74VHC112 Dual J-K Flip-Flops with Preset and Clear

Physical Dimensions

Dimensions are in millimeters unless otherwise noted.

Figure 1. 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

Package Number M16A

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 6

74VHC112 Dual J-K Flip-Flops with Preset and Clear

Physical Dimensions (Continued)

Dimensions are in millimeters unless otherwise noted.

Figure 2. 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package Number M16D

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 7

74VHC112 Dual J-K Flip-Flops with Preset and Clear

Physical Dimensions (Continued)

Dimensions are in millimeters unless otherwise noted.

5.00±0.10

4.55

5.90

4.45 7.35

0.65

4.4±0.1

1.45

5.00

0.11

12°

MTC16rev4

Figure 3. 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package Number MTC16

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 8

74VHC112 Dual J-K Flip-Flops with Preset and Clear

TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an

exhaustive list of all such trademarks.

®

ACEx i-Lo™ Power-SPM™ TinyBoost™

®

Across the board. Around the world.™ ImpliedDisconnect™ PowerTrench TinyBuck™

®

ActiveArray™ IntelliMAX™ Programmable Active Droop™ TinyLogic

®

Bottomless™ ISOPLANAR™ QFET TINYOPTO™

Build it Now™ MICROCOUPLER™ QS™ TinyPower™

CoolFET™ MicroPak™ QT Optoelectronics™ TinyWire™

CROSSVOLT™ MICROWIRE™ Quiet Series™ TruTranslation™

CTL™ Motion-SPM™ RapidConfigure™ µSerDes™

®

Current Transfer Logic™ MSX™ RapidConnect™ UHC

DOME™ MSXPro™ ScalarPump™ UniFET™

2

E CMOS™ OCX™ SMART START™ VCX™

® ®

EcoSPARK OCXPro™ SPM Wire™

®

EnSigna™ OPTOLOGIC STEALTH™

®

FACT Quiet Series™ OPTOPLANAR SuperFET™

®

FACT PACMAN™ SuperSOT™-3

®

FAST PDP-SPM™ SuperSOT™-6

FASTr™ POP™ SuperSOT™-8

®

FPS™ Power220 SyncFET™

® ®

FRFET Power247 TCM™

®

GlobalOptoisolator™ PowerEdge™ The Power Franchise

GTO™ PowerSaver™ ™

HiSeC™

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER

ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support,

which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be

(b) support or sustain life, and (c) whose failure to perform reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In Design This datasheet contains the design specifications for product

development. Specifications may change in any manner without notice.

Preliminary First Production This datasheet contains preliminary data; supplementary data will be

published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild Semiconductor

reserves the right to make changes at any time without notice to improve

design.

Obsolete Not In Production This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I26

©1995 Fairchild Semiconductor Corporation www.fairchildsemi.com

74VHC112 Rev. 1.2 9

S-ar putea să vă placă și

- 74VHC574CW Al 74VHC574MSCX PDFDocument8 pagini74VHC574CW Al 74VHC574MSCX PDFJosé Moisés Nuñez SilvaÎncă nu există evaluări

- 74HC564 PhilipsSemiconductorsDocument7 pagini74HC564 PhilipsSemiconductorsTeyfik koyuncuÎncă nu există evaluări

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2De la EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Încă nu există evaluări

- Jameco Part Number 50534FSC: Distributed byDocument4 paginiJameco Part Number 50534FSC: Distributed bymekatronika elbÎncă nu există evaluări

- 74ac74 - DFFDocument13 pagini74ac74 - DFFHoàng Đạt LưuÎncă nu există evaluări

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument5 paginiDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsJoão AlmeidaÎncă nu există evaluări

- 74173Document11 pagini74173zunaidur_rashidÎncă nu există evaluări

- 74HC HCT109 CNV 2Document10 pagini74HC HCT109 CNV 2MUHAMMAD SISWANTOROÎncă nu există evaluări

- DM7476 Dual Master-Slave J-K Flip-Flops With Clear, Preset, and Complementary OutputsDocument6 paginiDM7476 Dual Master-Slave J-K Flip-Flops With Clear, Preset, and Complementary Outputsقرين لطفيÎncă nu există evaluări

- Integrated CircuitsDocument7 paginiIntegrated Circuitssexan8Încă nu există evaluări

- Data Sheet: 74HC/HCT273Document9 paginiData Sheet: 74HC/HCT273Edson CostaÎncă nu există evaluări

- MM74HC74A Dual D-Type Flip-Flop With Preset and Clear: Features General DescriptionDocument11 paginiMM74HC74A Dual D-Type Flip-Flop With Preset and Clear: Features General DescriptionAle MorenoÎncă nu există evaluări

- CD4538Document11 paginiCD4538Sridhar MohanÎncă nu există evaluări

- 74VHC273 29251Document15 pagini74VHC273 29251Alfredo rodriguez gomezÎncă nu există evaluări

- 74HC HCT374 CNV 2Document9 pagini74HC HCT374 CNV 2Bambang D. JayantoÎncă nu există evaluări

- 7476 - JK FFDocument4 pagini7476 - JK FFjbcen8293Încă nu există evaluări

- PI74ALVTC16374: Product Description Product FeaturesDocument9 paginiPI74ALVTC16374: Product Description Product Featuresdcastrelos2000Încă nu există evaluări

- 1-Of-8 Decoder/Demultiplexer: SL74HC138Document5 pagini1-Of-8 Decoder/Demultiplexer: SL74HC138Dimano ManoÎncă nu există evaluări

- MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description FeaturesDocument8 paginiMM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description Featureskumar_santosh1989100% (1)

- 74112Document12 pagini74112Luis Rey Martínez RodríguezÎncă nu există evaluări

- Datasheet PDFDocument4 paginiDatasheet PDFMauricio MontañoÎncă nu există evaluări

- Data Sheet: 74AHC373 74AHCT373Document21 paginiData Sheet: 74AHC373 74AHCT373quasemanobrasÎncă nu există evaluări

- DM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionDocument7 paginiDM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionAzri AzsrÎncă nu există evaluări

- 74HC195Document10 pagini74HC195MUHAMMAD SISWANTOROÎncă nu există evaluări

- Dual J-K Flip Flop With Preset and Clear: Order CodesDocument11 paginiDual J-K Flip Flop With Preset and Clear: Order CodesAtzin SanchezÎncă nu există evaluări

- DM54LS73A/DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument6 paginiDM54LS73A/DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary Outputs4ew018Încă nu există evaluări

- 74HC78 Dual JK Flipflop-RenesasDocument7 pagini74HC78 Dual JK Flipflop-RenesasQuartz AlexanderÎncă nu există evaluări

- 74 Ls 74Document6 pagini74 Ls 74LucianamxsÎncă nu există evaluări

- Dual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221Document5 paginiDual Monostable Multivibrators With Schmitt-Trigger Inputs SN54/74LS221parsa mahvisÎncă nu există evaluări

- M74HC131 Datasheet PDFDocument12 paginiM74HC131 Datasheet PDFmuhamad.badar9285Încă nu există evaluări

- CD 4538Document10 paginiCD 4538Geraldo PereiraÎncă nu există evaluări

- Data Sheet: 74HC595 74HCT595Document29 paginiData Sheet: 74HC595 74HCT595EmaxxSeverusÎncă nu există evaluări

- SMD-DatasheetDocument8 paginiSMD-DatasheetAhmed Sherif CupoÎncă nu există evaluări

- HD74LS76A: Dual J-K Flip-Flops (With Preset and Clear)Document7 paginiHD74LS76A: Dual J-K Flip-Flops (With Preset and Clear)Thế giới điện tửÎncă nu există evaluări

- DM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary OutputsDocument4 paginiDM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary Outputsnivaldo de oliveira OliveiraÎncă nu există evaluări

- DM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary OutputsDocument4 paginiDM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary Outputsnivaldo de oliveira OliveiraÎncă nu există evaluări

- DM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary OutputsDocument4 paginiDM74S112 Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop With Preset, Clear, and Complementary Outputsnivaldo de oliveira OliveiraÎncă nu există evaluări

- 74 Ls 1092Document6 pagini74 Ls 1092JuanDiegoÎncă nu există evaluări

- 74F74 PDFDocument7 pagini74F74 PDFJavier LorensÎncă nu există evaluări

- Data Sheet: 74HC/HCT165Document10 paginiData Sheet: 74HC/HCT165Thế TùngÎncă nu există evaluări

- 74 HC 76Document12 pagini74 HC 76agus satyaÎncă nu există evaluări

- Flip Flop JK 7473Document11 paginiFlip Flop JK 7473Tatyantoro AndrastoÎncă nu există evaluări

- Data Sheet: 74HC/HCT166Document10 paginiData Sheet: 74HC/HCT166vetchboyÎncă nu există evaluări

- Data Sheet: 74HC/HCT240Document7 paginiData Sheet: 74HC/HCT240ALFREDO MORALESÎncă nu există evaluări

- 74HC-HCT251x Eng DatasheetDocument7 pagini74HC-HCT251x Eng Datasheetjohn9999_502754Încă nu există evaluări

- Data Sheet: 74HC/HCT251Document7 paginiData Sheet: 74HC/HCT251kennyfernandezÎncă nu există evaluări

- 74HC74D T PhilipsDocument23 pagini74HC74D T PhilipsБогомолов МаксимÎncă nu există evaluări

- Search For DocumentsDocument9 paginiSearch For DocumentsdineshvhavalÎncă nu există evaluări

- CD-4035 (CD4035 - Registro Desplazamiento de 4 Bits. CMOS - COMPIC)Document11 paginiCD-4035 (CD4035 - Registro Desplazamiento de 4 Bits. CMOS - COMPIC)Adilson LucaÎncă nu există evaluări

- 74HC4053Document18 pagini74HC4053Alvaro MedinaÎncă nu există evaluări

- 74LS107 JK Flip FlopDocument7 pagini74LS107 JK Flip FlopQuartz AlexanderÎncă nu există evaluări

- Hoja Caracteristicas 7474 PDFDocument6 paginiHoja Caracteristicas 7474 PDFArun UpadhyayaÎncă nu există evaluări

- Data Sheet: 74HC/HCT221Document16 paginiData Sheet: 74HC/HCT221MUHAMMAD SISWANTOROÎncă nu există evaluări

- Data Sheet: 74HC/HCT540Document7 paginiData Sheet: 74HC/HCT540Diego GrisalesÎncă nu există evaluări

- M54HC165 M74HC165: 8 Bit Piso Shift RegisterDocument13 paginiM54HC165 M74HC165: 8 Bit Piso Shift RegisternooorÎncă nu există evaluări

- Data Sheet: 74HC/HCT74Document13 paginiData Sheet: 74HC/HCT74mohamadziÎncă nu există evaluări

- Data Sheet: 74HC/HCT175Document14 paginiData Sheet: 74HC/HCT175MUHAMMAD SISWANTOROÎncă nu există evaluări

- ES FinalDocument26 paginiES FinalBilal AhmedÎncă nu există evaluări

- I2C ProtocolDocument17 paginiI2C ProtocolAditya BarveÎncă nu există evaluări

- I. Présentation de L 'Automate II. Représentation Des Entrées Sorties III. Le Langage À Contact Ou LADDER IV. Blocs Fonctions StandardDocument27 paginiI. Présentation de L 'Automate II. Représentation Des Entrées Sorties III. Le Langage À Contact Ou LADDER IV. Blocs Fonctions StandardKacem MohamedÎncă nu există evaluări

- ASUS vw224 Service ManualDocument109 paginiASUS vw224 Service ManualZoran ProkicÎncă nu există evaluări

- Computer Organization and Architecture: Internal MemoryDocument49 paginiComputer Organization and Architecture: Internal MemoryCông PhạmÎncă nu există evaluări

- X360glitchip v2 Installation (En)Document14 paginiX360glitchip v2 Installation (En)Julh BallysÎncă nu există evaluări

- 8051 Assembly Language ProgrammingDocument35 pagini8051 Assembly Language ProgrammingavmapÎncă nu există evaluări

- Es QuestionsDocument2 paginiEs QuestionsdeccancollegeÎncă nu există evaluări

- m1250 Mini PlsDocument34 paginim1250 Mini PlsHuỳnh TuấnÎncă nu există evaluări

- SD Card Module User's Manual v1.0Document9 paginiSD Card Module User's Manual v1.0yunpingchang100% (1)

- Nr310501 Interfacing Through Microprocessors Set1Document2 paginiNr310501 Interfacing Through Microprocessors Set1Srinivasa Rao GÎncă nu există evaluări

- Card Text Main Pi49nDocument34 paginiCard Text Main Pi49nminhthuitbg100% (1)

- Ulcreforr.: AnsmacrDocument4 paginiUlcreforr.: AnsmacrarcÎncă nu există evaluări

- Quartus Prime Introduction Using VHDL DesignsDocument31 paginiQuartus Prime Introduction Using VHDL DesignsNicoli LourençoÎncă nu există evaluări

- Mpa Question Bank1Document16 paginiMpa Question Bank1Sharon FrancisÎncă nu există evaluări

- Red Hat Enterprise Linux-7-Virtualization Deployment and Administration Guide-en-US PDFDocument579 paginiRed Hat Enterprise Linux-7-Virtualization Deployment and Administration Guide-en-US PDFouououououÎncă nu există evaluări

- Assignment 3 - 2 Microcontrollers With DatasheetsDocument2 paginiAssignment 3 - 2 Microcontrollers With Datasheetsapi-42328551276% (45)

- Digital Circuits & Systems EENG 14000: University of Bristol Faculty of EngineeringDocument18 paginiDigital Circuits & Systems EENG 14000: University of Bristol Faculty of Engineering栾子璇Încă nu există evaluări

- SGH A188 Service SchematicsDocument22 paginiSGH A188 Service SchematicsDinesh JenekarÎncă nu există evaluări

- Chapter - 03: Accessing I/O DevicesDocument42 paginiChapter - 03: Accessing I/O DevicesJoseph JohnÎncă nu există evaluări

- Application Kits: PRICE LIST - Currency: USD (No Tax) April 2011Document11 paginiApplication Kits: PRICE LIST - Currency: USD (No Tax) April 2011piyushpandeyÎncă nu există evaluări

- Ug908 Vivado Programming Debugging PDFDocument394 paginiUg908 Vivado Programming Debugging PDFdekas_guitarhero3616Încă nu există evaluări

- Binary Subtractor Lecture NotesDocument6 paginiBinary Subtractor Lecture Notesraul gironellaÎncă nu există evaluări

- Ca 3161Document4 paginiCa 3161romanjoseÎncă nu există evaluări

- 4026 DatasheetDocument12 pagini4026 Datasheetatmega168100% (1)

- Generation of Computer ': Rajiv Academy For Technology and Management, Mathura ONDocument26 paginiGeneration of Computer ': Rajiv Academy For Technology and Management, Mathura ONsouarvÎncă nu există evaluări

- Use of Digital Technologies in EducationDocument5 paginiUse of Digital Technologies in EducationOpen Access JournalÎncă nu există evaluări

- Manual NoctisDocument13 paginiManual NoctisSrMarcos28Încă nu există evaluări

- Expt05 - BCD To 7-Segment DecoderDocument3 paginiExpt05 - BCD To 7-Segment DecoderDvizma SinhaÎncă nu există evaluări