Documente Academic

Documente Profesional

Documente Cultură

BW Scalable

Încărcat de

metalnonmetalDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

BW Scalable

Încărcat de

metalnonmetalDrepturi de autor:

Formate disponibile

A 10MHz to 100MHz Bandwidth Scalable, Fully Differential Current Feedback Amplifier

Nihit Bajaj, Bert Vermeire and Bertan Bakkaloglu

School of Electrical, Computer and Energy Engineering Arizona State University Tempe, AZ 85287, USA Email: nihit@asu.edu

Abstract A technique for power-bandwidth scaling of a current feedback amplifier (CFA) is presented. By employing current gain, instead of the feedback resistance, to alter the closed-loop bandwidth of the CFA, the proposed approach is shown to provide 30% quiescent power savings for a bandwidth variation of 10MHz to 100MHz. Parasitic extracted simulations are performed in a 0.18m CMOS process with a power supply of 3.3V and a load capacitance of 1.5pF. A closed-loop gain range of 0-20dB, slew rate of 200V/s, settling time of 33ns and total harmonic distortion of 73dB is achieved at a quiescent power consumption range of 3mW to 4.4mW.

resistance to vary the bandwidth, we utilize the current gain to do the same, keeping power scaling in mind. Fig. 1 shows the top-level test bench of a first-order CFA model in the conventional non-inverting gain configuration. The voltage at node Y (Vin for this configuration) is first copied to node X through a buffer, which is modeled as a unity-gain block with a series resistance, rb1. The current through node X also the error current for any CFA feedback configuration is then mirrored with finite current gain, Ai (equal to one in most CFA architectures), to an internal high impedance node, Z. The voltage at Z is buffered, through a unity-gain buffer similar to the one at the input, to the output node, Vo. This output node voltage is finally converted to a current through a resistance, Rf, to complete the feedback loop. Rg, is used to vary the closed-loop gain setting. A first order analysis of the circuit yields the following

I.

INTRODUCTION

Current feedback amplifier (CFA) based circuit architectures have gained increased attention in the recent past owing to superiority over their voltage-mode counterparts in terms of speed, linearity, slew rate and bandwidth [1], [2]. These advantages have also led to CFAs being used in a variety of applications including buffers, filters, oscillators and regulators [3]-[7]. Unlike voltage-feedback opamps, which are inherently limited by a constant gain-bandwidth product, CFAs can be used to independently control gain and bandwidth, albeit at the expense of reduced loop gain and hence, reduced accuracy. Moreover, to achieve gainbandwidth independence, a very low output-impedance is usually desired from the input buffer of a CFA [8] - [10]. This is one of the key reasons - along with better current drive capability - why BJTs are preferred over CMOS transistors in most practical designs [11], [12]. Nevertheless, a number of CMOS alternatives have been published in the recent years. Most of these, however, focus on particular performance parameters, including offset compensation [13], highfrequency [14] and low-voltage operation [15], [16]. In this paper, we focus on the complementary source follower cascade current feedback amplifier published in [17] and propose a more generic, modified architecture to accommodate field-programmable closed-loop gain and bandwidth settings. While most CFA designs use the feedback

Figure 1. System-level model of a CFA in the non-inverting configuration

978-1-4244-5309-2/10/$26.00 2010 IEEE

217

expression for the voltage transfer function,

II.

TRANSISTOR-LEVEL DESIGN

Rf 1 + Rg Vo = Vi Rf rb1 1 + Rg 1 + sCZ Ai

(1)

+ Rf

Ignoring the effect of rb1, the closed loop dc voltage gain, AV, and closed loop 3-dB bandwidth, fCL, can be written as

AV = 1 +

f CL =

Rf Rg

(2) (3)

Ai 2R f C Z

The transistor-level schematic of the proposed CFA, shown in Fig. 2, is based on the classic complementary source follower cascade architecture presented in [17], as mentioned earlier. In the circuit, while transistors M1-M4 form the input unity-gain buffer, transistors M13-M16 form the buffer at the output. M7-M8 and M9-M10 help mirror the fed-back current from node X to node Z. M8 and M10 are split into four programmable devices to allow for selection from four bandwidth settings 10MHz, 33MHz, 66MHz and 100MHz. Gain-boosting is also employed to increase the impedance at node Z and hence, to increase the loop gain and settling accuracy. A P-input differential amplifier is designed, as shown in Fig. 3, for the NMOS current mirror since the drain terminals of M9 and M10 sit close to ground. A similar reasoning explains the use of an N-input amplifier (Fig. 4) for the PMOS current mirror. In contrast, low impedance is ensured at node X to help reduce bandwidth variations with closed-loop gain, given by (1), and at node Vo to lower the output impedance of the overall current feedback amplifier. The scaling of transistors M8 and M10 is achieved through switches S3, S2, S1 and S0. A small aspect ratio for M8 and M10 would yield a lower Ai and according to (3), a lower closed-loop bandwidth along with the obvious advantage of lower current flowing through the M8-M11-M12-M10 branch. A point to note here is that transistors M11 and M12, being cascode devices, need not be scaled in the same proportion as their rail-counterparts for bandwidth variation and so, their aspect ratios are kept constant for this design. Another key merit of this architecture is the ability to improve the amplifier bandwidth - at the expense of some extra power - for higher closed loop gain settings by adding extra branches to

It can be seen from (3) that if Ai is used to alter fCL (with Rf and CZ fixed), quiescent power can be saved. Adopting this technique, we show in this paper that scaling the bandwidth from 10MHz to 100MHz leads to 30% savings in power. Keeping Rf constant also means that AV can now be varied using Rg only. Section II describes the transistor-level schematic of the circuit while Section III presents simulation results with the CFA driving a pipeline ADC. Using the CFA for this particular application meant that a fully-differential version of the circuit was required and this resulted in the doubling of area and power requirements. Conclusions are provided in Section IV.

Figure 3. Local N-input gain-boosting amplifier

Figure 2. Transistor-level schematic of the proposed CFA

Figure 4. Local P-input gain-boosting amplifier

218

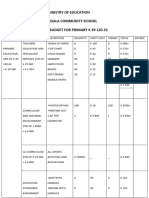

TABLE I.

TRANSISTOR ASPECT RATIOS OF CFA Transistor W/L(m/m) 120/0.54 108/0.54 360/0.54 36/0.54 240/0.54 40/0.54 240/0.54 72/0.54 12/0.54 72/0.54 160/0.72 48/0.72 Figure 6. Power- Bandwidth scaling in the proposed CFA

M1, M5, M13, M17 M2, M6, M14, M18 M3, M15 M4, M16 M7, M19 M8 M9, M20 M10 M11 M12

transistors M8 and M10, a point that will become clear in the next section. III. RESULTS

differential circuit. And as is evident from Fig. 6, which is the bandwidth-power plot for the same set of points as in Fig. 5, 30% of this power is saved when the amplifiers bandwidth requirements are reduced to 10MHz. The small signal AC magnitude response of the CFA for four different values of gain 0dB, 6dB, 12dB and 20dB (achieved by having the resistor, Rg, as a ladder network) can be seen in Fig. 7. Although the bandwidth for a closed loop gain of 20dB is about half of its corresponding 0dB value, it is still five times higher than what could be achieved with a conventional voltage feedback structure. This reduction in bandwidth for the CFA is due largely to the non-zero output impedance of the input buffer stage as can be derived from (1). As hinted earlier, at higher closed loop gain settings, the bandwidth can be improved at the cost of some extra power instead of adopting the conventional technique of further lowering the output resistance of the input buffer. The solution is to add more branches to transistors M8 and M10 and increase Ai to values greater than 1. An example of this scheme is presented in Fig. 8 where the closed-loop bandwidth, for a closed-loop gain setting of 20dB, improves from 48MHz to 100MHz by simply increasing Ai from 1 to 2. The extra power burnt in the process is 1.55mW, only 35% of the total power. Fig. 9 shows the amplifiers response to a 1V differential step input. The slew-rate is noted to be greater than 200V/s and the 0.05% settling time, 33ns. With the CFA in the unity gain configuration and Rf = 2k, pss simulations reveal a total

The current feedback amplifier was used as a buffer for a pipeline ADC with an input capacitance of 1.5pF. Simulations were performed after parasitic extraction in the JAZZ 0.18m CMOS process with a power supply of 3.3V. To achieve a 4V peak-to-peak differential swing, 1.8V-devices were used everywhere in the circuit except for switch implementation. Transistor dimensions are summarized in Table I. The feedback resistor was fixed at 2k and the capacitance, CZ, at 1.5pF. Fig. 5 serves as proof of the proposed concept by plotting closed-loop bandwidth (fCL) vs. current gain (Ai). The plot has four data points corresponding to the four branches of transistors M8 and M10 in Fig. 2. The figure appears to be deviate slightly from the linear dependence between these two parameters expressed in (3). The reasoning lies in the addition of extra poles due to the unity-gain buffers and the current mirrors at the transistor level. The closed-loop system is no longer first-order, which is seen by adding a high-frequency current mirror pole to the system-level model presented in Fig. 1 [18]. The quiescent power required to obtain the maximum desired bandwidth of 100MHz is 4.4mW for the fully-

Figure 5. Bandwidth vs. Current gain plot for the CFA

Figure 7. Closed-loop bandwidth of the CFA for four closed loop gain settings 0dB, 6dB, 12dB and 20dB

219

TABLE II.

KEY PERFORMANCE PARAMETERS OF CFA Parameter Technology (m) Power Supply (V) Value 0.18 3.3 10-100 3.0-4.4 1.5 200 33 0-20 73 68

Closed-loop Bandwidth (MHz) (in four steps) Power Dissipation (mW) Load Capacitance (pF) Slew Rate (V/s) Figure 8. CFA Bandwidth improvement by adding extra current branches (AV = 20dB) Settling time (ns) Closed-loop Gain (dB) (in ten steps of 2dB each) THD @ 1MHz 2Vpp in unity gain with Rf = 2k (dB) IMD @ 1MHz 1Vpp, 2MHz 1Vpp in unity gain with Rf = 2k (dB) [4]

[5]

[6] Figure 9. Step response of CFA to 1V differential step [7]

harmonic distortion (THD) of 73dB for a 1MHz, 2V peak-topeak input signal and an inter-modulation distortion (IMD) of 68dB between 1V peak-to-peak signals of 500kHz and 1MHz. Table II summarizes the key performance parameters of the proposed current feedback amplifier. IV. CONCLUSION

[8] [9]

A current feedback amplifier employing current gain to alter the closed-loop bandwidth has been proposed. The technique is shown to save 30% of power when the bandwidth is scaled from 10MHz to 100MHz. Through simulations performed in the 0.18m process, the circuit is also shown to provide programmable gain setting from 0-20dB, a slew rate of 200V/s, a settling time of 33ns and a total harmonic distortion of 73dB. REFERENCES

[1] D.F. Bowers, "The so-called current-feedback operational amplifier technological breakthrough or engineering curiosity?," IEEE Int. Sym. Circuits Syst., vol. 2, pp. 1054-1057, May 1993. Current Feedback Amplifier Theory and Applications, Intersil Application Note, AN9420.1, Apr. 1995. A. Soliman, Applications of the current feedback operational amplifiers, Analog Integrated Circuits Signal Process., vol. 11, pp. 265302, Nov. 1996.

[10] [11] [12] [13]

[14]

[15]

[16]

[17]

[2] [3]

[18]

A. S. Elwakil and M. P. Kennedy, Improved implementation of Chuas chaotic oscillator using current feedback op amp, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 47, no. 1, pp. 7679, Jan. 2000. A. K. Singh and R. Senani, Active-R design using CFOA-poles: New resonators, filters, and oscillators, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 48, no. 5, pp. 504511, May 2001. J. Bayard and M. Ayachi, OTA- or CFOA-based LC sinusoidal oscillators Analysis of the magnitude stabilization phenomenon, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 49, no. 8, pp. 1231 1236, Aug. 2002. W. Oh, B. Bakkaloglu, A CMOS low-dropout regulator with currentmode feedback buffer amplifier, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 10, pp. 922926, Oct. 2007. G. Palmisano, G. Palumbo, and S. Pennisi, CMOS Current Amplifiers, Boston, MA: Kluwer Academic, 1999. G. Palumbo and S. Pennisi, Current-feedback amplifiers versus voltage operational amplifiers, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 48, no. 5, pp. 617623, May 2001. AD844, Analog Devices Datasheet. OPA683, Texas Instruments Datasheet. OPA2832, Texas Instruments Datasheet. A. Assi, M. Sawan, and J. Zhu, An offset compensated and high-gain CMOS current-feedback Op-Amp, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 45, no. 1, pp. 8590, Jan. 1998. A. M. Ismail and A. M. Soliman, Novel CMOS current feedback OpAmp realisation suitable for high frequency applications, IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 47, no. 6, pp. 918921, Jun. 2000. R. Mita, G. Palumbo, and S. Pennisi, Low-voltage high-drive CMOS current feedback Op-Amp, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 52, no. 6, pp. 317321, Jun. 2005. B. J. Maundy, A. R. Sarkar, and S. J. Gift, A new design for lowvoltage CMOS current feedback amplifiers, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 1, pp. 3438, Jan. 2006. E. Bruun, A dual current feedback op amp in CMOS technology, Analog Integrated Circuits Sig. Proc., vol. 5, no. 3, pp 213-217, May 1994. J. Mahattanakul, C. Toumazou, A theoretical study of the stability of high frequency current feedback op-amp integrators, IEEE Trans. Circuits and Syst. I: Fundamental Theory and Applications, vol. 43, no. 1, pp. 2-12, Jan 1996.

220

S-ar putea să vă placă și

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Origin CDocument110 paginiOrigin CmetalnonmetalÎncă nu există evaluări

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- Baba Katha BooksDocument2 paginiBaba Katha BooksmetalnonmetalÎncă nu există evaluări

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- Anil AmbaniDocument5 paginiAnil AmbanimetalnonmetalÎncă nu există evaluări

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Frequency Key: Campus Loop North CLNDocument1 paginăFrequency Key: Campus Loop North CLNmetalnonmetalÎncă nu există evaluări

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- Substance: Hematite (-Fe O) Property: Magnetic PropertiesDocument5 paginiSubstance: Hematite (-Fe O) Property: Magnetic PropertiesmetalnonmetalÎncă nu există evaluări

- Gta Position Description2014-2015Document2 paginiGta Position Description2014-2015metalnonmetalÎncă nu există evaluări

- Biomass To Liquids ResearchDocument27 paginiBiomass To Liquids ResearchmetalnonmetalÎncă nu există evaluări

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (400)

- Office of Admissions Application Fee Payment Form: Credit CardsDocument1 paginăOffice of Admissions Application Fee Payment Form: Credit CardsmetalnonmetalÎncă nu există evaluări

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- 2014-15 Cbe Bingo SheetDocument4 pagini2014-15 Cbe Bingo SheetIsaac McDermottÎncă nu există evaluări

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- Check-Out Procedures: Last Day at The University... We May Not Be Able To Accomodate You On Such Short NoticeDocument1 paginăCheck-Out Procedures: Last Day at The University... We May Not Be Able To Accomodate You On Such Short NoticemetalnonmetalÎncă nu există evaluări

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- Vegan Friendly Restaurants - Columbus, Ohio: Updated, 4/10/2015, Laura StandfieldDocument5 paginiVegan Friendly Restaurants - Columbus, Ohio: Updated, 4/10/2015, Laura StandfieldmetalnonmetalÎncă nu există evaluări

- 13 14 Sgs Intnl Fee Schedule3Document28 pagini13 14 Sgs Intnl Fee Schedule3metalnonmetalÎncă nu există evaluări

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- Crushing and Grinding 1Document9 paginiCrushing and Grinding 1metalnonmetalÎncă nu există evaluări

- Synthesis and Pharmacological Evaluation of Some Novel Potent Type Ii Antidiabetic AgentsDocument10 paginiSynthesis and Pharmacological Evaluation of Some Novel Potent Type Ii Antidiabetic AgentsmetalnonmetalÎncă nu există evaluări

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- Trek Essential ListDocument1 paginăTrek Essential ListmetalnonmetalÎncă nu există evaluări

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (345)

- Quants Quantitative Comparison Directions: Each of The Questions 1-10 Consists of Two Quantities, One in Column ADocument5 paginiQuants Quantitative Comparison Directions: Each of The Questions 1-10 Consists of Two Quantities, One in Column AmetalnonmetalÎncă nu există evaluări

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (74)

- Aspen InfoDocument2 paginiAspen InfometalnonmetalÎncă nu există evaluări

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- QuizDocument11 paginiQuizDanica RamosÎncă nu există evaluări

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- Hitt PPT 12e ch08-SMDocument32 paginiHitt PPT 12e ch08-SMHananie NanieÎncă nu există evaluări

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- Bank of AmericaDocument1 paginăBank of AmericaBethany MangahasÎncă nu există evaluări

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Agreement Deed BangladeshDocument8 paginiAgreement Deed BangladeshVabna EnterpriseÎncă nu există evaluări

- Data Mining - Exercise 2Document30 paginiData Mining - Exercise 2Kiều Trần Nguyễn DiễmÎncă nu există evaluări

- HP Sustainability Impact Report 2018Document147 paginiHP Sustainability Impact Report 2018Rinaldo loboÎncă nu există evaluări

- 7Document101 pagini7Navindra JaggernauthÎncă nu există evaluări

- Sangeetahealingtemples Com Tarot Card Reading Course in UsaDocument3 paginiSangeetahealingtemples Com Tarot Card Reading Course in UsaSangeetahealing templesÎncă nu există evaluări

- SPC Abc Security Agrmnt PDFDocument6 paginiSPC Abc Security Agrmnt PDFChristian Comunity100% (3)

- IP Based Fingerprint Access Control & Time Attendance: FeatureDocument2 paginiIP Based Fingerprint Access Control & Time Attendance: FeaturenammarisÎncă nu există evaluări

- Effects of Organic Manures and Inorganic Fertilizer On Growth and Yield Performance of Radish (Raphanus Sativus L.) C.V. Japanese WhiteDocument5 paginiEffects of Organic Manures and Inorganic Fertilizer On Growth and Yield Performance of Radish (Raphanus Sativus L.) C.V. Japanese Whitepranjals8996Încă nu există evaluări

- August 2015Document96 paginiAugust 2015Cleaner MagazineÎncă nu există evaluări

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (121)

- PartitionDocument5 paginiPartitionKotagiri AravindÎncă nu există evaluări

- Labor CasesDocument47 paginiLabor CasesAnna Marie DayanghirangÎncă nu există evaluări

- Sciencedirect: Jad Imseitif, He Tang, Mike Smith Jad Imseitif, He Tang, Mike SmithDocument10 paginiSciencedirect: Jad Imseitif, He Tang, Mike Smith Jad Imseitif, He Tang, Mike SmithTushar singhÎncă nu există evaluări

- V Series: Three Wheel, Counterbalanced Lift TruckDocument126 paginiV Series: Three Wheel, Counterbalanced Lift TruckВиктор МушкинÎncă nu există evaluări

- Dr. Li Li Prof. Feng Wu Beijing Institute of TechnologyDocument20 paginiDr. Li Li Prof. Feng Wu Beijing Institute of TechnologyNarasimman NarayananÎncă nu există evaluări

- OrganometallicsDocument53 paginiOrganometallicsSaman KadambÎncă nu există evaluări

- Millionaire Next Door QuestionsDocument7 paginiMillionaire Next Door Questionsapi-360370073Încă nu există evaluări

- EASY DMS ConfigurationDocument6 paginiEASY DMS ConfigurationRahul KumarÎncă nu există evaluări

- Switch CondenserDocument14 paginiSwitch CondenserKader GüngörÎncă nu există evaluări

- Relevant Cost For Decision: Kelompok 2Document78 paginiRelevant Cost For Decision: Kelompok 2prames tiÎncă nu există evaluări

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- UBITX V6 MainDocument15 paginiUBITX V6 MainEngaf ProcurementÎncă nu există evaluări

- QCM Part 145 en Rev17 310818 PDFDocument164 paginiQCM Part 145 en Rev17 310818 PDFsotiris100% (1)

- Practical GAD (1-32) Roll No.20IF227Document97 paginiPractical GAD (1-32) Roll No.20IF22720IF135 Anant PatilÎncă nu există evaluări

- Quality in CRDocument10 paginiQuality in CRkaushikcrÎncă nu există evaluări

- ArpitResumeISM PDFDocument1 paginăArpitResumeISM PDFchethan rÎncă nu există evaluări

- Ministry of Education Musala SCHDocument5 paginiMinistry of Education Musala SCHlaonimosesÎncă nu există evaluări

- Computer System Architecture: Pamantasan NG CabuyaoDocument12 paginiComputer System Architecture: Pamantasan NG CabuyaoBien MedinaÎncă nu există evaluări

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDe la EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonEvaluare: 5 din 5 stele5/5 (2)

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...De la EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Încă nu există evaluări