Documente Academic

Documente Profesional

Documente Cultură

Microprocessors & Interfacing - (Ch3-Sec3A) - 80 X 86 Processor Architecture

Încărcat de

Sainadh PolavarapuDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Microprocessors & Interfacing - (Ch3-Sec3A) - 80 X 86 Processor Architecture

Încărcat de

Sainadh PolavarapuDrepturi de autor:

Formate disponibile

3.

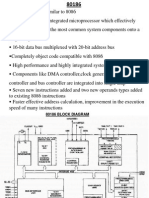

3 The 80386

80286 introduced the protected mode 80386 refined the protected mode 80386 expanded the data registers to 32 bits A new feature called virtual 8086 mode became available 80386 Modes:

Real Mode Protected Mode Virtual 8086 Mode

386 architecture has become the foundation for the next four generations of Intel processors (P3-P6) and seven different microprocessor chips.

The 80386 Real Mode

It is the mode which the processor is initiated to, when started

In this mode the chip is virtually identical to 8086. I.e. it has the following:

Address space is limited to 1MB using the low order address lines A0-A19. The segmented memory addressing scheme is retained (each segment is limited to 64K)

Two new features are available to the programmer:

Access to the 32-bit registers The addition of two new segments: F and G to be explained later

The 80386 Protected Mode

Primary difference from the real mode is in the new addressing mechanism and protection levels in the protected mode Each segment may now range from single byte to 4GB (the full physical address space)

The addresses stored in segment registers are now interpreted as pointers into a descriptor table Each segments entry in this table is 8 bytes long and identifies :

the 32-bit base address of the segment, the segment size and the access rights

The 80386 Protected Mode (continued)

Memory addresses are calculated by adding the offset specified by the instruction to the segment base address. Paging Mechanism:

Translates the 32-bit linear address (segment base plus offset) into a physical address within a 4K page frame. Can manage multiple frames, even swapping frames out to disk, such that 64TB (65,536 GB) of virtual memory is available. Tasks (programs) run in a particular segment and assigned a privilege level, so programs are protected from each other.

Paging Unit:

Protection Mechanism:

The main difference between segmentation and paging is the difference in block sizes. (1 byte 4GB with segmentation). (always 4kB with paging)

The 80386 Virtual 8086 Mode

80386 has two modes to run 8086 programs:

Real mode (discussed above) Virtual 8086 mode

Virtual 8086 mode allows multiple 8086 programs (and 386 applications) to run independent of each other and simultaneously In virtual 8086, each task sees 1MB of address space (which is mapped anywhere in the 4GB of physical memory through paging) Real mode limits the 386 to 1MB of physical memory and one 8086 task can run at a time. Moreover, all of protection and memory management features of 386 are turned off. 386 can be operated in both virtual 8086 mode and protected mode simultaneously. Because each 8086 program is assigned the lowest privilege, access to other programs and segments is not allowed, thus protecting each such task.

FIGURE 3-10

When operated in Virtual 8086 Mode the 386 can run multiple 8086/88 programs simultaneously.

John Uffenbeck 6 The 80x86 Family: Design, Programming, and Interfacing, 3e

The 80386 Processor model

80386 is divided into 3 units:

Bus Interface Unit (BIU) Central Processing Unit (CPU) Memory Management Unit (MMU)

FIGURE 3-11 The processor model for the 80386 microprocessor consists of the bus interface unit (BIU), central processing unit (CPU), and the memory management unit (MMU).

John Uffenbeck 8 The 80x86 Family: Design, Programming, and Interfacing, 3e

The 80386 The BIU

Manages the 32-bit address and data buses and various control signals Keep instruction queue (now 16 bytes) full Two new features have been added: Address pipelining. Dynamic Data Bus Sizing

The 80386 The BIU (continued)

Address pipelining: In this technique the address of the next memory location is to be accessed is output by the 386 half way through the current bus cycle Gives the external memory more address decode time Makes it easier for memory to keep up with the twoclock-pulses-per-bus-cycle processor without adding wait state. The bus cycle is only two clock cycles (compare to 4 clock cycles in 8086)

10

The 80386 The BIU (continued)

Dynamic Data Bus Sizing This allows the 80386 to switch between a 32-bit and 16bit data bus on the fly. The 386 chip can accommodate an external 16-bit memory card or I/O device. When the 16-bit mode is selected, the BIU adjusts bus cycle to use only the low 16-bit of the data bus. When the bus size is set to 32 bit, 4 memory banks are required.

11

The 80386 The CPU

CPU consists of: Instruction Unit (IU): Retrieves instructions from the queue Decodes them Stores them in the decoded instruction queue Execution Unit (EU): Contains the ALU and the 8 general-purpose data registers (now expanded to 32 bits)

12

The 80386 The MMU

The MMU has 2 parts: 1. Segmentation Unit: 2. Paging Unit:

Segmentation Unit Generates the 8086-style (20 bit) physical address when the 386 operates in real mode. When operated in protected mode, the descriptor registers store the base address, size, and attributes of the various segments In effect these registers cache the descriptor tables stored in RAM allowing the processor to switch between tasks very quickly

13

The 80386 The MMU

Paging Unit: Determines the physical address associated with each active segment. Allows segments to be divided into 4K pages. Typically, only the most current pages are kept in memory with the others swapped out to disk. This allows programs whose size is larger than the physical memory to be able to run. This is called Virtual Memory

14

The 80386 Programming Model

The programming model has 2 parts: 1. General-purpose registers

Used by application programs 1. Data group 2. Pointer and index group 3. Status and control flags 4. Segment group

2.

Special-purpose registers

Used by the operating system 1. Control registers 2. System address registers 3. Debug registers 4. Test registers

15

General-purpose registers : used by application programmers

80386 programming model: The general-purpose registers

John Uffenbeck 16 The 80x86 Family: Design, Programming, and Interfacing, 3e

Special-purpose registers : used by OS

John Uffenbeck 17 The 80x86 Family: Design, Programming, and Interfacing, 3e

The 80386 General-purpose Registers- The Data and Address Group

They are the data, pointer and index registers (same as in 8086) Each has been extended to 32-bit To reference the 32-bits use E(A,B,C,D)X Each of the registers EAX, EBX, ECX, and EDX can be accessed in four ways. Example: AL : D0-D7 AH : D8-D15 AX : D0-D15 EAX: D0-D31

18

The 80386 General-purpose Registers- The Status and Control Flags

The 8086 status and control flags have been retained but extended to 32-bits (See figure) In addition, 4 more flags are added (VM, RF, NT, IOPL) VM (Virtual Mode): This is a protected mode control flag, used to switch the processor to virtual 8086 mode RF (Resume flag): Used with the debug registers. When set, the debug fault is ignored and the next instruction is executed normally.

19

The 80386 General-purpose Registers- The Status and Control Flags

NT (Nested task): Used in Protected mode to indicate that the current task was called from another task This affects the type of return instruction to be executed when the nested task completes IOPL ( I/O Privilege Level): 2-bit flag These two Protected Mode control bits identify the current privilege level (0-3) required to execute I/O instructions Allow the operating system to restrict I/O privileges of a task

20

FIGURE 3-13 The 80386 flag word is 32 bits long. Four new flags have been added compared to the 8086: VM, RF, NT, and IOPL. (Courtesy of Intel Corporation.)

John Uffenbeck 21 The 80x86 Family: Design, Programming, and Interfacing, 3e

The 80386 General-purpose Registers- The Segment Group

Two new segment registers have been added : GS and FS. Now six different segments can be active at a time.

All registers are 16-bit (same as 8086). Since no instructions default to the GS or FS, the previous segment register assignment still apply. Real Mode: Same addressing mechanism in 8086, segment registers hold the base address of the segment Protected Mode: Content of segment registers are pointers into a descriptor table whose entries determine the base address of the segment, its size and attributes

22

The 80386 Special-purpose Registers

Not normally used by application programmer. Intended to control the processor in protected mode and for testing. Three Control Registers: They are 32-bit : CR0, CR2, CR3 CR0: is used to enable the paging mechanism, monitor task switching, and select Protected Mode or Real Mode. CR2: holds the address of the last instruction to cause a page fault ( page is not in memory and must be loaded from disk) CR3: holds the base address of the page table.

23

Page table holds the starting address of each page frame and access information about that frame.

The 80386 Special-purpose Registers (continued)

Four System address Registers (GDTR, IDTR, TR, and LDTR): Hold information about the descriptor tables used in Protected Mode. Six Debugging Registers: DR0-3 and DR6-7 Used to set program breakpoints( are addresses where the program should break (pause) and pass control to a debugging routine and that to allow the programmer to inspect the state of registers to debug the program). Two Test Registers (TR6 and TR7): Used to test RAM in the Translation Lookaside buffer (TLB). TLB is used by paging unit to translate virtual memory addresses into physical addresses

24

S-ar putea să vă placă și

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960De la EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Încă nu există evaluări

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDe la EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationÎncă nu există evaluări

- Microprocessor 80386Document17 paginiMicroprocessor 80386gujusÎncă nu există evaluări

- Architecture of 80386Document39 paginiArchitecture of 80386Raj KumarÎncă nu există evaluări

- Architecture of 80386Document39 paginiArchitecture of 80386Imran KhanÎncă nu există evaluări

- Architecture of 80386 MicroproDocument39 paginiArchitecture of 80386 Microproompa13Încă nu există evaluări

- Architecture of 80386Document39 paginiArchitecture of 80386Satish KedarÎncă nu există evaluări

- Architecture of 80386Document39 paginiArchitecture of 80386Jaimon JacobÎncă nu există evaluări

- Microprocessor 80386Document40 paginiMicroprocessor 80386eshwar_worldÎncă nu există evaluări

- MP-MC R16 - Unit-4Document14 paginiMP-MC R16 - Unit-4satyanarayana12Încă nu există evaluări

- FEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofDocument39 paginiFEATURES OF 80386:: 2) Address 4GB of Memory 2) 16 MB ofJ VÎncă nu există evaluări

- Pentium ProcessorDocument18 paginiPentium ProcessorRabab Khan RongonÎncă nu există evaluări

- Architecture of 80386 MicroproDocument39 paginiArchitecture of 80386 MicroproDeepthiÎncă nu există evaluări

- Unit - Iv: Advanced Microprocessors: Salient Features of 80386Document14 paginiUnit - Iv: Advanced Microprocessors: Salient Features of 80386Swamy NallabelliÎncă nu există evaluări

- The Complete Understanding of Microprocessors and Intro To ARMDocument56 paginiThe Complete Understanding of Microprocessors and Intro To ARMasimÎncă nu există evaluări

- Unit-I: - 80386 IntroductionDocument74 paginiUnit-I: - 80386 IntroductionOmkar MarkadÎncă nu există evaluări

- FEATURES OF 80386:: 3) Address 4GB of Memory 3) 16 MB ofDocument39 paginiFEATURES OF 80386:: 3) Address 4GB of Memory 3) 16 MB ofSorabh ChhabraÎncă nu există evaluări

- Architecture of 80386 MicroproDocument40 paginiArchitecture of 80386 MicroproajayÎncă nu există evaluări

- Architecture of 80386Document42 paginiArchitecture of 80386santosh.parsaÎncă nu există evaluări

- 32 - Bit Microprocessor-Intel 80386Document35 pagini32 - Bit Microprocessor-Intel 80386Kartik BinagekarÎncă nu există evaluări

- NotesDocument21 paginiNotesShinisg Vava50% (2)

- 80386Document84 pagini80386SridharÎncă nu există evaluări

- Document 2Document4 paginiDocument 2Abdulrafay SaimÎncă nu există evaluări

- G MPMC U4 Rit 150 CopiesDocument19 paginiG MPMC U4 Rit 150 CopiesBobby SatyaÎncă nu există evaluări

- Introduction of Intel ProcessorsDocument22 paginiIntroduction of Intel ProcessorscrsarinÎncă nu există evaluări

- Advanced Microprocessors: Presented by Ashish Kumar Singh Pranav Gautam Guide Mrs. Nayanica SrivastavaDocument20 paginiAdvanced Microprocessors: Presented by Ashish Kumar Singh Pranav Gautam Guide Mrs. Nayanica SrivastavaPranav GautamÎncă nu există evaluări

- Architecture of 80286 80386 80486 MicroproseccorsDocument91 paginiArchitecture of 80286 80386 80486 MicroproseccorsYash Mistry100% (1)

- 3rd Unit FinalDocument80 pagini3rd Unit FinalTARANÎncă nu există evaluări

- Week2-The 8086 Microprocessor ArchitectureDocument48 paginiWeek2-The 8086 Microprocessor ArchitectureJerone CastilloÎncă nu există evaluări

- 8086 Third Term TopicsDocument46 pagini8086 Third Term TopicsgandharvsikriÎncă nu există evaluări

- Advanced Microprocessors: Dr. Hetal PatelDocument29 paginiAdvanced Microprocessors: Dr. Hetal PatelAnasÎncă nu există evaluări

- Microprocessor Unit OneDocument21 paginiMicroprocessor Unit OneUtshab ChapagainÎncă nu există evaluări

- and 80486Document28 paginiand 80486sangeetaranjan0% (1)

- 32 - Bit Microprocessor-Intel 80386Document71 pagini32 - Bit Microprocessor-Intel 80386Ibtisam Anwar KhattakÎncă nu există evaluări

- Features of 80386Document13 paginiFeatures of 80386Aswathy CjÎncă nu există evaluări

- MP Unit-8 VtuDocument10 paginiMP Unit-8 VtuBmvpÎncă nu există evaluări

- Features of 80186, 80286, 80386, 80486 and Pentium Family Processors Ee Vi Sem Amit ThakurDocument23 paginiFeatures of 80186, 80286, 80386, 80486 and Pentium Family Processors Ee Vi Sem Amit Thakuritsanshika555Încă nu există evaluări

- Lecture#2 Fut Microprocessor PDFDocument81 paginiLecture#2 Fut Microprocessor PDFAhmedGamalÎncă nu există evaluări

- Features of 80186, 80286, 80386, 80486 and Pentium Family ProcessorsDocument32 paginiFeatures of 80186, 80286, 80386, 80486 and Pentium Family ProcessorsRahul SinghÎncă nu există evaluări

- Microprocessor ArchitectureDocument23 paginiMicroprocessor Architectureganesh6583Încă nu există evaluări

- Advanced Microprocessors: Intel 80186Document13 paginiAdvanced Microprocessors: Intel 80186Rehana Karim Toma100% (1)

- Processor: Microprocessor Architectures and Assembly Language ProgrammingDocument76 paginiProcessor: Microprocessor Architectures and Assembly Language ProgrammingInquisitive KidÎncă nu există evaluări

- and Pentium MicroprocessorsDocument37 paginiand Pentium Microprocessorsgayathrishiv91100% (1)

- Advanced ProcessorDocument85 paginiAdvanced ProcessorRenit AntoÎncă nu există evaluări

- Physical AddressingDocument28 paginiPhysical AddressingRajiv SivalingamÎncă nu există evaluări

- 15Cs205J/Microprocessors and Microcontrollers Unit - 1: Introduction To Microprocessor and FamilyDocument194 pagini15Cs205J/Microprocessors and Microcontrollers Unit - 1: Introduction To Microprocessor and FamilySeven EightÎncă nu există evaluări

- 80286, 80386, 80486 and Pentium MicroprocessorDocument9 pagini80286, 80386, 80486 and Pentium Microprocessoramit mahajan91% (11)

- 80386Document89 pagini80386chandanayadav849050% (2)

- Vtu 4TH Sem Cse Microprocessors Notes 10CS45Document125 paginiVtu 4TH Sem Cse Microprocessors Notes 10CS45EKTHATIGER63359095% (22)

- 80386DX-Basic Programming Model and Applications Instruction SetDocument126 pagini80386DX-Basic Programming Model and Applications Instruction SetNIRAJ CHORDIAÎncă nu există evaluări

- MICRO133 Prelim Lecture 3 Intel 80286 and 80386 Microprocessor Protected Mode Addressing v2Document60 paginiMICRO133 Prelim Lecture 3 Intel 80286 and 80386 Microprocessor Protected Mode Addressing v2John Vinz CustodioÎncă nu există evaluări

- MPMC M-2 U-4Document21 paginiMPMC M-2 U-4Krishna BoreddyÎncă nu există evaluări

- Real-Mode and Protected-Mode Memory AddressingDocument13 paginiReal-Mode and Protected-Mode Memory AddressingPriya DarshiniÎncă nu există evaluări

- Contents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086Document26 paginiContents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086ajayÎncă nu există evaluări

- Chapter Two: The 8086 Microcontroller ArchitectureDocument42 paginiChapter Two: The 8086 Microcontroller Architecturehaftom brhaneÎncă nu există evaluări

- MPS Lecture 3 - The Microprocessor and Its ArchitectureDocument26 paginiMPS Lecture 3 - The Microprocessor and Its ArchitectureShehroze TalatÎncă nu există evaluări

- Microprocessor Unit-1 PART ADocument12 paginiMicroprocessor Unit-1 PART ASasi BhushanÎncă nu există evaluări

- Unit 3 MicroprocessorDocument155 paginiUnit 3 MicroprocessorHUISCIÎncă nu există evaluări

- Microprocessor Helpful NotesDocument234 paginiMicroprocessor Helpful NotesNevin HardyÎncă nu există evaluări

- Unit 1Document48 paginiUnit 120IF207 Gayatri PatilÎncă nu există evaluări

- Amp. 100 Watt ExtractedDocument6 paginiAmp. 100 Watt ExtractedJosue CórdovaÎncă nu există evaluări

- Protection Relay StandardDocument3 paginiProtection Relay StandardThirumalÎncă nu există evaluări

- Vostro 3500 Compal - La-9103Document53 paginiVostro 3500 Compal - La-9103Rogerio E. Santo0% (1)

- Power in RC and RL CircuitsDocument4 paginiPower in RC and RL CircuitsYzza Veah Esquivel100% (1)

- How To Extend LTE Coverage With Limited RRU Capacity-Read OnlyDocument14 paginiHow To Extend LTE Coverage With Limited RRU Capacity-Read OnlyArtty Numatti67% (3)

- IOT2x 01 Ohm S LawDocument4 paginiIOT2x 01 Ohm S LawRajesh Babu MovvaÎncă nu există evaluări

- TransformersDocument33 paginiTransformersMaster ChiefÎncă nu există evaluări

- JVC XM-228BK MD Recorder Owner's ManualDocument40 paginiJVC XM-228BK MD Recorder Owner's ManualhjlopezÎncă nu există evaluări

- Ilox Epu-1500 ManualDocument1 paginăIlox Epu-1500 ManualMar Val Ionita100% (1)

- Vectron OcxoDocument7 paginiVectron Ocxob33g33Încă nu există evaluări

- Power Calculation Summary and ExamplesDocument12 paginiPower Calculation Summary and ExamplesHernán RodarteÎncă nu există evaluări

- Basic Arduino NotesDocument11 paginiBasic Arduino NotesdanielÎncă nu există evaluări

- VAT3FD 6-13 Bis 6-42Document30 paginiVAT3FD 6-13 Bis 6-42msmhnkmr33Încă nu există evaluări

- Digital IQ DemodulatorDocument3 paginiDigital IQ DemodulatoraboashoorÎncă nu există evaluări

- Scheme Asus n10 PDFDocument97 paginiScheme Asus n10 PDFЮра ИвановÎncă nu există evaluări

- F5050 NTSC TV14-69 Black CurvesDocument1 paginăF5050 NTSC TV14-69 Black Curvesefren6716Încă nu există evaluări

- A Complete Narrow-Band Power Line Communication Node For AMRDocument6 paginiA Complete Narrow-Band Power Line Communication Node For AMRSudheer KakaniÎncă nu există evaluări

- Rhomberg Brasler Slimline Sc-320 - Especificaciones GeneralesDocument4 paginiRhomberg Brasler Slimline Sc-320 - Especificaciones Generalesbiotech666Încă nu există evaluări

- 7SS52xx Manual A1 V046002 enDocument430 pagini7SS52xx Manual A1 V046002 enmuthusamyeeeÎncă nu există evaluări

- Preview of Introduction To IDDQ TestingDocument20 paginiPreview of Introduction To IDDQ TestingywkaiÎncă nu există evaluări

- Power Converter For Wind Turbine Application: of PO IdahoDocument2 paginiPower Converter For Wind Turbine Application: of PO IdahosmkiruthigaÎncă nu există evaluări

- Antenna - Wireless NetworkDocument20 paginiAntenna - Wireless NetworkYoza FendrianiÎncă nu există evaluări

- Supra BBK Cv9202l-tDocument57 paginiSupra BBK Cv9202l-tSimon Tyzack0% (1)

- Ac To AcDocument32 paginiAc To AcAbenezer ZenebeÎncă nu există evaluări

- 2.linear Integrated Circuits Lab 2013 RegulationDocument104 pagini2.linear Integrated Circuits Lab 2013 RegulationNandha KumarÎncă nu există evaluări

- Project: Order: Customer: Drawing: Date:: VVVF L1000A Oper. 220V Br200 SimplexDocument18 paginiProject: Order: Customer: Drawing: Date:: VVVF L1000A Oper. 220V Br200 SimplexMarcelo MuñozÎncă nu există evaluări

- A 72db-Dr 465mhz-Bw Continous-Time 1-2 Mash Adc in 28nm CmosDocument11 paginiA 72db-Dr 465mhz-Bw Continous-Time 1-2 Mash Adc in 28nm CmosHoang NguyenÎncă nu există evaluări

- Precision Rectifier CircuitsDocument13 paginiPrecision Rectifier CircuitsWaqas PervaizÎncă nu există evaluări

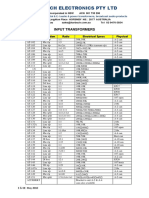

- Harbuch Electronics Pty LTD: Input TransformersDocument4 paginiHarbuch Electronics Pty LTD: Input Transformersattapapa100% (1)

- MicroKinetics MightyDrive SL PIN OUTS Reference Manual Official CNC DMicroriver Stepper Controller BoardDocument2 paginiMicroKinetics MightyDrive SL PIN OUTS Reference Manual Official CNC DMicroriver Stepper Controller BoardAndreus GrotiusÎncă nu există evaluări