Documente Academic

Documente Profesional

Documente Cultură

A Generic RTOS Model For Real-Time Systems Simulation With SystemC

Încărcat de

nithin s gowdaDescriere originală:

Titlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

A Generic RTOS Model For Real-Time Systems Simulation With SystemC

Încărcat de

nithin s gowdaDrepturi de autor:

Formate disponibile

A Generic RTOS Model for Real-time Systems Simulation with SystemC

R. Le Moigne, O. Pasquier, J-P. Calvez Polytech, University of Nantes, France rocco.lemoigne@polytech.univ-nantes.fr

Abstract

The main difficulties in designing real-time systems are related to time constraints: if an action is performed too late, it is considered as a fault (with different levels of criticism). Designers need to use a solution that fully supports timing constraints and enables them to simulate early on the design process a real-time system. One of the main difficulties in designing HW/SW systems resides in studying the effect of serializing tasks on processors running a Real-Time Operating System (RTOS). In this paper, we present a generic model of RTOS based on SystemC. It allows assessing real-time performances and the influence of scheduling according to RTOS properties such as scheduling policy, context-switch time and scheduling latency.

1. Introduction and objective

A real-time system is characterized by its timing constraints in a sense that results or actions must be provided within a specific time window otherwise they are considered to be wrong, whatever their value is [10]. Beyond the correctness of algorithms, checking early on the design process the systems time-related behavior and constraints is essential. In this paper, we present a solution for modeling and simulating real-time systems including software and hardware parts (co-simulation) with SystemC. Our solution is based on a set of generic C++ classes that model a RTOS. The choice for working with a System Level Design Language (SLDL) (like SystemC or SpecC) is important for ensuring portability of the model. We chose to work on SystemC [3] because it emerges as the industry standard for transactional-level modeling and system-level design, and co-simulation of mixed HW/SW systems. However, our solution can easily be adapted to another SLDL language like SpecC for example. As a reminder, SystemC is a language and a simulation kernel based on C++ that allows the

representation of software and hardware components and communications at different abstraction levels. It appears as a well-suited answer to the increase of systems design complexity, by providing an executable model early on the design process. Since its introduction in 1999, the capabilities of SystemC are evolving; SystemC 1.x has similar modeling capabilities as VHDL and Verilog -intended for system design at the RTL level-, whereas the most recent versions -2.0 and 2.0.1- allow for modeling at the system level [3]. However, up to now, SystemC does not allow describing and simulating real-time applications using a Real Time Operating System (RTOS) dealing with the serialization of tasks on a processor. Therefore, our objective is defining an accurate RTOS model to allow designers of real-time systems to validate their concepts with SystemC. Since there are numerous scheduling policies used by designers, this model should be also generic. This document is organized as follows. First, we describe the problems to be solved and related solution. Then, we present the main features of our RTOS model. Next, we present two different techniques to implement a RTOS model. The last part presents experiments and results.

2. Problems to be solved and related solution

Generally speaking, a real-time system is composed of a set of tasks, each running a sequential algorithm, and communicating between them with high-level communication mechanisms. With most RTOS, these communication mechanisms are: - Synchronization (based on events or semaphores) - Message passing (based on message queues); - Data sharing (based on global data protected by mutual exclusion). Our work is based on the MCSE methodology [5] and its functional model which describes a system by a set of functions (e.g. tasks) and relations between them. These

1

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

relations, similar to those of a RTOS, can be of three kinds: - Event: it is used to synchronize functions. Several policies are used to model different behaviors: fugitive (no memorization like SystemC sc_event), boolean (one level of memorization) or counter. - Message queue: it implements a producer/consumer type of relation. Its message capacity is a parameter. - Shared variable: it exchanges data without any synchronization except mutual exclusion. We use the MCSE functional model for system modeling because it describes at a high abstraction level all features that can be found in a real-time system. However, this work is not specifically linked to this model, and can be applied to any other high level abstraction model. Simulation of a system at a high abstraction level becomes very important for early design-space exploration. A first level of difficulty resides in simulating the behavior of the system without considering the effect of implementing tasks on processors. This kind of simulation can be easily achieved with SystemC 2.0 and a set of extended classes for example [8]. But this only allows verifying the correctness of the systems behavior and algorithms, because it does not take into account the influence of implementation choices or physical constraints (processor, RTOS, communications network ). However, it is essential to take into account the implementation early on the design process to explore efficiently the design space. For this purpose, it is necessary to simulate the system according to the platform on which it runs (processor, DSP, FPGA ). A SLDL can simulate easily concurrent behaviors, but not the effect of task serialization on a processor when using a RTOS. In this paper we focus on modeling and simulating the effect of a RTOS on the systems behavior. The objective is to provide results to help designers in their designspace exploration and timing-constraints verification as early as possible on the design process. Different techniques have been proposed for RTOS simulation. TIMAs team proposes a first technique that consists in using a simulator dedicated to a specific RTOS [2] like WindRivers VxSim for VxWorks [9]. The produced results are very precise, since the simulator is designed to perfectly model the RTOS, but they are also fully linked to a specific RTOS and its API. Thus, the design-space exploration is limited to the possibilities of the selected RTOS. To avoid this limitation, a highly abstract model of a RTOS can be developed. In [11], such a model (called SoCOS) is presented, but it is based on a specific

simulation engine. With this solution, it is difficult to synchronize the simulation of the RTOS part with the simulation of hardware part which may run on another simulation engine (SystemC for example). We presented the same idea in [7]. Another solution consists in developing a RTOS model on top of a SLDL. Gajskis team proposes in [1] a RTOS model which is developed for SpecC. This kind of model allows obtaining results on dynamic real-time behavior without being influenced by technical choices. But for us, this model is related to SpecC and does not model RTOS preemption with enough time accuracy since its precision depends on the models clock accuracy. The solution we present in this paper is close to Gajskis team proposal [1] but it uses SystemC and provides a timeaccurate preemption model of RTOS independent from any clock considerations. Our solution is also already integrated into a global tool [12] for performance analysis developed and sold by CoFluent Design. It can be considered as a mixture of the virtual OS and aggregate timed model of OS also proposed by TIMA in [4]. In the next section, we present a description of the RTOS behavior and then, the model we propose.

3. The RTOS model

A RTOS is not only defined by its behavior (scheduling algorithm), but also its timing properties, i.e. contribution to the time evolution of a set of tasks. A global system timing parameter is called the RTOS overhead. In our solution we accurately model both the RTOS behavior and its timing properties.

3.1 RTOS behavior modeling

The priority-based preemptive scheduling policy is the most widely used, but there are many others [10] and some are developed specifically for an application. At a high abstraction level, we can characterize a RTOS behavior by two parameters: - The scheduling policy: it defines the RTOS algorithm used to select the running task among the ready tasks. It can be based on task priorities or deadlines for example. - The preemptive/non-preemptive mode. A preemptive RTOS can suspend a running task between two of its RTOS calls (hardware interrupt occurrence for example). This parameter is very important in RTOS modeling since it can delay or not (non-preemptive) the consideration of external events. Our model considers these two parameters. Several scheduling policies are implemented but since we

2

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

cannot implement all specific ones, designers can also define their own policies by overloading the SchedulingPolicy method of our Processor class. While the scheduling policy is set at the simulations start and cannot be dynamically changed, the preemptive/non-preemptive mode can be changed during the simulation. This enables to model critical regions during which task preemption is not allowed.

in [8]. This code generator is able to automatically provide an executable model including functions and processors in a few seconds.

4. RTOS model implementation

First we present a task scheduling implementation based on a thread that simulates the behavior of the RTOS. For us, this first approach seemed natural in its principle. After analyzing the pros and cons of this first solution, we finally present a second approach based on the definition of a set of RTOS procedures called by tasks as they really do with a real RTOS. Before presenting our approaches, let us remind that each task running on a RTOS can be in only one of the following states at each moment [10]: - Waiting: waiting for a synchronization; - Running: running on the processor; - Ready: waiting to be selected by the RTOS to enter the Running state.

3.2 RTOS timing modeling

The RTOS overhead may be neglected if it is very much smaller than tasks durations. But it is not always the case. RTOS overhead depends mainly on 3 parameters: - The scheduling duration: it characterizes the time spent by the RTOS to select a ready task. This duration depends not only on the scheduling algorithm, but also on the number of ready tasks when the algorithm runs. - The context-load duration: it characterizes the time required by the RTOS to load the context of the running task (processor registers). - The context-save duration: it characterizes the time required by the RTOS to copy the context of the suspended task from the processor registers to the memory. In our model, these three parameters are modeled and can be fixed or defined by a user formula computed during the simulation according to the current state of the simulated system (number of ready tasks for example). To summarize our solution, a system is modeled by a set of C++ objects that inherit from the processor and function classes defined in our model. Figure 1 illustrates a part of the UML class diagram of our solution.

SystemC classes

sc_module sc_event

4.1 Task scheduling using a dedicated thread

For our first solution, the behavior of each task implemented on a processor is implemented by a SystemC thread. The behavior of the RTOS is also modeled by a SystemC thread. Each task is implemented by a C++ object which uses four SystemC events (TaskResume, TaskRun, TaskPreempt and TaskBlocked) which the thread can wait on according to the tasks current state. The RTOS thread waits on a SystemC event (RTKRun). The simulation technique consists in controlling the evolution of all these threads by using the SystemC events so that at any moment only one thread is running. The time evolution of the system and RTOS is based on a delay procedure similar to the one presented by TIMAs laboratory [2]. Each task in the Ready state is referenced in the RTOS ReadyTaskQueue.

Ta sk thr ea ds

RTOS model classes

+ Next 0..1

Processor List + Elt : Function*

+ ReadyTaskQueue - SchedulingDuration

-LocalProcessor Function

TaskN Task2 Task1

RTOS thread

+ priority

- ContextLoadDuration - ContextSaveDuration <<virtual>> SchedulingPolicy()

+ TaskResume + TaskRun + TaskPreempt + TaskBlocked

Ready

TaskResume(T1) RTKRun

Running

System to simulate classes

: Processor : Processor

: Function : Function : Function

TaskRun(T1)

Waiting

TaskPreempt(T1)

RTKRun TaskPreempt(Ti)

RTKBlocked TaskRun(Tj)

Figure 1 UML class diagram. To provide the SystemC code that models the system, we have enhanced our SystemC code generator presented

TaskBlocked(T1) RTKRun

Running

Waiting

Figure 2 Task states and RTOS states.

3

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

Figure 2 presents the possible different states of a task and of the RTOS and the synchronization links between these threads. During the simulation, system tasks notify the RTOS thread when they enter or leave the Waiting state. Then the RTOS thread runs the scheduling algorithm and decides what task in its ReadyTaskQueue must be activated and then notifies it by its TaskRun event. Figure 3 shows an example of thread switching to simulate two tasks running on a RTOS.

In this second solution, we use one thread per task; the RTOS is implemented by a C++ object with a set of methods, but without using a thread (see Figure 4). Each task notifies the other ones by using methods of the RTOS object. The RTOS object has three main methods used by the tasks: TaskIsReady(): it is called when the task enters the Ready state. If the scheduling policy allows the ready task to preempt the running one, then the ready task sends the TaskPreempt event to the running task. TaskIsBlocked(): it is called by a task that enters the Waiting state. The scheduling algorithm must select another task to run and notifies it with the TaskRun event. TaskIsPreempted(): this method is called by the running task when receiving the TaskPreempt event. It computes the remaining time for completing the current operation.

Scheduling TaskContextSave Scheduling TaskContextLoad TaskContextSave

Threads

priority

RTOS Task1 Task2

Task1 waits for an external event external event (HW interrupt)

Figure 3 Task scheduling with a RTOS thread.

4.2 Task scheduling using procedure calls

Our first solution implies many SystemC thread switches (between tasks and RTOS). This has a huge effect on the simulation duration. So we optimize the RTOS model implementation by removing the RTOS thread, without altering the models possibilities. This solution is close to the real implementation of a RTOS which is based on a set of procedures (called primitives) [10].

Ta sk thr ea ds

Threads Task1 Task2

RT OS

TaskContextLoad

priority

TaskN Task2 Task1

TaskIsReady()

t HW interrupt Figure 5 Task scheduling without a RTOS thread.

Figure 5 shows the threads behaviors for this solution. We can observe that fewer thread switches occur than in the previous solution and that the RTOS algorithm is executed by the thread of the running task which becomes blocked and by the thread of the task which was awaked. Figure 5 also presents the RTOS overhead decomposition in three basic times which correspond to the context save, scheduling and context load operations of a RTOS. To conclude on these two approaches, we think that the use of a thread dedicated to the task scheduling makes the modeling of some scheduling policies easier, like modeling the Time Sharing algorithm for example. However, this approach increases the simulation duration since there is a context switch for each call to the scheduler and each return, what is not the case when we use procedure calls. In the case of using procedure calls, the only thread switches are those of the tasks of the system were designing that occur.

Ready

TaskResume(T1) TaskIsReady()

TaskPreempt(Ti)

TaskRun(T1)

Waiting

TaskPreempt(T1) TaskIsPreempted()

TaskBlocked(T1) TaskIsBlocked()

Running

TaskRun(Ti)

Figure 4 Integration of the RTOS behavior into the behavior of tasks state transitions.

4

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

RT OS

5. Experiments and results

We developed a tool [8][12] that allows users to capture the model of real-time systems, and obtain automatically an equivalent SystemC model including our RTOS model for its behavioral verification. Results can be displayed in different ways [6][8]. The most interesting diagram that let users observe the influence of the RTOS is the Timeline chart. A TimeLine chart displays the tasks states and interactions with various types of relations (read, write, signal). A vertical arrow represents a task accessing a communications link and the arrow style informs on the kind of access (read, write). Each horizontal line represents the state of each task with a different style and color (Creation, Running, Destruction, Waiting for processor availability (Ready), Waiting for a synchronization (Waiting), Waiting for resource). From such a display tool we can get much information such as synchronization sequences between tasks and the time spent by a task waiting for synchronization or for mutual exclusion. Therefore, from a TimeLine chart we can extract performance results that are useful to define the best architecture to implement the application. On a TimeLine chart, we can make also time measurements to verify time constraints of the system. As an example, we can measure the time spent between an external event and the systems reaction. Figure 6 presents a part of a TimeLine chart produced by our tool. To make understanding easier, we added on the figure references and time durations, as these measurements can be easily done with our tool.

Processor. Here, tasks are scheduled by priority-based preemptive scheduling. First, we can observe the scheduling of the tasks at the beginning of the simulation: Function_1, Function_2 and Function_3 are executed sequentially. Next, we can see Function_1 preempting Function_3. On (1), Clock notifies the event Clk and so awakes Function_1. Then Function_1 preempts Function_3 and starts its processing. During its execution, Function_1 sends the Event_1 event (2) and awakes Function_2. Function_2 does not preempt Function_1 because it has a lower priority. When Function_1 ends, Function_2 starts its processing. Finally, when Function_2 ends, Function_3 resumes its execution where it was preempted. From this display, we can observe also the RTOS overheads. Here, we have defined a RTOS that has a SchedulingDuration, a TaskContextLoad and a TaskContextLoad that all equal to 5s. Then, we can observe the overhead duration when a task ends and when a task is resumed (a), when a task is preempted (b) or when a task is not preempted (c).

(2)

(1)

(3)

(1) 10s

(Priority = 5)

Figure 7 Example of mutual exclusion blocking.

15s (b) 5s (c) (2) 10s

10s

(Priority = 3)

(a) 10s 10s

(Priority = 2)

Figure 6 Example of a TimeLine result. The system is composed of a hardware task named Clock and of three software tasks named Function_1, Function_2 and Function_3 running on the same

Based on the simulation of the same application presented before, figure 7 presents a blocking mutual exclusion situation. On (1), Function_3 is preempted by Function_1 during a read operation of the SharedVar_1 shared variable. On (2), Function_2 is blocked, waiting for the SharedVar_1 resource. Then Function_3 resumes its execution after an overhead duration. On (3), Function_3 releases the SharedVar_1 resource and is preempted by Function_2 which has a higher priority. This priority inversion problem can be avoided by disabling preemption during access to shared data [10]. With our RTOS model, this behavior can be modeled. Designers can easily check the need or benefit of such a solution for their system.

5

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

The timeline display tool allows a detailed analysis of the behavior of a real-time system, but it is not easy to get a global view on the system. We can provide statistics for the whole simulation from a global analysis of the systems simulation.

(1) (2)

(3)

also accurately depicts task preemption by a hardware event without adding any delay due to simulation technique. Thus, it is very easy to explore the design space of real-time systems implemented on SoC composed of several processors and FPGA and obtain accurate results. Our solution is already implemented and available in a commercial product named CoFluent Studio [12]. Our technique is close to the real implementation of a multitask application running on a RTOS. This approach has been selected for simulation efficiency reasons, but also to ease software generation for a final implementation using commercial RTOS. This software generation is a goal of our future work. Another improvement we can imagine now is automatic verification of timing constraints by simulation after setting these constraints in the initial system model.

(4)

Figure 8 Example of statistics from a TimeLine. Figure 8 presents an example of statistic results obtained for the application we have previously presented. We can observe the activity ratio of each task on a processor (1), their preempted ratio (2) and the ratio when waiting on resources (mutual exclusion) (3). We can also get statistics concerning the communications like their utilization ratio (4). All these results are presented for a very simple system in this paper. We have also used our simulation model and display tools to explore the design space of a more complex application such as a video MPEG-2 compressing and decompressing SoC. The system is composed of 18 tasks implemented on six processors, three of them are software processors with a RTOS model.

7. References

[1] A Gerstlauer, H Yu and D D Gajski, UC Irvine, US, RTOS Modeling for System Level Design, DATE 2003 [2] S Yoo, I Bacivarov, A Bouchhima, Y Paviot, and A A Jerraya, TIMA Laboratory, FR, Building Fast and Accurate SW Simulation Models Based on Hardware Abstraction Layer and Simulation Environment Abstraction Layer, DATE 2003 [3] "Functional Specification for SystemC 2.0", available at www.systemc.org [4] S Yoo, G Nicolescu, L Gauthier, A A Jerraya, TIMA Laboratory, FR, Automatic generation of fast timed simulation models for operating systems in SoC Design, IEEE 2002 [5] J.P. Calvez, Embedded Real-Time Systems. A Specification and Design Methodology, John Wiley, 670 pages, 1993 [6] J.P. Calvez, O. Pasquier, Performance Monitoring and Assessment of Embedded Hw/Sw Systems. In "Design Automation for Embedded Systems", Vol 2, Kluwer Academic Publishers, 1997 [7] O. Pasquier , J-P. Calvez, An object-base executable model for simulation of real-time Hw/Sw systems, Proceedings of DATE 99, March 1999, Munich. [8] R. Le Moigne, O. Pasquier, J-P. Calvez, A Graphical Tool for System Level Modeling and Verification with SystemC, FDL 03, September 2003, Frankfurt. [9] VxWorks and Wind River Systems products available at www.windriver.com. [10] G. C.Buttazzo, "Hard Real-Time Computing Systems", Kluwer Academic Publishers 2002, ISBN 0-7923-9994-3 [11] D. Desmet, D. Verkerst, H. De Man, "Operating System Based Software Generation for System On Chip" in DAC, June 2000. [12] CoFluent StudioTM, available at www.cofluentdesign.com.

6. Conclusion and future work

In this paper, we propose a generic RTOS model for simulation of real-time systems at a high abstraction level with SystemC. This model is implemented as a set of C++ classes which run on top of the SystemC 2.0 simulation engine of and does not require any modification in the language. This solution allows co-simulating with SystemC hardware and software parts, including our RTOS model and application tasks. Compared to other existing models, our model allows an accurate RTOS time representation based on three parameters (context load and save durations and scheduling algorithm duration). They allow to analyze the effect of processor change (context load and save durations) and of RTOS change (scheduling algorithm duration) early in the design space exploration. Our model

6

Proceedings of the Design, Automation and Test in Europe Conference and Exhibition Designers Forum (DATE04) 1530-1591/04 $20.00 2004 IEEE

S-ar putea să vă placă și

- Modern Intelligent Instruments - Theory and ApplicationDe la EverandModern Intelligent Instruments - Theory and ApplicationÎncă nu există evaluări

- Real-Time Fuzzy Microcontroller PDFDocument6 paginiReal-Time Fuzzy Microcontroller PDFsamyÎncă nu există evaluări

- Dan Saks C++ in Embedded SystemsDocument24 paginiDan Saks C++ in Embedded SystemsarunksahaÎncă nu există evaluări

- Lambda PDFDocument24 paginiLambda PDFTrinidad MerriweatherÎncă nu există evaluări

- Diploma Project 1st Presentation PPT TemplateDocument13 paginiDiploma Project 1st Presentation PPT TemplateJay PatelÎncă nu există evaluări

- LoRa v01 PDFDocument38 paginiLoRa v01 PDFEmilian LpÎncă nu există evaluări

- Curs Symfony - EnglezaDocument295 paginiCurs Symfony - EnglezalucianluciÎncă nu există evaluări

- T-MXONE-7.0-C1-IM v1.3Document403 paginiT-MXONE-7.0-C1-IM v1.3assav0% (1)

- MMCM VS PLLDocument1 paginăMMCM VS PLLVijay KumarÎncă nu există evaluări

- CS6703-Grid and Cloud ComputingDocument11 paginiCS6703-Grid and Cloud ComputingBharath Reddy Mannem100% (1)

- Trajectory Modification Considering Dynamic Constraints of Autonomous RobotsDocument6 paginiTrajectory Modification Considering Dynamic Constraints of Autonomous RobotsOswin SoÎncă nu există evaluări

- Position Weight MatrixDocument4 paginiPosition Weight MatrixAnonymous E4Rbo2sÎncă nu există evaluări

- RNSF Curs1Document51 paginiRNSF Curs1Radu Alin BurteaÎncă nu există evaluări

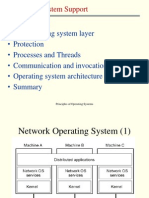

- Introduction: Operating System SupportDocument63 paginiIntroduction: Operating System SupportErmercado78Încă nu există evaluări

- Ball & Beam DocumentDocument8 paginiBall & Beam DocumentJorge PorrasÎncă nu există evaluări

- The 8284a Clock GeneratorDocument32 paginiThe 8284a Clock GeneratorBETHWEL KIPROTICH100% (1)

- Primii Pasi in Retelistica - InvataRetelisticaDocument54 paginiPrimii Pasi in Retelistica - InvataRetelisticaAdrian Anghel0% (1)

- Simple, Real-Time Obstacle Avoidance Algorithm For Mobile RobotsDocument6 paginiSimple, Real-Time Obstacle Avoidance Algorithm For Mobile RobotsStefania MihaiÎncă nu există evaluări

- 3.1.2 - IP Behavior I - FragmentationDocument41 pagini3.1.2 - IP Behavior I - FragmentationClaudio StroeÎncă nu există evaluări

- CRYPTOLOGYDocument8 paginiCRYPTOLOGYNur HayatiÎncă nu există evaluări

- Vxworks Vs RTLinuxDocument5 paginiVxworks Vs RTLinuxNithin RamakrishnaÎncă nu există evaluări

- Using LEGO NXT Mobile Robots With LabVIEW For Undergraduate Courses On MechatronicsDocument7 paginiUsing LEGO NXT Mobile Robots With LabVIEW For Undergraduate Courses On MechatronicsPravin BeheraÎncă nu există evaluări

- Vxworks Case StudyDocument11 paginiVxworks Case StudyPathella SudhakarÎncă nu există evaluări

- Study of DVMRP, MOSPF, CBT, PIM, MBONE, EIGRP, CIDRDocument6 paginiStudy of DVMRP, MOSPF, CBT, PIM, MBONE, EIGRP, CIDRnishiÎncă nu există evaluări

- Two Degrees of Freedom PID Control For Active Vibration Control of StructuresDocument9 paginiTwo Degrees of Freedom PID Control For Active Vibration Control of StructuresndjedouiÎncă nu există evaluări

- Role of IoT in EducationDocument4 paginiRole of IoT in EducationPondicherry UniversityÎncă nu există evaluări

- Hart Appguide PDFDocument156 paginiHart Appguide PDFealarconi7649Încă nu există evaluări

- Self Stabilized Platform PDFDocument4 paginiSelf Stabilized Platform PDFAnurag RanaÎncă nu există evaluări

- Multi-Core in JAVA/JVM: Concurrency Prior To Java 5: Synchronization and ThreadsDocument14 paginiMulti-Core in JAVA/JVM: Concurrency Prior To Java 5: Synchronization and ThreadsShravan KumarÎncă nu există evaluări

- ARP Tables Lookup AlgorithmsDocument3 paginiARP Tables Lookup AlgorithmsDouglas ManginiÎncă nu există evaluări

- VoIP - Voice Over IP On LinuxDocument11 paginiVoIP - Voice Over IP On LinuxWeb devÎncă nu există evaluări

- Toolbox PLUS Users Manual 3.11.0Document238 paginiToolbox PLUS Users Manual 3.11.0pyrodidoÎncă nu există evaluări

- Problem Solving With C++: The Object of ProgrammingDocument19 paginiProblem Solving With C++: The Object of ProgrammingomerqasÎncă nu există evaluări

- Embedded Operating SystemsDocument34 paginiEmbedded Operating SystemssanssecoursÎncă nu există evaluări

- Introducere in Matlab PDFDocument77 paginiIntroducere in Matlab PDFAlecs BalaÎncă nu există evaluări

- Internet of Things (IoT) Implementation in Learning Institutions - A Systematic Literature ReviewDocument48 paginiInternet of Things (IoT) Implementation in Learning Institutions - A Systematic Literature Reviewpecescd100% (1)

- Robust Face Recognition Under Difficult Lighting ConditionsDocument4 paginiRobust Face Recognition Under Difficult Lighting ConditionsijecctÎncă nu există evaluări

- How To Make Mobile Controlled Robot Using BluetoothDocument11 paginiHow To Make Mobile Controlled Robot Using BluetoothAvian WorkshopsÎncă nu există evaluări

- Conceptual Architecture of Mozilla FirefoxDocument14 paginiConceptual Architecture of Mozilla FirefoxKapil Aditani100% (1)

- CNN Project - GTSRB DatasetDocument4 paginiCNN Project - GTSRB DatasetMohamed ElHefnawy100% (2)

- Fuzzy Jerry M. MendelDocument2 paginiFuzzy Jerry M. MendelJuan Pablo Rodriguez HerreraÎncă nu există evaluări

- Vxworks For Pentium Architecture Supplement PDFDocument40 paginiVxworks For Pentium Architecture Supplement PDFNitesh SinghÎncă nu există evaluări

- Modbus Ethernet ManualDocument52 paginiModbus Ethernet ManualCarlos MercadoÎncă nu există evaluări

- Hart Driver ManualDocument119 paginiHart Driver ManualAntonio VerneÎncă nu există evaluări

- Information Systems Security LAB: RSA Cryptography AlgorithmDocument9 paginiInformation Systems Security LAB: RSA Cryptography AlgorithmAbdullah Al-HallakÎncă nu există evaluări

- TeslaSCADA IDE UserManualDocument459 paginiTeslaSCADA IDE UserManualIaros RodriguezÎncă nu există evaluări

- W11 Tutorial Solutions Chapter 13Document5 paginiW11 Tutorial Solutions Chapter 13mamnunbd100% (4)

- sbin/ifconfig Eth0 192.168.112.23 Netmask 255.255.255.0 Broadcast 192.168.0.255 IfconfigDocument5 paginisbin/ifconfig Eth0 192.168.112.23 Netmask 255.255.255.0 Broadcast 192.168.0.255 IfconfigIon CaimacanÎncă nu există evaluări

- Real Time Vehicle Tracking On Google Maps Using Raspberry Pi Web ServerDocument6 paginiReal Time Vehicle Tracking On Google Maps Using Raspberry Pi Web ServerEditor IJRITCCÎncă nu există evaluări

- HMI and SCADA SystemsDocument9 paginiHMI and SCADA SystemsFran JimenezÎncă nu există evaluări

- ASIMODocument16 paginiASIMOArun DineshÎncă nu există evaluări

- Intrebari ReteleDocument54 paginiIntrebari ReteleAnastasia SusciucÎncă nu există evaluări

- RTOS VxWorksDocument8 paginiRTOS VxWorksAshraful HimelÎncă nu există evaluări

- Introduction To Algorithms by Cormen: Special Features of BookDocument4 paginiIntroduction To Algorithms by Cormen: Special Features of BookAmit TiwariÎncă nu există evaluări

- ElGamal Signature SchemeDocument3 paginiElGamal Signature SchemeJibin PrasadÎncă nu există evaluări

- Wind River VxWorks Platform 6.9 - OverviewDocument3 paginiWind River VxWorks Platform 6.9 - OverviewciruvekofÎncă nu există evaluări

- IOT in Education FinalDocument8 paginiIOT in Education FinalAPS Fort Road100% (1)

- Switched Systems, Stability of Switched Systems in Sense of LyapunovDocument200 paginiSwitched Systems, Stability of Switched Systems in Sense of LyapunovMamdouh KhudaydusÎncă nu există evaluări

- ModTech2015 Program Book of AbstractsDocument293 paginiModTech2015 Program Book of AbstractsBuluc GheorgheÎncă nu există evaluări

- Host-Compiled Multicore RTOS Simulator For Embedded Real-Time Software DevelopmentDocument6 paginiHost-Compiled Multicore RTOS Simulator For Embedded Real-Time Software DevelopmentRey JohnÎncă nu există evaluări

- Threshold Voltage Modeling On Nanocrystalline Silicon Thin Film Transistors Navneet GuptaDocument5 paginiThreshold Voltage Modeling On Nanocrystalline Silicon Thin Film Transistors Navneet Guptanithin s gowdaÎncă nu există evaluări

- ECE 429 - Introduction To VLSI Design Fall 2015Document2 paginiECE 429 - Introduction To VLSI Design Fall 2015nithin s gowdaÎncă nu există evaluări

- Vedic MathsDocument8 paginiVedic Mathsnithin s gowda100% (1)

- GregoryDocument9 paginiGregorySalman AghaÎncă nu există evaluări

- CompaniesDocument1 paginăCompaniesnithin s gowdaÎncă nu există evaluări

- Nine Components of Mission Statement: Mohamed Adib Nazim Bin Mohd Yusoff AP160521Document3 paginiNine Components of Mission Statement: Mohamed Adib Nazim Bin Mohd Yusoff AP160521Adib NazimÎncă nu există evaluări

- CollegeApp DocumentationDocument165 paginiCollegeApp Documentationkalpesh khandelwalÎncă nu există evaluări

- SDLCDocument9 paginiSDLCTanmay JoshiÎncă nu există evaluări

- Sujeet's Milli Blog - 7 Lessons I Learnt During Facebook InternshipDocument7 paginiSujeet's Milli Blog - 7 Lessons I Learnt During Facebook InternshipRahul VenkatÎncă nu există evaluări

- Visual Controls: User GuideDocument32 paginiVisual Controls: User GuidejoseÎncă nu există evaluări

- General Elements of A C ProgramDocument6 paginiGeneral Elements of A C ProgramSundar GuyahÎncă nu există evaluări

- (INFO) ANDROID DEVICE PARTITIONS and FILESYSTEMS - XDA Developers ForumsDocument12 pagini(INFO) ANDROID DEVICE PARTITIONS and FILESYSTEMS - XDA Developers Forumssdancer75Încă nu există evaluări

- Managing Dataguard MonitoDocument4 paginiManaging Dataguard Monitomss5259Încă nu există evaluări

- Cs606 Advanced Database TechnologyDocument2 paginiCs606 Advanced Database TechnologyKarthik RlÎncă nu există evaluări

- Computer, Internet, Web, and EmailDocument48 paginiComputer, Internet, Web, and EmailAnil Penumacha50% (2)

- PDFDocument243 paginiPDFcjay100% (1)

- Address: 0x7e6f74e7Document1 paginăAddress: 0x7e6f74e7Tom ConnerÎncă nu există evaluări

- 20483B ENU TrainerHandbookDocument560 pagini20483B ENU TrainerHandbookLuis González Castro100% (3)

- 1.introduccion A CursoDocument10 pagini1.introduccion A Cursobelita1Încă nu există evaluări

- Chapter 1. Introduction To: C# ProgrammingDocument31 paginiChapter 1. Introduction To: C# ProgrammingJuan OrdoñezÎncă nu există evaluări

- Band in A Box 2009 ManualDocument511 paginiBand in A Box 2009 ManualAlexander WardÎncă nu există evaluări

- CHAPTER 4: Advanced Operations With Word: ObjectivesDocument29 paginiCHAPTER 4: Advanced Operations With Word: ObjectivesDiana EngalladoÎncă nu există evaluări

- Impact Analysis ChecklistDocument3 paginiImpact Analysis Checklistzuggo8485920% (1)

- Epicor9VantageVistaLabBook WednesdayDocument202 paginiEpicor9VantageVistaLabBook Wednesdayjhavrilla1Încă nu există evaluări

- ManualDocument319 paginiManualIván LassoÎncă nu există evaluări

- Linux BriefDocument3 paginiLinux BriefMohamed RamahÎncă nu există evaluări

- CEVA CI Brainware Admin Guide1.2Document27 paginiCEVA CI Brainware Admin Guide1.2Jorge CastellanosÎncă nu există evaluări

- imageRUNNER ADVANCE 5235 AGREGAR FONDOS DE PANTALLADocument9 paginiimageRUNNER ADVANCE 5235 AGREGAR FONDOS DE PANTALLAVelarde Antonio JoseÎncă nu există evaluări

- Secure NetworkDocument4 paginiSecure NetworkNirmalakumaran PrakalathanÎncă nu există evaluări

- Damage HUDDocument5 paginiDamage HUDAdrian Osorio RestrepoÎncă nu există evaluări

- RUTTER G2 VDR USB Data RecoveryDocument5 paginiRUTTER G2 VDR USB Data RecoveryAdi PrasetyoÎncă nu există evaluări

- Isabel MercadoDocument1 paginăIsabel MercadoSyed Zahid KhadriÎncă nu există evaluări

- Dcsea LZ Ais Velo12f01 2022 07 29Document155 paginiDcsea LZ Ais Velo12f01 2022 07 29ChandrahasÎncă nu există evaluări

- Hexagon PC Dmis 02 - Navigating The User InterfaceDocument32 paginiHexagon PC Dmis 02 - Navigating The User InterfacenalbanskiÎncă nu există evaluări

- AU All CodeDocument7 paginiAU All CodeJohnMiresÎncă nu există evaluări

- ChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessDe la EverandChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessÎncă nu există evaluări

- Fundamentals of Data Engineering: Plan and Build Robust Data SystemsDe la EverandFundamentals of Data Engineering: Plan and Build Robust Data SystemsEvaluare: 5 din 5 stele5/5 (1)

- Excel 2023 for Beginners: A Complete Quick Reference Guide from Beginner to Advanced with Simple Tips and Tricks to Master All Essential Fundamentals, Formulas, Functions, Charts, Tools, & ShortcutsDe la EverandExcel 2023 for Beginners: A Complete Quick Reference Guide from Beginner to Advanced with Simple Tips and Tricks to Master All Essential Fundamentals, Formulas, Functions, Charts, Tools, & ShortcutsÎncă nu există evaluări

- ChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveDe la EverandChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveÎncă nu există evaluări

- Python for Beginners: A Crash Course Guide to Learn Python in 1 WeekDe la EverandPython for Beginners: A Crash Course Guide to Learn Python in 1 WeekEvaluare: 4.5 din 5 stele4.5/5 (7)

- Sweet Spot UX: Communicating User Experience to Stakeholders, Decision Makers and Other HumansDe la EverandSweet Spot UX: Communicating User Experience to Stakeholders, Decision Makers and Other HumansEvaluare: 4.5 din 5 stele4.5/5 (5)

- Microsoft Outlook Guide to Success: Learn Smart Email Practices and Calendar Management for a Smooth Workflow [II EDITION]De la EverandMicrosoft Outlook Guide to Success: Learn Smart Email Practices and Calendar Management for a Smooth Workflow [II EDITION]Evaluare: 5 din 5 stele5/5 (4)

- Microsoft Excel Guide for Success: Transform Your Work with Microsoft Excel, Unleash Formulas, Functions, and Charts to Optimize Tasks and Surpass Expectations [II EDITION]De la EverandMicrosoft Excel Guide for Success: Transform Your Work with Microsoft Excel, Unleash Formulas, Functions, and Charts to Optimize Tasks and Surpass Expectations [II EDITION]Evaluare: 5 din 5 stele5/5 (3)

- Optimizing DAX: Improving DAX performance in Microsoft Power BI and Analysis ServicesDe la EverandOptimizing DAX: Improving DAX performance in Microsoft Power BI and Analysis ServicesÎncă nu există evaluări

- Agile Project Management: Scrum for BeginnersDe la EverandAgile Project Management: Scrum for BeginnersEvaluare: 4 din 5 stele4/5 (7)

- Designing Data-Intensive Applications: The Big Ideas Behind Reliable, Scalable, and Maintainable SystemsDe la EverandDesigning Data-Intensive Applications: The Big Ideas Behind Reliable, Scalable, and Maintainable SystemsEvaluare: 5 din 5 stele5/5 (6)

- Microservices Patterns: With examples in JavaDe la EverandMicroservices Patterns: With examples in JavaEvaluare: 5 din 5 stele5/5 (2)

- Microsoft PowerPoint Guide for Success: Learn in a Guided Way to Create, Edit & Format Your Presentations Documents to Visual Explain Your Projects & Surprise Your Bosses And Colleagues | Big Four Consulting Firms MethodDe la EverandMicrosoft PowerPoint Guide for Success: Learn in a Guided Way to Create, Edit & Format Your Presentations Documents to Visual Explain Your Projects & Surprise Your Bosses And Colleagues | Big Four Consulting Firms MethodEvaluare: 5 din 5 stele5/5 (4)

- Computer Science Beginners Crash Course: Coding Data, Python, Algorithms & HackingDe la EverandComputer Science Beginners Crash Course: Coding Data, Python, Algorithms & HackingEvaluare: 3.5 din 5 stele3.5/5 (12)

- Microsoft Teams Guide for Success: Mastering Communication, Collaboration, and Virtual Meetings with Colleagues & ClientsDe la EverandMicrosoft Teams Guide for Success: Mastering Communication, Collaboration, and Virtual Meetings with Colleagues & ClientsEvaluare: 5 din 5 stele5/5 (4)

- Learn Power BI: A beginner's guide to developing interactive business intelligence solutions using Microsoft Power BIDe la EverandLearn Power BI: A beginner's guide to developing interactive business intelligence solutions using Microsoft Power BIEvaluare: 5 din 5 stele5/5 (1)

- Microsoft Word Guide for Success: From Basics to Brilliance in Achieving Faster and Smarter Results [II EDITION]De la EverandMicrosoft Word Guide for Success: From Basics to Brilliance in Achieving Faster and Smarter Results [II EDITION]Evaluare: 5 din 5 stele5/5 (4)

- Kubernetes: The Updated Guide to Master Kubernetes for EveryoneDe la EverandKubernetes: The Updated Guide to Master Kubernetes for EveryoneEvaluare: 3 din 5 stele3/5 (3)

- Artificial Intelligence in Practice: How 50 Successful Companies Used AI and Machine Learning to Solve ProblemsDe la EverandArtificial Intelligence in Practice: How 50 Successful Companies Used AI and Machine Learning to Solve ProblemsEvaluare: 4.5 din 5 stele4.5/5 (38)

- Scrum: Understanding Scrum at a Deeper Level and Mastering Agile Project ManagementDe la EverandScrum: Understanding Scrum at a Deeper Level and Mastering Agile Project ManagementEvaluare: 3.5 din 5 stele3.5/5 (2)

- Notion for Beginners: Notion for Work, Play, and ProductivityDe la EverandNotion for Beginners: Notion for Work, Play, and ProductivityEvaluare: 4 din 5 stele4/5 (8)

- Creating Online Courses with ChatGPT | A Step-by-Step Guide with Prompt TemplatesDe la EverandCreating Online Courses with ChatGPT | A Step-by-Step Guide with Prompt TemplatesEvaluare: 4 din 5 stele4/5 (4)

- Excel Formulas That Automate Tasks You No Longer Have Time ForDe la EverandExcel Formulas That Automate Tasks You No Longer Have Time ForEvaluare: 5 din 5 stele5/5 (1)

- The Product Momentum Gap: Bringing together product strategy and customer valueDe la EverandThe Product Momentum Gap: Bringing together product strategy and customer valueEvaluare: 5 din 5 stele5/5 (1)

![Microsoft Outlook Guide to Success: Learn Smart Email Practices and Calendar Management for a Smooth Workflow [II EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728320983/198x198/d544db3174/1715431173?v=1)

![Microsoft Excel Guide for Success: Transform Your Work with Microsoft Excel, Unleash Formulas, Functions, and Charts to Optimize Tasks and Surpass Expectations [II EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318885/198x198/86d097382f/1715431156?v=1)

![Microsoft Word Guide for Success: From Basics to Brilliance in Achieving Faster and Smarter Results [II EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728320756/198x198/6f19793d5e/1715431125?v=1)