Documente Academic

Documente Profesional

Documente Cultură

Anna University, Chennai-25 Practical Examination: College Programee Semester: 06 Subject

Încărcat de

touchsatheeshTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Anna University, Chennai-25 Practical Examination: College Programee Semester: 06 Subject

Încărcat de

touchsatheeshDrepturi de autor:

Formate disponibile

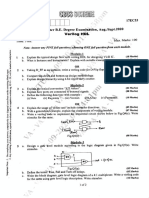

ANNA UNIVERSITY, CHENNAI-25 PRACTICAL EXAMINATION

College

: 135: VELTECH

Programee Subject

: B.E ECE

Semester : 06 LAB Date of Exam : 16, 17.04.2012

: EC2357 VLSI Design

SET II QUESTION PAPER

1. (a) Write a verilog code for Accumulator and write the test bench for the same. (b). Draw a layout for logic circuit .Which do the addition operation and show the spice code the circuit. 2. (a) Write the verilog code Demultiplexing & show P&R , Post P&R simulation and download it to FPGA kit.

(b) Draw a layout for and gate and Show the spice code for the layout. 3. (a) Write a verilog code for the priority encoder,Write the test bench for the code and finally download it to FPGA kit. (b) Design a layout ,which performs the complement of multiplication operation and show the spice code for the layout. 4. (a) Write a verilog code for the flipflop .Which has the letter from the word Rain & Shadow .explain the concept of concurrent sequential execution and show P&R, Post P&R simulation. (b) Design a layout for the NOT gate and show the spice code for it. 5. (a) Write a verilog code for a Flip flop which has a letter from the word Jack & King and show the floor planning, boundary scan for the circuit . Finally implement it in spartan kit.

(b) Design a layout which performs compliment of Addition operation and show the spice code for it.

6. (a) Write a verilog code for Pseudo Random binary sequence generator.Explain the concept of concurrent & sequential execution and show the P&R, Post P&R simulation. (b) Design a oscillator circuit to control the voltage and show the spice code for it. 7. (a) write a verilog code for a flipflop which toggles for that explain the concept of concurrent & sequential execution. (b) Design a schematic circuit for n-bit voltage controlled oscillator. 8. (a) Write a verilog code for a flipflop which delays the signal .show out put in the Spartan kit. (b) Show the automatic layout generation for 10-bit voltage controlled oscillator. 9. (a) Write a verilog code Adder circuit which has two input pin and one carry pin .Explain the concept of concurrent &sequential execution and write the test bench codes. (b) Draw a schematic circuit for the circuit which performs the complement operation and extract the code from the circuit. 10. (a) Write a verilog code for 4-bit Multiplier and should be implemented in FPGA kit. (b) Design differential amplifier circuit to show gain, bandwidth & CMMR 11. (a) Write code for multiplexer using binary operator. Show the output in the FPGA kit. (b) Draw a layout for complement circuit and show the spice code for it. 12. (a) Write the verilog code Address decoder and show the floor plan. (b) Design a Differential Amplifier and Determine the gain,bandwidth and CMRR.

13. (a) Write a Verilog Code for Full Subractor using case statement. (b) Show Automatic Layout Generation for N-bit VCO . 14. (a) Write a Verilog Code for Full Adder by instantiating two Half adder and download it to a FPGA kit. (b) Draw the layout for multiplication gate and extract the p-spice code for the same. 15. (a)Write a verilog code for 4-bit multiplier with two inputs and write the test bench for the same. (b) Design a layout for NOT gate using tanner and show the simulation output. 16. (a)Write a code for 8-bit adder & Implement it in FPGA kit. (b) Draw a layout for NOT gate and Show the spice code for it. 17. (a) Write a code for multiplying two 4-bit values and write a test bench code for the same . Highlight the concept of concurrent of sequential execution. (b)Design a circuit to verify gain, bandwidth &Output impedance. 18. (a) Write a code for decoding the binary values and explain P&R , Post P&R simulation.Finaly implement it in FPGA kit. (b) Design a VLSI circuit to derive the gain, Bandwidth and CMMR. 19. (a) Write a code for multiplexing the binary values .Show the floor planning for the design and implement it in FPGA kit. (b) Design a 10-bit voltage controlled oscillator and show the corresponding output for it. 20. (a) Write the code for synchronous counter and implement it in FPGA kit. (b) Show the automatic layout generation for 10-bit voltage controlled oscillator.

Internal Examiner

External Examiner

S-ar putea să vă placă și

- HDLQBDocument2 paginiHDLQBmanjula u rÎncă nu există evaluări

- Lab COE-II List of ExperimentsDocument1 paginăLab COE-II List of ExperimentsHarshil AmbagadeÎncă nu există evaluări

- DEC Lab Experiments - 2017aDocument5 paginiDEC Lab Experiments - 2017aManjeet SinghÎncă nu există evaluări

- 07a80405 DigitaldesignthroughverilogDocument4 pagini07a80405 DigitaldesignthroughverilogSharanya ThirichinapalliÎncă nu există evaluări

- Vlsi Lab Manua2Document75 paginiVlsi Lab Manua2Nandan Bm100% (1)

- 9A04706 Digital Design Through Verilog HDL PDFDocument4 pagini9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumÎncă nu există evaluări

- Electronic CircuitsDocument2 paginiElectronic CircuitsYashu GowdaÎncă nu există evaluări

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document3 paginiAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalÎncă nu există evaluări

- Mahendra Engineering Collge Mahendrapuri, Namakkal-637503: Sum of A Given Series With and Without CarryDocument2 paginiMahendra Engineering Collge Mahendrapuri, Namakkal-637503: Sum of A Given Series With and Without CarryJ.Gowri ShankarÎncă nu există evaluări

- VLSI LAB Manual 2014 PDFDocument67 paginiVLSI LAB Manual 2014 PDFraghvendrmÎncă nu există evaluări

- Digital Design Through Verilog HDLDocument4 paginiDigital Design Through Verilog HDLmukesh_sonuÎncă nu există evaluări

- DLDM Question BankDocument8 paginiDLDM Question BankMayur PatilÎncă nu există evaluări

- Experiment 6 (EE381A DCMP Lab. 2021-2022/II) : ObjectivesDocument2 paginiExperiment 6 (EE381A DCMP Lab. 2021-2022/II) : ObjectivesAditya SinghÎncă nu există evaluări

- Question Bank For Vlsi LabDocument4 paginiQuestion Bank For Vlsi LabSav ThaÎncă nu există evaluări

- Vlsi Lab Manual (18ecl77) - 2022-23Document226 paginiVlsi Lab Manual (18ecl77) - 2022-23Prajwal KoppaÎncă nu există evaluări

- VLSI Lab Bank QUESTIONDocument3 paginiVLSI Lab Bank QUESTIONdeekshamb01052001Încă nu există evaluări

- CS6211 Set3 PDFDocument3 paginiCS6211 Set3 PDFDhivya Dhanalakshmi ECEÎncă nu există evaluări

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 paginiEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniÎncă nu există evaluări

- 10ECL47 MICROCONTROLLER Lab ManualDocument142 pagini10ECL47 MICROCONTROLLER Lab ManualVishalakshi B HiremaniÎncă nu există evaluări

- Xilinx Lab RecordDocument76 paginiXilinx Lab RecordDivya SantoshiÎncă nu există evaluări

- Question Bank VLSI LABDocument3 paginiQuestion Bank VLSI LABPraveen AndrewÎncă nu există evaluări

- 637862647808605476ece 18ecl77 E1s1 PPTDocument37 pagini637862647808605476ece 18ecl77 E1s1 PPTSiddu UmaraniÎncă nu există evaluări

- VLSI & Embedded Systems Lab ManualDocument137 paginiVLSI & Embedded Systems Lab Manualganga avinash reddyÎncă nu există evaluări

- Lab ManualDocument78 paginiLab Manualgurusandhya11Încă nu există evaluări

- New Final Ae2406Document2 paginiNew Final Ae2406Jessica CarterÎncă nu există evaluări

- De University QuestionDocument16 paginiDe University Questionselvi0412Încă nu există evaluări

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxDe la EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxEvaluare: 4 din 5 stele4/5 (2)

- Digital System Design Using Verilog December 2011Document1 paginăDigital System Design Using Verilog December 2011Vinayaka HmÎncă nu există evaluări

- M.E Adsd Question PaperDocument2 paginiM.E Adsd Question PapershankarÎncă nu există evaluări

- VLSI Record 2022-23Document77 paginiVLSI Record 2022-23MANOJÎncă nu există evaluări

- Sub Code & Name: Ec2207 Digital Electronics Lab Semester: Iii DATE: 29.10.12-31.10.12Document4 paginiSub Code & Name: Ec2207 Digital Electronics Lab Semester: Iii DATE: 29.10.12-31.10.12Dewayne RogersÎncă nu există evaluări

- DLD Lab 2Document20 paginiDLD Lab 2Abdulrehman HabibÎncă nu există evaluări

- Ec8361-19 3Document3 paginiEc8361-19 3MaheswariÎncă nu există evaluări

- VTU Question PapersDocument12 paginiVTU Question PapersQwertyÎncă nu există evaluări

- Ee2356 MP and MC Lab Set 1Document2 paginiEe2356 MP and MC Lab Set 1Arul MuruganÎncă nu există evaluări

- Exercise of FPGA-Based Digital System Design: The BPSK ModulatorDocument3 paginiExercise of FPGA-Based Digital System Design: The BPSK ModulatorĐặng Hoài SơnÎncă nu există evaluări

- HDL Manual 2019 5th Sem E&CE 17ECL58Document77 paginiHDL Manual 2019 5th Sem E&CE 17ECL58vishvakirana100% (1)

- Cisco: Question & AnswersDocument65 paginiCisco: Question & AnswersDomainci BabaÎncă nu există evaluări

- VLSI Lab Experiment ListDocument2 paginiVLSI Lab Experiment ListShivam SanwariaÎncă nu există evaluări

- Department of Electronics & Communication Engineering.: Question BankDocument4 paginiDepartment of Electronics & Communication Engineering.: Question BankRamachandra TurkaniÎncă nu există evaluări

- DD Lab Expt 2Document9 paginiDD Lab Expt 2Umang goelÎncă nu există evaluări

- Question Paper Code:: (10 2 20 Marks)Document2 paginiQuestion Paper Code:: (10 2 20 Marks)AbdulAzizÎncă nu există evaluări

- Ade SyllDocument1 paginăAde SyllVijay GuruÎncă nu există evaluări

- Question BankDocument4 paginiQuestion BankChetan GowdaÎncă nu există evaluări

- 5.2.3.7 Lab - Configuring Port Address Translation (PAT) - ILM PDFDocument12 pagini5.2.3.7 Lab - Configuring Port Address Translation (PAT) - ILM PDFShelton Siziba100% (1)

- Verilog LabDocument70 paginiVerilog Labhkes rcrÎncă nu există evaluări

- 06 CSL38 Manual LDDocument68 pagini06 CSL38 Manual LDSwathi N SudarshanÎncă nu există evaluări

- Ece CDocument70 paginiEce CSri SandhiyaÎncă nu există evaluări

- 9A04504 Digital IC ApplicationsDocument4 pagini9A04504 Digital IC ApplicationssivabharathamurthyÎncă nu există evaluări

- QP Eee 22 May2010 LdicaDocument6 paginiQP Eee 22 May2010 LdicaHari PrasadÎncă nu există evaluări

- Lab - View Network Device MAC Addresses: TopologyDocument6 paginiLab - View Network Device MAC Addresses: TopologynujugtrÎncă nu există evaluări

- Task 1Document23 paginiTask 1Eren YeagerÎncă nu există evaluări

- Ug Vlsi Design LabDocument2 paginiUg Vlsi Design LabvlsijpÎncă nu există evaluări

- T.E. (Electrical) (Semester - I) Examination, 2014 Advanced Microcontroller and Its Applications (2012 Course)Document2 paginiT.E. (Electrical) (Semester - I) Examination, 2014 Advanced Microcontroller and Its Applications (2012 Course)DevarshWaliÎncă nu există evaluări

- H.D.L - Lab: For IV Semester B.EDocument76 paginiH.D.L - Lab: For IV Semester B.EvijaykannamallaÎncă nu există evaluări

- ECE 2003 ManualDocument79 paginiECE 2003 Manualannambaka satishÎncă nu există evaluări

- Dec 2009Document8 paginiDec 2009Viswa ChaitanyaÎncă nu există evaluări

- Peri Institute of Tecchnology ORDocument1 paginăPeri Institute of Tecchnology ORkumar_9583Încă nu există evaluări

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDe la EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemÎncă nu există evaluări

- Design of 32-Bit Risc Processor and Efficient VerificationDocument6 paginiDesign of 32-Bit Risc Processor and Efficient VerificationPallavi DikshitÎncă nu există evaluări

- Altera Soc Golden System Reference Design User Guide: Subscribe FeedbackDocument31 paginiAltera Soc Golden System Reference Design User Guide: Subscribe FeedbackusseerrÎncă nu există evaluări

- What Xilinx Xc6slx45-2fgg484i FpgaDocument14 paginiWhat Xilinx Xc6slx45-2fgg484i FpgajackÎncă nu există evaluări

- 5 Fpga Timing PDFDocument40 pagini5 Fpga Timing PDFdimen100Încă nu există evaluări

- Study Oriented Project - MTech RBL Guidance ListDocument6 paginiStudy Oriented Project - MTech RBL Guidance ListHIMANSHU YADAVÎncă nu există evaluări

- Programmable Asics 4: The AntifuseDocument12 paginiProgrammable Asics 4: The AntifuseVivek100% (2)

- Spartan-6 FPGA Data SheetDocument89 paginiSpartan-6 FPGA Data SheetfcikanÎncă nu există evaluări

- Gps VHDLDocument69 paginiGps VHDLmohan4630% (1)

- EE 668: System Design: Madhav P. Desai January 18, 2011Document3 paginiEE 668: System Design: Madhav P. Desai January 18, 2011Chiquita WhiteÎncă nu există evaluări

- (NEW) Prepaid Electricity Billing IEEE 2014Document4 pagini(NEW) Prepaid Electricity Billing IEEE 2014HarshalÎncă nu există evaluări

- Xilinx Virtex6 Pin DetailsDocument94 paginiXilinx Virtex6 Pin DetailsArun VeluÎncă nu există evaluări

- FPGA Implementation of Adaptive Filtering Algorithms For Noise Cancellation-A Technical SurveyDocument10 paginiFPGA Implementation of Adaptive Filtering Algorithms For Noise Cancellation-A Technical SurveyJabran SafdarÎncă nu există evaluări

- Rzeszut Osciloscope MAM 1 2018Document3 paginiRzeszut Osciloscope MAM 1 2018CarlosReisÎncă nu există evaluări

- Ground Bounce: (And It's Dual, V Bounce)Document31 paginiGround Bounce: (And It's Dual, V Bounce)9844352836Încă nu există evaluări

- Computer Architecture Final 1 2022Document2 paginiComputer Architecture Final 1 2022Omar EssamÎncă nu există evaluări

- MNL Avalon SpecDocument59 paginiMNL Avalon SpecAlexis Jonathan Bautista BaqueroÎncă nu există evaluări

- Zynq-7000 Ap Soc and 7 Series Devices Memory Interface Solutions (V4.0)Document13 paginiZynq-7000 Ap Soc and 7 Series Devices Memory Interface Solutions (V4.0)Evrim AltanÎncă nu există evaluări

- Pre Ph.D. Electronics and Communication EnggDocument49 paginiPre Ph.D. Electronics and Communication EnggKavita KamerikarÎncă nu există evaluări

- Cortex Resource Guide 2010Document116 paginiCortex Resource Guide 2010VănThịnhÎncă nu există evaluări

- ModelSim Testbenches VerilogDocument22 paginiModelSim Testbenches VerilogOluwatimileyin Michael OlagunjuÎncă nu există evaluări

- Labview Fpga ModuleDocument5 paginiLabview Fpga Modulevanhai_hvktqs41Încă nu există evaluări

- Christophe Bobda-Introduction To Reconfigurable Computing - Architectures, Algorithms and Applications (2007)Document375 paginiChristophe Bobda-Introduction To Reconfigurable Computing - Architectures, Algorithms and Applications (2007)Vittalbc ChikkalakiÎncă nu există evaluări

- Using Block Ram For High Performance Read/Write Cams: Cam16X8 MacroDocument19 paginiUsing Block Ram For High Performance Read/Write Cams: Cam16X8 MacroHariPrasanth GovindarajuÎncă nu există evaluări

- A Fpga Based Solution To LCD Digital Automobile DashDocument5 paginiA Fpga Based Solution To LCD Digital Automobile DashsrikanthshenoyÎncă nu există evaluări

- Placement YogaDocument205 paginiPlacement YogaBack IncÎncă nu există evaluări

- Syllabus of B.E. (Electronics and Computer)Document46 paginiSyllabus of B.E. (Electronics and Computer)4th2001Încă nu există evaluări

- Design and Implementation of 2 Bits BCH Error Correcting Codes Using FPGADocument7 paginiDesign and Implementation of 2 Bits BCH Error Correcting Codes Using FPGAJournal of TelecommunicationsÎncă nu există evaluări

- Field Programmable Gate Array (FPGA)Document17 paginiField Programmable Gate Array (FPGA)Arsalan HabibÎncă nu există evaluări

- Introduction To Embedded SystemV4Document89 paginiIntroduction To Embedded SystemV4amr083021Încă nu există evaluări

- CTS-7700 Service Manual PDFDocument109 paginiCTS-7700 Service Manual PDFvasquezbencomo100% (1)