Documente Academic

Documente Profesional

Documente Cultură

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates For Low Power Industrial Applications

Încărcat de

Pradeep SinglaTitlu original

Drepturi de autor

Formate disponibile

Partajați acest document

Partajați sau inserați document

Vi se pare util acest document?

Este necorespunzător acest conținut?

Raportați acest documentDrepturi de autor:

Formate disponibile

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates For Low Power Industrial Applications

Încărcat de

Pradeep SinglaDrepturi de autor:

Formate disponibile

REVERSIBLE PROGRAMMABLE LOGIC ARRAY (RPLA) USING FEYNMAN & MUX GATES FOR LOW POWER INDUSTRIAL APPLICATION

Pradeep Singhla, Hindu College of Engineering, Sonipat, Haryana, India pardeep51355@gmail.com Naveen Kumar Malik, Hindu College of Engineering, Sonipat, Haryana, India naveenmalik4u@gmail.com ABSTRACT This paper present the research work directed towards the design of reversible programmable logic array using very high speed integrated circuit hardware description language (VHDL). Reversible logic circuits have significant importance in bioinformatics, optical information processing, CMOS design etc. In this paper the authors propose the design of new RPLA using Feynman & MUX gate. VHDL based codes of reversible gates with simulating results are shown .This proposed RPLA may be further used to design any reversible logic function or Boolean function (Adder, Subtractor etc.) which dissipate very low or ideally no heat. Keywords: Reversible logic, quantum cost, garbage outputs, RPLA, constant inputs, VHDL INTRODUCTION Todays Electronic systems becomes important part of the humans life and engineers wants that the system should have high performance, speed and dissipate very low or ideally no heat. Still the power dissipation is one of the greatest limitation factors in these electronic systems. The digital systems designed by the conventional approach or irreversible design approach consume or dissipate KTln2 of energy on every bit computation (R. Lndauer, 1961). Where K is a Boltzmanns constant equals to 1.3807 J and T is the temperature at which the computation is performed..The dissipated energy directly correlated to the number of lost bits (C. H. Bennet, 1973). Resultantly, a new design approach has been comes in the hardware designing field for reducing the power dissipation known reversible logic structure possesd the property of one to one mapping between the inputs and output state (H. R. Bhagyalakshmi, et al., 2010). Reversible logics have very useful applications in everyday life like Laptop computers, wearable computers, spacecraft, smart cards etc (Michael P. Frank, 2005). So, in a new paradigm in computer design, reversible logics play a very important role over irreversible logics. The non-reversible PLA structure may be used to realize the reversible functions (Ahsan Raja, et al., 2006). Programming Logic Devices (PLDs) or Arrays (PLAs) are used in industrial applications to synthesis cost effective solutions to industrial designs (Hamid R. Arabnia, et al., 2006). The PLA designed using reversible gates is called RPLA. The authors seeing the benefits of programmable logic array design approach in industrial application designed new RPLA using reversible gates i.e. Feynman gate & Mux gate. This device can be changed at any time to perform any number of reversible Boolean functions. The proposed new architecture of RPLA has three inputs which can perform logical functions. The organization of paper as follows: the overview of reversible logic gate is explained first then the various reversible gates used in design are explained. In next the proposed architecture of RPLA is shown. Further, the design of 3 input RPLA with VHDL codes of Feynman & MUX gate with RTL view of Reversible AND plane & Reversible OR plane discussed and shown. The experimental results of Reversible AND plane & Reversible OR plane are shown. Finally Sum up the paper with conclusion and explores the future scopes and enlist the references.

OVERVIEW OF REVERSIBLE LOGIC

ICIAICT 2012 411 ISBN 978-93-81583-34-0

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

The idea of reversible computing comes from the thermodynamics which taught us the benefits of the reversible process over irreversible process. So, a computation is called reversible if its inputs can always be retrieved from its outputs (H. R. Bhagyalakshmi, et al., 2010). But reversible means not only logically reversibility in the circuit but also physical reversibility must be there. Logical reversibility implies that the number of inputs must equal to the outputs (G. De Mey, et al., 2008). In other words, these circuits can generate unique output vector from each input vector and vice-versa. So, an NN reversible gate can be represented as (Ahsan Raja, et al., 2006). ) ) Where input vectors = output vectors When a device can actually run backwards then it is called physically reversible and the second law of thermodynamics guarantees that it dissipates no heat. In this paper, we implement the RPLA by taking the case of logically reversibility. So, we only consider the logical reversibility part because this is the elementary idea which gave rise to a research area about reversible computing (G. De Mey, et al., 2008). For logical reversibility in the digital logics there are two conditions as follows (H. R. Bhagyalakshmi, et al., 2010). Fan-Out is not permitted Feedback is not permitted Some of the important and main measure in designing of the reversible logic circuits are QC (Quantum cost) (H. R. Bhagyalakshmi, et al., 2010): The number of reversible gates (11 or 22) to realize the circuit is known as quantum cost, (CI) Constant inputs (H. R. Bhagyalakshmi, et al., 2010): The number of inputs that are kept constant (0 or 1) for synthesis the given functions, GO (Garbage outputs) (H. R. Bhagyalakshmi, et al., 2010): The number of outputs that are not primary is known as Garbagr outputs Reversible Gates: There is several reversible logic gates have been proposed in the last years such as: Feynman gate (H. R. Bhagyalakshmi, et al., 2010), Fredkin gate (Ahsan Raja, et al., 2006), Peres gate (T. Toffoli, 1980), Toffolli gate (T. Toffoli, 1980), new gate (H. R. Bhagyalakshmi, et al., 2010), Mux gate (Sajib Kumar Mitra, et al., 2011) etc. Here we are reviewing the three gates i. e. Feynman, Fredkin and MUX gate because these gates are used in the designing of the RPLA. Fredkin Gate (Ahsan Raja, et al., 2006): Fredkin Gate is a 33 conservative reversible gate. It is called 33 gate because it has three inputs and three outputs. The inputs (A, B, C associates with its outputs outputs (P, Q, R).Its quantum cost is 5.

A FRG

P=A

B C

Q=A'B XOR AC R=A'C XOR AB

Figure 1: Fredkin Gate

1st International Conference on Innovations and Advancements in Information and Communication Technology 412

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

MUX Gate (Sajib Kumar Mitra, et al., 2011): Figure 2 shows the pictorial representation of 33 reversible gate called MUX (MG) Gate. It is a conservative gate havig three inputs (A, B, C) and three outputs (P, Q, R). The outputs are defined by P=A, Q=A XOR B XOR C and R= AC XOR AB. The hamming weight of its input vector is same as the hamming weight of its output vector and its Quantum cost is 4.

A B C MG

P=A Q=A XOR B XOR C R=A'C XOR AB

Figure 2: 33 MUX Gate MUX Gate as AND Gate and OR Gate: The structure of MUX Gate as AND Gate and OR Gate is shown in the Figure 2.1 and Figure 2.2. If we provide 0 at third input C then the output R will provide the AND combination of first & second input and if we If we provide 1 at second input B then the output Q will provide the OR combination of the first & third input.

A MG

MG

Q=A+C

R=AB

Figure 2.1: MUX gate as AND gate

Figure 2.2: MUX gate as OR gate

Feynman Gate (H. R. Bhagyalakshmi, et al., 2010): Figure 3 shows the 22 reversible gate called Feynman gate. Feynman gate is also recognized as controlled- not gate (CNOT). It has two inputs (A, B) and two outputs (P, Q). The outputs are defined by P=A, Q=A XOR B .This gate can be used to copy a signal. Since fan-out is not allowed in reversible logic circuits, the Feynman gate is used as the fan-out gate to copy a signal. Quantum cost of a Feynman gate is 1.

A Feynman Gate B Q=A XOR B P=A

Figure 3: 22 Feynman Gate Structure Feynman Gate as Data Copier & as NOT Gate (H. R. Bhagyalakshmi, et al., 2010): The structure of Feynman gate as Data Copier & as NOT gate is shown in the Figure 3.1 and Figure 3.2 respectively. If we provide 0 at second input B then the output Q will provide the copy of first input and if we If we provide 1 at second input B then the output Q will provide the complement of the first input.

1st International Conference on Innovations and Advancements in Information and Communication Technology 413

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

A Feynman Gate 0

A Feynman Gate

A'

Figure 3.1: Feynman Gate as Data Copier

Figure 3.2: Feynman Gate as NOT Gate

PROPOSED ARCHITECTURE OF NEW RPLA: The RPLA consist of AND plane with buffers/inverters, each of which can be programmed to generate some product terms of input variable combinations with OR plane to realize the output functions. The block representation of RPLA is shown in Figure 4.

n- Inputs

ReversibleAND Plane (Feynman & MUX gate)

K- Product terms Reversible OR Plane(MUX gate) m Outputs

RPLA

Figure 4: Schamatic Block Diagram of New RPLA In this architecture, we used n numbers of inputs and getting m numbers of outputs as in conventional PLA. In the complete structure of the RPLA there are two planes i.e. reversible AND plane & Reversible OR plane. METHODOLOGY The existing methodology which was proposed by (Himanshu Thapliyal, et al., 2006) which uses the two gates for the design i.e. Feynman & Fredkin gate (Himanshu Thapliyal, et al., 2006). We propose new methodology for design of RPLA in this paper by using Feynman & MUX gate. The new methodology

1st International Conference on Innovations and Advancements in Information and Communication Technology 414

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

uses the new gate i.e. MUX gate (Sajib Kumar Mitra, et al., 2011 having lower quantum cost as compare to the fredkin gate, so by replacing the fredkin gate by the MUX gate the total quantum cost of RPLA decreases. For the designing purpose we use the VHDL and simulate on the xilinx 8.2i. VHDL Description: This is the language Designed by IBM, Texas Instruments, and Intermetrics as part of the DoD funded VHSIC program and Standardized by the IEEE in 1987: IEEE 1076-1987. Its enhanced version of the defined in 1993: IEEE 1076-1993 (J. Bhasker). The VHDL stands for the very high speed integrated circuit hardware description language having three kinds of modeling i.e. Behavioral Modeling, Structural modeling and Dataflow modeling. For implementing any of the design we go through the following steps (J. Bhasker) as shown in Figure 5. Requirements Functional Design- Behavioral Simulation

Register TransferLevel Design -RTL Simulation Validation

Logic Design- -Logic Simulation Verification

Circuit Design-Timing SimulationCircuit Analysis

Physical Design-Design Rule Checking Figure 5: Basic Flow Steps of a simple Digital design through VHDL The proposed design of RPLA uses MUX gate & Feynman gate. The VHDL codes of MUX gate & Feynman gate design in Behavioral modeling are as follows: VHDL Codes for MUX gate Library IEEE; Use ieee.std_logic_1164.all; Use ieee.numeric_std.all; Entity MG3 is Port (IN1: in STD_LOGIC; IN2: in STD_LOGIC; IN3: in STD_LOGIC; OUT1: out STD_LOGIC; OUT2: out STD_LOGIC; OUT3: out STD_LOGIC); End MG3; Architecture Behavioral of MG3 is Begin OUT1<= IN1; OUT2<=IN1 xor IN2 xor IN3;

1st International Conference on Innovations and Advancements in Information and Communication Technology 415

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

OUT3<= (((NOT IN1) and IN3) xor (IN1 and IN2)); End behavioral; VHDL Codes for Feynman gate library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity FY2 is port(IN1:in STD_LOGIC; IN2:in STD_LOGIC; OUT1:out STD_LOGIC; OUT2:out STD_LOGIC); end FY2; architecture behavior of FY2 is begin OUT1<=IN1; OUT2<=IN1 xor IN2; End behavior; In our research, we define the individual behavior of every gate and then by structural modeling we connect all the output of the previous stage to the next stage by port mapping, assigning them the signal then from the VHDL code the RTL view if AND plane and RTL view of OR plane are generated .These are shown as Figure 6 and Figure 7 respectively.

1st International Conference on Innovations and Advancements in Information and Communication Technology 416

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

Figure 6: RTL Schamatic of AND Plane

Figure 7: RTL Schamatic of Reversible OR Plane

1st International Conference on Innovations and Advancements in Information and Communication Technology 417

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

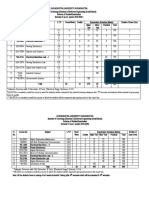

EXPERIMENTAL RESULT The proposed new RPLA resulted by VHDL and simulated on Xilinx ISE8.2i.

Figure 8: Simulated result of reversible AND palne

Figure 9: Simulated result of reversible OR plane

CONCLUSION In this paper we emphasis on an efficient approach to design low power digital system for industrial applications using RPLA. In this new RPLA design by Feynman & Mux gate is proposed..As we already discussed the quantum cost of the MUX gate is lower than the Fredkin gate and Mux gate can perform all operation that can be performed by fredkin. So the proposed RPLA by MUX gate is more cost - efficient than the existing one. In this paper we also represent the simulated results of the proposed RPLA which are completely varified and correct in all sense. So, to reduce the energy consumption, reversible PLA is one of the important logic arrays in digital system design. This work is expected to provide a new approach for design of low power reconfigurable computing for industrial applications. REFERENCES R. Landauer, (1961). Irreversibility and Heat Generation in the Computational Process, IBM J. Res. Develop., vol. 5, pp. 183-191. C. H. Bennet, (1973). Logical Reversibility of Computation, IBM J. Res. Develop., vol. 17, no. 6, pp. 525-532. T. Toffoli., (1980). Reversible Computing, Tech Memo MIT/LCS/TM-151, MIT Lab for Computer Science. Himanshu Thapliyal and Hamid R. Arabnia, (2006). Reversible Programmable Logic Array using Fredkin & Feynmam Gates for Industrial Electronics and Applications, Proceedings if International Conference on Embedded Systems (ESA06), USA.

1st International Conference on Innovations and Advancements in Information and Communication Technology 418

Reversible Programmable Logic Array (RPLA) Using Feynman & MUX Gates for Low Power

Abu Sadat Md. Sayem and Sajib Kumar Mitra, (2011). Efficient Approach to Design Low Power Reversible Logic Blocks for Field Programmable Gate Arrays978-114244-8728-8/11/IEEE. H.R. Bhagyalakshmi, M.K. Venkeatesha, (2010). An Improved Design of a Multiplier using Reversible Logic Gates, International Journal of Engineering Science and Technology, vol.2 (8), pp.3838-3845. G. De Mey and A. De Vos, (2008). The Minimum Energy for a One Bit Comutation: A Proof of the Landauer Limit, Proc.26th International Conf. On Microelectronics IEEE. Michael P. Frank, (2005). Introduction to Reversible Computing: Motivation, Progress and challenges, Proceedings of 2nd International Conference on Computing Frontiers ACM New York. Ahsan Raja Chowdhury, Rumana Nazmul, Hafiz Md. Hasan Babu, (2006). A New Approach to Synthesis Multiple-Output Functions using Reversible Programmable Logic Array Proceedings of the 19th International Conference on VLSI Design., 1063-9667. J. Bhasker, A VHDL Primer, Third Edition, Pearson Education.

1st International Conference on Innovations and Advancements in Information and Communication Technology 419

S-ar putea să vă placă și

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDe la EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryEvaluare: 3.5 din 5 stele3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)De la EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Evaluare: 4.5 din 5 stele4.5/5 (120)

- Grit: The Power of Passion and PerseveranceDe la EverandGrit: The Power of Passion and PerseveranceEvaluare: 4 din 5 stele4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDe la EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaEvaluare: 4.5 din 5 stele4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingDe la EverandThe Little Book of Hygge: Danish Secrets to Happy LivingEvaluare: 3.5 din 5 stele3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDe la EverandNever Split the Difference: Negotiating As If Your Life Depended On ItEvaluare: 4.5 din 5 stele4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeDe la EverandShoe Dog: A Memoir by the Creator of NikeEvaluare: 4.5 din 5 stele4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDe la EverandThe Emperor of All Maladies: A Biography of CancerEvaluare: 4.5 din 5 stele4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDe la EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeEvaluare: 4 din 5 stele4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDe la EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyEvaluare: 3.5 din 5 stele3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDe la EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersEvaluare: 4.5 din 5 stele4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDe la EverandTeam of Rivals: The Political Genius of Abraham LincolnEvaluare: 4.5 din 5 stele4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDe la EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreEvaluare: 4 din 5 stele4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDe la EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceEvaluare: 4 din 5 stele4/5 (895)

- Her Body and Other Parties: StoriesDe la EverandHer Body and Other Parties: StoriesEvaluare: 4 din 5 stele4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDe la EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureEvaluare: 4.5 din 5 stele4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDe la EverandThe Unwinding: An Inner History of the New AmericaEvaluare: 4 din 5 stele4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)De la EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Evaluare: 4 din 5 stele4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDe la EverandOn Fire: The (Burning) Case for a Green New DealEvaluare: 4 din 5 stele4/5 (73)

- Entropy: Deep Residual Learning For Nonlinear RegressionDocument14 paginiEntropy: Deep Residual Learning For Nonlinear RegressionPradeep SinglaÎncă nu există evaluări

- IMF3Document96 paginiIMF3Pradeep SinglaÎncă nu există evaluări

- ControlDocument1 paginăControlPradeep SinglaÎncă nu există evaluări

- Apiit S.D. India, Panipat Apiit S.D. India, Panipat: Sessional - I Sessional - IDocument1 paginăApiit S.D. India, Panipat Apiit S.D. India, Panipat: Sessional - I Sessional - IPradeep SinglaÎncă nu există evaluări

- Citizen Registration and Appointment For Vaccination User ManualDocument14 paginiCitizen Registration and Appointment For Vaccination User ManualSahilÎncă nu există evaluări

- Signal and SystemDocument1 paginăSignal and SystemPradeep SinglaÎncă nu există evaluări

- TT Btech & Bca 21.12.2020Document78 paginiTT Btech & Bca 21.12.2020Pradeep SinglaÎncă nu există evaluări

- Bca 2011-12 PDFDocument39 paginiBca 2011-12 PDFfunny videosÎncă nu există evaluări

- Energies 12 01822Document22 paginiEnergies 12 01822Pradeep SinglaÎncă nu există evaluări

- A Study of Soft Computing TechniquesDocument19 paginiA Study of Soft Computing TechniquesPradeep SinglaÎncă nu există evaluări

- A Study of Soft Computing TechniquesDocument19 paginiA Study of Soft Computing TechniquesPradeep SinglaÎncă nu există evaluări

- Time Series Forecasting Using Deep Learning - MATLAB & SimulinkDocument7 paginiTime Series Forecasting Using Deep Learning - MATLAB & SimulinkPradeep SinglaÎncă nu există evaluări

- Data Regarding Ph.D. Scholars of ECE Department, DCRUST, Murthal-131039Document3 paginiData Regarding Ph.D. Scholars of ECE Department, DCRUST, Murthal-131039Pradeep SinglaÎncă nu există evaluări

- 160 Credit MECHATRONICS SYLLABUS FIRST-EIGHT SEMDocument117 pagini160 Credit MECHATRONICS SYLLABUS FIRST-EIGHT SEMPradeep SinglaÎncă nu există evaluări

- Electrical Machines - I: Electric Circuit TheoryDocument22 paginiElectrical Machines - I: Electric Circuit TheoryPradeep SinglaÎncă nu există evaluări

- Recent Trends in Electric Power and Energy Systems-2020 (RTEPES-2020)Document1 paginăRecent Trends in Electric Power and Energy Systems-2020 (RTEPES-2020)Pradeep SinglaÎncă nu există evaluări

- TTDocument4 paginiTTPradeep SinglaÎncă nu există evaluări

- TTDocument2 paginiTTPradeep SinglaÎncă nu există evaluări

- TT Btech & Bca 14.09.2020 OnlineDocument50 paginiTT Btech & Bca 14.09.2020 OnlinePradeep SinglaÎncă nu există evaluări

- Prediction Error For Identified Model - MATLAB Pe - MathWorks IndiaDocument4 paginiPrediction Error For Identified Model - MATLAB Pe - MathWorks IndiaPradeep SinglaÎncă nu există evaluări

- Annexure - A12 (Electrical & Electronics Engg - )Document6 paginiAnnexure - A12 (Electrical & Electronics Engg - )Pradeep SinglaÎncă nu există evaluări

- How To Model Residual Errors To Correct Time Series Forecasts With PythonDocument22 paginiHow To Model Residual Errors To Correct Time Series Forecasts With PythonPradeep SinglaÎncă nu există evaluări

- Prediction Error For Identified Model - MATLAB Pe - MathWorks IndiaDocument4 paginiPrediction Error For Identified Model - MATLAB Pe - MathWorks IndiaPradeep SinglaÎncă nu există evaluări

- List of B.tech 8619 Students - (3RD Sem)Document2 paginiList of B.tech 8619 Students - (3RD Sem)Pradeep SinglaÎncă nu există evaluări

- Subject Code: Basic Electronics EngineeringDocument5 paginiSubject Code: Basic Electronics EngineeringPradeep SinglaÎncă nu există evaluări

- COM 205 Multimedia Applications: St. Joseph's College Fall 2004Document45 paginiCOM 205 Multimedia Applications: St. Joseph's College Fall 2004loadaÎncă nu există evaluări

- On The Use of Wavelets Packet Decomposition For Time Series PredictionDocument12 paginiOn The Use of Wavelets Packet Decomposition For Time Series PredictionPradeep SinglaÎncă nu există evaluări

- Hargreaves Samani PDFDocument13 paginiHargreaves Samani PDFAnonymous M0tjyWÎncă nu există evaluări

- The 8051 Microcontroller: Introduction To MicrocontrollersDocument8 paginiThe 8051 Microcontroller: Introduction To MicrocontrollersPradeep SinglaÎncă nu există evaluări

- Renewable Energy For Sustainable Growth Assessment: EditorsDocument2 paginiRenewable Energy For Sustainable Growth Assessment: EditorsPradeep SinglaÎncă nu există evaluări

- 18bib23c U4Document13 pagini18bib23c U4Thashni PriyaÎncă nu există evaluări

- Digital Open EndedDocument13 paginiDigital Open EndedudayÎncă nu există evaluări

- 4d Digital System-Adder Encoder Decoder and MuxDocument42 pagini4d Digital System-Adder Encoder Decoder and MuxAhmad IzzuddinÎncă nu există evaluări

- Logic Design Sample Questions - Veda IIT - Official PageDocument3 paginiLogic Design Sample Questions - Veda IIT - Official PageGanagadhar CHÎncă nu există evaluări

- ECE 301 - Digital Electronics: CountersDocument25 paginiECE 301 - Digital Electronics: CountersHayan FadhilÎncă nu există evaluări

- VHDL Code For Counters With TestbenchDocument6 paginiVHDL Code For Counters With TestbenchTayou DieunedortÎncă nu există evaluări

- Part 1: Adder and SubtracterDocument12 paginiPart 1: Adder and SubtracterVenus Ilagan100% (2)

- Verlogic3 Chapter5Document90 paginiVerlogic3 Chapter5rahul parmarÎncă nu există evaluări

- BECE102L-Digital Systems Design: Course InstructorDocument115 paginiBECE102L-Digital Systems Design: Course Instructorhitesh bonamÎncă nu există evaluări

- VHDL Codes For Various Combinational CircuitsDocument6 paginiVHDL Codes For Various Combinational CircuitsKaranÎncă nu există evaluări

- Verilog Code For Simple ComputerDocument7 paginiVerilog Code For Simple ComputerEng'r Safeer AnsarÎncă nu există evaluări

- DSD Model Important QuestionsDocument2 paginiDSD Model Important QuestionsGiriÎncă nu există evaluări

- Computer Organization and Architecture LabExperimentsDocument31 paginiComputer Organization and Architecture LabExperimentsfun time [funny videos]Încă nu există evaluări

- DLD - Chapter 3 - 1Document31 paginiDLD - Chapter 3 - 1Nguyễn DuyÎncă nu există evaluări

- DLD Lecture 4Document53 paginiDLD Lecture 4sjbv.hardik582Încă nu există evaluări

- Hardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)Document3 paginiHardware Implementation of 8-Bit Adder/subtractor (Using Carry Look Ahead Adder)Nafi SiamÎncă nu există evaluări

- Logic Gates SymbolsDocument6 paginiLogic Gates Symbolssebastian guaicaraÎncă nu există evaluări

- It2623 Module3 Combi CKT Mod4 PLDDocument53 paginiIt2623 Module3 Combi CKT Mod4 PLDDERICK TIMOTHY CASTROÎncă nu există evaluări

- Gate Performance Characteristics and ParametersDocument7 paginiGate Performance Characteristics and ParametersAnup JalotaÎncă nu există evaluări

- Cb2Ce, Cb4Ce, Cb8Ce, Cb16Ce: 2-, 4-, 8-,16-Bit Cascadable Binary Counters With Clock Enable and Asynchronous ClearDocument6 paginiCb2Ce, Cb4Ce, Cb8Ce, Cb16Ce: 2-, 4-, 8-,16-Bit Cascadable Binary Counters With Clock Enable and Asynchronous ClearzippolÎncă nu există evaluări

- Appendix B Adders and D-Type Flip FlopsDocument31 paginiAppendix B Adders and D-Type Flip FlopsGlen MuthokaÎncă nu există evaluări

- Chapter ThreeDocument31 paginiChapter Threeelias ferhanÎncă nu există evaluări

- Lec-5 Basic Logic GatesDocument20 paginiLec-5 Basic Logic GatesManjare Hassin RaadÎncă nu există evaluări

- DecodersandEncoders NotesDocument14 paginiDecodersandEncoders NotesRohitÎncă nu există evaluări

- F19 Sysc3006 Finalexam 1Document13 paginiF19 Sysc3006 Finalexam 1FrostÎncă nu există evaluări

- Poornima College of Engineering A Seminar Presentation On: Fpga and Functions Realisation Using FpgaDocument21 paginiPoornima College of Engineering A Seminar Presentation On: Fpga and Functions Realisation Using FpgaVivek PCE/15/EC/119Încă nu există evaluări

- NAND and NOR ImplementationDocument13 paginiNAND and NOR ImplementationCörë ByäküyäÎncă nu există evaluări

- ICs Semiconductors Logic CMOS 4000 SeriesDocument3 paginiICs Semiconductors Logic CMOS 4000 SeriesAlfredo Meurer JuniorÎncă nu există evaluări

- Vlsi Comple Lab TaskDocument37 paginiVlsi Comple Lab TaskTausique SheikhÎncă nu există evaluări

- Pramod 2019Document12 paginiPramod 2019venkat301485Încă nu există evaluări